#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <a href="http://www.nxp.com">http://www.nxp.com</a>, <a href="http://www.semiconductors.philips.com/">http://www.nxp.com</a>, <a href="http://www.nexperia.com/">http://www.nexperia.com/</a>, <a href="http://www.nexperia.com/">http://www.nexperia.com/</a>, <a href="http://www.nexperia.com/">use http://www.nexperia.com/</a>

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use salesaddresses@nexperia.com (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

## INTEGRATED CIRCUITS

## DATA SHEET

For a complete data sheet, please also download:

- The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

## 74HC/HCT4514

4-to-16 line decoder/demultiplexer with input latches

Product specification

File under Integrated Circuits, IC06

September 1993

## 74HC/HCT4514

#### **FEATURES**

· Non-inverting outputs

· Output capability: standard

I<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

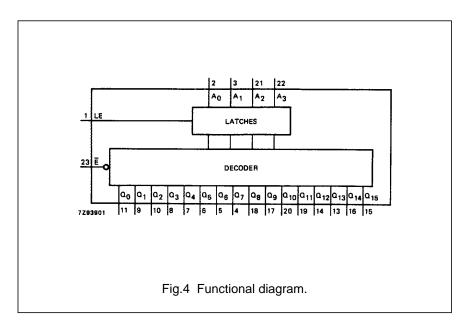

The 74HC/HCT4514 are high-speed Si-gate CMOS devices and are pin compatible with "4514" of the "4000B" series. They are specified in compliance with JEDEC standard no. 7A.

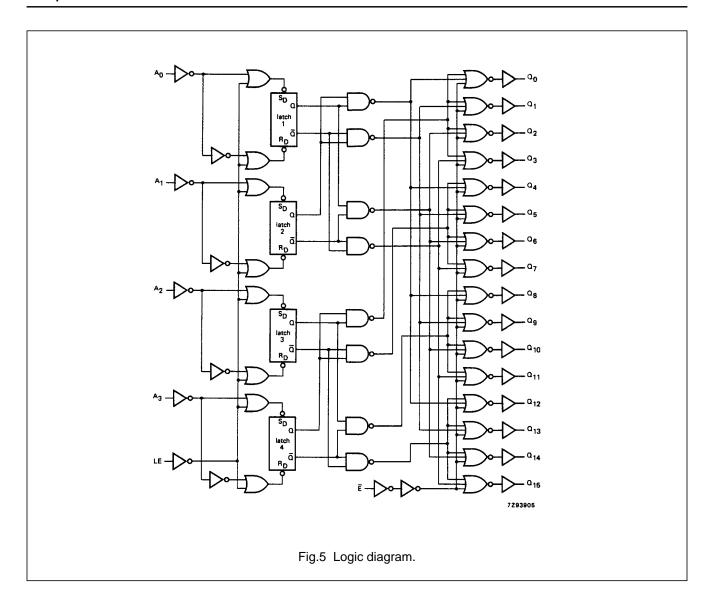

The 74HC/HCT4514 are 4-to-16 line decoders/demultiplexers having four binary weighted address inputs (A $_0$  to A $_3$ ), with latches, a latch enable input (LE), and an active LOW enable input ( $\overline{\rm E}$ ). The 16 outputs (Q $_0$  to Q $_{15}$ ) are mutually exclusive active HIGH. When LE is HIGH, the selected output is determined by the data on A $_n$ . When LE goes LOW, the last data present at A $_n$  are stored in the latches and the outputs remain stable. When  $\overline{\rm E}$  is LOW, the selected output, determined by the contents of the latch, is HIGH. At  $\overline{\rm E}$  HIGH, all outputs are LOW. The enable input ( $\overline{\rm E}$ ) does not affect the state of the latch.

When the "4514" is used as a demultiplexer,  $\overline{E}$  is the data input and  $A_0$  to  $A_3$  are the address inputs.

#### **QUICK REFERENCE DATA**

$GND = 0 V; T_{amb} = 25 °C; t_r = t_f = 6 ns$

| SYMBOL                              | PARAMETER                                          | CONDITIONS                                  | TYP | UNIT |      |  |

|-------------------------------------|----------------------------------------------------|---------------------------------------------|-----|------|------|--|

| STWIDOL                             | PARAWETER                                          | CONDITIONS                                  | нс  | нст  | ONII |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay A <sub>n</sub> to Q <sub>n</sub> | $C_L = 15 \text{ pF}; V_{CC} = 5 \text{ V}$ | 23  | 26   | ns   |  |

| C <sub>I</sub>                      | input capacitance                                  |                                             | 3.5 | 3.5  | pF   |  |

| C <sub>PD</sub>                     | power dissipation capacitance per package          | notes 1 and 2                               | 44  | 45   | pF   |  |

#### Notes

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$$P_D = C_{PD} \times V_{CC}^2 \times f_i + \sum (C_1 \times V_{CC}^2 \times f_o)$$

where:

f<sub>i</sub> = input frequency in MHz

fo = output frequency in MHz

$\sum (C_L \times V_{CC}^2 \times f_0) = \text{sum of outputs}$

C<sub>I</sub> = output load capacitance in pF

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_I = GND$  to  $V_{CC}$ For HCT the condition is  $V_I = GND$  to  $V_{CC} - 1.5$  V

#### **ORDERING INFORMATION**

See "74HC/HCT/HCU/HCMOS Logic Package Information".

## 74HC/HCT4514

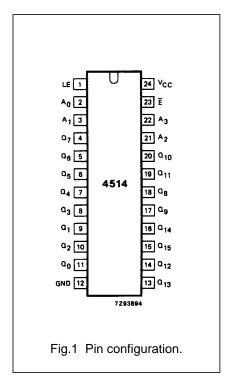

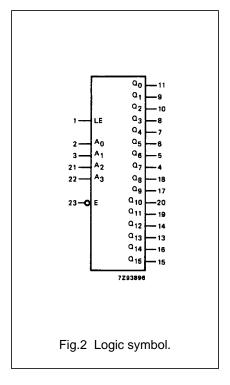

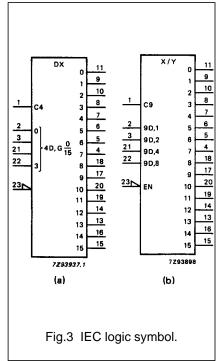

## **PIN DESCRIPTION**

| PIN NO.                                                  | SYMBOL                            | NAME AND FUNCTION                 |

|----------------------------------------------------------|-----------------------------------|-----------------------------------|

| 1                                                        | LE                                | latch enable input (active HIGH)  |

| 2, 3, 21, 22                                             | A <sub>0</sub> to A <sub>3</sub>  | address inputs                    |

| 11, 9, 10, 8, 7, 6, 5, 4, 18, 17, 20, 19, 14, 13, 16, 15 | Q <sub>0</sub> to Q <sub>15</sub> | multiplexer outputs (active HIGH) |

| 12                                                       | GND                               | ground (0 V)                      |

| 23                                                       | Ē                                 | enable input (active LOW)         |

| 24                                                       | V <sub>CC</sub>                   | positive supply voltage           |

Philips Semiconductors Product specification

# 4-to-16 line decoder/demultiplexer with input latches

## 74HC/HCT4514

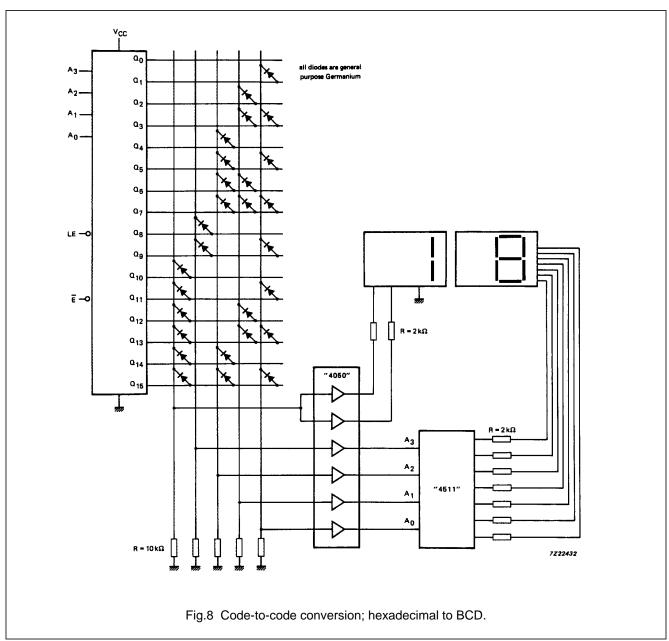

## **APPLICATIONS**

- · Digital multiplexing

- · Address decoding

- Hexadecimal/BCD decoding

## **FUNCTION TABLE**

|             | II             | NPUT                  | S              |                       | OUTPUTS     |             |                  |             |             |             |       |                |                |             |                 |                 |                 |                 |                  |                 |

|-------------|----------------|-----------------------|----------------|-----------------------|-------------|-------------|------------------|-------------|-------------|-------------|-------|----------------|----------------|-------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|

| Ē           | A <sub>0</sub> | <b>A</b> <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | $Q_0$       | $Q_1$       | Q <sub>2</sub>   | $Q_3$       | $Q_4$       | $Q_5$       | $Q_6$ | Q <sub>7</sub> | Q <sub>8</sub> | $Q_9$       | Q <sub>10</sub> | Q <sub>11</sub> | Q <sub>12</sub> | Q <sub>13</sub> | Q <sub>14</sub>  | Q <sub>15</sub> |

| Н           | Х              | Х                     | Х              | Х                     | L           | L           | L                | L           | L           | L           | L     | L              | L              | L           | L               | L               | L               | L               | L                | L               |

| L<br>L<br>L | L<br>H<br>L    | L<br>H<br>H           | L<br>L<br>L    | L<br>L<br>L           | H<br>L<br>L | L<br>H<br>L | L<br>L<br>H<br>L | L<br>L<br>H | L<br>L<br>L | L<br>L<br>L |       | L<br>L<br>L    | L<br>L<br>L    | L<br>L<br>L | L<br>L<br>L     | L<br>L<br>L     | L<br>L<br>L     | L<br>L<br>L     | L<br>L<br>L      | L<br>L<br>L     |

| L<br>L<br>L | L<br>H<br>L    | L<br>H<br>H           | H<br>H<br>H    | L<br>L<br>L           | L<br>L<br>L | L<br>L<br>L | L<br>L<br>L      | L<br>L<br>L | H<br>L<br>L | L<br>H<br>L | LLTL  | L<br>L<br>H    | L<br>L<br>L    | L<br>L<br>L | L<br>L<br>L     | L<br>L<br>L     | L<br>L<br>L     | L<br>L<br>L     | L<br>L<br>L      | L<br>L<br>L     |

| L<br>L<br>L | L<br>H<br>L    | L<br>H<br>H           | L<br>L<br>L    | H<br>H<br>H           | L<br>L<br>L | L<br>L<br>L | L<br>L<br>L      | L<br>L<br>L | L<br>L<br>L | L<br>L<br>L |       | L<br>L<br>L    | H<br>L<br>L    | L<br>H<br>L | L<br>H<br>L     | L<br>L<br>H     | L<br>L<br>L     | L<br>L<br>L     | L<br>L<br>L      | L<br>L<br>L     |

| L<br>L<br>L | L<br>H<br>L    | L<br>L<br>H           | H<br>H<br>H    | H<br>H<br>H           | L<br>L<br>L |             | L<br>L<br>L      |             |             | L<br>L<br>L |       | L<br>L<br>L    | L<br>L<br>L    | L<br>L<br>L | L<br>L<br>L     | L<br>L<br>L     | H<br>L<br>L     | LHLL            | L<br>L<br>H<br>L | L<br>L<br>H     |

#### **Notes**

1. LE = HIGH

H = HIGH voltage level

L = LOW voltage level

X = don't care

## 74HC/HCT4514

Philips Semiconductors Product specification

# 4-to-16 line decoder/demultiplexer with input latches

74HC/HCT4514

## DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

## **AC CHARACTERISTICS FOR 74HC**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                     | DADAMETED                                          |                |                 | •               | T <sub>amb</sub> (° |                 | TEST CONDITIONS |                 |      |                   |           |

|-------------------------------------|----------------------------------------------------|----------------|-----------------|-----------------|---------------------|-----------------|-----------------|-----------------|------|-------------------|-----------|

| SYMBOL                              |                                                    |                |                 |                 | 74HC                |                 |                 | MANEEODME       |      |                   |           |

|                                     | PARAMETER                                          | +25            |                 |                 | -40 t               | to +85          | -40 to          | 0 +125          | UNIT | V <sub>CC</sub>   | WAVEFORMS |

|                                     |                                                    | min.           | typ.            | max.            | min.                | max.            | min.            | max.            |      | ( ' /             |           |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay A <sub>n</sub> to Q <sub>n</sub> |                | 74<br>27<br>22  | 230<br>46<br>39 |                     | 290<br>58<br>49 |                 | 345<br>69<br>59 | ns   | 2.0<br>4.5<br>6.0 | Fig.6     |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>LE to Q <sub>n</sub>          |                | 74<br>27<br>22  | 230<br>46<br>39 |                     | 290<br>58<br>49 |                 | 345<br>69<br>59 | ns   | 2.0<br>4.5<br>6.0 | Fig.6     |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>E to Q <sub>n</sub>           |                | 41<br>15<br>12  | 175<br>35<br>30 |                     | 220<br>44<br>37 |                 | 265<br>53<br>45 | ns   | 2.0<br>4.5<br>6.0 | Fig.6     |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                             |                | 19<br>7<br>6    | 75<br>15<br>13  |                     | 95<br>19<br>16  |                 | 110<br>22<br>19 | ns   | 2.0<br>4.5<br>6.0 | Fig.6     |

| t <sub>W</sub>                      | latch enable pulse width<br>HIGH                   | 80<br>16<br>14 | 14<br>5<br>4    |                 | 100<br>20<br>17     |                 | 120<br>24<br>20 |                 | ns   | 2.0<br>4.5<br>6.0 | Fig.7     |

| t <sub>su</sub>                     | set-up time<br>A <sub>n</sub> to LE                | 90<br>18<br>15 | 25<br>9<br>7    |                 | 115<br>23<br>20     |                 | 135<br>27<br>23 |                 | ns   | 2.0<br>4.5<br>6.0 | Fig.7     |

| t <sub>h</sub>                      | hold time<br>A <sub>n</sub> to LE                  | 1<br>1<br>1    | -11<br>-4<br>-3 |                 | 1<br>1<br>1         |                 | 1<br>1<br>1     |                 | ns   | 2.0<br>4.5<br>6.0 | Fig.7     |

Philips Semiconductors Product specification

# 4-to-16 line decoder/demultiplexer with input latches

74HC/HCT4514

## DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

## Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications.

To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT          | UNIT LOAD COEFFICIENT |

|----------------|-----------------------|

| A <sub>n</sub> | 0.65                  |

| LE             | 1.40                  |

| Ē              | 1.00                  |

## **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

| SYMBOL                              | PARAMETER                                          |      |      | 7    |            | TEST CONDITIONS |             |      |      |                 |            |

|-------------------------------------|----------------------------------------------------|------|------|------|------------|-----------------|-------------|------|------|-----------------|------------|

|                                     |                                                    |      |      |      |            |                 | WAVEFORMS   |      |      |                 |            |

|                                     | PARAMETER                                          | +25  |      |      | -40 to +85 |                 | -40 to +125 |      | UNIT | V <sub>CC</sub> | WAVEFORING |

|                                     |                                                    | min. | typ. | max. | min.       | max.            | min.        | max. |      | (•,             |            |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay A <sub>n</sub> to Q <sub>n</sub> |      | 30   | 55   |            | 69              |             | 83   | ns   | 4.5             | Fig.6      |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>LE to Q <sub>n</sub>          |      | 29   | 50   |            | 63              |             | 75   | ns   | 4.5             | Fig.6      |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>E to Q <sub>n</sub>           |      | 17   | 40   |            | 50              |             | 60   | ns   | 4.5             | Fig.6      |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                             |      | 7    | 15   |            | 19              |             | 22   | ns   | 4.5             | Fig.6      |

| t <sub>W</sub>                      | latch enable pulse width HIGH                      | 16   | 4    |      | 20         |                 | 24          |      | ns   | 4.5             | Fig.7      |

| t <sub>su</sub>                     | set-up time<br>A <sub>n</sub> to LE                | 18   | 9    |      | 23         |                 | 27          |      | ns   | 4.5             | Fig.7      |

| t <sub>h</sub>                      | hold time<br>A <sub>n</sub> to LE                  | 3    | -3   |      | 3          |                 | 3           |      | ns   | 4.5             | Fig.7      |

## 74HC/HCT4514

#### **AC WAVEFORMS**

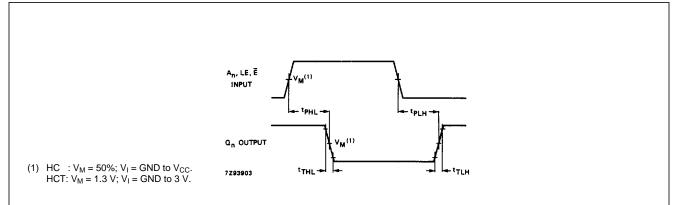

Fig.6 Waveforms showing the input  $(A_n, LE, \overline{E})$  to output  $(Q_n)$  propagation delays and the output transition times.

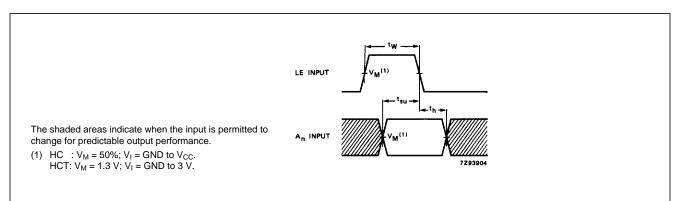

Fig.7 Waveforms showing the minimum pulse width of the latch enable input (LE) and the set-up and hold times for LE to A<sub>n</sub>. Set-up and hold times are shown as positive values but may be specified as negative values.

## 74HC/HCT4514

## **APPLICATION INFORMATION**

## **PACKAGE OUTLINES**

See "74HC/HCT/HCU/HCMOS Logic Package Outlines".

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## NXP:

74HC4514D,652 74HC4514DB,112 74HC4514DB,118 74HC4514DB,118 74HC4514DB,118 74HC4514DB,118 74HCT4514DB,118 74HCT4514DB,118 74HCT4514DB,118 74HCT4514DB,118 74HCT4514DB,118 74HCT4514PW,118