TPA6211A1-Q1

ZHCS294C -JUNE 2011-REVISED AUGUST 2016

# TPA6211A1-Q1 3.1W 单声道、全差分音频功率放大器

## 1 特性

- 适用于汽车电子 应用

- 符合 AEC-Q100 标准的下列结果:

- 器件温度**2**级: **-40°**C 至 **105°**C 的环境运行温度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级 3A

- 器件带电器件模型 (CDM) ESD 分类等级 C6

- 当

THD = 10%(典型值)时,5V 电源下的输出功率 是 3.1W/3 $\Omega$

- 低电源电流: 5V 时的典型值为 4mA

- 关断电流: 0.01µA(典型值)

- 具有最小杂音的快速启动

- 仅三个外部组件

- 针对直接电池供电运行的经改进电源抑制比 (PSRR) (-80dB) 和宽电源电压(2.5V至 5.5V)

- 全差动设计减少了 RF 整流

- 共模抑制比 (CMRR) 为 -63dB,省去了两个输入

耦合电容

## 2 应用范围

- 汽车音频

- 紧急呼叫

- 驾驶员通知

- 仪表板蜂鸣装置

# 3 说明

TPA6211A1-Q1 器件是一款 3.1W 单声道、全差分放大器,设计用于驱动阻抗为 3Ω 的扬声器,在大多数应用中仅占用 20mm² 的印刷电路板 (PCB) 区域。此器件的运行电压介于 2.5V 至 5.5V 之间,仅仅汲取 4mA的静态电源电流。TPA6211A1-Q1 器件采用节省空间的 8 引脚表面贴装小外形尺寸 (MSOP) (DGN) PowerPAD™封装。

该器件包含的 特性 有 -80dB 的电源电压抑制(20Hz 到 2KHz)、改善的 RF 整流抗扰度以及较小的 PCB 占用面积。杂音极低的快速启动特性使得

TPA6211A1-Q1 器件成为了紧急呼叫应用的 理想之选。此外,该器件能够满足信息娱乐和仪表板 应用中的低功耗需求,这类应用包括仪表板蜂鸣装置或驾驶员通知。

#### 器件信息(1)

| 器件型号         | 封装                | 封装尺寸 (标称值)      |

|--------------|-------------------|-----------------|

| TPA6211A1-Q1 | MSOP-PowerPAD (8) | 3.00mm x 3.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

(1) C<sub>(BYPASS)</sub> 为选配

| 目      | 录 |

|--------|---|

| $\Box$ | 1 |

| 1 | 特性1                                  | 7.3 Feature Description               | 12 |

|---|--------------------------------------|---------------------------------------|----|

| 2 | 应用范围                                 | 7.4 Device Functional Modes           |    |

| 3 | 说明1                                  | 8 Application and Implementation      | 18 |

| 4 | 修订历史记录                               | 8.1 Application Information           |    |

| 5 | Pin Configuration and Functions      | 8.2 Typical Applications              | 18 |

| 6 | Specifications                       | 9 Power Supply Recommendations        | 23 |

| U | 6.1 Absolute Maximum Ratings         | 9.1 Power Supply Decoupling Capacitor | 24 |

|   | 6.2 ESD Ratings                      | 10 Layout                             | 24 |

|   | 6.3 Recommended Operating Conditions | 10.1 Layout Guidelines                | 24 |

|   | 6.4 Thermal Information              | 10.2 Layout Example                   | 24 |

|   | 6.5 Electrical Characteristics       | 11 器件和文档支持                            | 25 |

|   | 6.6 Operating Characteristics        | 11.1 接收文档更新通知                         | 25 |

|   | 6.7 Dissipation Ratings 5            | 11.2 社区资源                             | 25 |

|   | 6.8 Typical Characteristics          | 11.3 商标                               | 25 |

| 7 | Detailed Description 12              | 11.4 静电放电警告                           | 25 |

|   | 7.1 Overview 12                      | 11.5 Glossary                         |    |

|   | 7.2 Functional Block Diagram 12      | 12 机械、封装和可订购信息                        | 25 |

|   | -                                    |                                       |    |

#### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

#

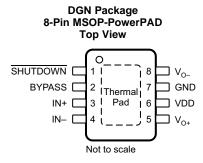

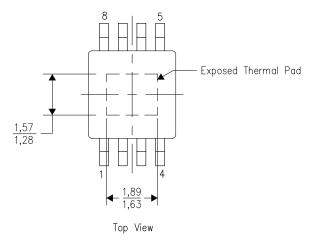

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN              |     | 1/0 | DESCRIPTION                                                                                                    |

|------------------|-----|-----|----------------------------------------------------------------------------------------------------------------|

| NAME             | NO. | 1/0 | DESCRIPTION                                                                                                    |

| BYPASS           | 2   | - 1 | Mid-supply voltage, adding a bypass capacitor improves PSRR                                                    |

| GND              | 7   | - 1 | High-current ground                                                                                            |

| IN-              | 4   | - 1 | Negative differential input                                                                                    |

| IN+              | 3   | I   | Positive differential input                                                                                    |

| SHUTDOWN         | 1   | I   | Shutdown pin (active low logic)                                                                                |

| Thermal Pad      | _   | _   | Connect to ground. Thermal pad must be soldered down in all applications to properly secure device on the PCB. |

| $V_{DD}$         | 6   | I   | Power supply                                                                                                   |

| V <sub>O+</sub>  | 5   | 0   | Positive BTL output                                                                                            |

| V <sub>O</sub> - | 8   | 0   | Negative BTL output                                                                                            |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                                        |     | MIN       | MAX              | UNIT |

|--------------------------------------------------------|-----|-----------|------------------|------|

| Supply voltage, V <sub>DD</sub>                        |     | -0.3      | 6                | V    |

| Input voltage, V <sub>I</sub>                          |     | -0.3      | $V_{DD} + 0.3 V$ | V    |

| Continuous total power dissipation                     |     | See Dissi | pation Ratings   |      |

| Lead temperature 1.6 mm (1/16 Inch) from case for 10 s | DGN |           | 260              | °C   |

| Operating free-air temperature, T <sub>A</sub>         | ·   | -40       | 105              | °C   |

| Junction temperature, T <sub>J</sub>                   |     | -40       | 150              | °C   |

| Storage temperature, T <sub>stg</sub>                  |     | -65       | 150              | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±4000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

|                 | , J                            |          | MIN  | MAX | UNIT |

|-----------------|--------------------------------|----------|------|-----|------|

| V <sub>DD</sub> | Supply voltage                 |          | 2.5  | 5.5 | V    |

| V <sub>IH</sub> | High-level input voltage       | SHUTDOWN | 1.55 |     | V    |

| $V_{IL}$        | Low-level input voltage        | SHUTDOWN |      | 0.5 | V    |

| T <sub>A</sub>  | Operating free-air temperature |          | -40  | 105 | °C   |

## 6.4 Thermal Information

|                      |                                              | TPA6211A1-Q1        |      |

|----------------------|----------------------------------------------|---------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGN (MSOP-PowerPAD) | UNIT |

|                      |                                              | 8 PINS              |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 71.7                | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 55.9                | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 44.9                | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 3.7                 | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 44.7                | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 19.6                | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

$T_A = 25^{\circ}C$

|                   | PARAMETER                                       | TEST CONDITIONS                                                                                    |                         | MIN                                              | TYP                                              | MAX                                              | UNIT   |

|-------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------|

| Vos               | Output offset voltage (measured differentially) | V <sub>I</sub> = 0-V differential, Gain = 1 V/V, V <sub>DD</sub> =                                 | 5.5 V                   | -9                                               | 0.3                                              | 9                                                | mV     |

| PSRR              | Power supply rejection ratio                    | V <sub>DD</sub> = 2.5 V to 5.5 V                                                                   |                         |                                                  | -85                                              | -60                                              | dB     |

| V <sub>IC</sub>   | Common mode input range                         | V <sub>DD</sub> = 2.5 V to 5.5 V                                                                   |                         | 0.5                                              |                                                  | $V_{DD} - 0.8$                                   | V      |

| CMRR              | Common mode valenties votic                     | V <sub>DD</sub> = 5.5 V, V <sub>IC</sub> = 0.5 V to 4.7 V                                          |                         |                                                  | -63                                              | -40                                              | dB     |

| CIVIRR            | Common mode rejection ratio                     | $V_{DD} = 2.5 \text{ V}, V_{IC} = 0.5 \text{ V to } 1.7 \text{ V}$                                 |                         |                                                  | -63                                              | -40                                              | ub<br> |

|                   |                                                 |                                                                                                    | V <sub>DD</sub> = 5.5 V |                                                  | 0.45                                             |                                                  |        |

|                   | Low-output swing                                | $R_L = 4 \Omega$ , $V_{IN+} = V_{DD}$ , $V_{IN+} = 0 V$ ,<br>$V_{IN-} = 0 V$ or $V_{IN-} = 0 V$    | V <sub>DD</sub> = 3.6 V |                                                  | 0.37                                             |                                                  | V      |

|                   |                                                 | Same i viv, vin= o v oi vin= v bb                                                                  | V <sub>DD</sub> = 2.5 V |                                                  | 0.26                                             | 0.4                                              | 1      |

|                   |                                                 |                                                                                                    | V <sub>DD</sub> = 5.5 V |                                                  | 4.95                                             |                                                  |        |

|                   | High-output swing                               | $R_L = 4 \Omega$ , $V_{IN+} = V_{DD}$ , $V_{IN-} = V_{DD}$ ,<br>$V_{IN-} = 0 V$ or $V_{IN+} = 0 V$ | V <sub>DD</sub> = 3.6 V |                                                  | 3.18                                             |                                                  | V      |

|                   |                                                 | Sain = 1                                                                                           | V <sub>DD</sub> = 2.5 V | 2                                                | 2.13                                             |                                                  | 1      |

| I <sub>IH</sub>   | High-level input current, shutdown              | V <sub>DD</sub> = 5.5 V, V <sub>I</sub> = 5.8 V                                                    | ·                       |                                                  | 58                                               | 100                                              | μΑ     |

| I <sub>IL</sub>   | Low-level input current, shutdown               | V <sub>DD</sub> = 5.5 V, V <sub>I</sub> = -0.3 V                                                   |                         |                                                  | 3                                                | 100                                              | μΑ     |

| IQ                | Quiescent current                               | V <sub>DD</sub> = 2.5 V to 5.5 V, no load                                                          |                         |                                                  | 4                                                | 5                                                | mA     |

| I <sub>(SD)</sub> | Supply current                                  | $V_{\overline{SHUTDOWN}} \le 0.5 \text{ V}, V_{DD} = 2.5 \text{ V to } 5.5 \text{ V}$              | , R <sub>L</sub> = 4 Ω  |                                                  | 0.01                                             | 1                                                | μΑ     |

|                   | Gain                                            | $R_L = 4 \Omega$                                                                                   |                         | $\frac{38 \text{ k}\Omega}{\text{R}_{\text{I}}}$ | $\frac{40 \text{ k}\Omega}{\text{R}_{\text{I}}}$ | $\frac{42 \text{ k}\Omega}{\text{R}_{\text{I}}}$ | V/V    |

|                   | Resistance from shutdown to GND                 |                                                                                                    |                         |                                                  | 100                                              |                                                  | kΩ     |

# 6.6 Operating Characteristics

$T_{\Delta} = 25^{\circ}C$ , Gain = 1 V/V

|                  | PARAMETER                            | Т                                              | EST CONDITION                                    | NS                      | MIN | TYP    | MAX | UNIT          |

|------------------|--------------------------------------|------------------------------------------------|--------------------------------------------------|-------------------------|-----|--------|-----|---------------|

|                  |                                      |                                                |                                                  | V <sub>DD</sub> = 5 V   |     | 2.45   |     |               |

|                  |                                      | THD + N = 1%, f = 1 i                          | THD + N = 1%, f = 1 kHz, $R_L$ = 3 $\Omega$      |                         |     | 1.22   |     |               |

|                  |                                      |                                                |                                                  |                         |     | 0.49   |     |               |

|                  |                                      |                                                |                                                  | V <sub>DD</sub> = 5 V   |     | 2.22   |     |               |

| Po               | Output power                         | THD + N = 1%, f = 1 i                          | kHz, $R_L = 4 \Omega$                            | V <sub>DD</sub> = 3.6 V |     | 1.1    |     | W             |

|                  |                                      |                                                |                                                  | V <sub>DD</sub> = 2.5 V |     | 0.47   |     |               |

|                  |                                      |                                                |                                                  | V <sub>DD</sub> = 5 V   |     | 1.36   |     |               |

|                  |                                      | THD + N = 1%, f = 1 i                          | kHz, $R_L = 8 \Omega$                            | V <sub>DD</sub> = 3.6 V |     | 0.72   |     |               |

|                  |                                      |                                                |                                                  | V <sub>DD</sub> = 2.5 V |     | 0.33   |     |               |

|                  |                                      |                                                | P <sub>O</sub> = 2 W, V <sub>DD</sub>            | = 5 V                   |     | 0.045% |     |               |

|                  |                                      | $f=1~kHz,~R_L=3~\Omega$                        | $P_O = 1 W, V_{DD}$                              | = 3.6 V                 |     | 0.05%  |     |               |

|                  |                                      |                                                | P <sub>O</sub> = 300 mW, V <sub>DD</sub> = 2.5 V |                         |     | 0.06%  |     |               |

|                  |                                      |                                                | $P_0 = 1.8 \text{ W}, V_0$                       | <sub>DD</sub> = 5 V     |     | 0.03%  |     |               |

| THD+N            | Total harmonic distortion plus noise | $f = 1 \text{ kHz}, R_L = 4 \Omega$            | P <sub>O</sub> = 0.7 W, V <sub>DD</sub> = 3.6 V  |                         |     | 0.03%  |     |               |

|                  |                                      |                                                | $P_0 = 300 \text{ mW},$                          | V <sub>DD</sub> = 2.5 V |     | 0.04%  |     |               |

|                  |                                      |                                                | $P_O = 1 W, V_{DD}$                              | = 5 V                   |     | 0.02%  |     |               |

|                  |                                      | $f = 1 \text{ kHz}, R_L = 8 \Omega$            | $P_0 = 0.5 \text{ W}, V_0$                       | <sub>DD</sub> = 3.6 V   |     | 0.02%  |     |               |

|                  |                                      |                                                | $P_0 = 200 \text{ mW},$                          | V <sub>DD</sub> = 2.5 V |     | 0.03%  |     |               |

| l.               | Cumply simple rejection setio        | V <sub>DD</sub> = 3.6 V, Inputs A0             | C-grounded with                                  | f = 217 Hz              |     | -80    |     | dB            |

| k <sub>SVR</sub> | Supply ripple rejection ratio        | $C_I = 2 \mu F$ , $V_{RIPPLE} = 2$             | 00 mV <sub>pp</sub>                              | f = 20 Hz to 20 kHz     |     | -70    |     | uБ            |

| SNR              | Signal-to-noise ratio                | V <sub>DD</sub> = 5 V, P <sub>O</sub> = 2 W,   | $R_L = 4 \Omega$                                 |                         |     | 105    |     | dB            |

| .,               | Outrot valta as asias                | V <sub>DD</sub> = 3.6 V, f = 20 Hz             | z to 20 kHz,                                     | No weighting            |     | 15     |     |               |

| V <sub>n</sub>   | Output voltage noise                 | Inputs AC-grounded v                           | with $C_1 = 2 \mu F$                             | A weighting             |     | 12     |     | $\mu V_{RMS}$ |

| CMRR             | Common mode rejection ratio          | $V_{DD} = 3.6 \text{ V}, V_{IC} = 1 \text{ V}$ | / <sub>pp</sub>                                  | f = 217 Hz              |     | -65    |     | dB            |

| Z <sub>I</sub>   | Input impedance                      |                                                |                                                  |                         | 38  | 40     | 44  | kΩ            |

|                  | Start up time from abutdows          | V <sub>DD</sub> = 3.6 V, No C <sub>BYP</sub>   | ASS                                              | _                       |     | 4      |     | μs            |

|                  | Start-up time from shutdown          | $V_{DD} = 3.6 \text{ V}, C_{BYPASS}$           | = 0.1 µF                                         |                         |     | 27     |     | ms            |

# 6.7 Dissipation Ratings

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING              | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------|-----------------------|-----------------------|

|         | POWER RATING          | FACTOR <sup>(1)</sup> | POWER RATING          | POWER RATING          |

| DGN     | 2.13 W                | 17.1 mW/°C            | 1.36 W                | 1.11 W                |

<sup>(1)</sup> Derating factor based on High-k board layout.

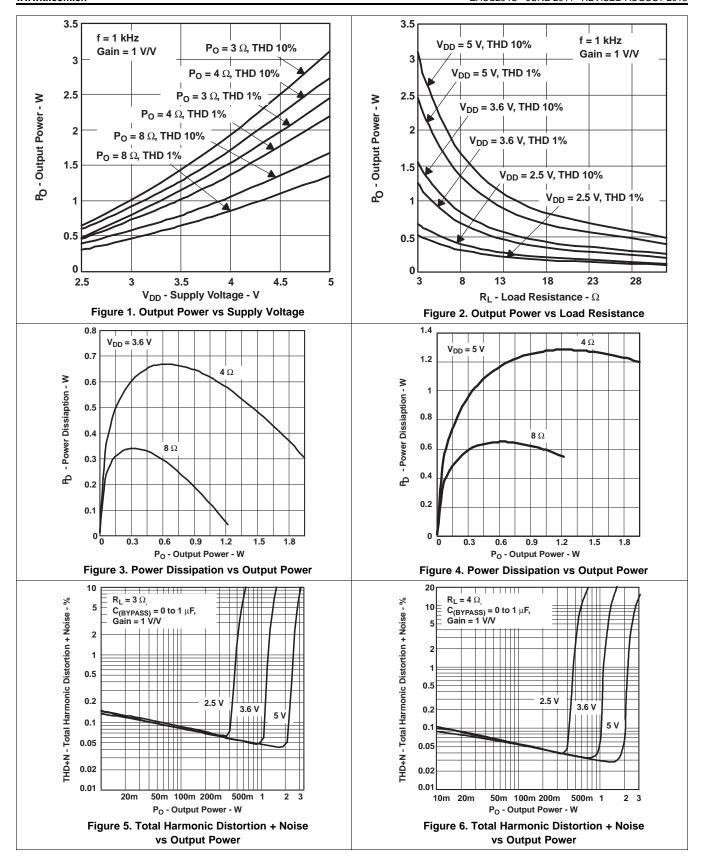

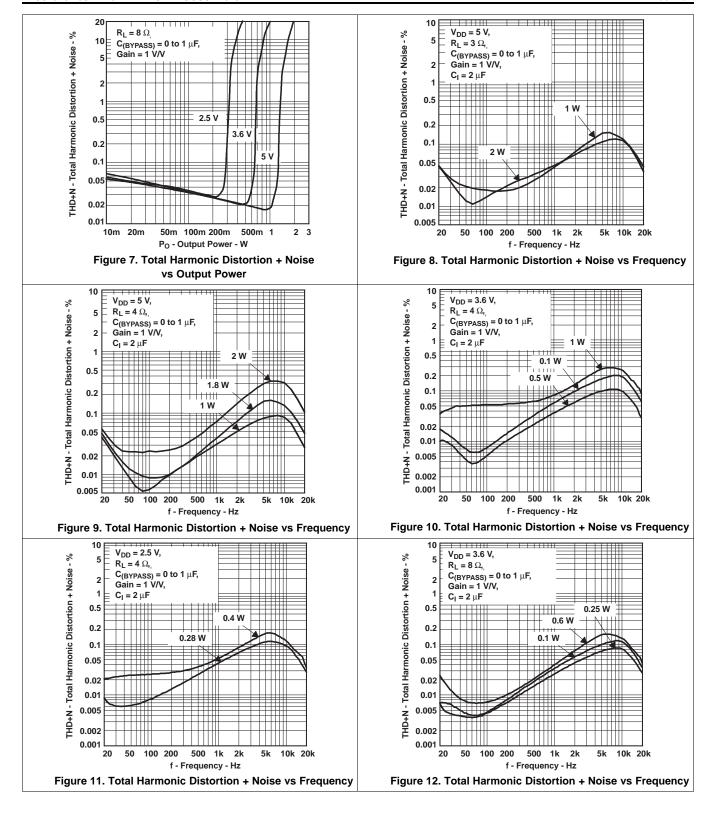

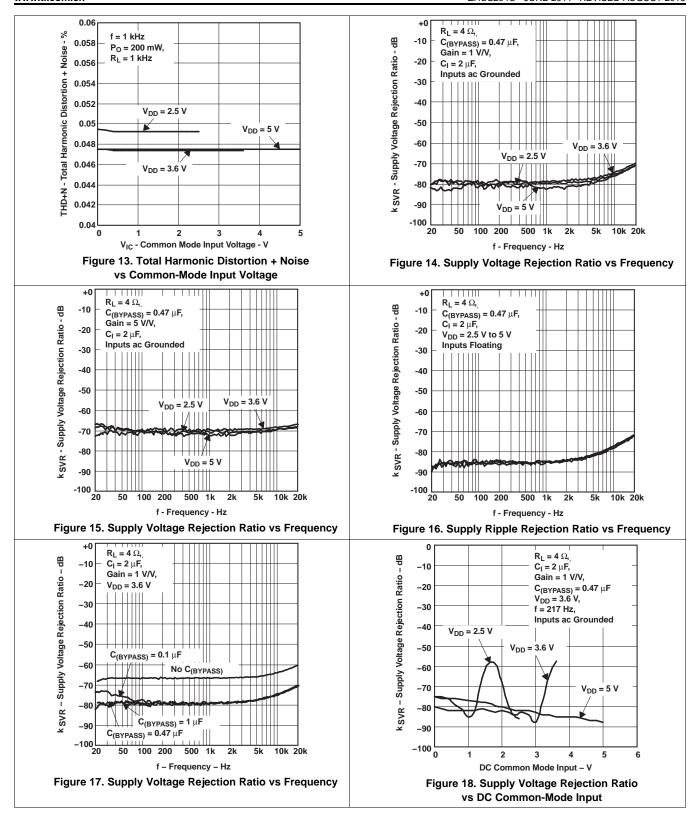

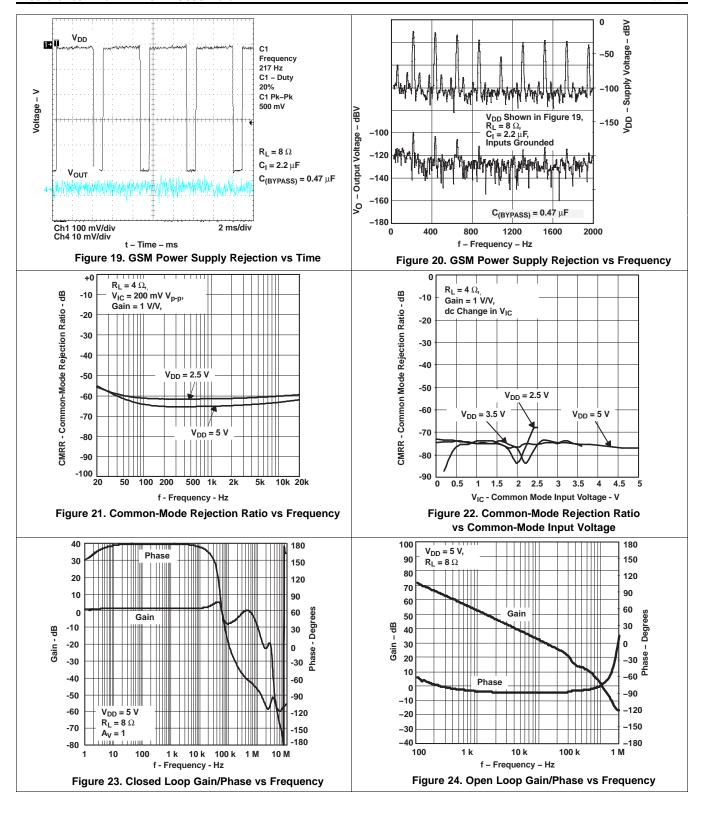

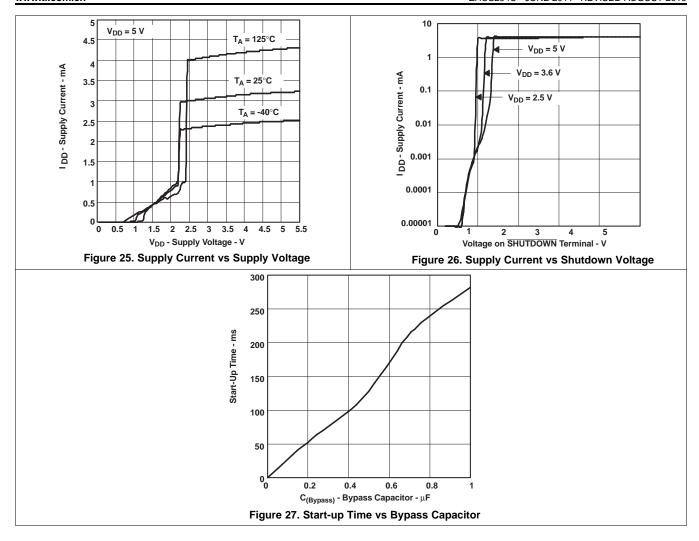

# 6.8 Typical Characteristics

# Table 1. Table of Graphs

|                                   |                              | FIGURE                                              |

|-----------------------------------|------------------------------|-----------------------------------------------------|

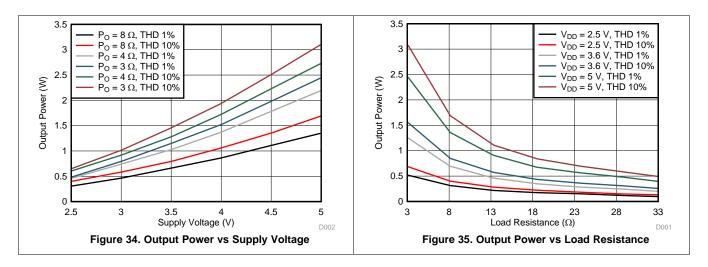

| Outrot = source                   | vs Supply voltage            | Figure 1                                            |

| Output power                      | vs Load resistance           | Figure 2                                            |

| Power dissipation                 | vs Output power              | Figure 3, Figure 4                                  |

|                                   | vs Output power              | Figure 5, Figure 6, Figure 7                        |

| Total harmonic distortion + noise | vs Frequency                 | Figure 8, Figure 9, Figure 10, Figure 11, Figure 12 |

|                                   | vs Common-mode input voltage | Figure 13                                           |

| Supply voltage rejection ratio    | vs Frequency                 | Figure 14, Figure 15, Figure 16, Figure 17          |

| Supply voltage rejection ratio    | vs Common-mode input voltage | Figure 18                                           |

| GSM Power supply rejection        | vs Time                      | Figure 19                                           |

| GSM Power supply rejection        | vs Frequency                 | Figure 20                                           |

| Commence and a main estimated     | vs Frequency                 | Figure 21                                           |

| Common-mode rejection ratio       | vs Common-mode input voltage | Figure 22                                           |

| Closed loop gain/phase            | vs Frequency                 | Figure 23                                           |

| Open loop gain/phase              | vs Frequency                 | Figure 24                                           |

| Cupply ourrent                    | vs Supply voltage            | Figure 25                                           |

| Supply current                    | vs Shutdown voltage          | Figure 26                                           |

| Start-up time                     | vs Bypass capacitor          | Figure 27                                           |

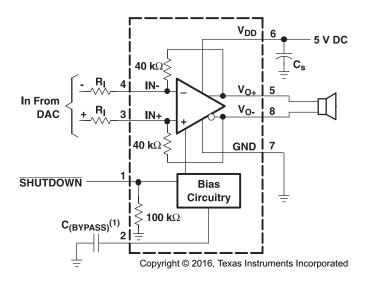

# 7 Detailed Description

#### 7.1 Overview

The TPA6211A1-Q1 device is a fully differential amplifier with differential inputs and outputs. The fully differential amplifier consists of a differential amplifier and a common-mode amplifier. The differential amplifier ensures that the amplifier outputs a differential voltage that is equal to the differential input times the gain. The common-mode feedback ensures that the common-mode voltage at the output is biased around  $V_{DD}$  / 2 regardless of the common-mode voltage at the input.

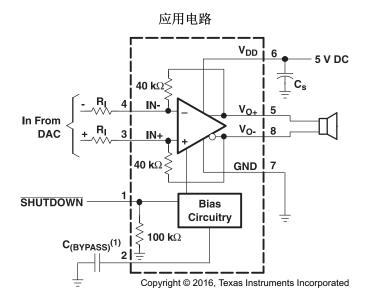

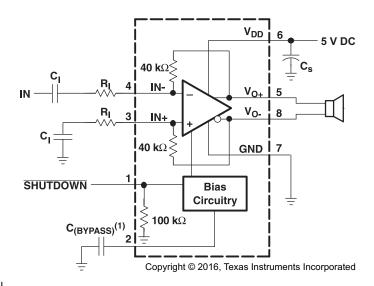

## 7.2 Functional Block Diagram

(1) C<sub>(BYPASS)</sub> is optional

#### 7.3 Feature Description

#### 7.3.1 Advantages of Fully Differential Amplifiers

Input coupling capacitors are not required. A fully differential amplifier with good CMRR, such as the TPA6211A1-Q1 device, allows the inputs to be biased at voltage other than mid-supply. For example, if a DAC has a lower mid-supply voltage than that of the TPA6211A1-Q1 device, the common-mode feedback circuit compensates, and the outputs are still biased at the mid-supply point of the TPA6211A1-Q1 device. The inputs of the TPA6211A1-Q1 device can be biased from 0.5 V to  $V_{DD}-0.8$  V. If the inputs are biased outside of that range, input coupling capacitors are required.

A Mid-supply bypass capacitor,  $C_{BYPASS}$ , is not required. The fully differential amplifier does not require a bypass capacitor. Any shift in the mid-supply voltage affects both positive and negative channels equally, thus canceling at the differential output. Removing the bypass capacitor slightly worsens power supply rejection ratio ( $k_{SVR}$ ), but a slight decrease of  $k_{SVR}$  can be acceptable when an additional component can be eliminated (see Figure 17).

The RF-immunity is improved. A fully differential amplifier cancels the noise from RF disturbances much better than the typical audio amplifier.

## 7.3.2 Fully Differential Amplifier Efficiency and Thermal Information

Class-AB amplifiers are inefficient, primarily because of voltage drop across the output-stage transistors. The two components of this internal voltage drop are the headroom or DC voltage drop that varies inversely to output power, and the sinewave nature of the output. The total voltage drop can be calculated by subtracting the RMS value of the output voltage from  $V_{DD}$ . The internal voltage drop multiplied by the average value of the supply current,  $I_{DD}$ (avg), determines the internal power dissipation of the amplifier.

#### **Feature Description (continued)**

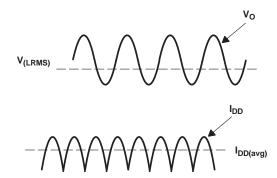

An easy-to-use equation to calculate efficiency starts out as being equal to the ratio of power from the power supply to the power delivered to the load. To accurately calculate the RMS and average values of power in the load and in the amplifier, the current and voltage waveform shapes must first be understood (see Figure 28).

Figure 28. Voltage and Current Waveforms for BTL Amplifiers

Although the voltages and currents for SE and BTL are sinusoidal in the load, currents from the supply are different between SE and BTL configurations. In an SE application the current waveform is a half-wave rectified shape, whereas in BTL the current waveform is a full-wave rectified waveform. This means RMS conversion factors are different. Keep in mind that for most of the waveform both the push and pull transistors are not on at the same time, which supports the fact that each amplifier in the BTL device only draws current from the supply for half the waveform. Equation 1 to Equation 10 are the basis for calculating amplifier efficiency.

$$\eta_{BTL} = \frac{P_L}{P_{SUP}}$$

where

- $\eta_{BTL}$  is the efficiency of a BTL amplifier

- P<sub>L</sub> is the power delivered to load

$P_L$  is calculated with Equation 2, and  $V_{LRMS}$  is calculated with Equation 3.

$$P_L = \frac{V_{LRMS}^2}{R_i}$$

where

V<sub>LRMS</sub> = RMS voltage on BTL load

$$V_{LRMS} = \frac{V_{P}}{\sqrt{2}}$$

where

Therefore, P<sub>I</sub> can be given as Equation 4.

$$P_{L} = \frac{V_{P}^{2}}{2 \times R_{L}} \tag{4}$$

P<sub>SUP</sub> is calculated with Equation 5.

$$P_{SUP} = V_{DD} \times I_{DD}avg$$

where

- V<sub>DD</sub> is power supply voltge

- I<sub>DD</sub>avg is average current drawn from the power supply

(5)

#### **Feature Description (continued)**

I<sub>DD</sub>avg is calculated with Equation 6.

$$I_{DD}avg = \frac{1}{\pi} \int_0^{\pi} \frac{V_P}{R_L} \times \sin(t) \times dt = -\frac{1}{\pi} \times \frac{V_P}{R_L} \times \cos(t)_0^{\pi} = \frac{2 \times V_P}{\pi \times R_L}$$

(6)

Therefore, P<sub>SUP</sub> can be given as Equation 7.

$$P_{SUP} = \frac{2 \times V_{DD} \times V_{P}}{\pi \times R_{L}}$$

(7)

Substituting for  $P_L$  and  $P_{SUP}$ , Equation 1 becomes Equation 8

$$\eta_{BTL} = \frac{\frac{V_P^2}{2 \times R_L}}{\frac{2 \times V_{DD} \times V_P}{\pi \times R_L}} = \frac{\pi \times V_P}{4 \times V_{DD}}$$

(8)

V<sub>P</sub> is calculated with Equation 9.

$$V_{P} = \sqrt{2 \times P_{L} \times R_{L}} \tag{9}$$

And substituting for  $V_P$ ,  $\eta_{BTL}$  can be calculated with Equation 10

$$\eta_{BTL} = \frac{\pi \sqrt{2 \times P_L \times R_L}}{4 \times V_{DD}}$$

(10)

A simple formula for calculating the maximum power dissipated  $(P_{Dmax})$  can be used for a differential output application:

$$P_{Dmax} = \frac{2V_{DD}^2}{\pi^2 R_L} \tag{11}$$

Table 2. Efficiency and Maximum Ambient Temperature vs Output Power

| OUTPUT POWER       | EFFICIENCY | INTERNAL DISSIPATION | POWER FROM SUPPLY | MAX AMBIENT TEMPERATURE                                      |

|--------------------|------------|----------------------|-------------------|--------------------------------------------------------------|

| 5-V, 3-Ω SYSTEMS   |            |                      |                   |                                                              |

| 0.5 W              | 27.2%      | 1.34 W               | 1.84 W            | 54°C                                                         |

| 1 W                | 38.4%      | 1.6 W                | 2.6 W             | 35°C                                                         |

| 2.45 W             | 60.2%      | 1.62 W               | 4.07 W            | 34°C                                                         |

| 3.1 W              | 67.7%      | 1.48 W               | 4.58 W            | 44°C                                                         |

| 5-V, 4-Ω BTL SYSTE | EMS        |                      |                   |                                                              |

| 0.5 W              | 31.4%      | 1.09 W               | 1.59 W            | 72°C                                                         |

| 1 W                | 44.4%      | 1.25 W               | 2.25 W            | 60°C                                                         |

| 2 W                | 62.8%      | 1.18 W               | 3.18 W            | 65°C                                                         |

| 2.8 W              | 74.3%      | 0.97 W               | 3.77 W            | 80°C                                                         |

| 5-V, 8-Ω SYSTEMS   |            |                      |                   |                                                              |

| 0.5 W              | 44.4%      | 0.625 W              | 1.13 W            | 105°C (limited by maximum ambient temperature specification) |

| 1 W                | 62.8%      | 0.592 W              | 1.6 W             | 105°C (limited by maximum ambient temperature specification) |

| 1.36 W             | 73.3%      | 0.496 W              | 1.86 W            | 105°C (limited by maximum ambient temperature specification) |

| 1.7 W              | 81.9%      | 0.375 W              | 2.08 W            | 105°C (limited by maximum ambient temperature specification) |

Equation 10 is used to calculate efficiencies for four different output power levels, see Table 2. The efficiency of the amplifier is quite low for lower power levels and rises sharply as power to the load is increased resulting in a nearly flat internal power dissipation over the normal operating range. The internal dissipation at full output power is less than in the half power range. Calculating the efficiency for a specific system is the key to proper power supply design. For a 2.8-W audio system with 4- $\Omega$  loads and a 5-V supply, the maximum draw on the power supply is almost 3.8 W.

A final point to remember about Class-AB amplifiers is how to manipulate the terms in the efficiency equation to the utmost advantage when possible. In Equation 10,  $V_{DD}$  is in the denominator. This indicates that as  $V_{DD}$  goes down, efficiency goes up.

The maximum ambient temperature depends on the heat sinking ability of the PCB system. Given  $R_{\theta JA}$  (junction-to-ambient thermal resistance), the maximum allowable junction temperature, and the internal dissipation at 1-W output power with a 4-Ohm load, the maximum ambient temperature can be calculated with Equation 12. The maximum recommended junction temperature for the TPA6211A1-Q1 device is 150°C.

$$T_A(Max) = T_J(Max) - R_{\theta JA} \times P_D = 150 - 71.7 \times 1.25 = 60^{\circ}C$$

(12)

Equation 12 shows that the maximum ambient temperature is 60°C at 1-W output power and 4-Ohm load with a 5-V supply.

Table 2 shows that the thermal performance must be considered when using a Class-AB amplifier to keep junction temperatures in the specified range. The TPA6211A1-Q1 device is designed with thermal protection that turns the device off when the junction temperature surpasses 150°C to prevent damage to the IC. In addition, using speakers with an impedance higher than 4  $\Omega$  dramatically increases the thermal performance by reducing the output current.

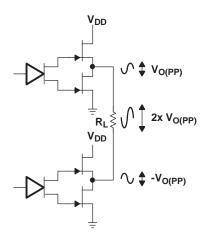

#### 7.3.3 Differential Output Versus Single-Ended Output

Figure 29 shows a Class-AB audio power amplifier (APA) in a fully differential configuration. The TPA6211A1-Q1 amplifier has differential outputs driving both ends of the load. One of several potential benefits to this configuration is power to the load. The differential drive to the speaker means that as one side is slewing up, the other side is slewing down, and vice versa. This in effect doubles the voltage swing on the load as compared to a ground-referenced load. Plugging  $2 \times V_{O(PP)}$  into the power equation (Equation 13) yields four-times the output power (as the voltage is squared) from the same supply rail and load impedance (see Equation 15 and Equation 16).

$$V_{(rms)} = \frac{V_{O(PP)}}{2\sqrt{2}}$$

$$Power = \frac{V_{(rms)}^{2}}{R_{L}}$$

(13)

$$Power_{(S-E)} = \frac{V_{(rms)}^2}{R_L} = \frac{\left(\frac{V_{O(PP)}}{2\sqrt{2}}\right)^2}{R_L} = \frac{V_{O(PP)}^2}{8R_L}$$

(14)

$$Power_{(Diff)} = \frac{V_{(rms)}^{2}}{R_{L}} = \frac{\left(\frac{2 \times V_{O(PP)}}{2\sqrt{2}}\right)^{2}}{R_{L}} = \frac{V_{O(PP)}^{2}}{2R_{L}}$$

(15)

$$Power_{(Diff)} = 4 \times Power_{(S-E)}$$

(16)

Figure 29. Differential Output Configuration

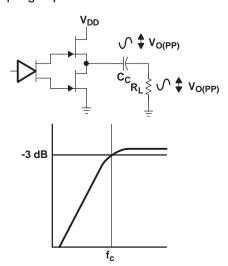

In a typical automotive application operating at 5 V, bridging raises the power into an  $8-\Omega$  speaker from a singled-ended (SE, ground reference) limit of 390 mW to 1.56 W. This is a 6-dB improvement in sound power, or loudness of the sound. In addition to increased power, there are frequency-response concerns. Consider the single-supply SE configuration shown in Figure 30. A coupling capacitor ( $C_C$ ) is required to block the DC-offset voltage from the load. This capacitor can be quite large (approximately 33  $\mu$ F to 1000  $\mu$ F) so it tends to be expensive, heavy, occupy valuable PCB area, and have the additional drawback of limiting low-frequency performance. This frequency-limiting effect is due to the high-pass filter network created with the speaker impedance and the coupling capacitance. This is calculated with Equation 17.

$$f_{c} = \frac{1}{2\pi R_{L} C_{C}} \tag{17}$$

For example, a  $68-\mu F$  capacitor with an  $8-\Omega$  speaker would attenuate low frequencies below 293 Hz. The BTL configuration cancels the DC offsets, which eliminates the need for the blocking capacitors. Low-frequency performance is then limited only by the input network and speaker response. Cost and PCB space are also minimized by eliminating the bulky coupling capacitor.

Figure 30. Single-Ended Output and Frequency Response

Increasing power to the load does carry a penalty of increased internal power dissipation. The increased dissipation is understandable considering that the BTL configuration produces four-times the output power of the SE configuration.

## 7.4 Device Functional Modes

The TPA6211A1-Q1 device can be put in shutdown mode when asserting SHUTDOWN pin to a logic LOW. While in shutdown mode, the device output stage is turned off and set into high impedance, making the current consumption very low. The device exits shutdown mode when a HIGH logic level is applied to SHUTDOWN pin.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The TPA6211A1-Q1 is a fully-differential amplifier designed to drive a speaker with at least 3- $\Omega$  impedance while consuming only 20-mm<sup>2</sup> total printed-circuit board (PCB) area in most applications.

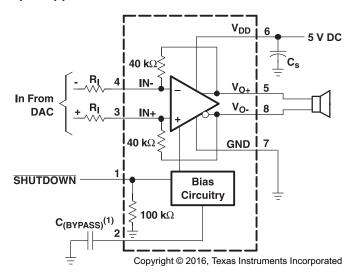

## 8.2 Typical Applications

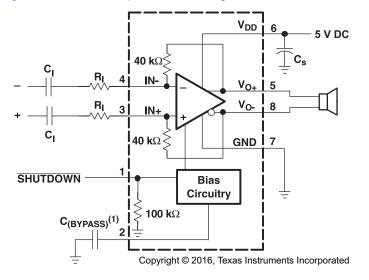

Figure 31 shows a typical application circuit for the TPA6211A1-Q1 with a speaker, input resistors, and supporting power supply decoupling capacitors.

#### 8.2.1 Typical Differential Input Application

(1) C<sub>(BYPASS)</sub> is optional

Figure 31. Typical Differential Input Application Schematic

Typical values are shown in Table 3.

**Table 3. Typical Component Values**

| COMPONENT                          | VALUE   |

|------------------------------------|---------|

| R <sub>I</sub>                     | 40 kΩ   |

| C <sub>BYPASS</sub> <sup>(1)</sup> | 0.22 μF |

| C <sub>S</sub>                     | 1 μF    |

| C <sub>I</sub>                     | 0.22 μF |

(1) C<sub>BYPASS</sub> is optional.

#### 8.2.1.1 Design Requirements

For this design example, use the parameters listed in Table 4 as the input parameters.

| Table 4. | Design | <b>Parameters</b> |

|----------|--------|-------------------|

|----------|--------|-------------------|

| PARAMETER            | EXAMPLE VALUE    |

|----------------------|------------------|

| Power supply voltage | 2.5 V to 5.5 V   |

| Current              | 4 mA to 5 mA     |

| Shutdown             | High > 1.55 V    |

| Shuldown             | Low < 0.5 V      |

| Speaker              | 3 Ω, 4 Ω, or 8 Ω |

#### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Resistors (R<sub>I</sub>)

The input resistor (R<sub>1</sub>) can be selected to set the gain of the amplifier according to Equation 18.

$$Gain = \frac{R_F}{R_I} \tag{18}$$

The internal feedback resistors ( $R_E$ ) are trimmed to 40 k $\Omega$ .

Resistor matching is very important in fully differential amplifiers. The balance of the output on the reference voltage depends on matched ratios of the resistors. CMRR, PSRR, and the cancellation of the second harmonic distortion diminishes if resistor mismatch occurs. Therefore, TI recommends 1%-tolerance resistors or better to optimize performance.

#### 8.2.1.2.2 Bypass Capacitor (CBYPASS) and Start-Up Time

The internal voltage divider at the BYPASS pin of this device sets a mid-supply voltage for internal references and sets the output common mode voltage to  $V_{DD}$  / 2. Adding a capacitor filters any noise into this pin, increasing  $k_{SVR}$ .  $C_{BYPASS}$  also determines the rise time of  $V_{O+}$  and  $V_{O-}$  when the device exits shutdown. The larger the capacitor, the slower the rise time.

## 8.2.1.2.3 Input Capacitor (C<sub>I</sub>)

The TPA6211A1-Q1 device does not require input coupling capacitors when driven by a differential input source biased from 0.5 V to  $V_{DD}$  – 0.8 V. Use 1% tolerance or better gain-setting resistors if not using input coupling capacitors.

In the single-ended input application, an input capacitor ( $C_I$ ) is required to allow the amplifier to bias the input signal to the proper DC level. In this case,  $C_I$  and  $R_I$  form a high-pass filter with the corner frequency defined in Equation 19.

$$f_{c} = \frac{1}{2\pi R_{l}C_{l}} \tag{19}$$

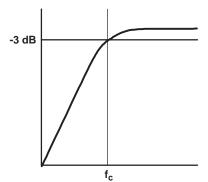

Figure 32. Input Filter Cutoff Frequency

The value of  $C_I$  is an important consideration, as it directly affects the bass (low frequency) performance of the circuit. Consider the example where  $R_I$  is 10 k $\Omega$  and the specification calls for a flat bass response down to 100 Hz. Equation 19 is reconfigured as Equation 20.

$$C_{l} = \frac{1}{2\pi R_{l} f_{c}} \tag{20}$$

In this example,  $C_I$  is 0.16  $\mu F$ , so the likely choice ranges from 0.22  $\mu F$  to 0.47  $\mu F$ . TI recommends the use of ceramic capacitors because they are the best choice in preventing leakage current. When polarized capacitors are used, the positive side of the capacitor faces the amplifier input in most applications. The input DC level is held at  $V_{DD}$  / 2, typically higher than the source DC level. Confirming the capacitor polarity in the application is important.

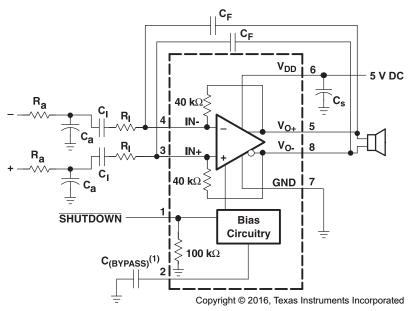

#### 8.2.1.2.4 Band-Pass Filter (R<sub>I</sub>, C<sub>I</sub>, and C<sub>F</sub>)

Having signal filtering beyond the one-pole high-pass filter formed by the combination of  $C_1$  and  $R_1$  can be desirable. A low-pass filter can be added by placing a capacitor ( $C_F$ ) between the inputs and outputs, forming a band-pass filter.

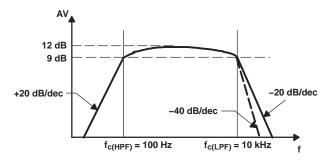

An example of when this technique might be used would be in an application where the desirable pass-band range is between 100 Hz and 10 kHz, with a gain of 4 V/V. Equation 21 to Equation 28 allow the proper values of  $C_F$  and  $C_I$  to be determined.

#### 8.2.1.2.4.1 Step 1: Low-Pass Filter

$$f_{c(LPF)} = \frac{1}{2\pi R_F C_F} \tag{21}$$

$$f_{c(LPF)} = \frac{1}{2\pi 40 \, k\Omega \, C_F} \tag{22}$$

Therefore.

$$C_{F} = \frac{1}{2\pi 40 \text{ k}\Omega \text{ f}_{c(LPF)}}$$

(23)

Substituting 10 kHz for f<sub>c(I PF)</sub> and solving for C<sub>F</sub>:

$$C_F = 398 \text{ pF}$$

(24)

#### 8.2.1.2.4.2 Step 2: High-Pass Filter

$$f_{c(HPF)} = \frac{1}{2\pi R_I C_I} \tag{25}$$

Because the application in this case requires a gain of 4 V/V, R<sub>1</sub> must be set to 10 kΩ.

Substituting R<sub>1</sub> into Equation 25.

$$f_{c(HPF)} = \frac{1}{2\pi 10 \text{ k}\Omega \text{ C}_{I}}$$

(26)

Therefore,

$$C_{I} = \frac{1}{2\pi 10 \text{ k}\Omega f_{c(HPF)}}$$

(27)

Substituting 100 Hz for f<sub>c(HPF)</sub> and solving for C<sub>I</sub>:

$$C_1 = 0.16 \,\mu\text{F}$$

(28)

At this point, a first-order band-pass filter has been created with the low-frequency cutoff set to 100 Hz and the high-frequency cutoff set to 10 kHz.

The process can be taken a step further by creating a second-order high-pass filter. This is accomplished by placing a resistor  $(R_a)$  and capacitor  $(C_a)$  in the input path.  $R_a$  must be at least 10 times smaller than  $R_l$ ; otherwise its value has a noticeable effect on the gain, as  $R_a$  and  $R_l$  are in series.

### 8.2.1.2.4.3 Step 3: Additional Low-Pass Filter

$R_a$  must be at least ten-times smaller than  $R_I$ . Set  $R_a = 1 \text{ k}\Omega$

$$f_{c(LPF)} = \frac{1}{2\pi R_a C_a} \tag{29}$$

Therefore,

$$C_{a} = \frac{1}{2\pi \, 1 \text{k}\Omega \, f_{c(\text{LPF})}} \tag{30}$$

Substituting 10 kHz for f<sub>c(LPF)</sub> and solving for C<sub>a</sub>:

$$C_a = 160 \text{ pF} \tag{31}$$

Figure 33 is a bode plot for the band-pass filter in the previous example. Figure 38 shows how to configure the TPA6211A1-Q1 device as a band-pass filter.

Figure 33. Bode Plot

#### 8.2.1.2.5 Decoupling Capacitor (C<sub>S</sub>)

The TPA6211A1-Q1 device is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD) is as low as possible. Power-supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F to 1  $\mu$ F, placed as close as possible to the device  $V_{DD}$  lead works best. For filtering lower frequency noise signals, a 10- $\mu$ F or greater capacitor placed near the audio power amplifier also helps, but is not required in most applications because of the high PSRR of this device.

#### 8.2.1.2.6 Using Low-ESR Capacitors

Low-ESR capacitors are recommended throughout this applications section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance the more the real capacitor behaves like an ideal capacitor.

#### 8.2.1.3 Application Curves

## 8.2.2 Other Application Circuits

Figure 36, Figure 37, and Figure 38 show example circuits using the TPA6211A1-Q1 device.

(1) C<sub>(BYPASS)</sub> is optional

Figure 36. Differential Input Application Schematic Optimized With Input Capacitors

(1)  $C_{(BYPASS)}$  is optional

Figure 37. Single-Ended Input Application Schematic

(1) C<sub>(BYPASS)</sub> is optional

Figure 38. Differential Input Application Schematic With Input Bandpass Filter

# 9 Power Supply Recommendations

The TPA6211A1-Q1 device is designed to operate from an input voltage supply range between 2.5 V and 5.5 V. Therefore, the output voltage range of power supply must be within this range and well regulated. The current capability of upper power should not exceed the maximum current limit of the power switch.

#### 9.1 Power Supply Decoupling Capacitor

The TPA6211A1-Q1 device requires adequate power supply decoupling to ensure a high efficiency operation with low total harmonic distortion (THD). Place a low equivalent series resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F, as close as possible of the  $V_{DD}$  pin. This choice of capacitor and placement helps with higher frequency transients, spikes, or digital hash on the line. TI recommends placing a 2.2- $\mu$ F to 10- $\mu$ F capacitor on the  $V_{DD}$  supply trace. This larger capacitor acts as a charge reservoir, providing energy faster than the board supply, thus helping to prevent any droop in the supply voltage.

# 10 Layout

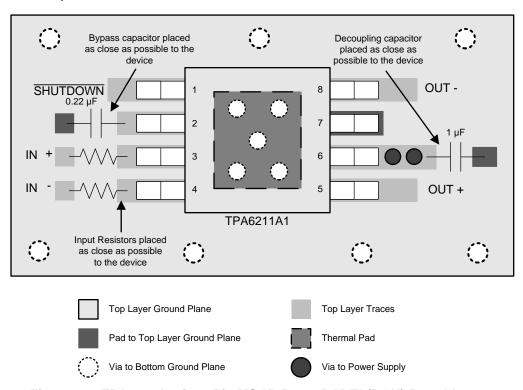

#### 10.1 Layout Guidelines

Place all the external components close to the TPA6211A1-Q1 device. The input resistors need to be close to the device input pins so noise does not couple on the high impedance nodes between the input resistors and the input amplifier of the device. Placing the decoupling capacitors,  $C_S$  and  $C_{BYPASS}$ , close to the TPA6211A1-Q1 device is important for the efficiency of the amplifier. Any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency.

### 10.2 Layout Example

Figure 39. TPA6211A1-Q1 8-Pin MSOP-PowerPAD™ (DGN) Board Layout

#### 11 器件和文档支持

#### 11.1 接收文档更新通知

如需接收文档更新通知,请访问 www.ti.com.cn 网站上的器件产品文件夹。点击右上角的提醒我 (Alert me) 注册后,即可每周定期收到已更改的产品信息。有关更改的详细信息,请查阅已修订文档中包含的修订历史记录。

#### 11.2 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.3 商标

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 11.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

# 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

#### 重要声明

德州仪器(TI) 及其下属子公司有权根据 JESD46 最新标准, 对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权根据 JESD48 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息, 并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。仅在 TI 保证的范围内,且 TI 认为 有必要时才会使用测试或其它质量控制技术。除非适用法律做出了硬性规定,否则没有必要对每种组件的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应 用相关的风险,客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予 的直接或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服 务的许可、授权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它 知识产权方面的许可。

对于 TI 的产品手册或数据表中 TI 信息的重要部分,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况 下才允许进行 复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。

在转售 TI 组件或服务时,如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分,则会失去相关 TI 组件 或服务的所有明示或暗示授权,且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。

客户认可并同意,尽管任何应用相关信息或支持仍可能由 TI 提供,但他们将独力负责满足与其产品及在其应用中使用 TI 产品 相关的所有法律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,可预见 故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因 在此类安全关键应用中使用任何 TI 组件而对 TI 及其代理造成的任何损失。

在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特 有的可满足适用的功能安全性标准和要求的终端产品解决方案。尽管如此,此类组件仍然服从这些条款。

TI 组件未获得用于 FDA Class III(或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使 用的特别协议。

只有那些 TI 特别注明属于军用等级或"增强型塑料"的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同 意,对并非指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独 力负责满足与此类使用相关的所有法律和法规要求。

TI 己明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。在任何情况下,因使用非指定产品而无法达到 ISO/TS16949 要求,TI不承担任何责任。

|               | 产品                                 |              | 应用                       |

|---------------|------------------------------------|--------------|--------------------------|

| 数字音频          | www.ti.com.cn/audio                | 通信与电信        | www.ti.com.cn/telecom    |

| 放大器和线性器件      | www.ti.com.cn/amplifiers           | 计算机及周边       | www.ti.com.cn/computer   |

| 数据转换器         | www.ti.com.cn/dataconverters       | 消费电子         | www.ti.com/consumer-apps |

| DLP® 产品       | www.dlp.com                        | 能源           | www.ti.com/energy        |

| DSP - 数字信号处理器 | www.ti.com.cn/dsp                  | 工业应用         | www.ti.com.cn/industrial |

| 时钟和计时器        | www.ti.com.cn/clockandtimers       | 医疗电子         | www.ti.com.cn/medical    |

| 接口            | www.ti.com.cn/interface            | 安防应用         | www.ti.com.cn/security   |

| 逻辑            | www.ti.com.cn/logic                | 汽车电子         | www.ti.com.cn/automotive |

| 电源管理          | www.ti.com.cn/power                | 视频和影像        | www.ti.com.cn/video      |

| 微控制器 (MCU)    | www.ti.com.cn/microcontrollers     |              |                          |

| RFID 系统       | www.ti.com.cn/rfidsys              |              |                          |

| OMAP应用处理器     | www.ti.com/omap                    |              |                          |

| 无线连通性         | www.ti.com.cn/wirelessconnectivity | 德州仪器在线技术支持社区 | www.deyisupport.com      |

|               |                                    |              |                          |

邮寄地址: 上海市浦东新区世纪大道1568 号,中建大厦32 楼邮政编码: 200122 Copyright © 2016, 德州仪器半导体技术(上海)有限公司

# PACKAGE OPTION ADDENDUM

7-Oct-2016

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type      | _       | Pins | _    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|-------------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |                   | Drawing |      | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| TPA6211A1TDGNRQ1 | ACTIVE | MSOP-<br>PowerPAD | DGN     | 8    | 2500 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 105   | 6211Q          | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

7-Oct-2016

#### OTHER QUALIFIED VERSIONS OF TPA6211A1-Q1:

www.ti.com

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

# PACKAGE MATERIALS INFORMATION

www.ti.com 3-Aug-2017

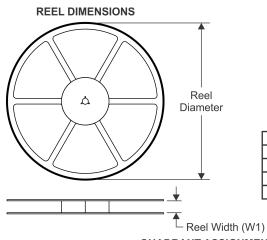

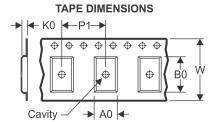

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type       | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPA6211A1TDGNRQ1 | MSOP-<br>Power<br>PAD | DGN                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com 3-Aug-2017

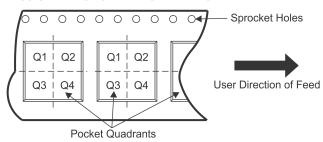

#### \*All dimensions are nominal

| Device           | Package Type  | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|---------------|-----------------|------|------|-------------|------------|-------------|

| TPA6211A1TDGNRQ1 | MSOP-PowerPAD | DGN             | 8    | 2500 | 346.0       | 346.0      | 29.0        |

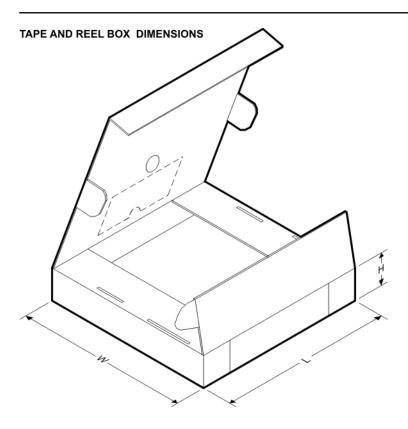

DGN (S-PDSO-G8)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

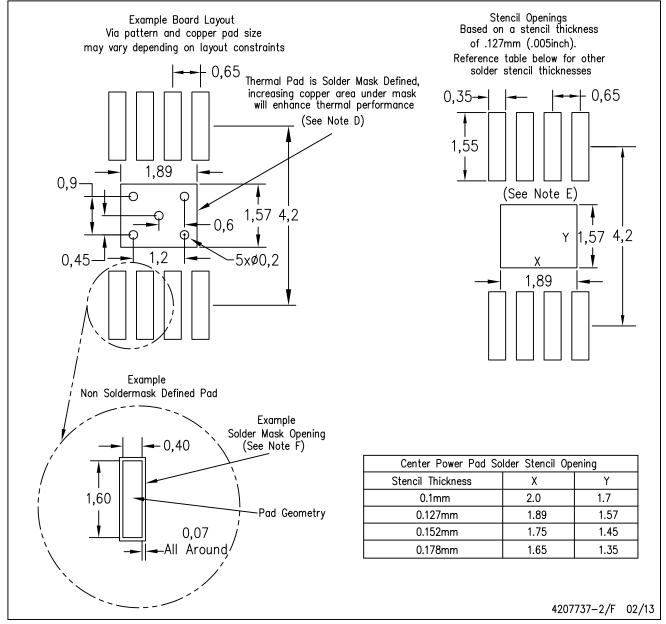

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-187 variation AA-T

#### PowerPAD is a trademark of Texas Instruments.

# DGN (S-PDSO-G8)

# PowerPAD™ PLASTIC SMALL OUTLINE

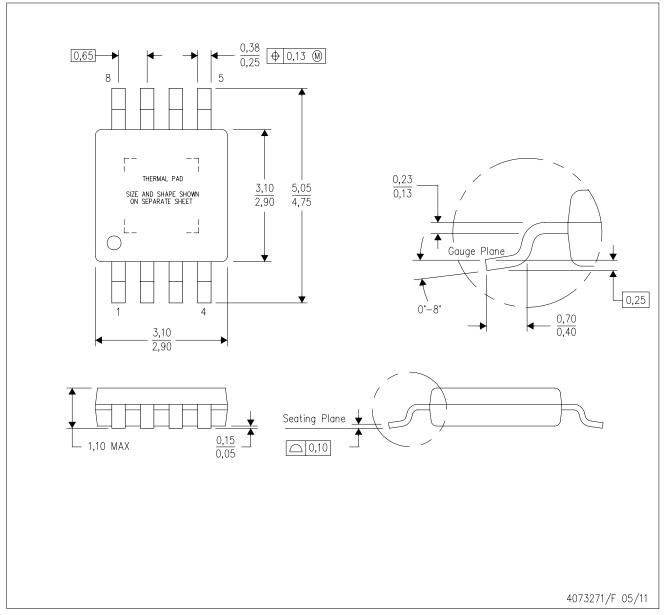

#### THERMAL INFORMATION

This PowerPAD  $^{\text{M}}$  package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206323-2/1 12/11

NOTE: All linear dimensions are in millimeters

# DGN (R-PDSO-G8)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments

#### 重要声明

德州仪器 (TI) 公司有权按照最新发布的 JESD46 对其半导体产品和服务进行纠正、增强、改进和其他修改,并不再按最新发布的 JESD48 提供任何产品和服务。买方在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。

TI 公布的半导体产品销售条款 (http://www.ti.com/sc/docs/stdterms.htm) 适用于 TI 己认证和批准上市的已封装集成电路产品的销售。另有其他条款可能适用于其他类型 TI 产品及服务的使用或销售。

复制 TI 数据表上 TI 信息的重要部分时,不得变更该等信息,且必须随附所有相关保证、条件、限制和通知,否则不得复制。TI 对该等复制文件不承担任何责任。第三方信息可能受到其它限制条件的制约。在转售 TI 产品或服务时,如果存在对产品或服务参数的虚假陈述,则会失去相关 TI 产品或服务的明示或暗示保证,且构成不公平的、欺诈性商业行为。TI 对此类虚假陈述不承担任何责任。

买方和在系统中整合 TI 产品的其他开发人员(总称"设计人员")理解并同意,设计人员在设计应用时应自行实施独立的分析、评价和判断,且应全权负责并确保应用的安全性,及设计人员的应用(包括应用中使用的所有 TI 产品)应符合所有适用的法律法规及其他相关要求。设计人员就自己设计的应用声明,其具备制订和实施下列保障措施所需的一切必要专业知识,能够(1)预见故障的危险后果,(2)监视故障及其后果,以及(3)降低可能导致危险的故障几率并采取适当措施。设计人员同意,在使用或分发包含 TI 产品的任何应用前,将彻底测试该等应用和该等应用中所用 TI 产品的功能。

TI 提供技术、应用或其他设计建议、质量特点、可靠性数据或其他服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI资源"),旨在帮助设计人员开发整合了 TI 产品的 应用, 如果设计人员(个人,或如果是代表公司,则为设计人员的公司)以任何方式下载、访问或使用任何特定的 TI资源,即表示其同意仅为该等目标,按照本通知的条款使用任何特定 TI资源。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

设计人员只有在开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为或对设计人员进行辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

除 TI 己明确指出特定产品已达到特定行业标准(例如 ISO/TS 16949 和 ISO 26262)的要求外,TI 不对未达到任何该等行业标准要求而承担任何责任。

如果 TI 明确宣称产品有助于功能安全或符合行业功能安全标准,则该等产品旨在帮助客户设计和创作自己的 符合 相关功能安全标准和要求的应用。在应用内使用产品的行为本身不会 配有 任何安全特性。设计人员必须确保遵守适用于其应用的相关安全要求和 标准。设计人员不可将任何 TI 产品用于关乎性命的医疗设备,除非己由各方获得授权的管理人员签署专门的合同对此类应用专门作出规定。关乎性命的医疗设备是指出现故障会导致严重身体伤害或死亡的医疗设备(例如生命保障设备、心脏起搏器、心脏除颤器、人工心脏泵、神经刺激器以及植入设备)。此类设备包括但不限于,美国食品药品监督管理局认定为 III 类设备的设备,以及在美国以外的其他国家或地区认定为同等类别设备的所有医疗设备。

TI 可能明确指定某些产品具备某些特定资格(例如 Q100、军用级或增强型产品)。设计人员同意,其具备一切必要专业知识,可以为自己的应用选择适合的 产品, 并且正确选择产品的风险由设计人员承担。设计人员单方面负责遵守与该等选择有关的所有法律或监管要求。

设计人员同意向 TI 及其代表全额赔偿因其不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司