# Communications System Supervisory/Sequencing Circuit

ADM1060

#### **FEATURES**

Faults detected on 7 independent supplies

1 high voltage supply (2 V to 14.4 V)

4 positive voltage only supplies (2 V to 6 V)

2 positive/negative voltage supplies (+2 V to +6 V and -2 V to -6 V)

Watchdog detector input—timeout delay programmable from 200 ms to 12.8 sec

4 general-purpose logic inputs

Programmable logic block—combinatorial and sequencing logic control of all inputs and outputs

9 programmable output drivers:

Open collector (external resistor required)

Open collector with internal pull-up to  $V_{\text{DD}}$

Fast internal pull-up to  $V_{\text{DD}}$

Open collector with internal pull-up to VPn

Fast internal pull-up to VPn

Internally charge-pumped high drive (for use with external N-channel FETs—PDOs 1 to 4 only)

EEPROM—256 bytes of user EEPROM

Industry-standard 2-wire bus interface (SMBus)

Guaranteed PDO low with VPn, VH = 1 V

### **APPLICATIONS**

Central office systems

Servers

Infrastructure network boards

High density, multivoltage system cards

#### **GENERAL DESCRIPTION**

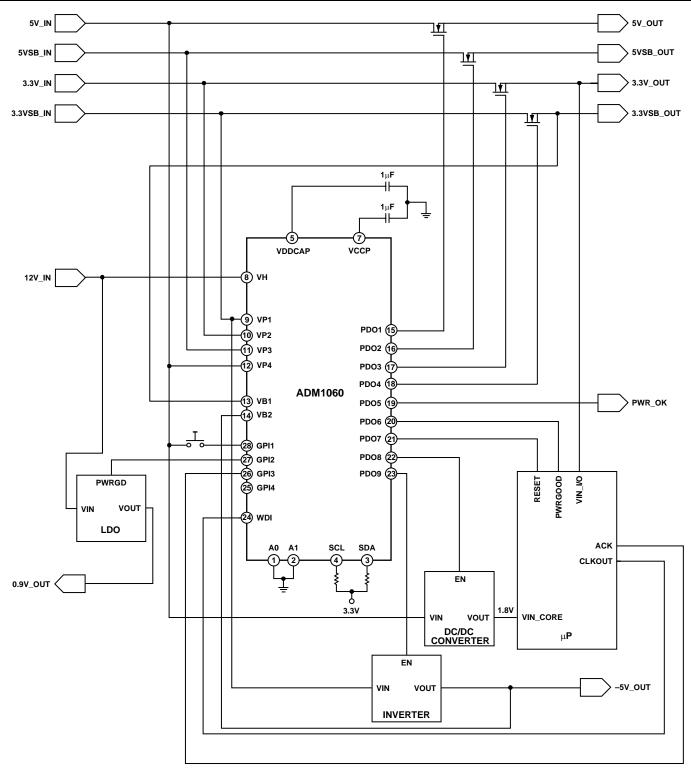

The ADM1060 is a programmable supervisory/sequencing device that offers a single chip solution for multiple power supply fault detection and sequencing in communications systems.

In central offices, servers, and other infrastructure systems, a common backplane dc supply is reduced to multiple board supplies using dc-to-dc converters. These multiple supplies are used to power different sections of the board, such as 3.3 V logic circuits, 5 V logic circuits, DSP core, and DSP I/O circuits. There is usually a requirement that certain sections power up before others; for example, a DSP core may need to power up before the DSP I/O, or vice versa, to avoid damage, miscommunication, or latch-up. The ADM1060 facilitates this, providing supply

fault detection and sequencing/combinatorial logic for up to seven independent supplies. The seven supply fault detectors consist of one high voltage detector (up to +14.4 V), two bipolar voltage detectors (up to +6 V or down to -6 V), and four positive low voltage detectors (up to +6 V). All of the detectors can be programmed to detect undervoltage, overvoltage, or out-of-window (undervoltage or overvoltage) conditions. The inputs to these supply fault detectors are via the VH (high voltage) pin, VBn (positive or negative) pins, and VPn (positive only) pins. Either the VH supply or one of the VPn supplies is used to power the ADM1060 (whichever is highest). This ensures that in the event of a supply failure, the ADM1060 is kept alive for as long as possible, thus enabling a reliable fault flag to be asserted and the system to be powered down in an ordered fashion.

Other inputs to the ADM1060 include a watchdog detector (WDI) and four general-purpose inputs (GPIn). The watchdog detector can be used to monitor a processor clock. If the clock does not toggle (transition from low to high or from high to low) within a programmable timeout period (up to 18 sec.), a fail flag will assert. The four general-purpose inputs can be configured as logic buffers or to detect positive/negative edges and to generate a logic pulse or level from those edges. Thus, the user can input control signals from other parts of the system (e.g., RESET or POWER\_GOOD) to gate the sequencing of the supplies supervised by the ADM1060.

The ADM1060 features nine programmable driver outputs (PDOs). All nine outputs can be configured to be logic outputs, which can provide multiple functions for the end user such as RESET generation, POWER\_GOOD status, enabling of LDOs, and watchdog timeout assertion. PDOs 1 to 4 have the added feature of being able to provide an internally charge-pumped high voltage for use as the gate drive of an external N-channel FET that could be placed in the path of one of the supplies being supervised.

(continued on Page 3)

### **TABLE OF CONTENTS**

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|

| Typical Performance Characteristics       8         Inputs       11         SFD REGISTER NAMES       14         SFD Register Bit Maps       15         Programming       21         Logic       22         PLBA REGISTER BIT MAPS       28         Outputs       33         REVISION HISTORY       12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications       5         Changes to Outputs section       33         Updated Outline Dimensions       50         5/03—Data sheet changed from Rev. 0 to Rev. A.       6         Changes to Features       1         Changes to Figure 1       4         Changes to Figure 1       4         Changes to Figure 2, 2, 1, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Programmable Driver Outputs section       33         Changes to Figure 25–26       43 | Specifications                                 | 5                                  |

| Inputs.       11         SFD REGISTER NAMES.       14         SFD Register Bit Maps       15         Programming       21         Logic       22         PLBA REGISTER BIT MAPS       28         Outputs       33         REVISION HISTORY         12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications.       5         Changes to Outputs section.       33         Updated Outline Dimensions.       50         5/03—Data sheet changed from Rev. 0 to Rev. A.       6         Changes to Features       1         Changes to Figure 1       4         Changes to Figure 1       4         Changes to Figure 2       8         10       1         11       1         12       1         13       1         14       1         15       1         16       1                                                                                                                                           | Absolute Maximum Ratings                       | 7                                  |

| SFD REGISTER NAMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Typical Performance Characteristics            | 8                                  |

| SFD Register Bit Maps       15         Programming       21         Logic       22         PLBA REGISTER BIT MAPS       28         Outputs       33         REVISION HISTORY         12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications       5         Changes to Outputs section       33         Updated Outline Dimensions       50         5/03—Data sheet changed from Rev. 0 to Rev. A       1         Changes to Features       1         Changes to Figure 1       4         Changes to Figure 1       4         Changes to Figure 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Change to Table 19       17         Changes to Figure 25–26       43         Changes to Figure 25–26       43         Changes to Table 58       49                                                                                                                                 | Inputs                                         | 11                                 |

| Programming       21         Logic       22         PLBA REGISTER BIT MAPS       28         Outputs       33         REVISION HISTORY         12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications       5         Changes to Outputs section       33         Updated Outline Dimensions       50         5/03—Data sheet changed from Rev. 0 to Rev. A       6         Changes to Features       1         Changes to Features       5         Changes to Figure 1       4         Changes to Figure 1       4         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Changes to Figure 25–26       43         Changes to Table 58       49                                                                                                                                                                                    | SFD REGISTER NAMES                             | 14                                 |

| Logic       22         PLBA REGISTER BIT MAPS       28         Outputs       33         REVISION HISTORY         12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications       5         Changes to Outputs section       33         Updated Outline Dimensions       50         5/03—Data sheet changed from Rev. 0 to Rev. A       1         Changes to Features       1         Changes to Specifications       5         Changes to Figure 1       4         Changes to Figure 1       4         Changes to Figure 8       10         Changes to Figure 17       11         Changes to Figure 18       12         Changes to Figure 18       12         Changes to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Figure 25–26       43         Changes to Table 58       49                                                                                                                                                                                                                                                           | SFD Register Bit Maps                          | 15                                 |

| PLBA REGISTER BIT MAPS       28         Outputs       33         REVISION HISTORY         12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications       5         Changes to Outputs section       33         Updated Outline Dimensions       50         5/03—Data sheet changed from Rev. 0 to Rev. A       1         Changes to Features       1         Changes to Specifications       5         Changes to Figure 1       4         Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Table 9       15         Change to Table 14       16         Changes to Table 19       17         Changes to Programmable Driver Outputs section       33         Changes to Figure 25–26       43         Changes to Table 58       49                                                                                                                                                                              | Programming                                    | 21                                 |

| Outputs       33         REVISION HISTORY         12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications       5         Changes to Outputs section       33         Updated Outline Dimensions       50         5/03—Data sheet changed from Rev. 0 to Rev. A         Changes to Features       1         Changes to Specifications       5         Changes to Figure 1       4         Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Changes to Table 19       17         Changes to Programmable Driver Outputs section       33         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                       | Logic                                          | 22                                 |

| REVISION HISTORY         12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PLBA REGISTER BIT MAPS                         | 28                                 |

| 12/03—Data sheet changed from Rev. A to Rev. B         Changes to Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Outputs                                        | 33                                 |

| Changes to Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | REVISION HISTORY                               |                                    |

| Changes to Outputs section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12/03—Data sheet changed from Rev. A to Rev. B |                                    |

| 5/03—Data sheet changed from Rev. 0 to Rev. A.         Changes to Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Changes to Specifications                      | 5                                  |

| 5/03—Data sheet changed from Rev. 0 to Rev. A.         Changes to Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Changes to Outputs section                     | 33                                 |

| Changes to Features.       1         Changes to Specifications       5         Changes to Figure 1       4         Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Updated Outline Dimensions                     | 50                                 |

| Changes to Features.       1         Changes to Specifications       5         Changes to Figure 1       4         Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                |                                    |

| Changes to Specifications       5         Changes to Figure 1       4         Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                |                                    |

| Changes to Specifications       5         Changes to Figure 1       4         Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5/03—Data sheet changed from Rev. 0 to Rev. A. |                                    |

| Changes to Figure 1       4         Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                | 1                                  |

| Changes to Absolute Maximum Ratings       7         Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Changes to Features                            |                                    |

| Changes to Figures 2, 8, 15–16       8–10         Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Changes to Programmable Driver Outputs section       33         Changes to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Changes to Features                            | 5                                  |

| Changes to Figure 17       11         Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Changes to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Changes to Features                            | 5<br>4                             |

| Changes to Programmable Supply Fault Detectors section       11         Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Change to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Changes to Features                            | 5<br>4<br>7                        |

| Changes to Figure 18       12         Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Change to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Changes to Features                            | 5<br>4<br>7<br>8–10                |

| Changes to Figure 19       13         Change to Table 9       15         Change to Table 14       16         Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Change to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Changes to Features                            | 5<br>                              |

| Change to Table 9       15         Change to Table 14       16         Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Change to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Changes to Features                            | 5<br>7<br>8–10<br>11               |

| Change to Table 14       16         Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Change to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Changes to Features                            | 5<br>4<br>7<br>8–10<br>11<br>on 11 |

| Change to Table 19       17         Changes to Programmable Driver Outputs section       33         Change to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Changes to Features                            |                                    |

| Changes to Programmable Driver Outputs section.       33         Change to Table 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Changes to Features                            |                                    |

| Change to Table 40       34         Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Changes to Features                            |                                    |

| Changes to Figure 25–26       43         Changes to Figure 37       47         Changes to Table 58       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Changes to Features                            |                                    |

| Changes to Figure 37 47 Changes to Table 58 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Changes to Features                            |                                    |

| Changes to Table 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Changes to Features                            | 5                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Changes to Features                            | 5                                  |

| Changes to Ordering Gilide Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Changes to Features                            | 5                                  |

| PROGRAMMABLE DRIVER OUTPUTS                   | 33         |

|-----------------------------------------------|------------|

| Status/Faults                                 | 35         |

| FAULT REGISTERS                               | 38         |

| MASK REGISTERS                                | 39         |

| Programming                                   | 40         |

| WRITE OPERATIONS                              | <b>4</b> 4 |

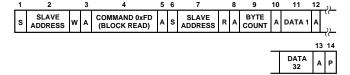

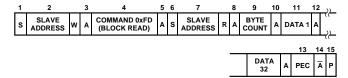

| READ OPERATIONS                               | 45         |

| Pin Configuration and Functional Descriptions | 49         |

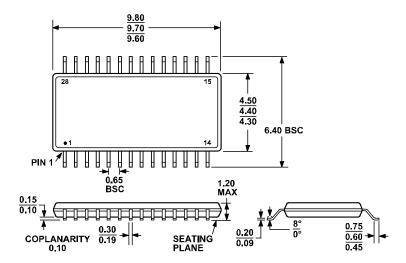

| Outline Dimensions                            | 50         |

| Ordering Guide                                | 50         |

### **GENERAL DESCRIPTION**

(continued from Page 1)

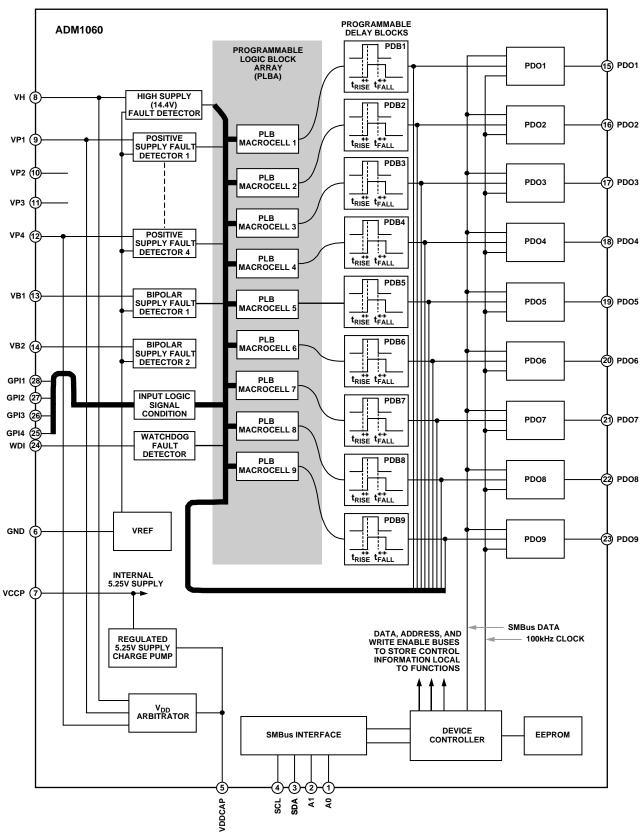

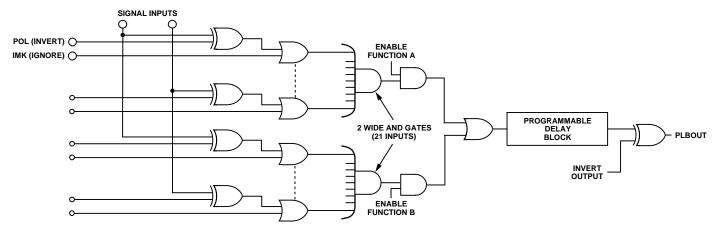

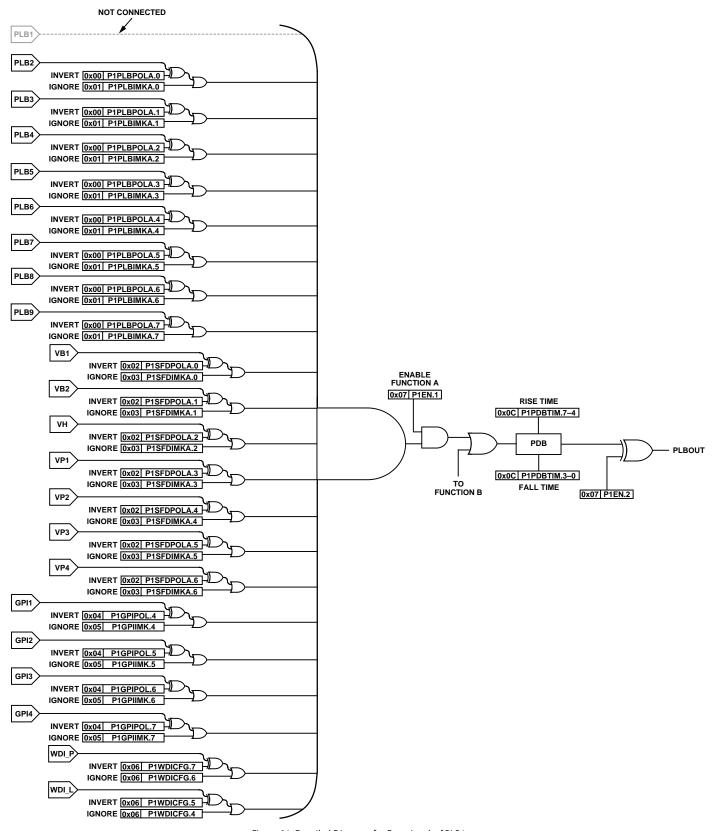

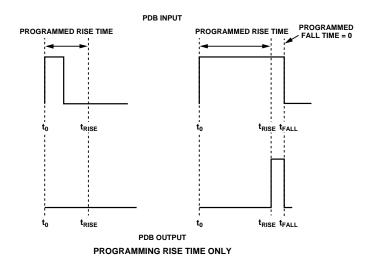

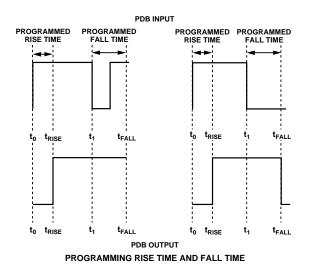

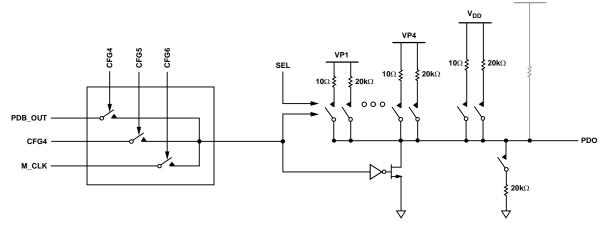

All of the inputs and outputs described previously are controlled by the programmable logic block array (PLBA). This is the logic core of the ADM1060. It is comprised of nine macrocells, one for each PDO. These macrocells are essentially just wide AND gates. Any/all of the inputs can be used as an input to these macrocells. The output of a macrocell can also be used as an input to any macrocell other than itself (an input to itself would result in a nonterminating loop). The PLBA outputs control the PDOs of the ADM1060 via delay blocks, where a delay of 0 ms to 500 ms can be programmed on the rising and/or the falling edge of the data. This results in a very flexible sequencing ability. Thus, for instance, PDO1 can be programmed so that it will not assert until the VP2, VP3, and VP4 supplies are in tolerance; VB1 and VH have been in tolerance for 200 ms; and PDO7 has already been asserted. A

simple sequencing operation would be to daisy-chain each PLB output into the input of the next PLB such that PDO9 does not assert until PDO8 asserts, which in turn does not assert until PDO7 asserts, and so on.

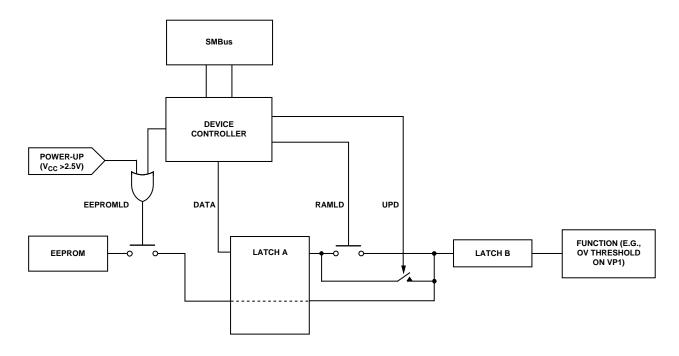

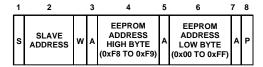

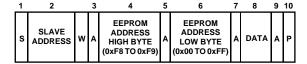

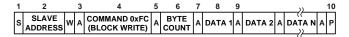

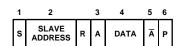

All of the functional capability described here is programmable through the industry-standard 2-wire bus (SMBus) provided. Device settings can be written to EEPROM memory for automatic programming of the device on power-up. The EEPROM is organized in 512 bytes, half of which are used to program all of the functions on the ADM1060. The other 256 bytes of EEPROM are for general-purpose system use such as date codes and system ID. Read/write access to this is also via the 2-wire interface. In addition, each output state can be directly overdriven from the serial interface, allowing a further level of control, as in a system controlled soft power-down.

Figure 1. Functional Block Diagram

### **SPECIFICATIONS**

(VH = 4.75 V to 14.4 V, VPn = 3.0 V to 6.0 V,  $^{1}$  T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.)

Table 1.

| Parameter                                                                         | Min       | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                   |

|-----------------------------------------------------------------------------------|-----------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY ARBITRATION                                                          |           |      |      |      |                                                                                                                                            |

| VDDCAP                                                                            | 2.7       |      |      | V    | Any VPn ≥ 3.0 V                                                                                                                            |

|                                                                                   | 2.7       |      |      | V    | VH ≥ 4.75 V                                                                                                                                |

|                                                                                   |           | 4.75 | 5.1  | V    | Any $VPn = 6.0 V$                                                                                                                          |

|                                                                                   |           | 4.75 | 5.1  | V    | VH = 14.4 V                                                                                                                                |

| POWER SUPPLY                                                                      |           |      |      |      |                                                                                                                                            |

| Supply Current, I <sub>DD</sub>                                                   |           | 3    |      | mA   | VDDCAP = 4.75 V, no PDO FET drivers on, no loaded PDO pull-ups to VDDCAP                                                                   |

|                                                                                   |           |      | 5    | mA   | VDDCAP = 4.75 V, all PDO FET drivers on (loaded with 1 $\mu$ A), no PDO pull-ups to VDDCAP                                                 |

| Additional Current Available from VDDCAP <sup>2</sup>                             |           |      | 1    | mA   | Max additional load that can be drawn from PDO pull-ups to VDDCAP                                                                          |

| SUPPLY FAULT DETECTORS                                                            |           |      |      |      |                                                                                                                                            |

| Input Impedance                                                                   |           |      |      |      |                                                                                                                                            |

| VH Input                                                                          |           | 52   |      | kΩ   | From VH to GND                                                                                                                             |

| VPn Inputs                                                                        |           | 52   |      | kΩ   | From VPn to GND                                                                                                                            |

| VBn Inputs                                                                        |           | 190  |      | kΩ   | From VBn to 2.25 V (internal reference)                                                                                                    |

|                                                                                   |           | 52   |      | kΩ   | From VBn to GND (positive mode)                                                                                                            |

|                                                                                   |           | 30   |      | kΩ   | From VBn to GND (negative mode)                                                                                                            |

| Absolute Accuracy (VH, VPn, VBn Inputs) Calibrated Absolute Accuracy <sup>3</sup> | -2.5      |      | +2.5 | %    |                                                                                                                                            |

| VH, VPn Inputs                                                                    | -1.0      |      | +1.0 | %    | Factory preprogrammed to specific thresholds                                                                                               |

| VBn Inputs                                                                        | -1.5      |      | +1.5 | %    | Factory preprogrammed to specific thresholds                                                                                               |

| Glitch Filters (Digital)                                                          | 0         |      | 100  | μs   | See Figure 19. Eight timeout options between 0 $\mu$ s and 100 $\mu$ s                                                                     |

| PROGRAMMABLE DRIVER OUTPUTS                                                       |           |      |      |      |                                                                                                                                            |

| High Voltage (Charge Pump) Mode (PDOs 1 to 4)                                     |           |      |      |      |                                                                                                                                            |

| Output Impedance, Rout                                                            |           | 440  |      | kΩ   |                                                                                                                                            |

| $V_{OH}$                                                                          | 11        | 12.5 | 14   | V    | $I_{OH} = 0 \mu A$                                                                                                                         |

|                                                                                   | 10.5      | 12   |      | V    | $I_{OH} = 1 \mu A$                                                                                                                         |

| loutavg                                                                           |           | 20   |      | μΑ   | $2 V < V_{OH} < 7 V$                                                                                                                       |

| Standard (Digital Output) Mode<br>(PDOs 1 to 9)                                   |           |      |      |      |                                                                                                                                            |

| $V_{OH}$                                                                          | 2.4       |      |      | V    | $V_{PU}$ (pull-up to VDDCAP or VPn) > 2.7 V, $I_{OH} = 1 \text{ mA}$                                                                       |

|                                                                                   |           |      | 4.5  | V    | $V_{PU}$ to $VPn = 6.0 V$ , $I_{OH} = 0 mA$                                                                                                |

|                                                                                   | VPU – 0.3 |      |      | V    | $V_{PU} \le 2.7 \text{ V, } I_{OH} = 1 \text{ mA}$                                                                                         |

| $V_{OL}$                                                                          |           |      | 0.4  | V    | $I_{OL} = 2 \text{ mA}$                                                                                                                    |

|                                                                                   |           |      | 1.2  | V    | $I_{OL} = 10 \text{ mA}$                                                                                                                   |

|                                                                                   |           |      | 2.0  | V    | $I_{OL} = 15 \text{ mA}$                                                                                                                   |

| I <sub>SINK</sub> <sup>2</sup>                                                    |           |      | 20   | mA   | Total sink current (PDO1–PDO9)                                                                                                             |

| R <sub>PULLUP</sub> - Weak Pull-Up                                                |           | 20   |      | kΩ   | Internal pull-up                                                                                                                           |

| ISOURCE (VPn) <sup>2</sup>                                                        |           |      | 2    | mA   | Current load on any VPn pull-up (i.e., total source current available through any number of PDO pull-up switches configured on to any one) |

| Three-State Output Leakage Current                                                |           |      | 10   | μΑ   | $V_{PDO} = 14.4 \text{ V}$                                                                                                                 |

| Parameter                                          | Min | Тур | Max  | Unit    | Test Conditions/Comments                                |

|----------------------------------------------------|-----|-----|------|---------|---------------------------------------------------------|

| DIGITAL INPUTS (GPI 1–4, WDI, A0, A1) <sup>4</sup> |     |     |      |         |                                                         |

| Input High Voltage, V <sub>⊪</sub>                 | 2.0 |     |      | V       |                                                         |

| Input Low Voltage, V <sub>IL</sub>                 |     |     | 0.8  | V       |                                                         |

| Input High Current, I <sub>IH</sub>                | -1  |     |      | μΑ      | $V_{IN} = 5.5 V$                                        |

| Input Low Current, I <sub>IL</sub>                 |     |     | 1    | μΑ      | $V_{IN} = 0 V$                                          |

| Input Capacitance                                  |     | 10  |      | рF      |                                                         |

| Programmable Pull-Down Current, IPULLDOWN          |     | 10  |      | μΑ      | If known logic state required                           |

| SERIAL BUS DIGITAL INPUTS (SDA, SCL)               |     |     |      |         |                                                         |

| Input High Voltage, V <sub>IH</sub>                | 2.0 |     |      | V       |                                                         |

| Input Low Voltage, V <sub>IL</sub>                 |     |     | 0.8  | V       |                                                         |

| Output Low Voltage, Vol                            |     |     | 0.4  | V       | $I_{OUT} = -3.0 \text{ mA}$                             |

| PROGRAMMABLE DELAY BLOCK                           |     |     |      |         |                                                         |

| Timeout                                            | 0   |     | 500  | ms      | 16 programmable options on both rising and falling edge |

| WATCHDOG TIMER INPUT                               |     |     |      |         |                                                         |

| Timeout                                            | 0   |     | 12.8 | S       | Eight programmable timeout options                      |

| EEPROM RELIABILITY                                 |     |     |      |         |                                                         |

| Endurance <sup>5, 6</sup>                          | 100 |     |      | Kcycles |                                                         |

| Data Retention <sup>7</sup>                        | 10  |     |      | Years   |                                                         |

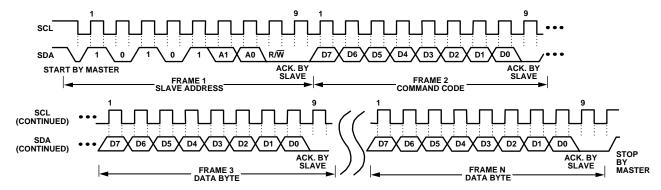

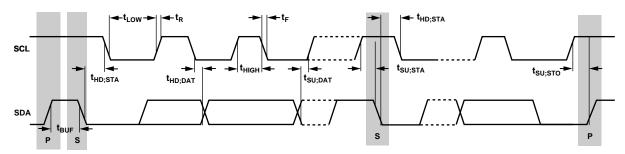

| SERIAL BUS TIMING <sup>8</sup>                     |     |     |      |         |                                                         |

| Clock Frequency, f <sub>SCLK</sub>                 |     |     | 400  | kHz     | See Figure 27                                           |

| Glitch Immunity, tsw                               |     |     | 50   | ns      | See Figure 27                                           |

| Bus Free Time, t <sub>BUF</sub>                    | 4.7 |     |      | μs      | See Figure 27                                           |

| Start Setup Time, t <sub>SU;STA</sub>              | 4.7 |     |      | μs      | See Figure 27                                           |

| Start Hold Time, t <sub>HD;STA</sub>               | 4   |     |      | μs      | See Figure 27                                           |

| SCL Low Time, t <sub>LOW</sub>                     | 4.7 |     |      | μs      | See Figure 27                                           |

| SCL High Time, t <sub>HIGH</sub>                   | 4   |     |      | μs      | See Figure 27                                           |

| SCL, SDA Rise Time, t <sub>r</sub>                 |     |     | 1000 | ns      | See Figure 27                                           |

| SCL, SDA Fall Time, t <sub>f</sub>                 |     |     | 300  | μs      | See Figure 27                                           |

| Data Setup Time, t <sub>SU;DAT</sub>               | 250 |     |      | ns      | See Figure 27                                           |

| Data Hold Time, t <sub>HD;DAT</sub>                | 300 |     |      | ns      | See Figure 27                                           |

NOTES

At least one VPn must be ≥3.0 V if used as supply. VH must be ≥4.5 V if used as supply.

2 Specification is not production tested, but is supported by characterization data at initial product release.

3 1% threshold accuracy is only achievable on parts preprogrammed by Analog Devices. Contact ADM1060.program@analog.com for further details.

<sup>&</sup>lt;sup>4</sup>Logic inputs will accept input high voltages up to 5.5 V even when the device is operating at supply voltages below 5 V. <sup>5</sup>Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117, and measured at -40°C, +25°C, and +85°C.

For programming and erasing of EEPROM, a minimum  $V_{DD} = 3.0 \text{ V}$  is required 0°C to +85°C and a minimum  $V_{DD} = 4.5 \text{ V}$  is required -40°C to 0°C. Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C as per JEDEC Std. 22 method A117. 8Timing specifications are tested at logic levels of  $V_{IL} = 0.8 \text{ V}$  for a falling edge and  $V_{IH} = 2.0 \text{ V}$  for a rising edge.

### **ABSOLUTE MAXIMUM RATINGS**

### **Table 2. Absolute Maximum Ratings**

|                                                     | ~                |

|-----------------------------------------------------|------------------|

| Parameter                                           | Rating           |

| Voltage on VH Pin, PDO Pins                         | 17 V             |

| Voltage on VP Pins                                  | 7 V              |

| Voltage on VB Pins                                  | -7 V to +7 V     |

| Voltage on Any Other Input                          | -0.3 V to +6.5 V |

| Input Current at Any Pin                            | ±5 mA            |

| Package Input Current                               | ±20 mA           |

| Maximum Junction Temperature (T <sub>J</sub> max)   | 150°C            |

| Storage Temperature Range                           | −65°C to +150°C  |

| Lead Temperature, Soldering<br>Vapor Phase (60 sec) | 215°C            |

| ESD Rating, All Pins                                | 2000 V           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS

28-Lead TSSOP Package:  $\theta_{JA} = 98^{\circ}\text{C/W}$

### TYPICAL PERFORMANCE CHARACTERISTICS

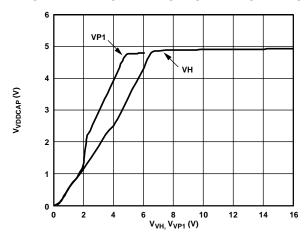

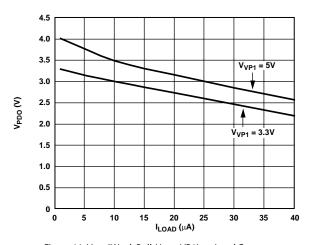

Figure 2. V<sub>VDDCAP</sub> vs. V<sub>VH</sub> and V<sub>VP1</sub>

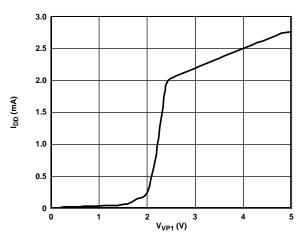

Figure 3.  $I_{DD}$  vs.  $V_{VP1}$  (Supply)

Figure 4. IVP1 vs. VVP1 (Not Supply)

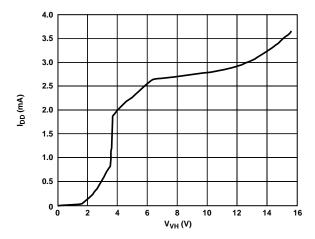

Figure 5. IDD vs. VVH

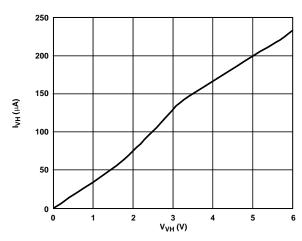

Figure 6. I<sub>VH</sub> vs. V<sub>VH</sub> (Not Supply)

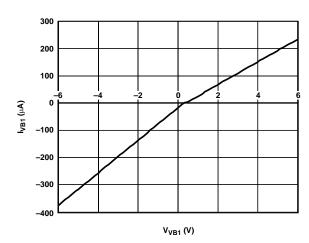

Figure 7. IVB1 vs. VVB1

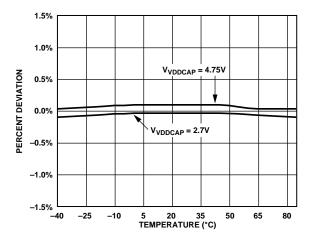

Figure 8. Percent Deviation in  $V_{\text{THRESH}}$  vs. Temperature

Figure 9. V<sub>PDO</sub> (FET Drive Mode) vs. Temperature

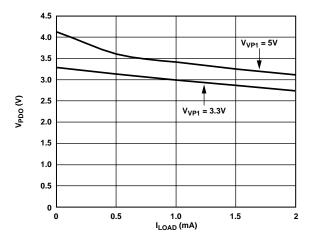

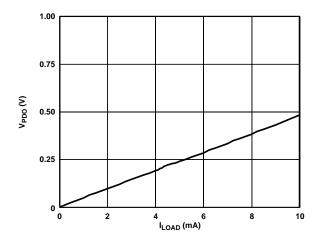

Figure 10. V<sub>PDO</sub> (Strong Pull-Up to VP1) vs. Load Current

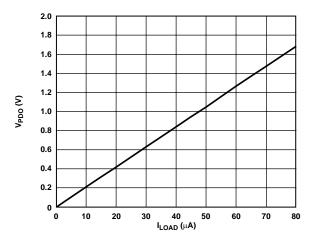

Figure 11. V<sub>PDO</sub> (Weak Pull-Up to VP1) vs. Load Current

Figure 12. V<sub>PDO</sub> (Strong Pull-Down) vs. Load Current

Figure 13. V<sub>PDO</sub> (Weak Pull-Down) vs. Load Current

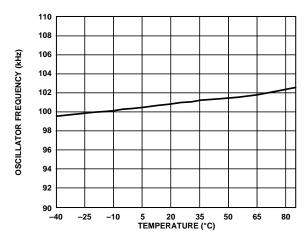

Figure 14. Oscillator Frequency vs. Temperature

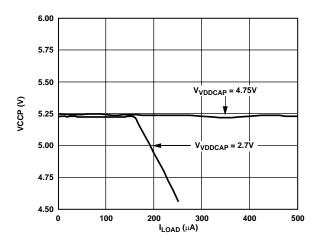

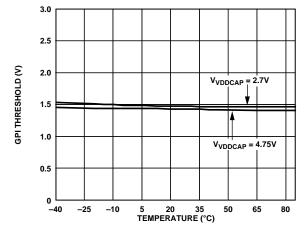

Figure 15. VCCP vs. Load Current

Figure 16. GPI Threshold vs. Temperature

### **INPUTS**

#### **POWERING THE ADM1060**

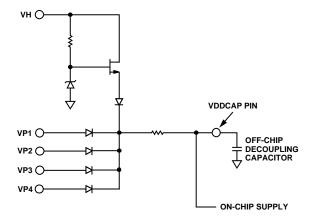

The ADM1060 is powered from the highest voltage input on either the Positive Only supply inputs (VPn) or the High Voltage supply input (VH). The same pins are used for supply fault detection (discussed below). A  $V_{\rm DD}$  arbitrator on the device chooses which supply to use. The arbitrator can be considered as diode OR'ing the positive supplies together (as shown in Figure 17). The diodes are supplemented with switches in a synchronous rectifier manner to minimize voltage loss. This loss can be reduced to ~0.2 V, resulting in the ability to power the ADM1060 from a supply as low as 3.0 V. Note that the supply on the VBn pins cannot be used to power the device, even if the input on these pins is positive. Also, the minimum supply of 3.0 V must appear on one of the VPn pins in order to correctly power up the ADM1060. A supply of no less than 4.5 V can be used on VH. This is because there is no synchronous rectifier circuit on the VH pin, resulting in a voltage drop of  $\sim$ 1.5 V across the diode of the V<sub>DD</sub> arbitrator.

An external capacitor to GND is required to decouple the on-chip supply from noise. This capacitor should be connected to the VDDCAP pin, as shown in Figure 17. The capacitor has another use during "brown outs" (momentary loss of power). Under these conditions, where the input supply, VPn, dips transiently below  $V_{\rm DD}$ , the synchronous rectifier switch immediately turns off so that it does not pull  $V_{\rm DD}$  down. The  $V_{\rm DD}$  capacitor can then act as a reservoir to keep the chip active until the next highest supply takes over the powering of the device. A 1  $\mu F$  capacitor is recommended for this function. A minimum capacitor value of 0.1  $\mu F$  is required.

Note that in the case where there are two or more supplies within 100 mV of each other, the supply that takes control of  $V_{\rm DD}$  first will keep control. For example, if VP1 is connected to a 3.3 V supply,  $V_{\rm DD}$  will power up to approximately 3.1 V through VP1. If VP2 is then connected to another 3.3 V supply, VP1 will still power the device, unless VP2 goes 100 mV higher than VP1.

A second capacitor is required on the VCCP pin of the ADM1060. This capacitor is the reservoir capacitor for the central charge pump. Again, a 1  $\mu F$  capacitor is recommended for this function. A minimum capacitor value of 0.1  $\mu F$  is required.

Figure 17. V<sub>DD</sub> Arbitrator Operation

# PROGRAMMABLE SUPPLY FAULT DETECTORS (SFDs)

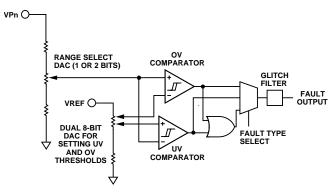

The ADM1060 has seven programmable supply fault detectors (SFDs): one high voltage detector (+2 V to +14.4 V), two bipolar detectors (+1 V to +6 V, -2 V to -6 V) and four positive only voltage detectors (+0.6 V to +6 V). Inputs are applied to these detectors via the VH (high voltage supply input), VBn (bipolar supply input), and VPn (positive only input) pins, respectively. The SFDs detect a fault condition on any of these input supplies. A fault is defined as undervoltage (where the supply drops below a preprogrammed level), overvoltage (where the supply rises above a preprogrammed level), or out-of-window (where the supply deviates outside either the programmed overvoltage or undervoltage threshold). Only one fault type can be selected at a time.

An undervoltage (UV) fault is detected by comparing the input supply to a programmed reference (the undervoltage threshold). If the input voltage drops below the undervoltage threshold, the output of the comparator goes high, asserting a fault. The undervoltage threshold is programmed using an 8-bit DAC. On a given range, the UV threshold can be set with a resolution of

An overvoltage (OV) fault is detected in exactly the same way, using a second comparator and DAC to program the reference.

All thresholds are programmed using 8-bit registers, one register each for the seven UV thresholds and one each for the seven OV thresholds. The UV or OV threshold programmed by the user is given by

$$V_T = \frac{V_R \times N}{255} + V_B$$

where

| Voltage Range   | V <sub>B</sub> (V) | V <sub>R</sub> (V) |

|-----------------|--------------------|--------------------|

| 0.6 V to 1.8 V  | 0.604              | 1.204              |

| 1 V to 3 V      | 1.003              | 1.999              |

| 2 V to 6 V      | 2.005              | 3.997              |

| 4.8 V to 14.4 V | 4.849              | 9.666              |

| -2 V to -6 V    | -1.994             | -3.995             |

$V_T$  is the desired threshold voltage (UV or OV)

$V_R$  is the threshold voltage range

N is the decimal value of the 8 bit code

$V_B$  is the bottom of threshold range

The code for a given threshold is therefore given by

$$N = 255 \times (V_T - V_B)/V_R$$

For example, if the user wishes to set a 5 V OV threshold on VP1, the code to be programmed in the PS1OVTH register (discussed later) would be

$$N = 255 \times (5 - 2.005)/3.997$$

Thus, N = 191 (1011 1111 binary, or 0xBF)

The available threshold ranges and their resolutions are shown in Table 3. Note that the low end of the detection range is fixed at 33.33% of the top of the range. Note also that for a given SFD, the ranges overlap; for example, VH goes from 2 V to 6 V and then from 4.8 V to 14.4 V. This is to provide better threshold setting resolution as supplies decrease in value.

**Table 3. Input Threshold Ranges and Resolution**

| Input Name | Voltage Ranges  | Resolution          |

|------------|-----------------|---------------------|

| VH         | 4.8 V to 14.4 V | 37.6 mV             |

| VП         | 2 V to 6 V      | 15.6 mV             |

|            | 2 V to 6 V      | 15.6 mV (Pos. Mode) |

| VBn        | 1 V to 3 V      | 7.8 mV (Pos. Mode)  |

|            | −6 V to −2 V    | 15.6 mV (Neg. Mode) |

|            | 2 V to 6 V      | 15.6 mV             |

| VPn        | 1 V to 3 V      | 7.8 mV              |

|            | 0.6 V to 1.8 V  | 4.7 mV              |

Figure 18 illustrates the function of the programmable SFD (for the case of a positive supply).

Figure 18. Positive Programmable Supply Fault Detector

#### SFD COMPARATOR HYSTERESIS

The OV and UV comparators shown in Figure 18 are always looking at VPn via a potential divider. In order to avoid chattering (multiple transitions when the input is very close to the set threshold level), these comparators have digitally programmable hysteresis. The UV and OV hysteresis can be programmed in two registers that are similar but separate to the UV or OV threshold registers. Only the five LSBs of these registers can be set. The hysteresis is added after the supply voltage goes out of tolerance. Thus, the user can determine how much above the UV threshold the input must rise again before a UV fault is deasserted. Similarly, the user can determine how much below the OV threshold the input must fall again before an OV fault is deasserted. The hysteresis figure is given by

$$V_H = V_R \times N_{THRESH}/255$$

where

$V_H$  is the desired hysteresis voltage

$N_{THRESH}$  is the decimal value of the 5-bit hysteresis code

Therefore, if the low range threshold detector was selected, the max hysteresis is defined as

$$(3 \text{ V} - 1 \text{ V}) \times 31/255 = 242 \text{ mV}$$

, where  $(2^5 - 1 = 31)$

The hysteresis programming resolution is the same as the threshold detect ranges—that is, 37.5 mV on the high range, 15.6 mV on the midrange, 7.8 mV on the low range, and 4.7 mV on the ultralow range.

#### **BIPOLAR SFDs**

The two bipolar SFDs also allow the detection of faults on negative supplies. A polarity bit in the setup register for this SFD (Bit 7 in Register BSnSEL—see register map overleaf) determines if a positive or negative input should be applied to VBn. Only one range (-6 V to -2 V) is available when the SFDs are in negative mode. Note that the bipolar SFDs cannot be used to power the ADM1060, even if the voltage on VBn is positive.

#### **SFD FAULT TYPES**

Three types of faults can be asserted by the SFD: an OV fault, a UV fault, and an out-of-window fault (where the UV and OV faults are OR'ed together). The type of fault required is programmed using the fault type select bits (Bits 0, 1 in Register \_SnSEL). If an application requires separate fault conditions to be detected on one supply (e.g., assert PDO1 if a UV fault occurs on a 3.3 V supply, assert PDO9 if an OV fault occurs on the same 3.3 V supply), that supply will need to be applied to more than one input pin.

#### **GLITCH FILTERING ON THE SFDs**

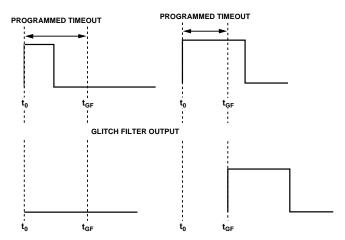

The final stage of the SFD is a glitch filter. This block provides time domain filtering on the output of the SFD. This allows the user to remove any spurious transitions (such as supply bounce at turn-on). This deglitching function is in addition to the programmable hysteresis of the SFDs. The glitch filter timeout is programmable up to  $100~\mu s$ . If a pulse shorter than the programmed timeout appears on the input, this pulse is masked and the signal change will appear on the output. If an input pulse longer than the programmed timeout appears on the input, this pulse will appear on the output. The output will be delayed (with respect to the input) by the length of the programmed timeout.

Figure 19 shows the implementation of glitch filtering.

#### **GLITCH FILTER INPUT**

Figure 19. Glitch Filtering on the SFDs

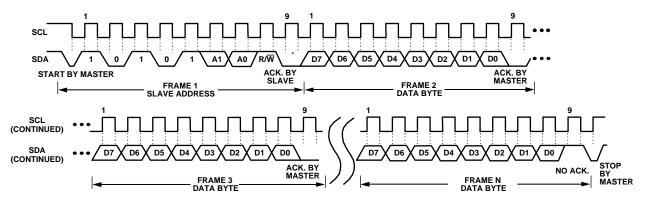

#### PROGRAMMING THE SFDs ON THE SMBus