# 12-Bit, 2.6 GSPS/2.5 GSPS/2.0 GSPS, 1.3 V/2.5 V Analog-to-Digital Converter

Data Sheet AD9625

#### **FEATURES**

12-bit 2.5 GSPS ADC, no missing codes

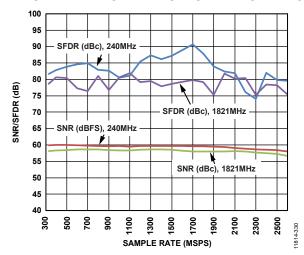

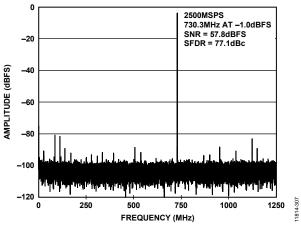

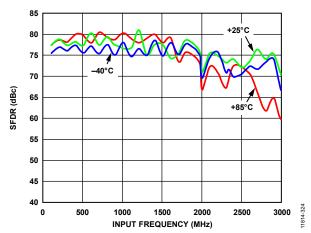

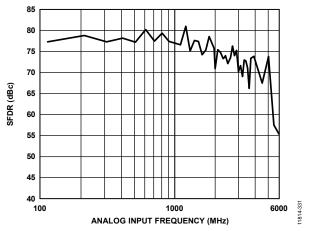

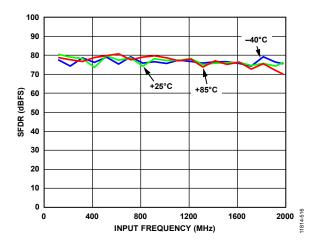

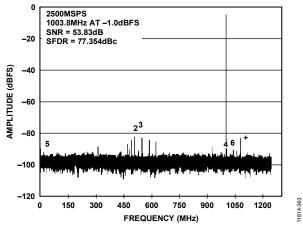

SFDR =  $79 \, dBc$ , AIN up to 1 GHz at  $-1 \, dBFS$ , 2.5 GSPS

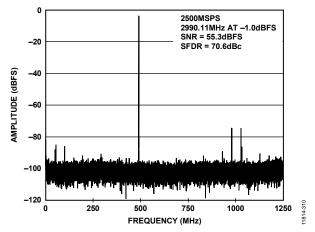

SFDR = 77 dBc, AIN up to 1.8 GHz at -1 dBFS, 2.5 GSPS

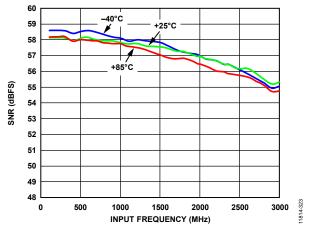

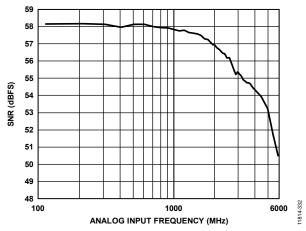

SNR = 57.6 dBFS, AIN up to 1 GHz at -1 dBFS, 2.5 GSPS

SNR = 57 dBFS, AIN up to 1.8 GHz at -1 dBFS, 2.5 GSPS

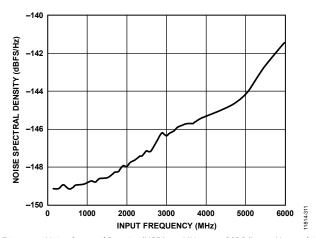

Noise spectral density =  $-149.5 \, dBFS/Hz$  at 2.5 GSPS

Differential analog input: 1.2 V p-p

Differential clock input

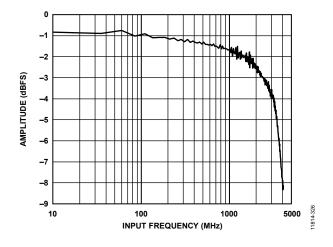

3.2 GHz analog input bandwidth, full power

High speed 6- or 8-lane JESD204B serial output at 2.6 GSPS

Subclass 1: 6.5 Gbps at 2.6 GSPS

Two independent decimate by 8 or decimate by 16 filters

with 10-bit NCOs

Supply voltages: 1.3 V, 2.5 V

**Serial port control**

Flexible digital output modes

**Built-in selectable digital test patterns**

**Timestamp feature**

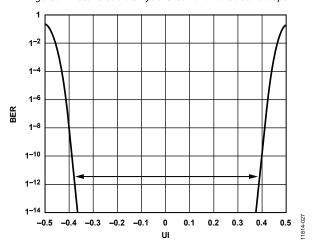

Conversion error rate  $< 10^{-15}$

#### **APPLICATIONS**

Spectrum analyzers

**Military communications**

Radar

High performance digital storage oscilloscopes

Active jamming/antijamming

**Electronic surveillance and countermeasures**

#### **GENERAL DESCRIPTION**

The AD9625 is a 12-bit monolithic sampling analog-to-digital converter (ADC) that operates at conversion rates of up to 2.6 giga samples per second (GSPS). This product is designed for sampling wide bandwidth analog signals up to the second Nyquist zone. The combination of wide input bandwidth, high sampling rate, and excellent linearity of the AD9625 is ideally suited for spectrum analyzers, data acquisition systems, and a wide assortment of military electronics applications, such as radar and electronic countermeasures.

The analog input, clock, and SYSREF± signals are differential inputs. The JESD204B-based high speed serialized output is configurable in a variety of one-, two-, four-, six-, or eight-lane configurations. The product is specified over the industrial temperature range of  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , measured at the case.

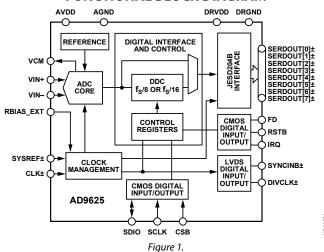

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **PRODUCT HIGHLIGHTS**

- 1. High performance: exceptional SFDR in high sample rate applications, direct RF sampling, and on-chip reference.

- 2. Flexible digital data output formats based on the JESD204B specification.

- Control path SPI interface port that supports various product features and functions, such as data formatting, gain, and offset calibration values.

## AD9625

## **TABLE OF CONTENTS**

| Features                                    |

|---------------------------------------------|

| Applications                                |

| Functional Block Diagram                    |

| General Description                         |

| Product Highlights                          |

| Revision History                            |

| Specifications                              |

| DC Specifications                           |

| AC Specifications5                          |

| Digital Specifications6                     |

| Switching Specifications                    |

| Timing Specifications                       |

| Absolute Maximum Ratings                    |

| Thermal Characteristics9                    |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

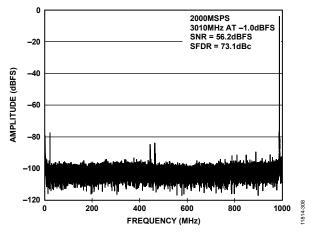

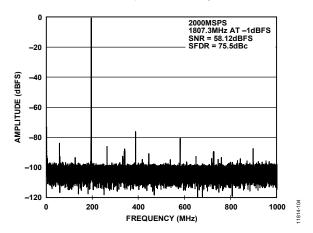

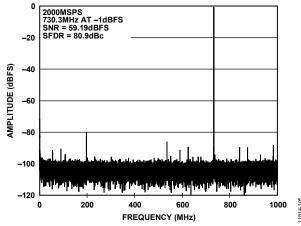

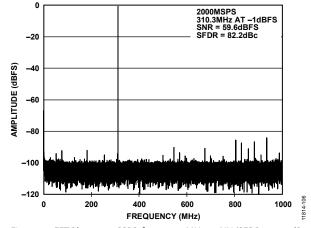

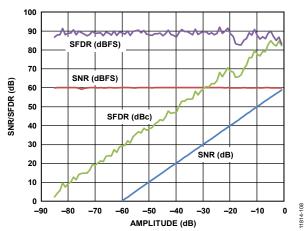

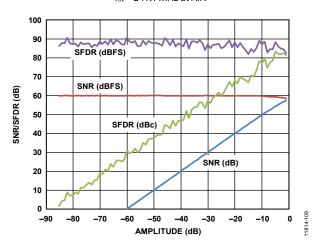

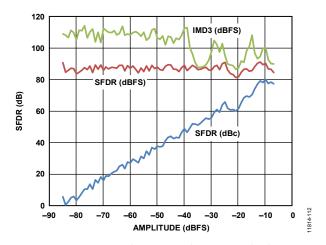

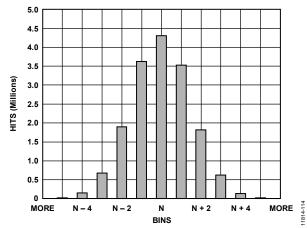

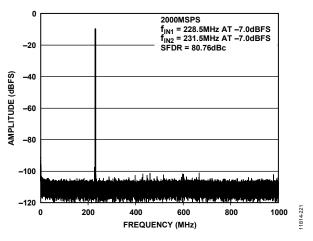

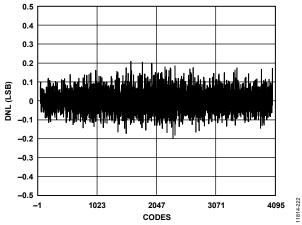

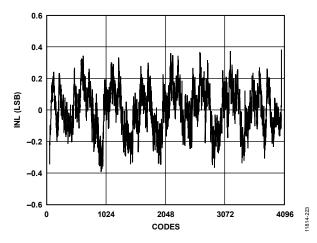

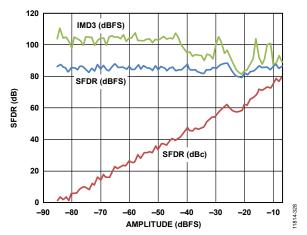

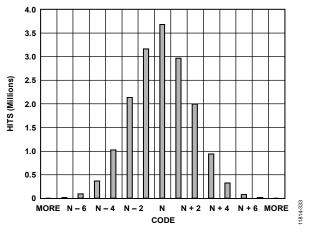

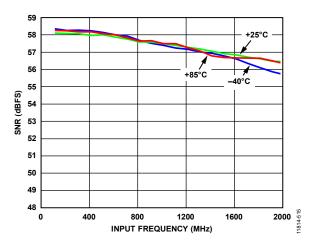

| AD9625-2.0                                  |

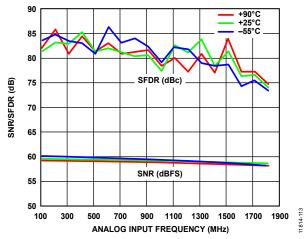

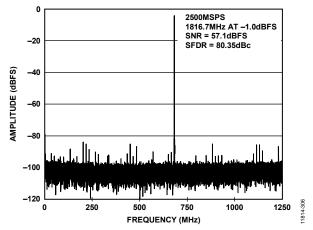

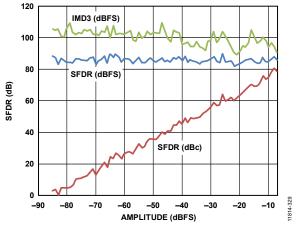

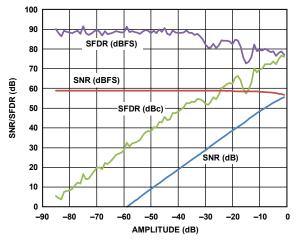

| AD9625-2.5                                  |

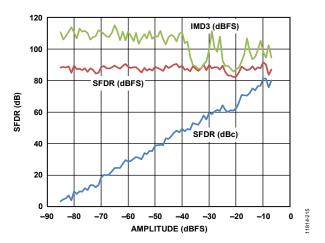

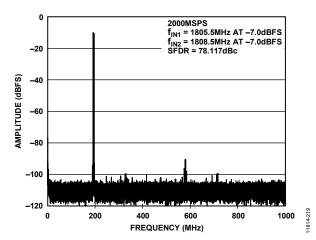

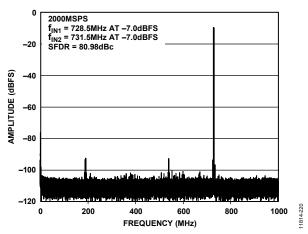

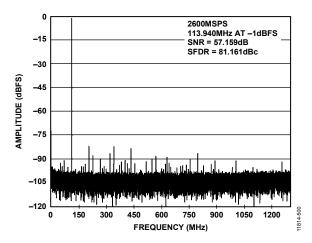

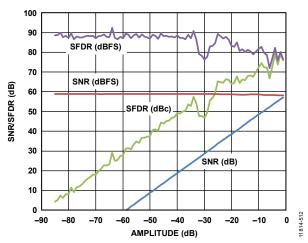

| AD9625-2.6                                  |

| Equivalent Test Circuits                    |

| Theory of Operation                         |

| ADC Architecture                            |

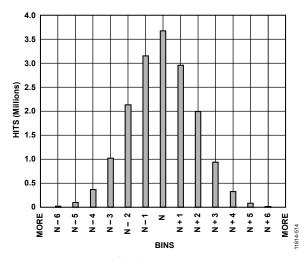

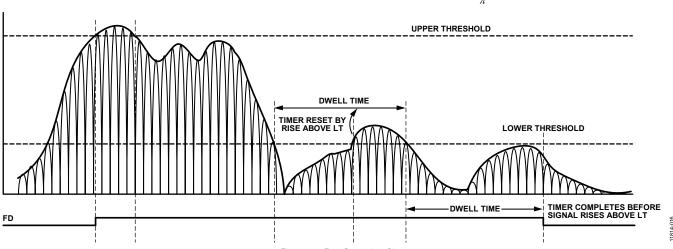

| Fast Detect                                 |

| Gain Threshold Operation                    |

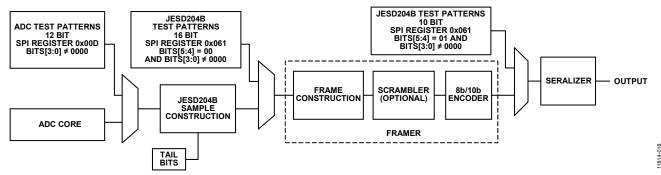

| Test Modes                                  |

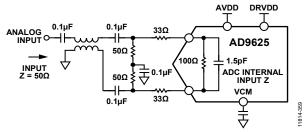

| Analog Input Considerations                 |

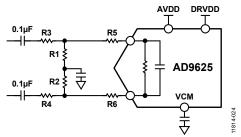

| Differential Input Configurations           |

| Using the ADA4961                           |

| DC Coupling32                               |

| Clock Input Considerations                  |

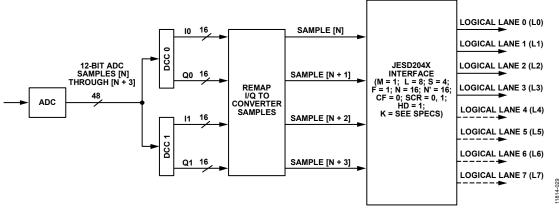

| Digital Downconverters (DDC)                |

| Frequency Synthesizer and Mixer             |

|                                             |

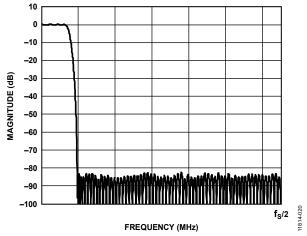

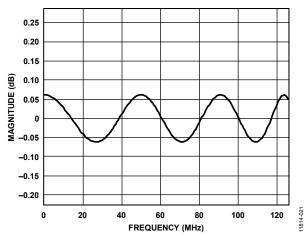

| High Bandwidth Decimator                 |

|------------------------------------------|

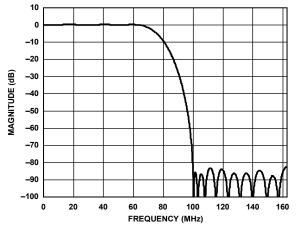

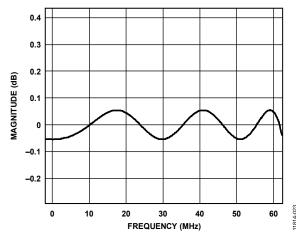

| Low Bandwidth Decimator                  |

| Digital Outputs                          |

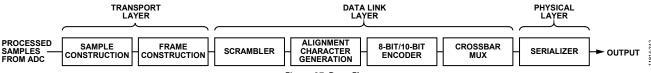

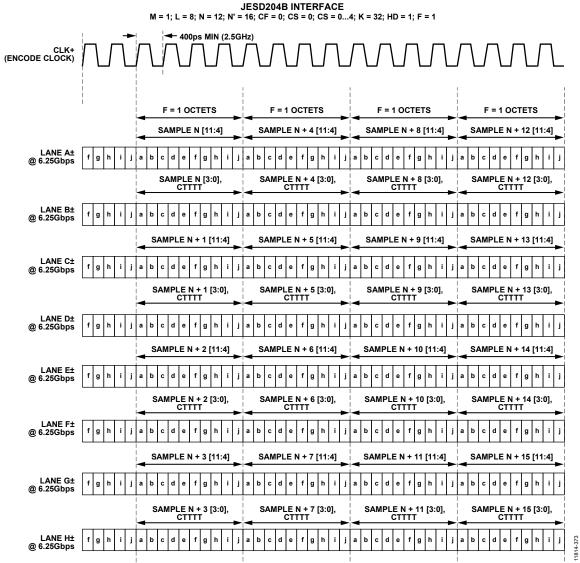

| Introduction to the JESD204B Interface   |

| Functional Overview                      |

| JESD204B Link Establishment              |

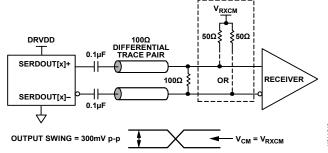

| Physical Layer Output                    |

| Scrambler                                |

| Tail Bits                                |

| DDC Modes (Single and Dual)              |

| CheckSum                                 |

| 8-Bit/10-Bit Encoder Control44           |

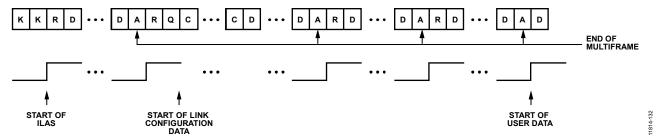

| Initial Lane Alignment Sequence (ILAS)44 |

| Lane Synchronization                     |

| JESD204B Application Layers              |

| Frame Alignment Character Insertion 51   |

| Thermal Considerations51                 |

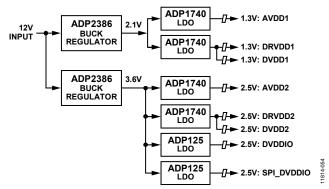

| Power Supply Considerations 51           |

| Serial Port Interface (SPI)              |

| Configuration Using the SPI52            |

| Hardware Interface                       |

| Memory Map                               |

| Reading the Memory Map Register53        |

| Memory Map Registers53                   |

| Applications Information                 |

| Design Guidelines                        |

| Power and Ground Recommendations71       |

| Clock Stability Considerations           |

| SPI Port71                               |

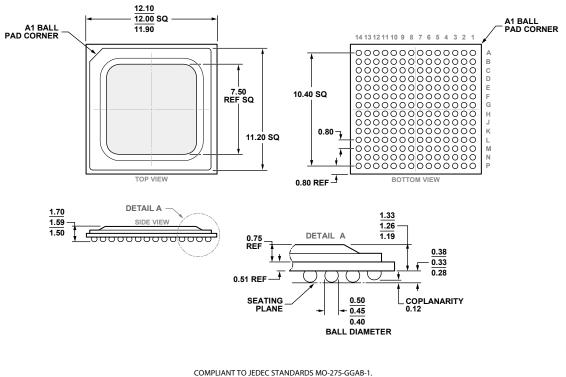

| Outline Dimensions                       |

| Ordering Guide72                         |

#### **REVISION HISTORY**

| 9/2016—Rev. B to Rev. C                                    |

|------------------------------------------------------------|

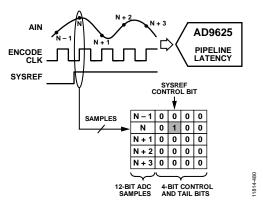

| Changes to ADC Output Control Bits on JESD204B Samples     |

| Section45                                                  |

| Changes to Table 9467                                      |

| Changes to Table 110 and Table 11169                       |

| Changes to Table 113 and Table 11470                       |

| Changes to the Clock Stability Considerations Section71    |

| Changes to Ordering Guide72                                |

| 5/2015—Rev. A to Rev. B                                    |

| Added AD9625-2.6Throughout                                 |

| Change to Figure 1                                         |

| Changes to Table 14                                        |

| Changes to Table 25                                        |

| Change to Figure 5                                         |

| Added Endnote 1, Table 8                                   |

| Added Endnote 2, Table 9                                   |

| Added AD9625-2.6 Section24                                 |

| Changes to Figure 61 and Figure 6327                       |

| Changes to Table 1130                                      |

| Added Using the ADA4961 Section30                          |

| Added Figure 77; Renumbered Sequentially, Figure 78,       |

| Figure 79, and Figure 8031                                 |

| Changes to Table 1234                                      |

| Changes to Low Bandwidth Decimator Section and Table 1336  |

| Changes to Table 2854                                      |

| Changes to Table 10769                                     |

| Changes to Ordering Guide72                                |

| 9/2014—Rev. 0 to Rev. A                                    |

| Added AD9625-2.5 Throughout                                |

| Changes to Features and General Description Sections       |

| Changes to Table 14                                        |

| Changes to Table 1                                         |

| Changes to Table 3                                         |

| Changes to Table 4                                         |

| Changes to Figure 3 and Figure 48                          |

| Changes to Table 69                                        |

| Changes to Pin K4; Figure 5, Table 8, and Table 910        |

| Added Typical Performance Characteristics Summary and      |

| Changes to Typical Performance Characteristics Summary and |

| Changes to Typical Ferrormance Characteristics             |

| Changes to Figure 45, Figure 49, and Figure 50; Added           |     |

|-----------------------------------------------------------------|-----|

| Figure 51 to Figure 54                                          | .23 |

| Changes to Gain Threshold Operation Section                     | .24 |

| Changes to Analog Input Considerations Section                  | .26 |

| Changes to Digital Downconverters (DDC) Section                 | .28 |

| Added Figure 68                                                 | .32 |

| Changes to Data Streaming Section; Added Link Setup             |     |

| Parameters Section                                              | .33 |

| Changes to Digital Outputs, Timing, and Controls Section an     | d   |

| Table 15                                                        | .34 |

| Changes to Table 16 and Table 17                                | .35 |

| Added Table 18                                                  | .36 |

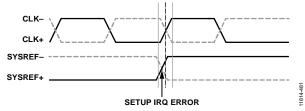

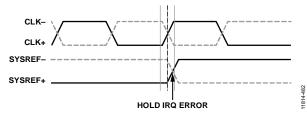

| Added Multichip Synchronization Using SYSREF± Timestam          | ıp, |

| Six Lane Output Mode, and SYSREF± Setup and Hold IRQ            |     |

| Sections                                                        | .39 |

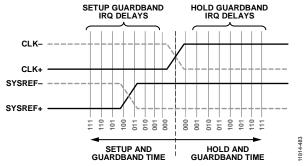

| Added IRQ Guardband Delays (SYSREF± Setup and Hold)             |     |

| Section                                                         | .40 |

| Added Using Rising/Falling Edges of CLK to Latch SYSREF±        |     |

| Section                                                         | .41 |

| Changes to Configuration Using the SPI Section                  | .46 |

| Changes to Transfer Register Map Section, Table 26, and         |     |

| Table 27                                                        | .47 |

| Changes to Table 28, Table 29, and Table 30                     | .48 |

| Changes to Table 33 and Table 34                                | .49 |

| Changes to Table 53                                             | .52 |

| Changes to Table 54                                             | .52 |

| Changes to Table 58                                             | .54 |

| Changes to Table 71                                             | .56 |

| Changes to Table 79 and Table 80                                | .57 |

| Changes to Table 81, Table 82, Table 83, Table 84, Table 85, ar | ıd  |

| Table 86                                                        | .58 |

| Changes to Table 89                                             | .59 |

| Changes to Table 92 and Table 93                                | .60 |

| Changes to Table 94, Table 97, and Table 98                     | .61 |

| Changes to Table 101 and Table 106                              |     |

| Added Table 107 and Table 108                                   | .63 |

| Added Table 115 and Table 116                                   | .64 |

| Added Applications Information Section                          | .65 |

| Changes to Ordering Guide                                       | .66 |

## **SPECIFICATIONS**

#### **DC SPECIFICATIONS**

AVDD1 = DVDD1 = DRVDD1 = 1.3 V, AVDD2 = DVDD2 = DRVDD2 = 2.5 V, specified maximum sampling rate, 1.2 V internal reference, AIN = -1.0 dBFS, default SPI settings, dc-coupled output data, unless otherwise noted.

Table 1.

|                                           | Test Conditions/                  |                          | AD9625-2.0 |          | AD9625-2.5 |       |         | AD9625-2.6 |       |         |       |                    |

|-------------------------------------------|-----------------------------------|--------------------------|------------|----------|------------|-------|---------|------------|-------|---------|-------|--------------------|

| Parameter                                 | Comments                          | Temperature <sup>1</sup> | Min        | Тур      | Max        | Min   | Тур     | Max        | Min   | Тур     | Max   | Unit               |

| RESOLUTION                                |                                   |                          | 12         |          |            | 12    |         |            | 12    |         |       | Bits               |

| ACCURACY                                  |                                   |                          |            |          |            |       |         |            |       |         |       |                    |

| No Missing Codes                          |                                   | Full                     | G          | iuarante | ed         | G     | uarante | ed         | G     | uarante | ed    |                    |

| Offset Error                              |                                   | Full                     | -7         | ±0.5     | +6.4       | -7    | ±0.5    | +6.4       | -8.5  | ±0.5    | +7.0  | LSB                |

| Gain Error                                |                                   | Full                     | -8         |          | +8         | -10.8 |         | +14.2      | -13.8 |         | +20.9 | %FSR               |

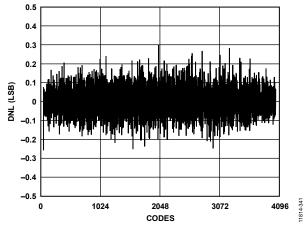

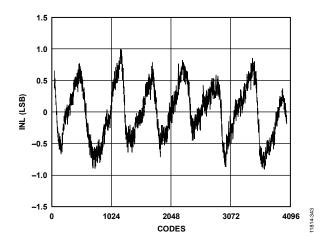

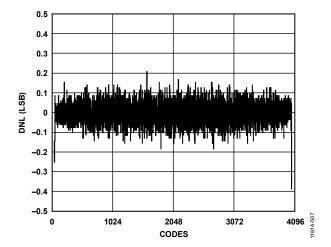

| Differential Nonlinearity (DNL)           |                                   | Full                     | -0.7       | ±0.3     | +0.7       | -0.5  | ±0.3    | +0.7       | -0.6  | ±0.3    | +0.7  | LSB                |

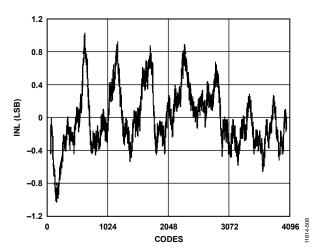

| Integral Nonlinearity (INL)               |                                   | Full                     | -3.6       | ±0.9     | +3.6       | -2.1  | ±1.0    | +2.1       | -2.7  | ±1.0    | +2.3  | LSB                |

| ANALOG INPUTS                             |                                   |                          |            |          |            |       |         |            |       |         |       |                    |

| Differential Input                        |                                   |                          |            |          |            |       |         |            |       |         |       |                    |

| Voltage Range                             | Internal V <sub>REF</sub> = 1.2 V | Full                     |            | 1.1      |            |       | 1       |            |       | 1       |       | V p-p              |

| Resistance                                |                                   | 25°C                     |            | 100      |            |       | 100     |            |       | 100     |       | Ω                  |

| Capacitance                               |                                   | 25°C                     |            | 1.5      |            |       | 1.5     |            |       | 1.5     |       | рF                 |

| Internal Common-Mode Voltage ( $V_{CM}$ ) |                                   | Full                     | 492        | 525      | 563        | 492   | 525     | 563        | 492   | 525     | 563   | mV                 |

| Analog Full-Power                         |                                   |                          |            |          |            |       |         |            |       |         |       |                    |

| Bandwidth <sup>2</sup>                    | Internal termination              | 25°C                     |            | 3.2      |            |       | 3.2     |            |       | 3.2     |       | GHz                |

| Input Referred Noise                      |                                   | 25°C                     |            | 2        |            |       | 2       |            |       | 2       |       | LSB <sub>RMS</sub> |

| POWER SUPPLIES                            |                                   |                          |            |          |            |       |         |            |       |         |       |                    |

| AVDD1                                     |                                   | Full                     | 1.26       | 1.3      | 1.32       | 1.26  | 1.3     | 1.32       | 1.26  | 1.3     | 1.32  | V                  |

| AVDD2                                     |                                   | Full                     | 2.4        | 2.5      | 2.6        | 2.4   | 2.5     | 2.6        | 2.4   | 2.5     | 2.6   | V                  |

| DRVDD1                                    |                                   | Full                     | 1.26       | 1.3      | 1.32       | 1.26  | 1.3     | 1.32       | 1.26  | 1.3     | 1.32  | V                  |

| DRVDD2                                    |                                   | Full                     | 2.4        | 2.5      | 2.6        | 2.4   | 2.5     | 2.6        | 2.4   | 2.5     | 2.6   | V                  |

| DVDD1                                     |                                   | Full                     | 1.26       | 1.3      | 1.32       | 1.26  | 1.3     | 1.32       | 1.26  | 1.3     | 1.32  | V                  |

| DVDD2                                     |                                   | Full                     | 2.4        | 2.5      | 2.6        | 2.4   | 2.5     | 2.6        | 2.4   | 2.5     | 2.6   | V                  |

| DVDDIO                                    |                                   | Full                     | 2.4        | 2.5      | 3.3        | 2.4   | 2.5     | 3.3        | 2.4   | 2.5     | 3.3   | V                  |

| SPI_VDDIO                                 |                                   | Full                     | 2.4        | 2.5      | 3.3        | 2.4   | 2.5     | 3.3        | 2.4   | 2.5     | 3.3   | V                  |

| I <sub>AVDD1</sub>                        |                                   | Full                     |            | 1120     | 1222       |       | 1250    | 1351       |       | 1267    | 1390  | mA                 |

| I <sub>AVDD2</sub>                        |                                   | Full                     |            | 383      | 460        |       | 427     | 491        |       | 432     | 492   | mA                 |

| I <sub>DRVDD1</sub>                       |                                   | Full                     |            | 456      | 470        |       | 476     | 518        |       | 497     | 544   | mA                 |

| I <sub>DRVDD2</sub>                       |                                   | Full                     |            | 9        | 10         |       | 9       | 10         |       | 9       | 10    | mA                 |

| I <sub>DVDD1</sub>                        |                                   | Full                     |            | 410      | 430        |       | 425     | 473        |       | 441     | 503   | mA                 |

| I <sub>DVDD2</sub>                        |                                   | Full                     |            | <1       |            |       | <1      |            |       | <1      |       | mA                 |

| IDVDDIO                                   |                                   | Full                     |            | <1       |            |       | <1      |            |       | <1      |       | mA                 |

| I <sub>SPI_VDDIO</sub>                    |                                   | Full                     |            | <1       |            |       | <1      |            |       | <1      |       | mA                 |

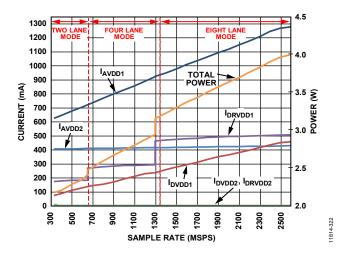

| Power Dissipation                         | Eight lane mode                   | Full                     |            | 3.48     | 3.8        |       | 3.90    | 4.2        |       | 4.0     | 4.3   | W                  |

| Power-Down Dissipation                    |                                   |                          |            | 125      | 3.8        |       | 125     |            |       | 125     |       | mW                 |

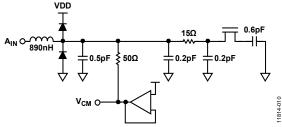

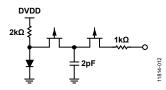

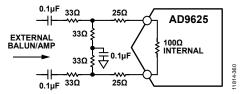

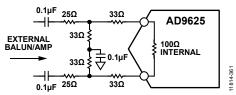

$<sup>^1</sup>$  Full temperature range is  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  measured at the case (Tc).  $^2$  See Figure 75 and Figure 76 for networks.

#### **AC SPECIFICATIONS**

AVDD1 = DVDD1 = DRVDD1 = 1.3 V, AVDD2 = DVDD2 = DRVDD2 = 2.5 V, specified maximum sampling, 1.2 V internal reference, AIN = -1.0 dBFS, sample clock input = 1.65 V p-p differential, default SPI settings, unless otherwise noted.

Table 2.

| -                                                            | Test Conditions/                   |                          | -    | ND9625-2 | .0  | P    | AD9625-2.5 |     | ,    | AD9625-2 | 2.6   |         |

|--------------------------------------------------------------|------------------------------------|--------------------------|------|----------|-----|------|------------|-----|------|----------|-------|---------|

| Parameter                                                    | Comments                           | Temperature <sup>1</sup> | Min  | Тур      | Max | Min  | Тур        | Max | Min  | Тур      | Max   | Unit    |

| SPEED GRADE                                                  |                                    |                          |      |          | 2.0 |      |            | 2.5 |      |          | 2.6   | GSPS    |

| ANALOG INPUT                                                 | Full scale                         | Full                     |      | 1.1      |     |      | 1.2        |     |      | 1.1      |       | V p-p   |

| NOISE DENSITY                                                |                                    | 25°C                     |      | -149.0   |     |      | -149.5     |     |      | -150.0   |       | dBFS/Hz |

| SIGNAL-TO-NOISE RATIO<br>(SNR)                               |                                    |                          |      |          |     |      |            |     |      |          |       |         |

| $f_{\text{IN}} = 100 \text{ MHz}$                            |                                    | 25°C                     |      | 59.5     |     |      | 58.3       |     |      | 58.1     |       | dBFS    |

| $f_{\text{IN}} = 500 \text{ MHz}$                            |                                    | 25°C                     |      | 59.4     |     |      | 58.0       |     |      | 58.0     |       | dBFS    |

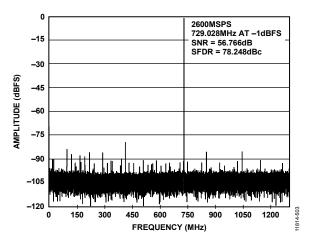

| $f_{IN} = 1000 \text{ MHz}$                                  |                                    | 25°C                     |      | 59.0     |     |      | 57.6       |     |      | 57.5     |       | dBFS    |

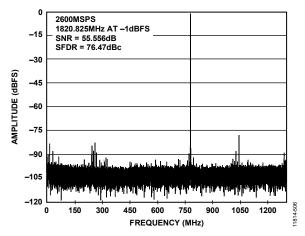

| $f_{IN} = 1800 \text{ MHz}$                                  |                                    | Full                     | 55.4 | 58.2     |     | 54.1 | 57.0       |     | 55.0 | 56.6     |       | dBFS    |

| SIGNAL-TO-NOISE AND<br>DISTORTION (SINAD)                    |                                    |                          |      |          |     |      |            |     |      |          |       |         |

| $f_{IN} = 100 \text{ MHz}$                                   |                                    | 25°C                     |      | 58.4     |     |      | 57.2       |     |      | 57.0     |       | dBc     |

| $f_{IN} = 500 \text{ MHz}$                                   |                                    | 25°C                     |      | 58.4     |     |      | 57.0       |     |      | 56.9     |       | dBc     |

| $f_{IN} = 1000 MHz$                                          |                                    | 25°C                     |      | 58.0     |     |      | 56.5       |     |      | 56.4     |       | dBc     |

| f <sub>IN</sub> = 1800 MHz                                   |                                    | Full                     | 54.1 | 57.2     |     | 53.1 | 55.9       |     | 53.9 | 55.6     |       | dBc     |

| EFFECTIVE NUMBER OF BITS (ENOB)                              |                                    |                          |      |          |     |      |            |     |      |          |       |         |

| $f_{IN} = 100 \text{ MHz}$                                   |                                    | 25°C                     |      | 9.4      |     |      | 9.2        |     |      | 9.2      |       | Bits    |

| $f_{IN} = 500 \text{ MHz}$                                   |                                    | 25°C                     |      | 9.4      |     |      | 9.2        |     |      | 9.2      |       | Bits    |

| $f_{IN} = 1000 \text{ MHz}$                                  |                                    | 25°C                     |      | 9.3      |     |      | 9.1        |     |      | 9.1      |       | Bits    |

| $f_{IN} = 1800 \text{ MHz}$                                  |                                    | 25°C                     |      | 9.2      |     |      | 9.0        |     |      | 8.9      |       | Bits    |

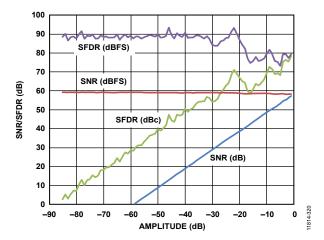

| SPURIOUS FREE<br>DYNAMIC RANGE<br>(SFDR)                     | Including second or thrid harmonic |                          |      |          |     |      |            |     |      |          |       |         |

| $f_{\text{IN}} = 100 \text{ MHz}$                            |                                    | 25°C                     |      | 80       |     |      | 77         |     |      | 80.5     |       | dBc     |

| $f_{\text{IN}} = 500 \text{ MHz}$                            |                                    | 25°C                     |      | 81       |     |      | 76         |     |      | 79.6     |       | dBc     |

| $f_{\text{IN}} = 1000 \text{ MHz}$                           |                                    | 25°C                     |      | 80       |     |      | 79         |     |      | 77.3     |       | dBc     |

| $f_{IN} = 1800 \text{ MHz}$                                  |                                    | Full                     | 67   | 76       |     | 70   | 77         |     | 65   | 75.4     |       | dBc     |

| WORST OTHER SPUR                                             | Excluding second or third harmonic |                          |      |          |     |      |            |     |      |          |       |         |

| $f_{IN} = 100 \text{ MHz}$                                   |                                    | 25°C                     |      | -80      |     |      | -77        |     |      | -81      |       | dBc     |

| $f_{IN} = 500 \text{ MHz}$                                   |                                    | 25°C                     |      | -86      |     |      | -76        |     |      | -83      |       | dBc     |

| $f_{IN} = 1000 \text{ MHz}$                                  |                                    | 25°C                     |      | -83      |     |      | -82        |     |      | -80      |       | dBc     |

| $f_{IN} = 1800 \text{ MHz}$                                  |                                    | Full                     |      | -85      | -73 |      | -78        | -70 |      | -78.0    | -66.0 | dBc     |

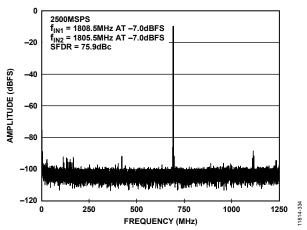

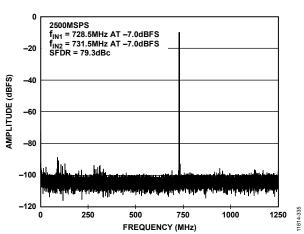

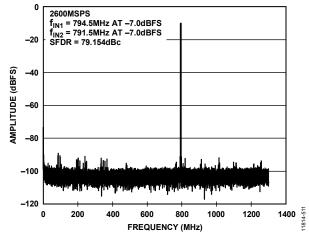

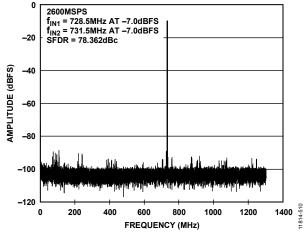

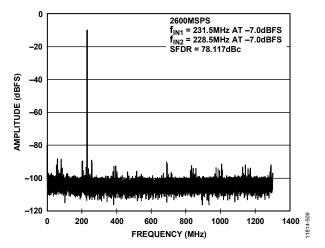

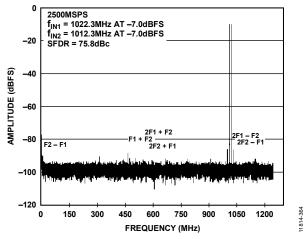

| TWO-TONE INTERMODULATION DISTORTION (IMD)                    | At –7 dBFS per tone                |                          |      |          |     |      |            |     |      |          |       |         |

| $f_{IN1} = 728.5 \text{ MHz}, f_{IN2} = 731.5 \text{ MHz}$   |                                    | 25°C                     |      | -82.8    |     |      | -81.2      |     |      | -78.3    |       | dBc     |

| f <sub>IN1</sub> = 1805.5 MHz, f <sub>IN2</sub> = 1808.5 MHz |                                    | 25°C                     |      | -77.6    |     |      | -76.3      |     |      | -77.7    |       | dBc     |

$<sup>^{1}</sup>$  Full temperature range is  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  measured at the case (Tc).

#### **DIGITAL SPECIFICATIONS**

AVDD1 = DVDD1 = DRVDD1 = 1.3 V, AVDD2 = DVDD2 = DRVDD2 = 2.5 V, specified maximum sampling rate, 1.2 V internal reference, AIN = -1.0 dBFS, default SPI settings, unless otherwise noted.

Table 3.

| Parameter                                                   | Temperature <sup>1</sup> | Min              | Тур             | Max  | Unit   |

|-------------------------------------------------------------|--------------------------|------------------|-----------------|------|--------|

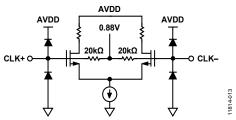

| CLOCK INPUTS (CLK+, CLK-)                                   |                          |                  |                 |      |        |

| Differential Input Voltage                                  | Full                     | 500              |                 | 1800 | mV p-p |

| Common-Mode Input Voltage                                   | Full                     |                  | 0.88            |      | V      |

| Input Resistance (Differential)                             | Full                     |                  | 40              |      | kΩ     |

| Input Capacitance                                           | Full                     |                  | 1.5             |      | pF     |

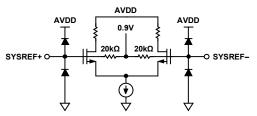

| SYSREF INPUTS (SYSREF+, SYSREF-)                            |                          |                  |                 |      |        |

| Differential Input Voltage                                  | Full                     | 500              |                 | 1800 | mV p-p |

| Common-Mode Input Voltage                                   | Full                     |                  | 0.88            |      | V      |

| Input Resistance (Differential)                             | Full                     |                  | 40              |      | kΩ     |

| Input Capacitance                                           | Full                     |                  | 1.5             |      | pF     |

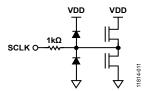

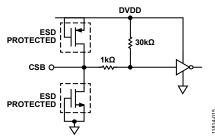

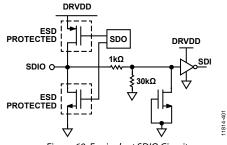

| LOGIC INPUTS (SDIO, SCLK, CSB)                              |                          |                  |                 |      |        |

| Logic Compliance                                            |                          |                  | CMOS            |      |        |

| Voltage                                                     |                          |                  |                 |      |        |

| Logic 1                                                     | Full                     | 0.8 × SPI_DVDDIO |                 |      | V      |

| Logic 0                                                     | Full                     | _                |                 | 0.5  | V      |

| Input Resistance                                            | Full                     |                  | 30              |      | kΩ     |

| Input Capacitance                                           | Full                     |                  | 0.5             |      | pF     |

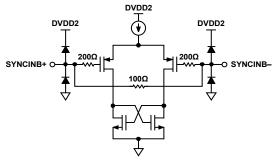

| SYNCB+/SYNCB- INPUT                                         |                          |                  |                 |      | 1      |

| Logic Compliance                                            | Full                     |                  | LVDS            |      |        |

| Input Voltage                                               |                          |                  | 2.00            |      |        |

| Differential                                                | Full                     | 250              |                 | 1200 | mV p-p |

| Common Mode                                                 | Full                     |                  | 1.2             | .200 | V      |

| Input Resistance (Differential)                             | Full                     |                  | 100             |      | Ω      |

| Input Capacitance                                           | Full                     |                  | 2.5             |      | pF     |

| LOGIC OUTPUT (SDIO)                                         | Tun                      |                  | 2.5             |      | Pi     |

| Logic Compliance                                            |                          |                  | CMOS            |      |        |

| Voltage                                                     |                          |                  | Cinos           |      |        |

| Logic 1 (I <sub>OH</sub> = 800 μA)                          | Full                     |                  | 0.8 × SPI_VDDIO |      | V      |

| Logic 0 ( $I_{OL} = 50 \mu A$ )                             | Full                     |                  | 0.3             |      | V      |

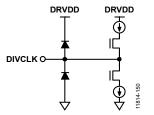

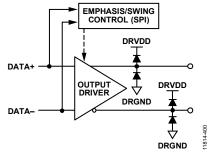

| DIGITAL OUTPUTS (SERDOUT[x]±)                               | 1 3                      |                  | 0.0             |      | +      |

| Compliance                                                  | Full                     |                  | CML             |      |        |

| Output Voltage                                              | T diii                   |                  | CIVIL           |      |        |

| Differential                                                | Full                     | 360              | 700             | 800  | mV p-p |

| Offset                                                      | Full                     | 300              | DRVDD/2         | 000  | mV p-p |

| Differential Return Loss (RL <sub>DIFF</sub> ) <sup>2</sup> | 25°C                     | 8                | DITVDD/2        |      | dB     |

| Common-Mode Return Loss (RL <sub>CM</sub> )                 | 25°C                     | 6                |                 |      | dB     |

| Differential Termination Impedance                          | 25°C                     |                  |                 | 100  | Ω      |

| RESET (RSTB)                                                | 25 0                     |                  |                 | 100  | +      |

| Voltage                                                     |                          |                  |                 |      |        |

| Logic 1                                                     | Full                     | 0.8 × DVDDIO     |                 |      | V      |

| Logic 0                                                     | Full                     | 0.0 \ 0.0000     |                 | 0.5  | V      |

| Input Resistance (Differential)                             | Full                     |                  | 20              | 0.5  | kΩ     |

| Input Resistance (Differential)  Input Capacitance          | Full                     |                  | 2.5             |      | pF     |

| FAST DETECT (FD), PWDN, AND INTERRUPT (IRQ)                 | i uii                    |                  | ۷.3             |      | Pi     |

|                                                             |                          |                  | CMOS            |      |        |

| Logic Compliance<br>Voltage                                 |                          |                  | CIVIOS          |      |        |

|                                                             | Full                     | 0.8 × DVDDIO     |                 |      | V      |

| Logic 1                                                     | Full<br>Full             | טוטטעע × א.ט     |                 | 0.5  | V      |

| Logic 0                                                     |                          |                  | 20              | 0.5  |        |

| Input Resistance (Differential)                             | Full                     |                  | 20              |      | kΩ     |

| Input Capacitance                                           | Full                     |                  | 2.5             |      | pF     |

$<sup>^1</sup>$  Full temperature range is  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  measured at the case (Tc).  $^2$  Differential and common-mode return loss measured from 100 MHz to 0.75  $\times$  baud rate.

#### **SWITCHING SPECIFICATIONS**

AVDD1 = DVDD1 = DRVDD1 = 1.3 V, AVDD2 = DVDD2 = DRVDD2 = 2.5 V, specified maximum sampling rate, 1.2 V internal reference, AIN = -1.0 dBFS, default SPI settings, unless otherwise noted.

Table 4.

| Parameter                                    | Test Conditions/Comments | Temperature <sup>1</sup> | Min              | Тур  | Max  | Unit         |

|----------------------------------------------|--------------------------|--------------------------|------------------|------|------|--------------|

| CLOCK (CLK)                                  |                          |                          |                  |      |      |              |

| Maximum Clock Rate                           |                          | Full                     |                  |      | 2600 | MSPS         |

| Minimum Clock Rate                           |                          | Full                     | 330 <sup>2</sup> |      |      | MSPS         |

| Clock Pulse Width High                       |                          | Full                     | $50 \pm 5$       |      |      | % duty cycle |

| Clock Pulse Width Low                        |                          | Full                     | $50 \pm 5$       |      |      | % duty cycle |

| SYSREF (SYSREF±) <sup>3</sup>                |                          |                          |                  |      |      |              |

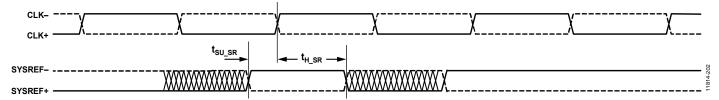

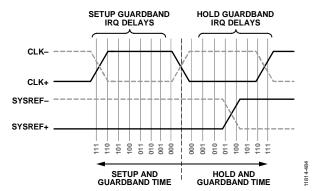

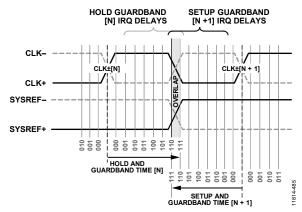

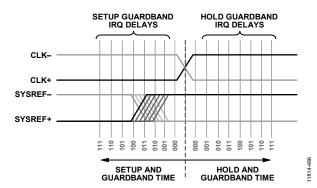

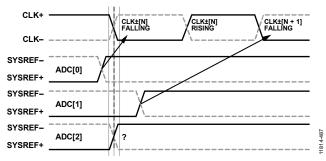

| Setup Time (t <sub>SU_SR</sub> )             |                          | 25°C                     |                  | +200 |      | ps           |

| Hold Time (t <sub>H_SR</sub> )               |                          | 25°C                     |                  | -100 |      | ps           |

| FAST DETECT OUTPUT (FD)                      |                          |                          |                  |      |      |              |

| Latency                                      |                          | Full                     |                  | 82   |      | Clock cycles |

| OUTPUT PARAMETERS (SERDOUT[x]±)              |                          |                          |                  |      |      |              |

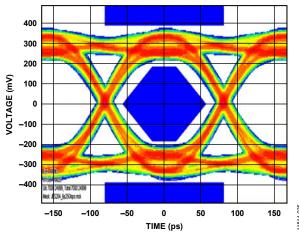

| Rise Time                                    |                          | 25°C                     |                  | 70   |      | ps           |

| Fall Time                                    |                          | 25°C                     |                  | 70   |      | ps           |

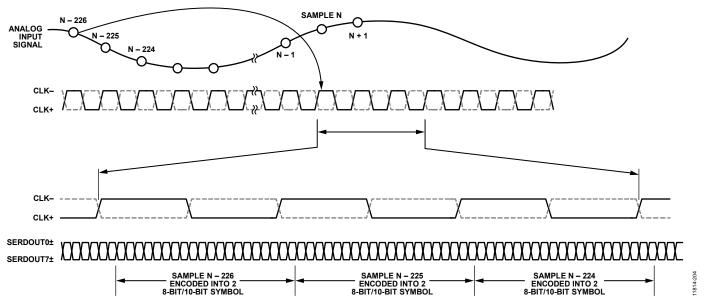

| Pipeline Latency                             | Eight lane mode          | 25°C                     |                  | 226  |      | Clock cycles |

| SYNCB± Falling Edge to First K.28 Characters |                          | 25°C                     | 4                |      |      | Multiframes  |

| CGS Phase K.28 Characters Duration           |                          | 25°C                     | 1                |      |      | Multiframes  |

| Differential Termination Resistance          |                          | 25℃                      |                  | 100  |      | Ω            |

| APERTURE                                     |                          |                          |                  |      |      |              |

| Delay                                        |                          | Full                     |                  | 200  |      | ps           |

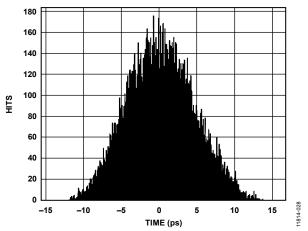

| Uncertainty (Jitter)                         |                          | Full                     |                  | 80   |      | fs rms       |

| Out-of-Range Recovery Time                   |                          | Full                     |                  | 2    |      | Clock cycles |

$<sup>^{1}</sup>$  Full temperature range is  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  measured at the case (Tc).

#### **TIMING SPECIFICATIONS**

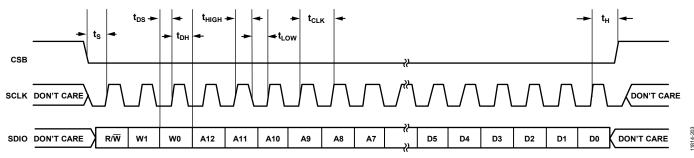

Table 5.

| Parameter              | Test Conditions/Comments                                                                              | Min | Тур | Max | Unit |

|------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SPITIMING REQUIREMENTS |                                                                                                       |     |     |     |      |

| t <sub>DS</sub>        | Setup time between the data and the rising edge of SCLK                                               | 2   |     |     | ns   |

| t <sub>DH</sub>        | Hold time between the data and the rising edge of SCLK                                                | 2   |     |     | ns   |

| t <sub>CLK</sub>       | Period of the SCLK                                                                                    | 40  |     |     | ns   |

| $t_S$                  | Setup time between CSB and SCLK                                                                       | 2   |     |     | ns   |

| tн                     | Hold time between CSB and SCLK                                                                        | 2   |     |     | ns   |

| t <sub>нібн</sub>      | Minimum period that SCLK should be in a logic high state                                              | 10  |     |     | ns   |

| t <sub>LOW</sub>       | Minimum period that SCLK should be in a logic low state                                               | 10  |     |     | ns   |

| t <sub>EN_SDIO</sub>   | Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge | 10  |     |     | ns   |

| t <sub>DIS_SDIO</sub>  | Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge  | 10  |     |     | ns   |

<sup>&</sup>lt;sup>2</sup> Must use a two-lane, generic output lane configuration for minimum sample rate. For more information, see the lane table in the JESD204B specification document.

<sup>&</sup>lt;sup>3</sup> SYSREF± setup and hold times are defined with respect to the rising SYSREF± edge and rising clock edge. Positive setup time leads the clock edge. Negative hold time also leads the clock edge.

#### **Timing Diagrams**

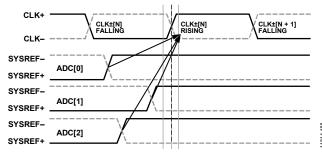

Figure 2. SYSREF± Setup and Hold Timing

Figure 3. Serial Port Interface Timing Diagram (MSB First)

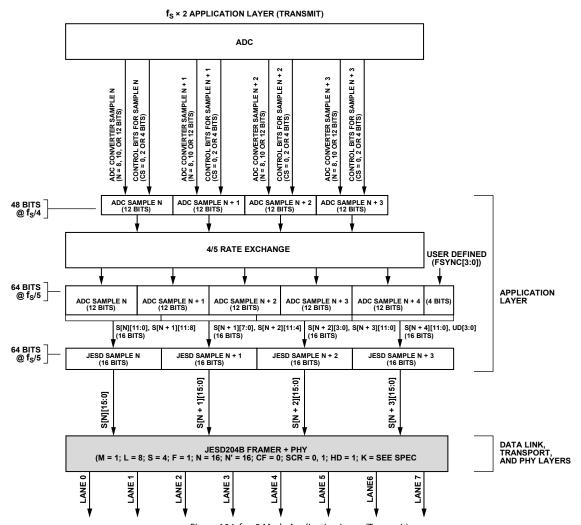

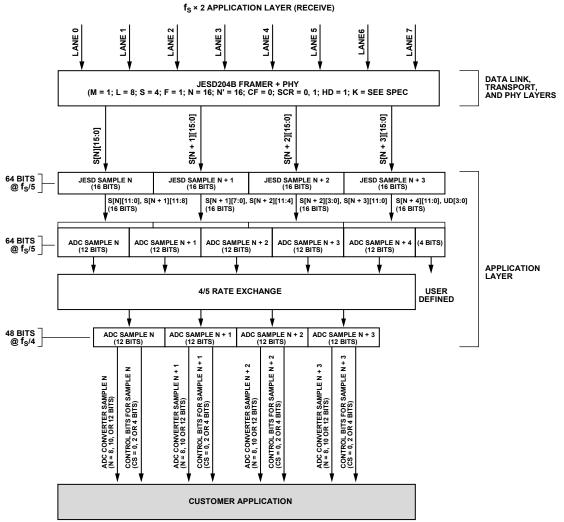

Figure 4. Data Output Timing for Eight Lane Mode

### **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Electrical  AVDD1 to AGND  AVDD2 to AGND  AVDD2 to DRGND  DRVDD1 to DRGND  DRVDD2 to DRGND  DVDD1 to DRGND  DVDD1 to DGND  DVD1 to DG | rable 6.                         |                             |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------|--|--|--|--|--|

| AVDD1 to AGND  AVDD2 to AGND  DRVDD1 to DRGND  DRVDD2 to DRGND  DVDD1 to DGND  SPI_VDDIO to DGND  AGND to DRGND  VIN± to AGND  VIM± to AGND  CLK± to AGND  SYSREF± to AGND  SYNCINB± to DRGND  SOLK to DRGND  DVDD1 to DRGND  SOLK to DRGND  SOLK to DRGND  DVDD1 to DRGND  SOLK to DRGND  SOLK to DRGND  SOLK to DRGND  DIVCLK± to DRGND  DIVCLK± to DRGND  DIVCLK± to DRGND  SERDOUT[x]± to DRGND  Environmental  Storage Temperature Range  Operating Case Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Parameter                        | Rating                      |  |  |  |  |  |

| AVDD2 to AGND  DRVDD1 to DRGND  DRVDD2 to DRGND  DVDD1 to DGND  O.3 V to +2.75 V  O.3 V to +1.32 V  O.3 V to +2.75 V  O.3 V to +2.75 V  O.3 V to +2.75 V  O.3 V to +3.63 V  O.3 V to +0.3 V  O.3 V to AVDD1 + 0.2 V  O.3 V to SPI_VDDIO + 0.2 V  O.3 V to SPI_VDDIO + 0.2 V  O.3 V to DVDDIO + 0.2 V  O.3 V to D | Electrical                       |                             |  |  |  |  |  |

| DRVDD1 to DRGND DRVDD2 to DRGND DVDD1 to DGND DVDD2 to DGND DVDD1 to DGND DVDD1 to DGND DVDD1 to DGND DVDD10 to DGND DVDD10 to DGND AGND to DRGND AGND to DRGND VIN± to AGND VCM to AGND CLK± to AGND SYSREF± to AGND SYSREF± to AGND SYNCINB± to DRGND SYNCINB± to DRGND DIVCLK± to DRGND CSB to DRGND DIVCLK± to DRGND SERDOUT[x]± to DRGND Environmental Storage Temperature Range Operating Case Temperature Range Operating Case Temperature Range  -0.3 V to +1.32 V -0.3 V to +1.32 V -0.3 V to +2.75 V -0.3 V to AVDD1 + 0.2 V -0.3 V to AVDD1 + 0.2 V -0.3 V to AVDD1 + 0.2 V -0.3 V to DRVDD2 + 0.2 V -0.3 V to SPI_VDDIO + 0.2 V -0.3 V to DVDDIO + 0.2 V -0.3 V to DVDDIO + 0.2 V -0.3 V to DVDDIO + 0.2 V -0.3 V to DRVDD2 + 0.2 V -0.3 V to DRVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AVDD1 to AGND                    | −0.3 V to +1.32 V           |  |  |  |  |  |

| DRVDD2 to DRGND  DVDD1 to DGND  DVDD2 to DGND  DVDD10 to DGND  SPI_VDDIO to DGND  AGND to DRGND  VIN± to AGND  VMON to AGND  CLK± to AGND  SYSREF± to AGND  SYNCINB± to DRGND  SOLK to DRGND  SOLK to DRGND  CSB to DRGND  CSB to DRGND  DIVCLK± to DRGND  SERDOUT[x]± to DRGND  Environmental  Storage Temperature Range  Operating Case Temperature Range  Operating Case Temperature Range  Operating Case Temperature Range  -0.3 V to +2.75 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to SPI_VDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AVDD2 to AGND                    | −0.3 V to +2.75 V           |  |  |  |  |  |

| DVDD1 to DGND DVDD2 to DGND DVDDIO to DGND DVDDIO to DGND SPI_VDDIO to DGND AGND to DRGND VIN± to AGND VCM to AGND CLK± to AGND SYSREF± to AGND SYNCINB± to DRGND SYNCINB± to DRGND SOLK to DRGND TRQ to DRGND TRQ to DRGND CSB to DRGND DIVCLK± to DRGND DIVCLK± to DRGND DIVCLK± to DRGND SERDOUT[x]± to DRGND DIVCLK± to DRGND SERDOUT[x]± to DRGND DIVCLK± to DRGND SERDOUT CASE TEmperature Range Operating Case Temperature Range Operating Case Temperature Range  -0.3 V to +1.32 V -0.3 V to +3.63 V -0.3 V to +0.3 V -0.3 V to AVDD1 + 0.2 V -0.3 V to DRVDD2 + 0.2 V -0.3 V to DRVDD2 + 0.2 V -0.3 V to SPI_VDDIO + 0.2 V -0.3 V to DVDDIO + 0.2 V -0.3 V to DVDDIO + 0.2 V -0.3 V to DRVDD2 + 0.2 V -0.3 V to DRVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DRVDD1 to DRGND                  | -0.3 V to +1.32 V           |  |  |  |  |  |

| DVDD2 to DGND DVDDIO to DGND DVDDIO to DGND  SPI_VDDIO to DGND AGND to DRGND VIN± to AGND VCM to AGND VMON to AGND CLK± to AGND SYSREF± to AGND SYNCINB± to DRGND SUIND TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DRVDD2 to DRGND                  | −0.3 V to +2.75 V           |  |  |  |  |  |

| DVDDIO to DGND  SPI_VDDIO to DGND  AGND to DRGND  VIN± to AGND  VCM to AGND  CLK± to AGND  SYSREF± to AGND  SYNCINB± to DRGND  SOLK to DRGND  DIVCLK± to DRGND  CSB to DRGND  DIVCLK± to DRGND  SERDOUT[x]± to DRGND  Environmental  Storage Temperature Range  Operating Case Temperature Range  Operating Case Temperature Range  -0.3 V to +3.63 V  -0.3 V to +3.63 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to SPI_VDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DVDD1 to DGND                    | −0.3 V to +1.32 V           |  |  |  |  |  |

| SPI_VDDIO to DGND       -0.3 V to +3.63 V         AGND to DRGND       -0.3 V to +0.3 V         VIN± to AGND       -0.3 V to AVDD1 + 0.2 V         VCM to AGND       -0.3 V to AVDD1 + 0.2 V         VMON to AGND       -0.3 V to AVDD1 + 0.2 V         CLK± to AGND       -0.3 V to AVDD1 + 0.2 V         SYSREF± to AGND       -0.3 V to AVDD1 + 0.2 V         SYNCINB± to DRGND       -0.3 V to DRVDD2 + 0.2 V         SCLK to DRGND       -0.3 V to SPI_VDDIO + 0.2 V         SDIO to DRGND       -0.3 V to DVDDIO + 0.2 V         RSTB to DRGND       -0.3 V to DVDDIO + 0.2 V         CSB to DRGND       -0.3 V to DVDDIO + 0.2 V         FD to DRGND       -0.3 V to DRVDD2 + 0.2 V         DIVCLK± to DRGND       -0.3 V to DRVDD2 + 0.2 V         SERDOUT[x]± to DRGND       -0.3 V to DRVDD1 + 0.2 V         Environmental       -0.3 V to DRVDD1 + 0.2 V         Coperating Case Temperature Range       -60°C to +150°C         Operating Case Temperature Range       -40°C to +85°C         (measured at case)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DVDD2 to DGND                    | −0.3 V to +2.75 V           |  |  |  |  |  |

| AGND to DRGND  VIN± to AGND  VCM to AGND  VCM to AGND  VMON to AGND  CLK± to AGND  SYSREF± to AGND  SYNCINB± to DRGND  SDIO to DRGND  RSTB to DRGND  CSB to DRGND  DIVCLK± to DRGND  DIVCLK± to DRGND  DIVCLK± to DRGND  SERDOUT[x]± to DRGND  Environmental  Storage Temperature Range  Operating Case Temperature Range  -0.3 V to AVDD1 + 0.2 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to AVDD1 + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to SPI_VDDIO + 0.2 V  -0.3 V to SPI_VDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDDIO to DGND                   | −0.3 V to +3.63 V           |  |  |  |  |  |

| VIN± to AGND       −0.3 V to AVDD1 + 0.2 V         VCM to AGND       −0.3 V to AVDD1 + 0.2 V         VMON to AGND       −0.3 V to AVDD1 + 0.2 V         CLK± to AGND       −0.3 V to AVDD1 + 0.2 V         SYSREF± to AGND       −0.3 V to AVDD1 + 0.2 V         SYNCINB± to DRGND       −0.3 V to DRVDD2 + 0.2 V         SDIO to DRGND       −0.3 V to SPI_VDDIO + 0.2 V         SDIO to DRGND       −0.3 V to DVDDIO + 0.2 V         RSTB to DRGND       −0.3 V to DVDDIO + 0.2 V         CSB to DRGND       −0.3 V to SPI_VDDIO + 0.2 V         FD to DRGND       −0.3 V to DVDDIO + 0.2 V         FD to DRGND       −0.3 V to DRVDD2 + 0.2 V         DIVCLK± to DRGND       −0.3 V to DRVDD2 + 0.2 V         SERDOUT[x]± to DRGND       −0.3 V to DRVDD1 + 0.2 V         Environmental       −0.3 V to DRVDD1 + 0.2 V         Coperating Case Temperature Range       −60°C to +150°C         Operating Case Temperature Range       −60°C to +85°C         (measured at case)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SPI_VDDIO to DGND                | −0.3 V to +3.63 V           |  |  |  |  |  |

| VCM to AGND         −0.3 V to AVDD1 + 0.2 V           VMON to AGND         −0.3 V to AVDD1 + 0.2 V           CLK± to AGND         −0.3 V to AVDD1 + 0.2 V           SYSREF± to AGND         −0.3 V to AVDD1 + 0.2 V           SYNCINB± to DRGND         −0.3 V to DRVDD2 + 0.2 V           SCLK to DRGND         −0.3 V to SPI_VDDIO + 0.2 V           SDIO to DRGND         −0.3 V to DVDDIO + 0.2 V           IRQ to DRGND         −0.3 V to DVDDIO + 0.2 V           CSB to DRGND         −0.3 V to DVDDIO + 0.2 V           FD to DRGND         −0.3 V to DVDDIO + 0.2 V           FD to DRGND         −0.3 V to DRVDD2 + 0.2 V           SERDOUT[x]± to DRGND         −0.3 V to DRVDD1 + 0.2 V           Environmental         −0.3 V to DRVDD1 + 0.2 V           Coperating Case Temperature Range         −60°C to +150°C           Operating Case Temperature Range         −60°C to +85°C           (measured at case)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AGND to DRGND                    | -0.3 V to +0.3 V            |  |  |  |  |  |

| VMON to AGND         −0.3 V to AVDD1 + 0.2 V           CLK± to AGND         −0.3 V to AVDD1 + 0.2 V           SYSREF± to AGND         −0.3 V to AVDD1 + 0.2 V           SYNCINB± to DRGND         −0.3 V to DRVDD2 + 0.2 V           SCLK to DRGND         −0.3 V to SPI_VDDIO + 0.2 V           SDIO to DRGND         −0.3 V to DVDDIO + 0.2 V           IRQ to DRGND         −0.3 V to DVDDIO + 0.2 V           RSTB to DRGND         −0.3 V to DVDDIO + 0.2 V           CSB to DRGND         −0.3 V to SPI_VDDIO + 0.2 V           FD to DRGND         −0.3 V to DRVDDIO + 0.2 V           DIVCLK± to DRGND         −0.3 V to DRVDD2 + 0.2 V           SERDOUT[x]± to DRGND         −0.3 V to DRVDD1 + 0.2 V           Environmental         −60°C to +150°C           Operating Case Temperature Range         −60°C to +85°C (measured at case)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VIN± to AGND                     | −0.3 V to AVDD1 + 0.2 V     |  |  |  |  |  |

| CLK± to AGND       -0.3 V to AVDD1 + 0.2 V         SYSREF± to AGND       -0.3 V to AVDD1 + 0.2 V         SYNCINB± to DRGND       -0.3 V to DRVDD2 + 0.2 V         SCLK to DRGND       -0.3 V to SPI_VDDIO + 0.2 V         SDIO to DRGND       -0.3 V to DVDDIO + 0.2 V         IRQ to DRGND       -0.3 V to DVDDIO + 0.2 V         CSB to DRGND       -0.3 V to SPI_VDDIO + 0.2 V         FD to DRGND       -0.3 V to SPI_VDDIO + 0.2 V         FD to DRGND       -0.3 V to DRVDD2 + 0.2 V         DIVCLK± to DRGND       -0.3 V to DRVDD2 + 0.2 V         SERDOUT[x]± to DRGND       -0.3 V to DRVDD1 + 0.2 V         Environmental       -0.3 V to DRVDD1 + 0.2 V         Coperating Case Temperature Range       -60°C to +150°C         Operating Case Temperature Range       -40°C to +85°C         (measured at case)       -40°C to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VCM to AGND                      | -0.3 V to AVDD1 + 0.2 V     |  |  |  |  |  |

| SYSREF± to AGND       −0.3 V to AVDD1 + 0.2 V         SYNCINB± to DRGND       −0.3 V to DRVDD2 + 0.2 V         SCLK to DRGND       −0.3 V to SPI_VDDIO + 0.2 V         SDIO to DRGND       −0.3 V to DVDDIO + 0.2 V         IRQ to DRGND       −0.3 V to DVDDIO + 0.2 V         RSTB to DRGND       −0.3 V to DVDDIO + 0.2 V         CSB to DRGND       −0.3 V to SPI_VDDIO + 0.2 V         FD to DRGND       −0.3 V to DVDDIO + 0.2 V         DIVCLK± to DRGND       −0.3 V to DRVDD2 + 0.2 V         SERDOUT[x]± to DRGND       −0.3 V to DRVDD1 + 0.2 V         Environmental       −0.3 V to DRVDD1 + 0.2 V         Coperating Case Temperature Range       −60°C to +150°C         Operating Case Temperature Range       −60°C to +85°C         (measured at case)       −0.3 V to AVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VMON to AGND                     | −0.3 V to AVDD1 + 0.2 V     |  |  |  |  |  |

| SYNCINB± to DRGND       −0.3 V to DRVDD2 + 0.2 V         SCLK to DRGND       −0.3 V to SPI_VDDIO + 0.2 V         SDIO to DRGND       −0.3 V to SPI_VDDIO + 0.2 V         IRQ to DRGND       −0.3 V to DVDDIO + 0.2 V         RSTB to DRGND       −0.3 V to DVDDIO + 0.2 V         CSB to DRGND       −0.3 V to SPI_VDDIO + 0.2 V         FD to DRGND       −0.3 V to DVDDIO + 0.2 V         DIVCLK± to DRGND       −0.3 V to DRVDD2 + 0.2 V         SERDOUT[x]± to DRGND       −0.3 V to DRVDD1 + 0.2 V         Environmental       −0.3 V to DRVDD1 + 0.2 V         Coperating Case Temperature Range       −60°C to +150°C         Operating Case Temperature Range       −40°C to +85°C         (measured at case)       −40°C to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CLK± to AGND                     | -0.3 V to AVDD1 + 0.2 V     |  |  |  |  |  |

| SCLK to DRGND       -0.3 V to SPI_VDDIO + 0.2 V         SDIO to DRGND       -0.3 V to SPI_VDDIO + 0.2 V         IRQ to DRGND       -0.3 V to DVDDIO + 0.2 V         RSTB to DRGND       -0.3 V to DVDDIO + 0.2 V         CSB to DRGND       -0.3 V to SPI_VDDIO + 0.2 V         FD to DRGND       -0.3 V to DVDDIO + 0.2 V         DIVCLK± to DRGND       -0.3 V to DRVDD2 + 0.2 V         SERDOUT[x]± to DRGND       -0.3 V to DRVDD1 + 0.2 V         Environmental       -0.3 V to DRVDD1 + 0.2 V         Storage Temperature Range       -60°C to +150°C         Operating Case Temperature Range       -40°C to +85°C         (measured at case)       -40°C to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SYSREF± to AGND                  | −0.3 V to AVDD1 + 0.2 V     |  |  |  |  |  |

| SDIO to DRGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SYNCINB± to DRGND                | -0.3 V to DRVDD2 + 0.2 V    |  |  |  |  |  |

| IRQ to DRGND  RSTB to DRGND  CSB to DRGND  FD to DRGND  DIVCLK± to DRGND  SERDOUT[x]± to DRGND  Environmental  Storage Temperature Range  Operating Case Temperature Range  -0.3 V to DVDDIO + 0.2 V  -0.3 V to SPI_VDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DRVDDI + 0.2 V  -0.3 V to DRVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SCLK to DRGND                    | -0.3 V to SPI_VDDIO + 0.2 V |  |  |  |  |  |

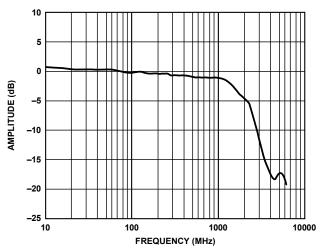

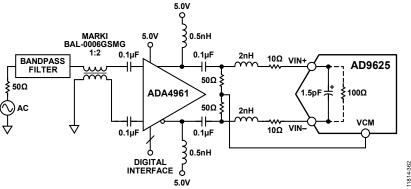

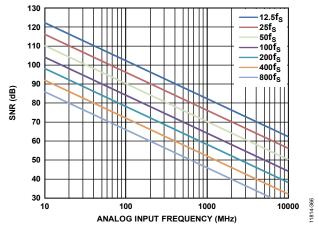

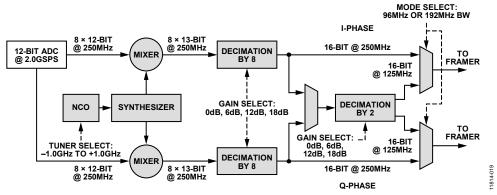

| RSTB to DRGND  CSB to DRGND  FD to DRGND  DIVCLK± to DRGND  SERDOUT[x]± to DRGND  Environmental  Storage Temperature Range  Operating Case Temperature Range  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DVDDIO + 0.2 V  -0.3 V to DRVDD2 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V  -0.3 V to DRVDD1 + 0.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SDIO to DRGND                    | -0.3 V to SPI_VDDIO + 0.2 V |  |  |  |  |  |