# AK5351

## Enhanced Dual bit $\Delta\Sigma$ 20bit ADC

### GENERAL DESCRIPTION

The AK5351 is a 20-bit, 64x oversampling rate(64fs), 2-channel A/D converter for stereo digital systems. The  $\Delta\Sigma$  modulator in the AK5351 uses the new developed Enhanced Dual bit architecture. This new architecture achieves the wider dynamic range, while keeping much the same superior distortion characteristics as the conventional Single bit way. The AK5351 is suitable for digital surround and Hi-Fi audio application such as Car-audio, MD, etc. Analog inputs of the AK5351 are normally Full-differential inputs, while they are also acceptable Single-ended inputs.

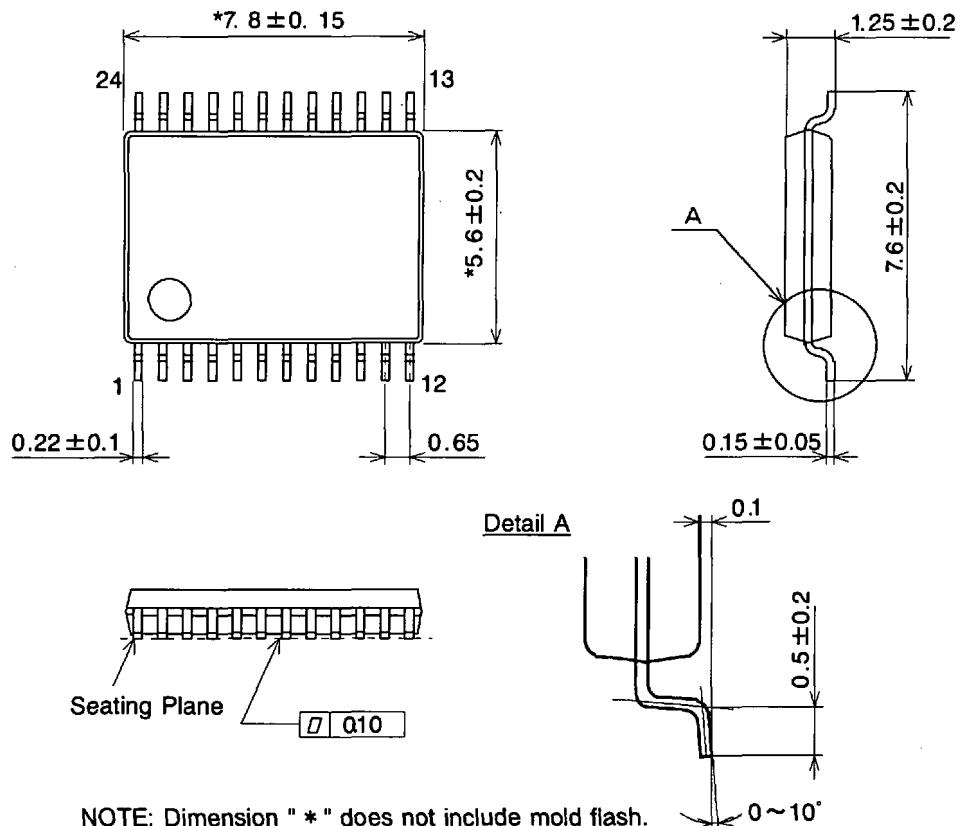

The AK5351 is available in a small 24pin VSOP package which will reduce your system space.

### FEATURES

- Full-differential / Single-ended inputs

- S/(N+D): 97dB

- DR, S/N: 103dB

- Linear phase digital filter

- Pass band: 0~22kHz(@fs=48kHz)

- Pass band ripple:  $\pm 0.005$ dB

- Stop band attenuation: 80dB

- Digital HPF for DC-offset cancel

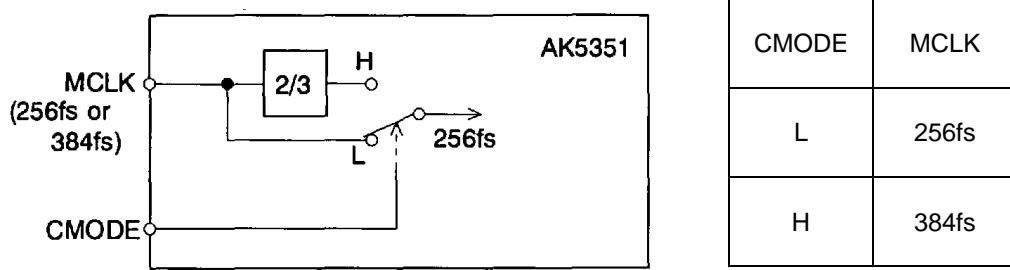

- Master clock: 256fs/384fs

- Power supply: 5V $\pm 10\%$

- Small package: 24pinVSOP

### ■ Ordering Guide

AK5351-VF      -40~85°C      24pin VSOP

AKD5351/2      Evaluation Board

### ■ Pin Layout

### ■ Replacement from AK5350 to AK5351

|                                  | AK5350                | AK5351                                             |

|----------------------------------|-----------------------|----------------------------------------------------|

| Package                          | 28VSOP                | 24VSOP<br>*)Interchangeable with AK5350            |

| Analog Inputs Voltage            | $\pm 3.47\text{Vp-p}$ | $\pm 2.10\text{Vp-p}$<br>*)Acceptable Single-ended |

| f <sub>c</sub> of HPF(@fs=48kHz) | 7Hz                   | 1Hz                                                |

| SCLK                             | $\sim 64\text{fs}$    | $\sim 128\text{fs}$                                |

## PIN/FUNCTION

| No. | Pin Name        | I/O | FUNCTION                                                                                                                                                                                                                                                                          |

|-----|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AINR+           | I   | Right channel analog positive input pin                                                                                                                                                                                                                                           |

| 2   | AINR-           | I   | Right channel analog negative input pin                                                                                                                                                                                                                                           |

| 3   | VREF            | O   | Voltage Reference output pin (VA-2.6V)<br>Normally connected to VA with a 0.1uF ceramic capacitor in parallel with a 10uF electrolytic capacitor.                                                                                                                                 |

| 4   | VA              | -   | Analog section Analog Power Supply, +5V                                                                                                                                                                                                                                           |

| 5   | AGND            | -   | Analog section Analog Ground                                                                                                                                                                                                                                                      |

| 6   | AINL+           | I   | Left channel analog positive input pin                                                                                                                                                                                                                                            |

| 7   | AINL-           | I   | Left channel analog negative input pin                                                                                                                                                                                                                                            |

| 8   | TST1            |     | Test pin (Pull-down pin)                                                                                                                                                                                                                                                          |

| 10  | TST2            |     | Should be left floating.                                                                                                                                                                                                                                                          |

| 11  | TST3            |     |                                                                                                                                                                                                                                                                                   |

| 14  | TST4            |     |                                                                                                                                                                                                                                                                                   |

| 9   | HPFE            | I   | High Pass Filter Enable pin (Pull-up pin)<br>"H": ON<br>"L": OFF                                                                                                                                                                                                                  |

| 12  | VD              | -   | Digital section Digital Power Supply pin, +5V                                                                                                                                                                                                                                     |

| 13  | DGND            | -   | Digital section Digital Ground pin                                                                                                                                                                                                                                                |

| 16  | $\overline{PD}$ | I   | Power Down pin<br>"L" brings the device into power-down mode. Must be done once after power-on.                                                                                                                                                                                   |

| 17  | MCLK            | I   | Master Clock input pin<br>CMODE="H":384fs<br>CMODE="L":256fs                                                                                                                                                                                                                      |

| 18  | SCLK            | I/O | Serial Data Clock pin<br>Data is clocked out at the falling edge of SCLK.<br>Slave mode: 64fs clock is input usually.<br>Master mode: SCLK outputs a 64fs clock.<br>SCLK stays low during the power-down mode( $\overline{PD}="L"$ ).                                             |

| 19  | LRCK            | I/O | L/R Channel Clock Select pin<br>Slave mode: An fs clock is fed to this LRCK pin.<br>Master mode: LRCK output an fs clock.<br>LRCK goes "H" at SMODE2="L" and "L" at SMODE2="H" during reset when SMODE1 "H".                                                                      |

| 20  | FSYNC           | I/O | Frame Synchronization Signal pin<br>Slave mode: When "H", data bits are clocked out on SDATA.<br>As I <sup>2</sup> S slave mode ignores FSYNC, it should hold "L" or "H".<br>Master mode: FSYNC outputs 2fs clock.<br>Stay low during the power-down mode( $\overline{PD}="L"$ ). |

|          |                    |   |                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21       | SDATA              | O | Serial Data Output pin<br>Data are output with MSB first, in 2's complement format.<br>After 20 bits are output it turns to "L". It also remains "L" at a power-down mode(PD="L").                                                                                                                                                                       |

| 22       | CMODE              | I | Master Clock Selection pin<br>"L": MCLK=256fs<br>"H": MCLK=384fs                                                                                                                                                                                                                                                                                         |

| 23<br>15 | S MODE1<br>S MODE2 | I | Serial Interface Mode Select pin<br>Defines the directions of LRCK, SCLK and FSYNC pins and Output Data Format. S MODE2 is pull-down pin.<br>S MODE1 S MODE2 MODE LRCK<br>L L Slave mode: MSB justified : H/L<br>H L Master mode: Similar to I <sup>2</sup> S : H/L<br>L H Slave mode: I <sup>2</sup> S : L/H<br>H H Master mode: I <sup>2</sup> S : L/H |

| 24       | VB                 | - | Substrate Power Supply, +5V                                                                                                                                                                                                                                                                                                                              |

|                                 |

|---------------------------------|

| <b>ABSOLUTE MAXIMUM RATINGS</b> |

|---------------------------------|

(AGND,DGND=0V; Note 1 )

| Parameter                                                     | Symbol | min  | max        | Units |

|---------------------------------------------------------------|--------|------|------------|-------|

| DC Power Supply: Analog Power(VA pin)                         | VA     | -0.3 | 6.0        | V     |

| Digital Power(VD pin) (Note 2 )                               | VD     | -0.3 | 6.0/VB+0.3 | V     |

| Substrate Power(VB pin)                                       | VB     | -0.3 | 6.0        |       |

| Input Current (Any pin except supplies)                       | IIN    | -    | $\pm 10$   | mA    |

| Analog Input Voltage<br>AINL+,AINL-,AINR+,AINR-pins (Note 2 ) | VINA   | -0.3 | 6.0/VA+0.3 | V     |

| Digital Input Voltage (Note 2 )                               | VIND   | -0.3 | 6.0/VB+0.3 | V     |

| Ambient Temperature                                           | Ta     | -40  | 85         | °C    |

| Storage Temperature                                           | Tstg   | -65  | 150        | °C    |

Note 1 : All voltage with respect to ground.

Note 2 : Absolute maximum value is the highest voltage in 6.0V, VA+0.3V and VB+0.3V.

WARNING: Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

|                                         |

|-----------------------------------------|

| <b>RECOMMENDED OPERATING CONDITIONS</b> |

|-----------------------------------------|

(AGND,DGND=0V; Note 1 )

| Parameter                       | Symbol | min  | typ | max  | Units |

|---------------------------------|--------|------|-----|------|-------|

| DC Power Supplies: Analog Power | VA     | 4.50 | 5.0 | 5.50 | V     |

| Digital Power(VD pin)           | VD     | 4.50 | 5.0 | VB   | V     |

| (VB pin) (Note 3 )              | VB     | 4.50 | 5.0 | 5.50 | V     |

Note 1 : All voltages with respect to ground.

Note 3 : The VA and VB are connected together through the chip substrate and have several ohms resistance. The VA and VB should be powered at the same time or earlier than VD.

\* AKM assumes no responsibility for the usage beyond the conditions in this data sheet.

## ANALOG CHARACTERISTICS

(Ta=25°C; VA,VD,VB=5.0V; fs=48kHz; 20bit; Input signal frequency=1kHz,

Measurement Bandwidth=10Hz~20kHz; unless otherwise specified.)

| Parameter                                                    | min   | typ   | max   | Units  |

|--------------------------------------------------------------|-------|-------|-------|--------|

| Resolution                                                   |       | 20    |       | Bits   |

| Analog Input Characteristics (Analog source impedance: 330Ω) |       |       |       |        |

| S/(N+D) (Note 4)                                             | 88    | 97    |       | dB     |

| Dynamic Range (A-weighted) (Note 5)                          | 97    | 103   |       | dB     |

| S/N (A-weighted) (Note 6)                                    | 97    | 103   |       | dB     |

| Interchannel Isolation (f=1kHz)                              | 100   | 120   |       | dB     |

| Interchannel Gain Mismatch                                   |       | 0.1   | 0.3   | dB     |

| Gain drift                                                   |       | ±200  |       | ppm/°C |

| Input Voltage Range                                          | ±1.97 | ±2.10 | ±2.23 | Vp-p   |

| Input Impedance                                              | 30    | 50    |       | kΩ     |

| Power Supplies                                               |       |       |       |        |

| Power Supply Current (Note 7)                                |       |       |       |        |

| Normal Operation (PD="H")                                    |       |       |       |        |

| VA+VB                                                        | 15    | 25    |       | mA     |

| VD                                                           | 6     | 9     |       | mA     |

| Power-Down mode (PD="L")                                     |       |       |       |        |

| VA+VB                                                        | 20    |       |       | uA     |

| VD                                                           | 10    |       |       | uA     |

| Power Consumption (Note 7)                                   |       |       |       |        |

| Normal Operation                                             | 105   | 170   |       | mW     |

| Power-Down mode                                              | 150   |       |       | uW     |

| Power Supply Rejection Ratio                                 | 50    |       |       | dB     |

Note 4 : The ratio of the rms value of the signal to the sum of all other spectral components up to 20kHz except for the signal (included harmonic component, excluded DC component, analog input signal is -0.5dB). Inversed of THD+N.

Note 5 : S/(N+D) with an input signal of 60dB below full-scale.

Note 6 : When using only 20kHzLPF, S/N and DR are 99dB(typ.). When using CCIR-ARM filter, S/N is 99dB(typ.)

Note 7 : Almost no current is supplied from VB pin.

|                                       |

|---------------------------------------|

| <b>DIGITAL FILTER CHARACTERISTICS</b> |

|---------------------------------------|

(Ta=25°C; VA,VD,VB=5.0V±10%; fs=48kHz)

| Low Pass Filter characteristics         |                    | Symbol | min  | typ  | max    | Units |

|-----------------------------------------|--------------------|--------|------|------|--------|-------|

| Passband                                | -0.005dB (Note 8 ) | PB     | 0    |      | 21.5   | kHz   |

|                                         | -0.02dB            |        |      |      | 21.768 |       |

|                                         | -0.06dB            |        |      |      | 22.0   |       |

| Stopband                                | (Note 9 )          | SB     | 26.5 |      |        | kHz   |

| Passband Ripple                         | (Note 10 )         | PR     |      |      | ±0.005 | dB    |

| Stopband Attenuation (Note 9 ,Note 11 ) |                    | SR     | 80   |      |        | dB    |

| Group Delay Distortion                  |                    | Δ GD   |      |      | 0      | us    |

| Group Delay                             | (Note 12 )         | GD     |      | 29.3 |        | 1/fs  |

| High Pass Filter characteristics        |                    |        |      |      |        |       |

| Frequency Response                      | -3dB(Note 8 )      | FR     |      | 1.0  |        | Hz    |

|                                         | -0.5dB             |        |      | 2.9  |        | Hz    |

|                                         | -0.1dB             |        |      | 6.5  |        | Hz    |

Note 8 : These frequencies scale with the sampling frequency(fs).

Note 9 : Stopband is 26.5kHz to 3.0455MHz at fs=48kHz.

Note 10 : Passband is DC to 21.5kHz at fs=48kHz.

Note 11 : The analog modulator samples the input at 3.072MHz for a system sampling rate of fs=48kHz. These is no rejection of input signals at those bandwidths which are multiples of the sampling frequency (n x 3.072MHz ±22kHz ;n=0,1,2,3...).

Note 12 : The calculation delay time occurred by digital filtering. This is the time from the input of analog signal to setting the 20bit data of both channels to the output registers. GD=29.3/fs.

|                                   |

|-----------------------------------|

| <b>ELECTRICAL CHARACTERISTICS</b> |

|-----------------------------------|

■ Digital Characteristics

(Ta=25°C; VA,VD,VB=5.0V±10%)

| Parameter                        | Symbol | min    | typ | max   | Units |

|----------------------------------|--------|--------|-----|-------|-------|

| High-Level Input voltage         | VIH    | 70%VD  | -   | -     | V     |

| Low-Level Input voltage          | VIL    | -      | -   | 30%VD | V     |

| High-Level Output voltage        | VOH    | VD-0.1 | -   | -     | V     |

| Low-Level Output voltage         | VOL    | -      | -   | 0.1   | V     |

| Input Leakage Current (Note 13 ) | Iin    | -      | -   | ±10   | uA    |

Note 13 : Except for pull-down and pull-up pins. TST1, TST2, TST3, TST4, SMODE2 pins have internal pull-down device, HPFE pin has internal pull-up devive(Typ. 50kΩ)

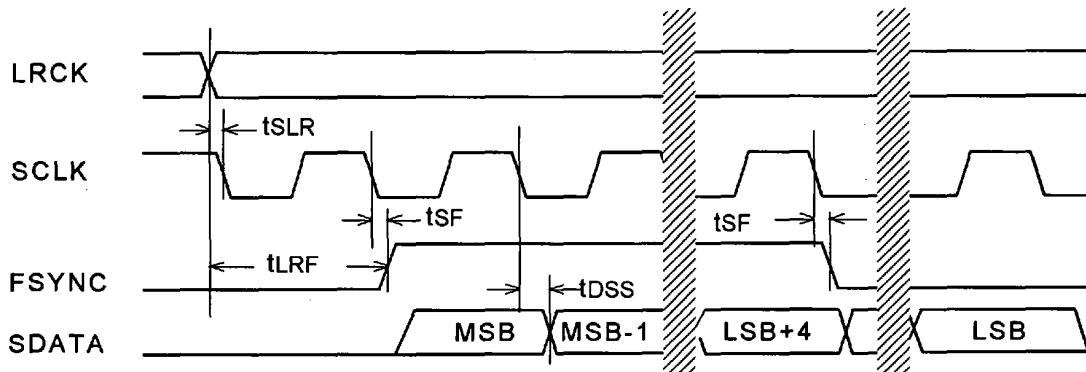

## ■ SWITCHING CHARACTERISTICS

(Ta=25°C; VA,VD,VB=5.0V±10%; CL=20pF)

| Parameter                                | Symbol | min   | typ   | max   | Unit |

|------------------------------------------|--------|-------|-------|-------|------|

| Control Clock Frequency                  |        |       |       |       |      |

| Master Clock 256fs:                      |        |       |       |       |      |

| Pulse width Low                          | tCLKL  | 30.0  |       |       | ns   |

| Pulse width High                         | tCLKH  | 30.0  |       |       | ns   |

| 384fs:                                   |        |       |       |       |      |

| Pulse width Low                          | tCLKL  | 20.0  |       |       | ns   |

| Pulse width High                         | tCLKH  | 20.0  |       |       | ns   |

| Serial Data Output Clock                 | fSLK   |       | 3.072 | 6.912 | MHz  |

| Channel Select Clock(Sampling Frequency) | fs     | 8     | 48    | 54    | kHz  |

| Duty Cycle                               |        | 25    |       | 75    | %    |

| Serial Interface Timing (Note 14)        |        |       |       |       |      |

| Slave Mode(SMODE1="L")                   |        |       |       |       |      |

| SCLK Period                              | tSLK   | 144.7 |       |       | ns   |

| SCLK Pulse width Low                     | tSLKL  | 65    |       |       | ns   |

| Pulse width High                         | tSLKH  | 65    |       |       | ns   |

| SCLK Rising to LRCK Edge (Note 15)       | tSHLR  | 30    |       |       | ns   |

| LRCK Edge to SCLK Rising (Note 15)       | tLRSH  | 30    |       |       | ns   |

| LRCK Edge to SDATA MSB Valid             | tDLR   |       |       | 50    | ns   |

| SCLK Falling to SDATA Valid              | tDSS   |       |       | 50    | ns   |

| SCLK Rising to FSYNC Edge (Note 15)      | tSHF   | 30    |       |       | ns   |

| FSYNC Edge to SCLK Rising (Note 15)      | tFSH   | 30    |       |       | ns   |

| Master Mode(SMODE1="H")                  |        |       |       |       |      |

| SCLK Frequency                           | fSLK   |       | 64fs  |       | Hz   |

| Duty Cycle                               |        |       | 50    |       | %    |

| FSYNC Frequency                          | fFSYNC |       | 2fs   |       | Hz   |

| Duty Cycle                               |        |       | 50    |       | %    |

| SCLK Falling to LRCK Edge                | tSLR   | -20   |       | 20    | ns   |

| LRCK Edge to FSYNC Rising                | tLRF   |       | 1     |       | tSLK |

| SCLK Falling to SDATA Valid              | tDSS   |       |       | 50    | ns   |

| SCLK Falling to FSYNC Edge               | tsF    | -20   |       | 20    | ns   |

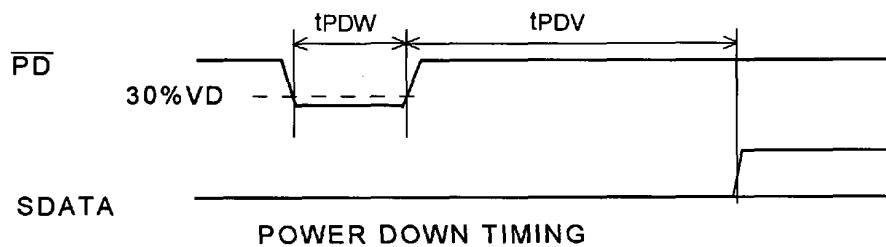

| Power down timing                        |        |       |       |       |      |

| PD Pulse width                           | tPDW   | 150   |       |       | ns   |

| PD Rising to SDATA Valid (Note 16)       | tPDV   |       | 516   |       | 1/fs |

Note 14 : Refer to Serial Data Interface.

Note 15 : Specified LRCK and FSYNC edges not to coincide with the rising edges of SCLK.

Note 16 : The number of LRCK rising edges after  $\overline{PD}$  brought high. The value is in master mode.

In slave mode it becomes one LRCK clock(1/fs) longer.

## ■ Timing Chart

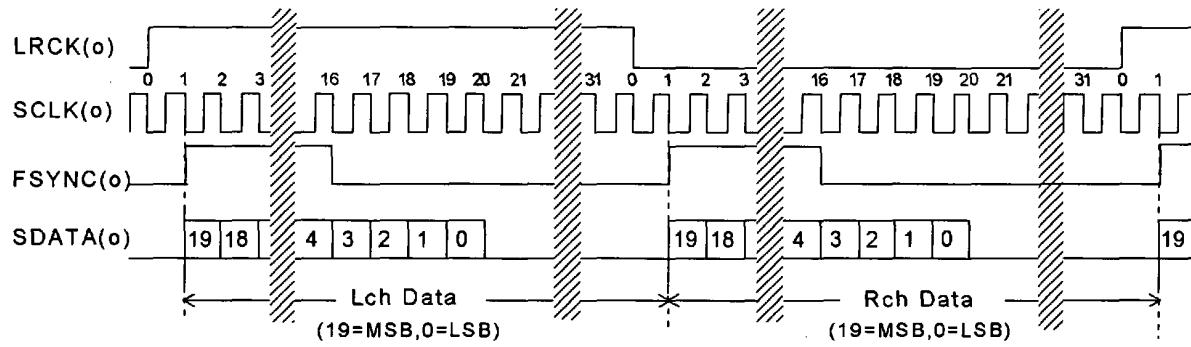

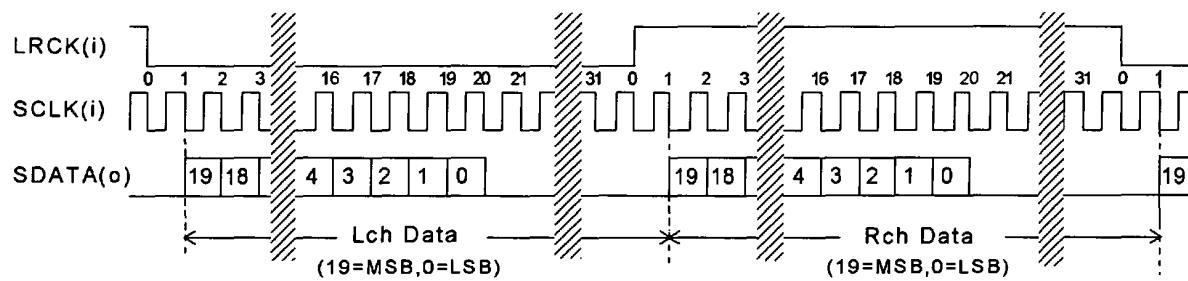

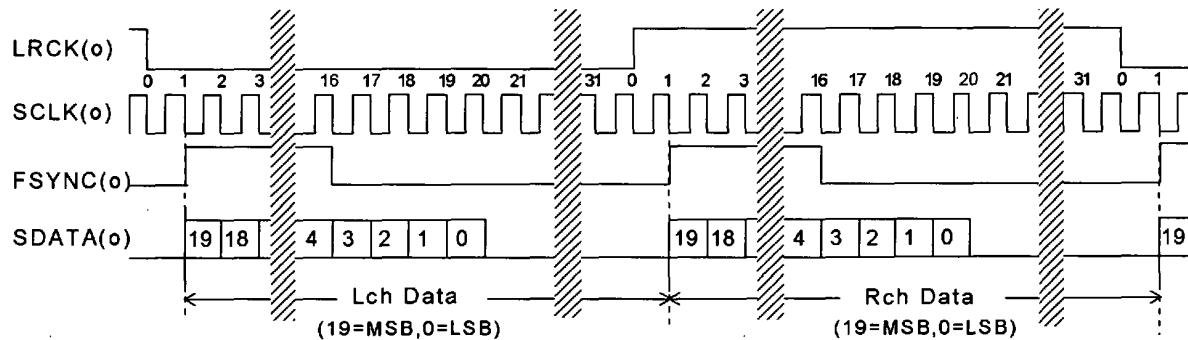

SERIAL DATA TIMING (SLAVE MODE,  $FSYNC = "H"$ )

SERIAL DATA TIMING (SLAVE MODE)

SERIAL DATA TIMING (MASTER MODE)

## OPERATION OVERVIEW

### ■ System clock

In slave mode, MCLK(256fs/384fs), LRCK(fs) and SCLK(64fs) are required for AK5351. Use a signal divided from the MCLK for LRCK. In master mode, only MCLK is needed. A LRCK clock rate meets standard audio rates (32kHz, 44.1kHz, 48kHz). In slave mode, the MCLK should be synchronized with LRCK but the phase is free of care.

The AK5351 includes the phase detect circuit for LRCK clock, the AK5351 is reset automatically when the synchronization is out of phase by changing the clock frequencies. (Please refer to the "Asynchronization - reset."). When changing sampling frequency(fs) after power-up, AK5351 should be reset.

During the operation ( $\overline{PD} = "H"$ ) following external clocks should never be stopped : CLK in master mode and MCLK, SCLK and LRCK in slave mode. When the clocks stop there is a possibility that the device comes into a malfunction because of over currents in the dynamic logic. If the external clocks are not present, the AK5351 should be in the power-down mode. ( $\overline{PD} = "L"$ )

| fs      | Master Clock (MCLK) |            | SCLK(64fs) |

|---------|---------------------|------------|------------|

|         | 256fs               | 384fs      |            |

| 32.0kHz | 8.1920MHz           | 12.2880MHz | 2.0480MHz  |

| 44.1kHz | 11.2896MHz          | 16.9344MHz | 2.8224MHz  |

| 48.0kHz | 12.2880MHz          | 18.4320MHz | 3.0720MHz  |

Table 1 . System Clock

### ■ Clock Circuit

AK5351 has an internal divider as shown in the above figure. The device can interface either or an external MCLK(256fs or 384fs) by controlling CMODE pin.

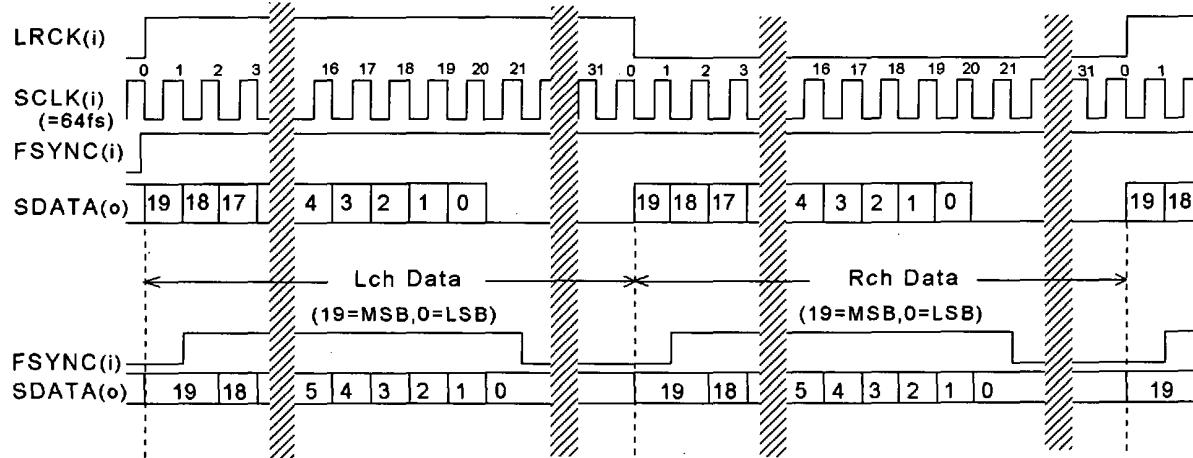

## ■ Serial Data Interface

Audio Serial Interface has four kinds of mode, it can be changed by SMODE1 and SMODE2 pins. Data format is MSB first, 2's complement.

| Figure   | S MODE1 | S MODE2 | Mode                                     | L/R polarity |

|----------|---------|---------|------------------------------------------|--------------|

| Figure 1 | L       | L       | Slave Mode: 20bit, MSB justified         | Lch=H, Rch=L |

| Figure 2 | H       | L       | Master Mode: Similar to I <sup>2</sup> S | Lch=H, Rch=L |

| Figure 3 | L       | H       | Slave Mode: I <sup>2</sup> S             | Lch=L, Rch=H |

| Figure 4 | H       | H       | Master Mode: I <sup>2</sup> S            | Lch=L, Rch=H |

Table 2 . Serial Interface

### 1) SLAVE mode

An output channel is defined by LRCK. Both channel data are output in sequence, in order of the Lch first then Rch at the rate of fs. Data bits are clocked out via the SDATA pin at SCLK rate. Figure 1 and Figure 3 shows data output timing at SCLK=64fs. FSYNC enables SCLK to start clocking out data. The MSB is clocked out by the LRCK edge. SCLK causes the ADC to output succeeding bits when FSYNC is high. However, as I<sup>2</sup>S slave mode ignores FSYNC, it should hold "L" or "H".

### 2) MASTER mode

In MASTER mode, the A/D converter is driven from a master clock(MCLK:256fs/384fs) and outputs all other clocks(LRCK, SCLK). The falling edge of SCLK causes the ADC to output each bit. Figure 2 and Figure 4 shows the output timing. 2x fs clock of 50% duty is output via the FSYNC pin. FSYNC rises one SCLK cycle after the transition of LRCK edges and stays high during 16 serial clocks(16\*t<sub>SLK</sub>). Upper 16 bit data is output during FSYNC "H", lower 4 bit is output after FSYNC "L" transition.

Figure 1 . Data Output Timing (Slave mode)

Figure 2. Data Output Timing(Master mode)

Figure 3. Data Output Timing(I<sup>2</sup>S Slave mode)Figure 4. Data Output Timing (I<sup>2</sup>S Master mode)

**■ Power-down mode**

The AK5351 has to be reset once by bringing  $\overline{PD}$  "L" upon power-up. All internal registers of the digital filter and so on in the AK5351 are reset by this operation. When exiting the power-down mode( $\overline{PD}="H"$ ), the internal timing starts clocking by first MCLK " $\uparrow$ "(rising edge). In master mode internal counter starts at once, in slave mode internal counter starts after synchronizing with the first rising edge of LRCK. The serial output data is available after 516 counting clock of LRCK cycle.

**■ Asynchronization-reset**

In slave mode, if the phase difference between LRCK and internal control signals is larger than  $+1/16\sim-1/16$  of word period( $1/fs$ ), the synchronization of internal control signals with LRCK is done automatically at the first rising edge of LRCK.

**■ High Pass Filter(HPFE pin)**

The AK5351 has a Digital High Pass Filter(HPF) for DC-offset cancel. When HPFE pin goes "H", HPF is enabled. The cut-off frequency of the HPF is 1Hz(@ $fs=48kHz$ ). It also scales with the sampling frequency( $fs$ ). The HPF can be disabled by bringing HPFE pin "L". In this case, the AK5351 has the DC-offset of a few mV.

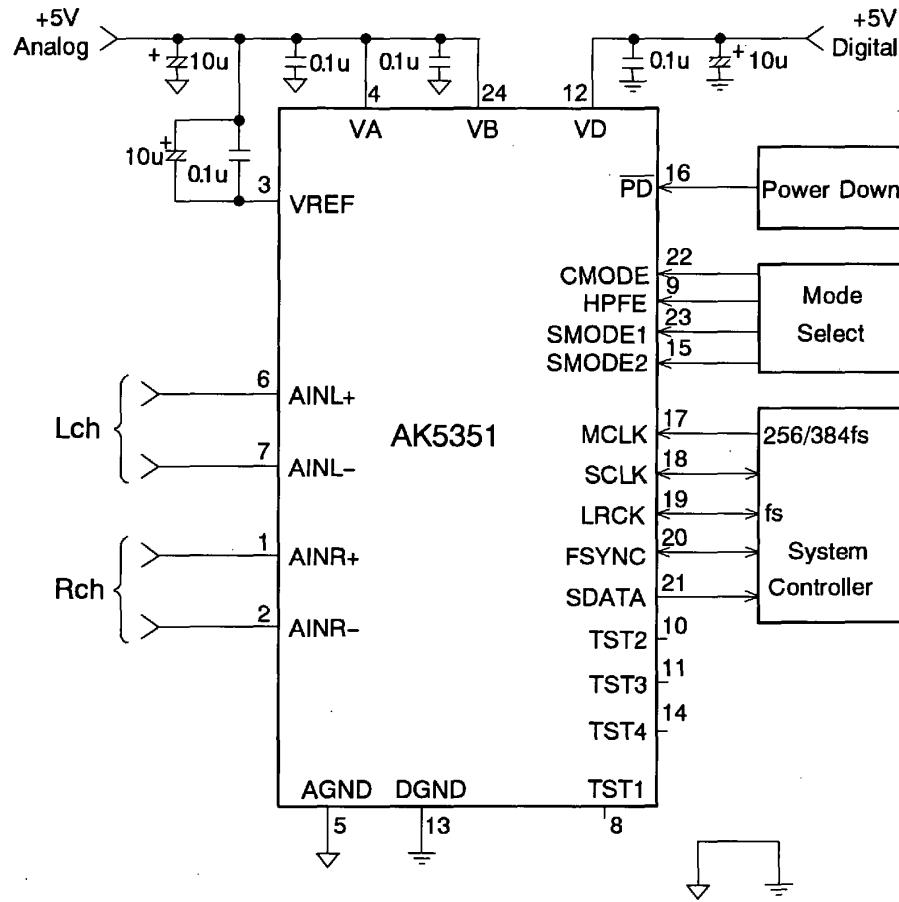

## SYSTEM DESIGN

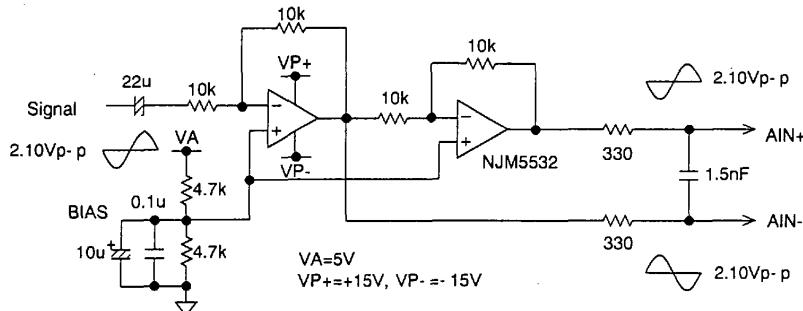

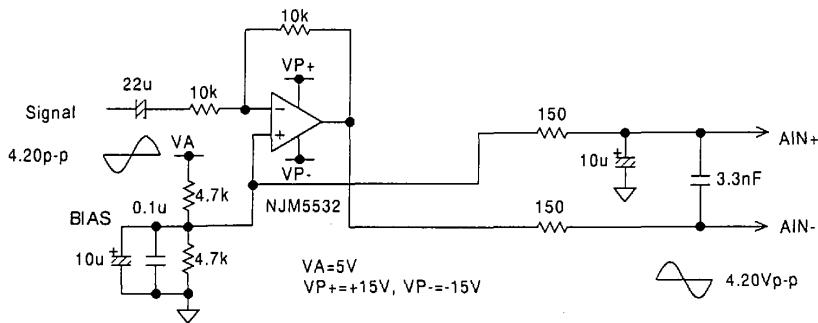

Figure 5 shows the system connection diagram. Figure 6 and Figure 7 shows the input buffer circuit. An evaluation board[AKD5351/2] is available which demonstrates the optimum layout, power supply arrangement and measurement results.

Figure 5 . System Connection Diagram Example

NOTE: +5V Analog should be powered the same time or earlier than +5V Digital.

### ■ Grounding and Power Supply Decoupling

The AK5351 requires careful attention to power supply and grounding arrangements. The VA and VB are connected together through the chip substrate and have several ohm resistance. The power to VB should come up at the same time or faster than the power to VD, when they are fed separately to the device (Figure 5). As to the connections of decoupling capacitors, refer to Figure 5 . The 0.1uF of decoupling capacitors connected power supply pins should be as near as possible to the power supply pin. As AIN $\pm$  pins is near VD pin, ground pattern should be inserted between VD line and AINL $\pm$  lines to avoid digital noise coupling. Refer to evaluation board manual of AKD5352/1 Rev.B about board layout.

## ■ Analog connections

Analog signal is differentially input into the modulator via the AIN+ and the AIN- pins. The input voltage is the difference between AIN+ and AIN- pins. The full-scale of each pin is  $\pm 2.10\text{Vp-p}$  on its reference voltage(VREF). In case that the positive input is more than its full-scale, the AK5351 outputs positive 7FFFFH(Hex, Full-scale). In case that the negative input is more than its full-scale, the AK5351 outputs negative 80000H(Hex, Full-scale). Analog inputs of the AK5351 are normally Full-differential inputs, while they are also acceptable Single-ended inputs. In case of Single-ended inputs, analog signal is input from either positive or negative input and the other side inputs bias voltage. Figure 7 is a circuit example which analog input signal is input 4.20Vp-p into AIN- pin and bias voltage into AIN+ pin. The DC offset is removed by the internal HPF.

AK5351 samples the analog inputs at 3.072MHz with  $\text{fs}=48\text{kHz}$ . The digital filter rejects all noise between 26.5kHz and 3.0455MHz. However, the filter will not reject frequencies right around 3.072MHz ( and multiples of 3.072MHz). Most audio signals do not have significant noise energy at 3.072MHz. Hence, a simple RC filter is sufficient to attenuate any noise energy at 3.072MHz.

The reference voltage for A/D converter is supplied from the VREF pin at VA reference. In order to eliminate the effects of high frequency noise on the VREF pin, a 10uF or less electrolytic capacitor and a 0.1uF ceramic capacitor should be connected parallel between the VREF and the VA pins. No current should be driven from the VREF pin.

The AK5351 accepts +5V supply voltage. Any voltage which exceeds the upper limit of  $(\text{VA}+)+0.3\text{V}$  and lower limit of  $\text{AGND}-0.3\text{V}$  and any current beyond 10mA for the analog input pins(AINL $\pm$ , AINR $\pm$ ) should be avoided. Excessive currents to the input pins may damage the device. Hence input pins must be protected from signals at or beyond these limits.

Use caution specially in case of using  $\pm 15\text{V}$  in surrounding analog circuit.

Figure 6 . Full-differential Input Buffer Circuit Example

Figure 7 . Single-ended Input Buffer Circuit Example

**■ Digital Connections**

To minimize digital originated noise, connect the ADC digital outputs only to CMOS inputs. Logic families of 4000B, 74HC, 74AC, 74ACT and 74HCT series are suitable.

**■ Multiple AK5351**

In systems where multiple ADC's are required, care must be taken to insure the internal clocks are synchronized between converters to make simultaneous sampling. In slave mode, synchronous sampling is achieved by supplying the same MCLK and LRCK to all converters. In master mode, the same  $\overline{PD}$  signal is supplied to each ADC. The  $\overline{PD}$  state is released at the first rising edge of MCLK after bringing  $\overline{PD}$  into high. Hence, if the rising edge of  $\overline{PD}$  and rising edge of MCLK coincides together the sampling difference among the ADC's modulator would occur. The difference could be 1/256fs in the sampling clock(64fs) of the modulator, typically 81ns at  $f_s=48\text{kHz}$ .

## PACKAGE

## ● 24pin VSOP (Unit: mm)

## ■ Material &amp; Lead finish

Package: Epoxy

Lead-frame: Copper

Lead-finish: Soldering plate

**MARKING**

Contents of AAXXXX

AA: Lot#

XXXX: Date Code

## IMPORTANT NOTICE

- These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.

- AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:

- (a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- (b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.