#### **Features**

- Very Low-cost Configuration Memory

- Programmable 1,048,576 x 1, 2,097,152 x 1, 4,194,304 x 1 and 7,340,032 x 1-bit Serial Memories Designed to Store Configuration Programs for Field Programmable Gate Arrays (FPGAs)

- 1.8V, 2.5V, and 3.3V I/O

- 3.3V Supply Voltage

- Program Support using an Atmel Programmer or Industry-standard Third Party Programmers

- In-System Programmable (ISP) via JTAG Interface (IEEE 1532)

- IEEE 1149.1 Boundary-scan Testability

- Simple Interface to SRAM FPGAs

- Pin Compatible with Xilinx® XCFxxS Series Platform Flash PROM to Configure Xilinx Spartan® and Virtex® FPGAs

- Cascadable Read-back to Support Additional Configurations or Higher-density FPGAs

- Low-power CMOS FLASH Process

- Available in 20-lead TSSOP Package

- Low-power Standby Mode

- Fast Serial Download Speeds up to 33 MHz

- Endurance: 100,000 Write Cycles Typical

- Green (Pb/Halide-free/RoHS Compliant) Package

- Functionally-compatible with Existing AT17 Series Configuration Memories to Configure Atmel AT40KAL Series FPGAs

#### AT18F Series Configuration Memory Offering

|                     | AT18F010      | AT18F002 | AT18F040 | AT18F080 |  |  |  |

|---------------------|---------------|----------|----------|----------|--|--|--|

| Density             | 1 Mbit        | 2 Mbit   | 4 Mbit   | 7 Mbit   |  |  |  |

| JTAG Programming    |               | Yes      |          |          |  |  |  |

| VCCINT              |               | 3.3V     |          |          |  |  |  |

| VCCO                | 1.8-3.3V      |          |          |          |  |  |  |

| VCCJ                | 1.8-3.3V      |          |          |          |  |  |  |

| Configuration Clock | 33 MHz        |          |          |          |  |  |  |

| Package             | 20-lead TSSOP |          |          |          |  |  |  |

| Green Package       | Yes           |          |          |          |  |  |  |

## 1. Description

The AT18F Series of JTAG In-System Programmable Configuration PROMs (Configurators) provide an easy-to-use, cost-effective configuration memory for Field Programmable Gate Arrays. The AT18F Series device is packaged in a 20-lead TSSOP. The AT18F Series Configurator uses a simple serial-access procedure to configure one or more FPGA devices.

The AT18F Series Configurators can be programmed with Atmel or industry-standard, third-party, stand-alone programmers such as BP, Data I/O, Hi-Lo, etc.

# FPGA Configuration Flash Memory

AT18F010 AT18F002 AT18F040 AT18F080

# **Preliminary**

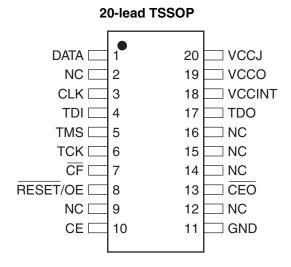

## 2. Pin Configuration

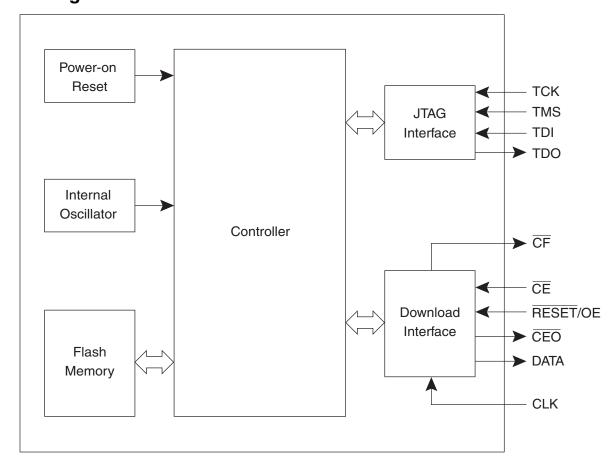

## 3. Block Diagram

## 4. Device Description

The download interface of the configuration memory will directly communicate with the FPGA through the interface-control signals (CLK, RESET/OE, CE) to initialize and terminate configuration. All FPGA devices in the master serial mode can control the entire configuration process to receive data from the configuration device without requiring an external intelligent controller. When FPGA devices are used in slave serial mode, an external clock signal can be applied to the CLK pin of an AT18F series device as a configuration loading clock. Multiple FPGAs that are setup in Master Serial and Slave Serial modes can also be used to control the configuration process to obtain data from a single configurator or cascaded configurators. Please contact Atmel at configurator@atmel.com for detailed descriptions.

The  $\overline{\text{CF}}$  pin is used as an optional input pin for the JTAG CONFIG instruction to initialize the FPGA configuration without requiring powering down the device. The  $\overline{\text{RESET}}/\text{OE}$  and  $\overline{\text{CE}}$  pins control the tri-state buffer on the DATA output pin and enable the address counter. When  $\overline{\text{RESET}}/\text{OE}$  is driven Low, the configuration device resets its address counter and tri-states its DATA pin. The  $\overline{\text{CE}}$  pin also controls the output of the AT18F Series Configurator. If  $\overline{\text{CE}}$  is held High after the  $\overline{\text{RESET}}/\text{OE}$  reset pulse, the counter is reset and the DATA output pin is tri-stated.

When the configurator has driven out all of its data and CEO is driven Low, the device tri-states the DATA pin to avoid contention with other configurators. Upon power-up, the address counter is automatically reset.

AT18F series devices are compatible with a portion of the Xilinx's FGPA device families.

Table 4-1.

AT18F Series Configurator Compatibility with Xilinx FPGAs

| Atmel          | XiI           | inx      | Atmel          | Xili                 | nx                    |

|----------------|---------------|----------|----------------|----------------------|-----------------------|

|                | Virtex-II     | XC2V40   |                | Virtex-II Pro        | XC2VP4                |

|                | VII (GX-II    | XC2V80   |                | Virtex-II            | XC2V500               |

|                | =             | XCV50E   |                | VII (ex-II           | XC2V1000              |

|                | Virtex-E      | XCV100E  |                |                      | XCV400E               |

|                |               | XCV50    |                | Virtex-E             | XCV405E               |

|                | Virtex        | XCV100   |                |                      | XCV600E               |

|                |               | XCV150   | AT405040 00VII | Vintar               | XCV400                |

|                | Spartan-3E    | XC3S100E | AT18F040-30XU  | Virtex               | XCV600                |

| AT18F010-30XU  | Consultant O  | XC3S50   |                | Consider OF          | XC3S500E              |

|                | Spartan-3     | XC3S200  |                | Spartan-3E           | XC3S1200E             |

|                | 0             | XC2S50E  |                | Spartan-3L           | XC3S1000L             |

|                | Spartan-IIE   | XC2S100E |                | Spartan-3            | XC3S1000              |

|                |               | XC2S15   |                | 0                    | XC2S400E              |

|                |               | XC2S30   |                | Spartan-IIE          | XC2S600E              |

|                | Spartan-II    | XC2S50   |                | Virtex-5 LX          | XC5VLX30              |

|                |               | XC2S100  |                | Virtex-4 LX          | XC4VLX15              |

|                |               | XC2S150  |                |                      | XC4VLX25              |

|                | Virtex-II Pro | XC2VP2   |                | Virtex-4 FX          | XC4VFX12              |

|                | Virtex-II     | XC2V250  |                |                      | XC4VFX20              |

|                | \Catao        | XCV200E  |                | Virtex-II Pro X      | XC2VPX20              |

|                | Virtex-E      | XCV300E  |                | Vintary II Day       | XC2VP7                |

|                | V Contact     | XCV200   |                | Virtex-II Pro        | XC2VP20               |

| AT10F000 00VII | Virtex        | XCV300   |                |                      | XC2V1500              |

| AT18F002-30XU  | Spartan-3E    | XC3S250E | AT18F080-30XU  | Virtex-II            | XC2V2000              |

|                | Spartan-3     | XC3S400  |                |                      | XCV812E               |

|                |               | XC2S150E |                | Virtex-E             | XCV1000E              |

|                | Spartan-IIE   | XC2S200E |                |                      | XCV1600E              |

|                |               | XC2S300E |                | Minton               | XCV800                |

|                | Spartan-II    | XC2S200  |                | Virtex               | XCV1000               |

|                |               |          |                | Spartan-3E           | XC3S1600E             |

|                |               |          |                |                      |                       |

|                |               |          |                | Spartan-3L           | XC3S1500L             |

|                |               |          |                | Spartan-3L Spartan-3 | XC3S1500L<br>XC3S1500 |

### 5. Programming

AT18Fxx devices are in-system programmable (ISP) devices utilizing the 4-pin JTAG protocol. This capability eliminates package handling normally required for programming and facilitates rapid design iterations and field changes.

Atmel provides ISP hardware and software to allow programming of the AT18Fxx via the PC. ISP is performed by using either a download cable or a comparable board tester or a simple microprocessor interface.

To allow ISP programming support by the Automated Test Equipment (ATE) vendors, Serial Vector Format (SVF) files can be created by the Atmel JCPS Software. Conversion to other ATE tester format beside SVF is also possible

AT18Fxx devices can also be programmed using standard third-party programmers such as BP, Datal/O, Hi-Lo, etc. Factory-preprogrammed devices, as required by customers, are also available for certain ordering quantities.

Contact your local Atmel representatives or Atmel PLD applications for details.

#### 5.1 JTAG-BST Overview

The JTAG boundary-scan testing is controlled by the Test Access Port (TAP) controller in the AT18F series. The boundary-scan technique involves the inclusion of a shift-register stage (contained in a boundary-scan cell) adjacent to each component so that signals at component boundaries can be controlled and observed using scan testing principles. Each input pin and I/O pin has its own boundary-scan cell (BSC) in order to support boundary-scan testing. The AT18Fxx series does not currently include a Test Reset (TRST) input pin because the TAP controller is automatically reset at power-up. The six JTAG BST modes supported include: SAMPLE/PRELOAD, EXTEST, BYPASS and IDCODE. BST on the AT18Fxx series is implemented using the Boundary-scan Definition Language (BSDL) described in the JTAG specification (IEEE Standard 1149.1). Any third-party tool that supports the BSDL format can be used to perform BST on the AT18Fxx series.

The AT18F series uses the four JTAG-standard I/O pins for In-System programming (ISP). The AT18F series is programmable through the four JTAG pins using programming algorithm compatible with the IEEE JTAG Standard 1532. Programming is performed by using selectable voltage levels of the programming signals from the JTAG ISP interface.

### 5.2 JTAG Boundary-scan Cell (BSC) Testing

The AT18F series has I/Os that contain boundary-scan cells (BSC) in order to support boundary-scan testing as described in detail by IEEE Standard 1149.1. Input to the capture register chain is fed in from the TDI pin while the output is directed to the TDO pin. Capture registers are used to capture active device data signals, to shift data in and out of the device and to load data into the update registers. Control signals are generated internally by the JTAG TAP controller.

### 6. Pin Description

Table 6-1. Pin Descriptions

| Name     | Туре         | 20-lead TSSOP        |

|----------|--------------|----------------------|

| DATA     | I/O          | 1                    |

| CLK      | I            | 3                    |

| RESET/OE | I            | 8                    |

| CE       | I            | 10                   |

| CF       | I            | 7                    |

| CEO      | 0            | 13                   |

| TMS      | I            | 5                    |

| тск      | I            | 6                    |

| TDI      | I            | 4                    |

| TDO      | 0            | 17                   |

| VCCINT   | I            | 18                   |

| NC       | -            | 2, 9, 12, 14, 15, 16 |

| VCCO     | Power Supply | 19                   |

| GND      | Ground       | 11                   |

| VCCJ     | Power Supply | 20                   |

### 6.1 DATA (D0)

Open-collector bi-directional data pin. This pin has an internal 20 K $\Omega$  pull-up resistor.

#### 6.2 CLK

Clock input. Used to increment the internal address and bit counter for reading and programming. This pin has an internal 20 K $\Omega$  pull-up resistor.

#### 6.3 RESET/OE

Output Enable (active High) and  $\overline{RESET}$  (active Low). A Low level on  $\overline{RESET}/OE$  resets both the address and bit counters. A High level (with  $\overline{CE}$  Low) enables the data output driver. This pin has an internal 20 K $\Omega$  pull-up resistor.

#### 6.4 <u>CE</u>

Chip Enable input (active Low). A Low level (with OE High) allows CLK to increment the address counter and enables the data output driver. A High level on  $\overline{\text{CE}}$  disables both the address and bit counters and forces the device into a low-power standby mode. This pin has an internal 20 K $\Omega$  pull-up resistor.

#### 6.5 **CF**

6

Configuration Pulse (open-drain output). Allows JTAG CONFIG instruction to initiate FPGA configuration without powering down the FPGA. This is an open-drain output that is pulsed Low by the JTAG CONFIG command.

#### 6.6 **CEO**

Chip Enable Output for configuration download. This output goes Low when the internal address counter of the device has reached its maximum value which signals that all configuration data is being clocked out of the device. In a daisy chain of AT18F Series devices, the  $\overline{\text{CEO}}$  pin of one device must be connected to the  $\overline{\text{CE}}$  input of the next device in the chain. It will stay Low as long as  $\overline{\text{CE}}$  is Low and OE is High. It will then follow  $\overline{\text{CE}}$  until OE goes Low; thereafter,  $\overline{\text{CEO}}$  will stay High until the entire memory device is read again.

#### 6.7 TMS

JTAG Mode Control Input. The state of TMS with the rising edge of TCK determines the state transitions of the Test Access Port (TAP) controller. TMS has an internal 50 K $\Omega$  weak pull-up to  $V_{CCJ}$  to provide a logic 1 to the device.

#### 6.8 TCK

JTAG Clock Input. This pin is the JTAG clock input to the TAP controller of the device.

#### 6.9 TDI

JTAG Serial Data Input. This pin is the serial input to all JTAG instructions and data registers. An internal 50 K $\Omega$  weak pull-up to V<sub>CCJ</sub> provides a logic 1 to the device.

#### 6.10 TDO

JTAG Serial Data Output. This pin is the serial output to all JTAG instruction and data registers. An internal 50 K $\Omega$  weak pull-up to V<sub>CCJ</sub> provides a logic 1 to the device if the pin is not driven.

#### 6.11 VCCINT

+3.3V supply voltage for internal logic.

#### 6.12 NC

No Connect Pin. This pin is not connected to any internal logic of the device and can be left floating.

#### 6.13 VCCO

Supply voltage for I/O drivers (1.8V, 3.3V, or 3.3V).

#### 6.14 VCCJ

Supply voltage for JTAG I/O drivers (1.8V, 3.3V, or 3.3V).

#### 6.15 GND

Power supply ground.

## 7. Standby Mode

The AT18F Series Configurators enter a low-power standby mode whenever the JTAG mode is inactive and  $\overline{\text{CE}}$  is asserted High. In this mode, the AT18F Configurator consumes less than 1 mA of current at 3.3V. The output remains in a high-impedance state regardless of the state of the OE input.

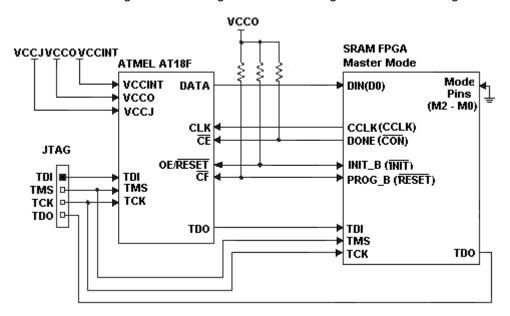

## 8. Configuration Memory to FPGA Device Interface Connection Diagrams

Figure 8-1. General Connection Diagram for Loading FPGA from Configurator and JTAG Signals

Notes: 1. Signals within parenthesis will be applied to Atmel AT40AK FPGA.

2. For details of the circuit connection, please contact factory.

## 9. Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                                    |

|------------------------------------------------------------------------|

| Storage Temperature65° C to +150° C                                    |

| Voltage on Any Pin with Respect to Ground0.1V to V <sub>CC</sub> +0.5V |

| Supply Voltage (V <sub>CC</sub> )0.5V to +3.6V                         |

| Maximum Soldering Temp. (10 sec. @ 1/16 in.) 260° C                    |

| ESD (R <sub>ZAP</sub> = 1.5K, C <sub>ZAP</sub> = 100 pF)2000V          |

\*NOTICE:

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those listed under operating conditions is not implied. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect device reliability.

### 10. Operating Conditions

$T_{AI} = -40^{\circ} \, \text{C}$  to  $+85^{\circ} \, \text{C}$  for Industrial and  $0^{\circ} \, \text{C}$  to  $+70^{\circ} \, \text{C}$  for Commercial

| Symbol             | Description                                          |                | Min                     | Тур | Max                     | Units |

|--------------------|------------------------------------------------------|----------------|-------------------------|-----|-------------------------|-------|

| V <sub>CCINT</sub> | Supply Voltage for Internal Logic                    |                | 3.0                     | 3.3 | 3.6                     | V     |

|                    |                                                      | 3.3V Operation | 3.0                     | 3.3 | 3.6                     |       |

| $V_{CCO}$          | CO Supply Voltage for I/O Drivers                    | 2.5V Operation | 2.3                     | 2.5 | 2.7                     | V     |

|                    | 1.8V Operation                                       | 1.7            | 1.8                     | 1.9 |                         |       |

|                    | V <sub>CCJ</sub> Supply Voltage for JTAG I/O Drivers | 3.3V Operation | 3.0                     | 3.3 | 3.6                     |       |

| $V_{CCJ}$          |                                                      | 2.5V Operation | 2.3                     | 2.5 | 2.7                     | V     |

|                    |                                                      | 1.8V Operation | 1.7                     | 1.8 | 1.9                     |       |

|                    |                                                      | 3.3V Operation | -0.3                    |     | 0.8                     |       |

| $V_{IL}$           | Input Low Voltage                                    | 2.5V Operation | -0.3                    |     | 0.7                     | V     |

|                    |                                                      | 1.8V Operation | -0.3                    |     | 0.35 x V <sub>CCO</sub> |       |

|                    |                                                      | 3.3V Operation | 2.0                     |     | 3.9                     |       |

| V <sub>IH</sub>    | Input High Voltage                                   | 2.5V Operation | 1.7                     |     | 3.9                     | V     |

|                    |                                                      | 1.8V Operation | 0.65 x V <sub>CCO</sub> |     | 3.9                     |       |

## 11. DC Characteristics

| Symbol              | Description                                   |                | Condition                                          | Min                     | Тур | Max  | Units |

|---------------------|-----------------------------------------------|----------------|----------------------------------------------------|-------------------------|-----|------|-------|

| I <sub>CCINT</sub>  | Internal Voltage Supply Current, Active Mode  |                | 33 MHz                                             |                         |     | 10   | mA    |

| I <sub>CCIO</sub>   | I/O Drive Supply Curren                       | t, Active Mode | 33 MHz                                             |                         |     | 10   | mA    |

| I <sub>CCJ</sub>    | JTAG Supply Current, A                        | ctive Mode     |                                                    |                         |     | 5    | mA    |

| I <sub>CCINTS</sub> | Internal Voltage Supply Current, Standby Mode |                | $V_{CCINT} = 3.6V,$<br>$V_{CIO} = 3.6V$            |                         |     | 1    | mA    |

| I <sub>CCIOS</sub>  | Output Drive Supply Current, Standby Mode     |                | $V_{CCINT} = 3.6V,$<br>$V_{CIO} = 3.6V$            |                         |     | 1    | mA    |

| I <sub>CCJS</sub>   | JTAG Supply Current, Standby Mode             |                | $V_{\text{CCINT}} = 3.6V,$ $V_{\text{CIO}} = 3.6V$ |                         |     | 1    | mA    |

| I <sub>IL</sub>     | Input or I/O Low Leakage                      |                |                                                    |                         | 1   | 10   | μΑ    |

| I <sub>IH</sub>     | Input or I/O High Leakag                      | je             |                                                    | -10                     | 10  | 10   | μΑ    |

|                     |                                               | 3.3V Operation |                                                    |                         |     | 0.4  |       |

| $V_{OL}$            | Output Low Voltage                            | 2.5V Operation |                                                    |                         |     | 0.4  | V     |

|                     |                                               | 1.8V Operation |                                                    |                         |     | 0.45 |       |

|                     |                                               | 3.3V Operation |                                                    | V <sub>CCO</sub> - 0.4  |     |      |       |

| $V_{OH}$            | Output High Voltage                           | 2.5V Operation |                                                    | V <sub>CCO</sub> - 0.4  |     |      | V     |

|                     |                                               | 1.8V Operation |                                                    | V <sub>CCO</sub> - 0.45 |     |      |       |

### 12. AC Characteristics

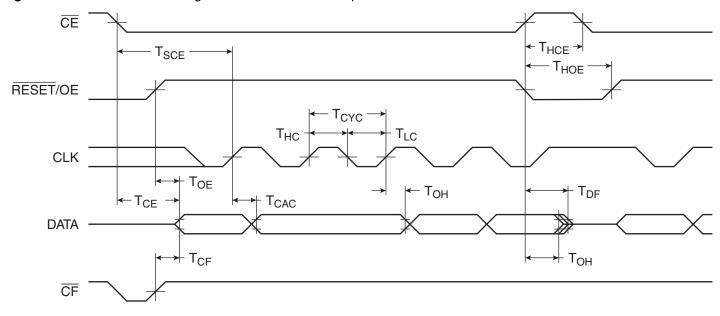

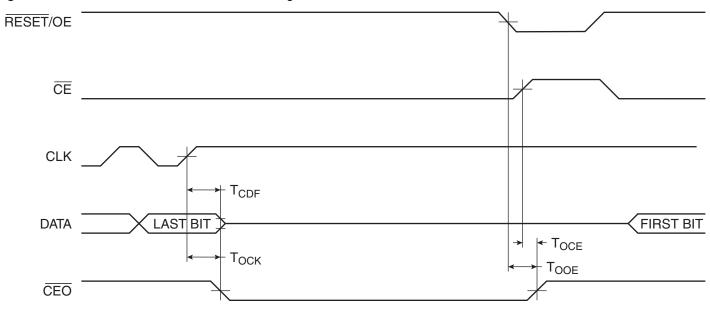

Figure 12-1. AT18Fxx as Configuration Slave with CLK Input Pin as Clock Source

Table 12-1. AC Characteristics over Operating Conditions

| Symbol             | Description                             | Min | Max | Units |

|--------------------|-----------------------------------------|-----|-----|-------|

| T <sub>CF</sub>    | CF to Data Delay                        | 20  | 50  | μs    |

| T <sub>OE</sub>    | RESET/OE to Data Delay                  |     | 10  | ns    |

| T <sub>CE</sub>    | CE to Data Delay                        | 20  |     | μs    |

| T <sub>CAC</sub>   | CLK to Data Delay                       |     | 15  | ns    |

| T <sub>OH</sub>    | Data Hold from CE, RESET/OE, CLK, or CF |     | 15  | ns    |

| T <sub>DF</sub>    | CE or RESET/OE to Data Float Delay      |     | 25  | ns    |

| T <sub>CYC</sub>   | Clock Period                            | 30  |     | ns    |

| T <sub>LC</sub>    | CLK Low Time                            | 15  |     | ns    |

| T <sub>HC</sub>    | CLK High Time                           | 15  |     | ns    |

| T <sub>SCE</sub>   | CE Setup Time to CLK                    | 20  |     | μs    |

| T <sub>HCE</sub>   | CE Hold Time                            | 250 |     | ns    |

| $T_{HOE}$          | RESET/OE Hold Time                      | 250 |     | ns    |

| T <sub>BLKE</sub>  | Block Erase Time                        | 0.7 | 1   | S     |

|                    | Bulk Erase Time – 1M                    |     | 3   | S     |

| <b>-</b>           | Bulk Erase Time – 2M                    |     | 5   | S     |

| T <sub>ERASE</sub> | Bulk Erase Time – 4M                    |     | 9   | s     |

|                    | Bulk Erase Time – 8M                    |     | 15  | s     |

| T <sub>CK_J</sub>  | TAP Clock Minimum Period                | 100 |     | ns    |

Figure 12-2. AC Characteristics when Cascading

Table 12-2. AC Characteristics When Cascading

| Symbol           | Description               | Min | Max | Units |

|------------------|---------------------------|-----|-----|-------|

| T <sub>CDF</sub> | CLK to Output Float Delay |     | 25  | ns    |

| T <sub>OCK</sub> | CLK to CEO Delay          |     | 20  | ns    |

| T <sub>OCE</sub> | CE to CEO Delay           |     | 20  | ns    |

| T <sub>OOE</sub> | RESET/OE to CEO Delay     |     | 20  | ns    |

# 13. Ordering Information

| Memory Size | Ordering Code | Package         | Operation Range                 |

|-------------|---------------|-----------------|---------------------------------|

| 1-Mbit      | AT18F010-30XU | 20A2 - 20 TSSOP | Industrial<br>(-40° C to 85° C) |

| 2-Mbit      | AT18F002-30XU | 20A2 - 20 TSSOP | Industrial<br>(-40° C to 85° C) |

| 4-Mbit      | AT18F040-30XU | 20A2 - 20 TSSOP | Industrial<br>(-40° C to 85° C) |

| 7-Mbit      | AT18F080-30XU | 20A2 - 20 TSSOP | Industrial<br>(-40° C to 85° C) |

|      | Package Type                                                      |

|------|-------------------------------------------------------------------|

| 20A2 | 20-lead, 0.65 mm Wide, Plastic Think-Shrink Small Outline (TSSOP) |

### 14. Packaging Information

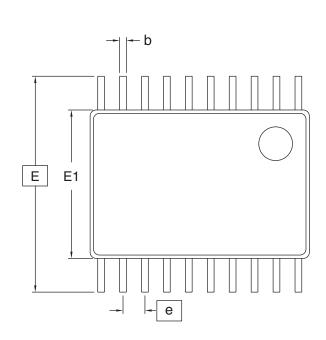

#### 14.1 20A2 - TSSOP

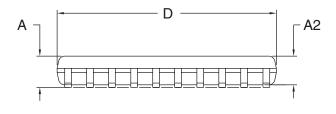

Top View

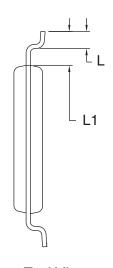

Side View

**End View**

### COMMON DIMENSIONS

(Unit of Measure = mm)

| SYMBOL | MIN  | NOM      | MAX  | NOTE |

|--------|------|----------|------|------|

| D      | 6.40 | 6.50     | 6.60 | 2, 5 |

| E      |      | 6.40 BSC |      |      |

| E1     | 4.30 | 4.40     | 4.50 | 3, 5 |

| А      | _    | _        | 1.20 |      |

| A2     | 0.80 | 1.00     | 1.05 |      |

| b      | 0.19 | -        | 0.30 | 4    |

| е      |      |          |      |      |

| L      | 0.45 | 0.60     | 0.75 |      |

| L1     |      | 1.00 REF |      |      |

Notes:

- This drawing is for general information only. Please refer to JEDEC Drawing MO-153, Variation AC, for additional information.

- 2. Dimension D does not include mold Flash, protrusions or gate burrs. Mold Flash, protrusions and gate burrs shall not exceed 0.15 mm (0.006 in) per side.

- 3. Dimension E1 does not include inter-lead Flash or protrusions. Inter-lead Flash and protrusions shall not exceed 0.25 mm (0.010 in) per side.

- 4. Dimension b does not include Dambar protrusion. Allowable Dambar protrusion shall be 0.08 mm total in excess of the b dimension at maximum material condition. Dambar cannot be located on the lower radius of the foot. Minimum space between protrusion and adjacent lead is 0.07 mm.

- 5. Dimension D and E1 to be determined at Datum Plane H.

6/3/02

# 15. Revision History

| Revision Level – Release Date | History          |

|-------------------------------|------------------|

| A – January 2008              | Initial release. |

#### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

Technical Support

configurator@atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2008. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Atmel:

AT18F010-30XU AT18F080-30XU