Data sheet

# BMA220 Digital, triaxial acceleration sensor

**Bosch Sensortec**

#### **BMA220: Data sheet**

Document revision 1.15

Document release date 23 August 2011

Document number BST-BMA220-DS003-08

Technical reference code(s) 0 273 141 102

Notes Data in this document are subject to change without notice. Product

photos and pictures are for illustration purposes only and may differ from

the real product's appearance.

### **BMA220**

# TRIAXIAL ±2G TO ±16G ACCELERATION SENSOR WITH ON-CHIP MOTION-TRIGGERED INTERRUPT CONTROLLER

#### **Key features**

· Three-axis accelerometer

Ultra-Small package

Mold package (LGA 12ld)

Footprint 2mm x 2mm, height 0.98mm

Digital interface

SPI (4-wire, 3-wire), I<sup>2</sup>C, interrupt pin I/O supply voltage range: 1.6V to 3.6V

Programmable functionality

Acceleration ranges ±2g/±4g/±8g/±16g

Bandwidth 1kHz . . . 32Hz

Self test

On-chip interrupt controller

Motion-triggered interrupt-signal generation for

orientation recognition

any-motion detection

tap/double tap sensing

low-g/high-g detection

Stand-alone capability (no microcontroller needed)

Ultra-low power ASIC

Low current consumption, short wake-up time, advanced features for system power management

· RoHS compliant, halogen-free

#### **Typical applications**

- Display profile switching

- Tap/double tap sensing

- Menu scrolling

- Gaming

- Drop detection for warranty logging

- Advanced system power management for mobile applications

#### **General Description**

The BMA220 is a triaxial, low-g acceleration sensor with digital output for consumer market applications. It allows measurements of acceleration in three perpendicular axes. An evaluation circuitry (ASIC) converts the output of a micromechanical acceleration-sensing structure (MEMS) that works according to the differential capacitance principle.

Package and interface have been defined to match a multitude of hardware requirements. Since the sensor features an ultra-small footprint and a flat package it is ingeniously suited for mobile applications. The sensor offers a variable I/O supply voltage range from 1.6V to 3.6V and can be programmed to optimize functionality, performance and power consumption in customer specific applications. In addition it features an on-chip interrupt controller enabling motion-based applications without use of a microcontroller.

The BMA220 senses tilt, motion and shock vibration in cell phones, handhelds, computer peripherals, man-machine interfaces, virtual reality features and game controllers.

### **Index of Contents**

| 1. | SPECIFICATION                                    | 5                    |

|----|--------------------------------------------------|----------------------|

| 2. | ABSOLUTE MAXIMUM RATINGS                         | 7                    |

| 3. | BLOCK DIAGRAM                                    | . 8                  |

| 4. | GLOBAL MEMORY MAP                                | 9                    |

|    | 4.1 CONTROL REGISTERS                            | 9                    |

|    | 4.1.1 3-WIRE SPI MODE SELECTION                  | 10<br>11<br>11<br>12 |

|    | 4.2 SETTING REGISTERS                            | 12                   |

|    | 4.2.1 Acceleration range and sensitivity setting |                      |

|    | 4.3 Data registers                               | 14                   |

|    | 4.3.1 Acceleration data read-out                 |                      |

|    | 4.4 INTERRUPT CONTROL REGISTERS                  | 15                   |

| 5. | INTERRUPT CONTROLLERS                            | 16                   |

|    | 5.1 LATCHED VS. NON-LATCHED MODES                | 16                   |

|    | 5.2 SUPPORTED TYPES OF INTERRUPTS                | 17                   |

|    | 5.3 POWER-SAVING MODES                           | 17                   |

|    | 5.4 ANY-MOTION (SLOPE) DETECTION                 | 18                   |

|    | 5.5 TAP-SENSING                                  | 22                   |

|    | 5.6 ORIENTATION RECOGNITION                      | 24                   |

|    | 5.7 LOW-G DETECTION                              | 27                   |

|    | 5.8 High-g detection                             | 29                   |

|    | 5.9 Data ready detection                         | 30                   |

| 6. | OPERATION MODES                                  | 31                   |

|    | 6.1 DEDICATED MODES (µC-LESS / STAND ALONE)      | 33                   |

|    | 6.2 DIGITAL INTERFACE MODES                      | 34                   |

Page 4

| 6.3 LOW-POWER MODE AND SUSPEND MODE                             | 35       |

|-----------------------------------------------------------------|----------|

| 6.4 MODE TRANSITION VIA INTERFACE                               |          |

| 6.5 SELF TEST MODE                                              |          |

|                                                                 |          |

| 7. INTERFACES                                                   | 38       |

| 7.1 GENERAL DIGITAL INTERFACE DESCRIPTION                       | 39       |

| 7.2 SPI INTERFACE                                               | 40       |

| 7.3 I <sup>2</sup> C INTERFACE                                  | 43       |

| 7.4 I <sup>2</sup> C WATCHDOG TIMER                             | 48       |

| 7.5 SPI AND I <sup>2</sup> C ACCESS RESTRICTIONS                | 48       |

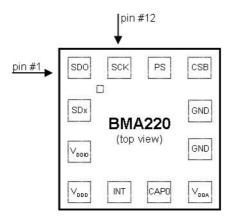

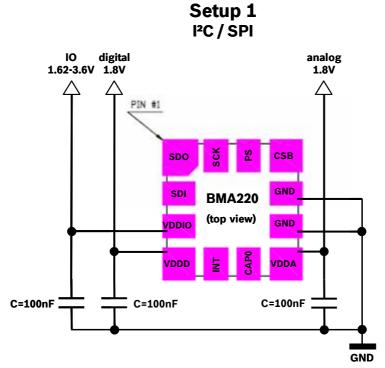

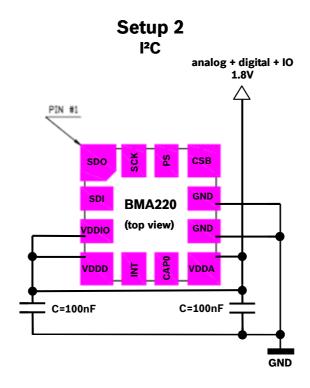

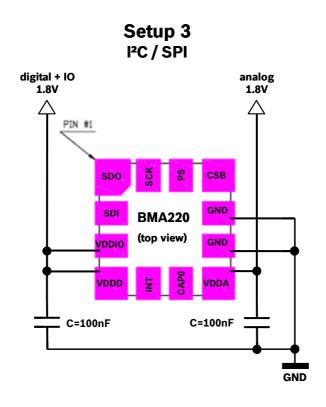

| 8. PIN-OUT AND CONNECTING DIAGRAM                               | 49       |

| 8.1 PIN-OUT                                                     | 49       |

| 8.2 CONNECTING DIAGRAMS                                         | 50       |

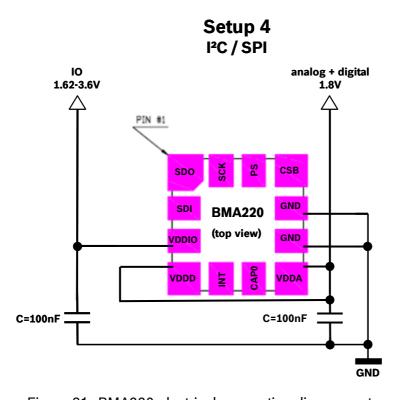

| 9. PACKAGE                                                      | 53       |

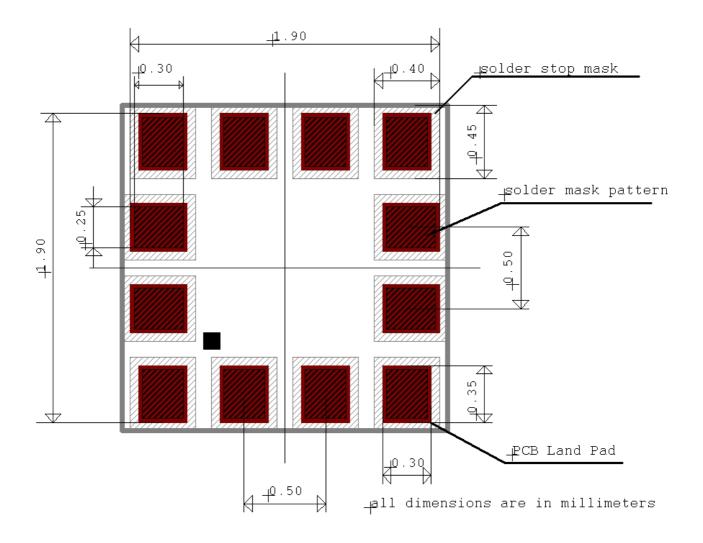

| 9.1 OUTLINE DIMENSIONS                                          | 53       |

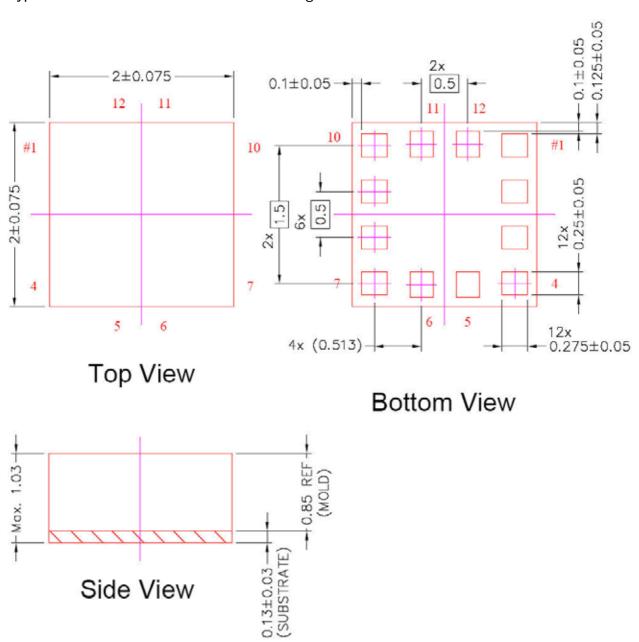

| 9.2 SENSING AXES ORIENTATION AND POLARITY OF THE ACCELERATION C | UTPUT 54 |

| 9.3 LANDING PATTERN RECOMMENDATION                              | 55       |

| 9.4 Marking                                                     | 56       |

| 9.4.1 Mass production samples                                   |          |

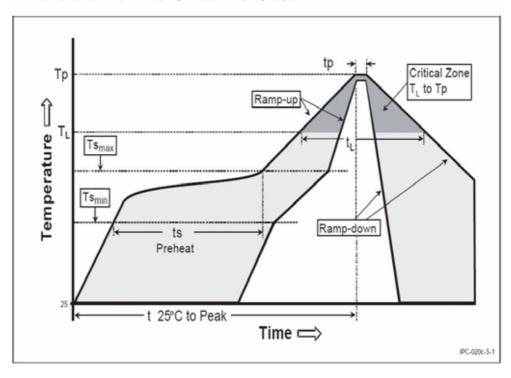

| 9.5 MOISTURE SENSITIVITY LEVEL AND SOLDERING                    | 57       |

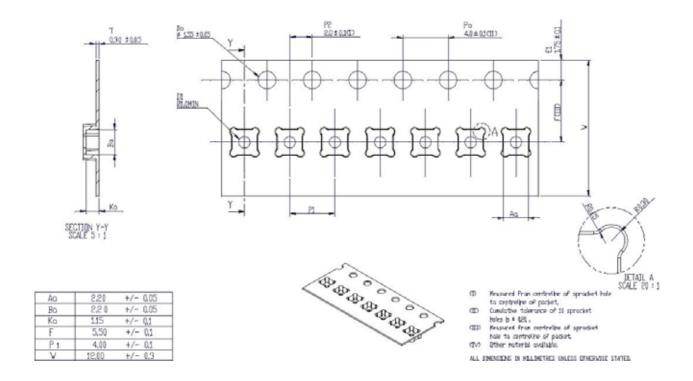

| 9.6 TAPE AND REEL SPECIFICATION                                 | 58       |

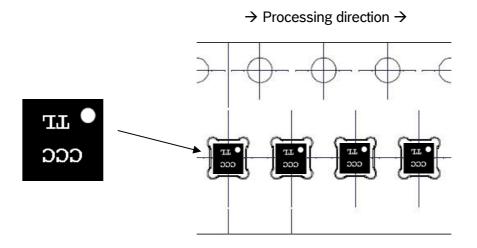

| 9.7 ORIENTATION                                                 | 59       |

| 9.8 ROHS COMPLIANCY                                             | 59       |

| 9.9 HALOGEN CONTENT                                             | 59       |

| 9.10 NOTE ON INTERNAL PACKAGE STRUCTURE                         | 59       |

| 9.11 HANDLING INSTRUCTION                                       | 60       |

| 10. LEGAL DISCLAIMER                                            | 61       |

| 10.1 Engineering samples                                        | 61       |

| 10.2 PRODUCT USE                                                | 61       |

| 10.3 APPLICATION EXAMPLES AND HINTS                             | 61       |

| 11. DOCUMENT HISTORY AND MODIFICATIONS                          | 62       |

### 1. Specification

If not stated otherwise, the given values are maximum values over lifetime and full performance temperature and voltage ranges. Min/max. data represent 3-sigma values.

Table 1: Operating conditions, output signal and mechanical characteristics

| Parameter                           | Symbol              | Condition                                | Min                   | Тур               | Max                   | Units |

|-------------------------------------|---------------------|------------------------------------------|-----------------------|-------------------|-----------------------|-------|

|                                     |                     | OPERATING CONDIT                         | IONS                  |                   |                       |       |

|                                     | g <sub>FS2g</sub>   |                                          |                       | ±2.0              |                       | g     |

| Assolute in Danse                   | <b>g</b> FS4g       | switchable via                           |                       | ±4.0              |                       | g     |

| Acceleration Range                  | <b>g</b> FS8g       | serial digital<br>interface              |                       | ±8.0              |                       | g     |

|                                     | g <sub>FS16g</sub>  |                                          |                       | ±16.0             |                       | g     |

| Supply Voltage<br>Analog Domain     | $V_{DDA}$           |                                          | 1.62                  | 1.8               | 1.98                  | V     |

| Supply Voltage<br>Digital Domain    | $V_{DDD}$           |                                          | 1.62                  | 1.8               | 1.98                  | V     |

| Supply Voltage<br>I/O Domain        | $V_{DDIO}$          |                                          | 1.62                  |                   | 3.6                   | ٧     |

| Voltage Input                       | $V_{IL\;SPI}$       | SPI                                      |                       |                   | $0.1*V_{DDIO}$        | V     |

| Low Level                           | $V_{\text{IL I2C}}$ | I <sup>2</sup> C                         |                       |                   | 0.3*V <sub>DDIO</sub> | V     |

| Voltage Input                       | $V_{IHSPI}$         | SPI                                      | 0.9*V <sub>DDIO</sub> |                   |                       | V     |

| High Level                          | V <sub>IH I2C</sub> | I <sup>2</sup> C                         | 0.7*V <sub>DDIO</sub> |                   |                       | V     |

| Voltage Output<br>High Level        | $V_{OH}$            | SPI & I <sup>2</sup> C                   |                       | $V_{\text{DDIO}}$ |                       | ٧     |

| Voltage Output                      | V <sub>OL SPI</sub> | SPI                                      |                       | GND               | _                     | V     |

| Low Level                           | $V_{\text{OL I2C}}$ | $I^2$ C, R <sub>P</sub> ≥ 680 Ω          |                       |                   | $0.2*V_{DDIO}$        | V     |

| Supply Current in<br>Normal Mode    | I <sub>DD</sub>     | Nominal $V_{DD}$ supplies at $T_A$ =25°C |                       | 250               |                       | μА    |

| Supply current in<br>Low Power Mode |                     |                                          |                       | < 10              |                       | μΑ    |

| Supply Current in<br>Suspend Mode   | I <sub>DDsd</sub>   | Nominal $V_{DD}$ supplies at $T_A$ =25°C |                       |                   | < 1                   | μΑ    |

| Wake-Up Time                        | t <sub>w_up</sub>   | from sleep/suspend<br>mode @1kHz bw      |                       |                   | 1.2                   | ms    |

Page 6

| Start-Up Time                      | t <sub>s_up</sub> | POR @1kHz bw                                                                                                              |     | 1.5                                    |     | ms     |  |

|------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------|-----|--------|--|

| Operating<br>Temperature           | T <sub>A</sub>    |                                                                                                                           | -40 |                                        | +85 | °C     |  |

|                                    |                   | OUTPUT SIGNAL                                                                                                             |     |                                        |     |        |  |

| Device resolution                  | $D_{res}$         | g <sub>FS2g</sub>                                                                                                         |     | 62.5                                   |     | mg     |  |

|                                    | S <sub>2g</sub>   | g <sub>FS2g</sub> , T <sub>A</sub> =25°C                                                                                  |     | 16                                     |     | LSB/g  |  |

| Sensitivity                        | S <sub>4g</sub>   | $g_{FS4g}$ , $T_A$ =25°C                                                                                                  |     | 8                                      |     | LSB/g  |  |

|                                    | S <sub>8g</sub>   | g <sub>FS8g</sub> , T <sub>A</sub> =25°C                                                                                  |     | 4                                      |     | LSB/g  |  |

|                                    | S <sub>16g</sub>  | g <sub>FS16g</sub> , T <sub>A</sub> =25°C                                                                                 |     | 2                                      |     | LSB/g  |  |

| Sensitivity<br>Temperature Drift   | TCS               | $\text{-40°C} \leq T_A \leq \text{+85°C}$                                                                                 |     | ±0.03                                  |     | %/K    |  |

| Zero-g Offset                      | Off               | $T_A=25^{\circ}\text{C},$ $V_{DDA}=1.8V,$ $g_{FS2g}$                                                                      |     | ±95                                    |     | mg     |  |

| Zero-g Offset<br>Temperature Drift | тсо               | $\label{eq:continuous} \begin{array}{c} \text{-40°C} \leq T_{\text{A}} \leq \text{+85°C,} \\ g_{\text{FS2g}} \end{array}$ |     | ±2                                     |     | mg/K   |  |

| Bandwidth                          | bw                | 1 <sup>st</sup> order filter,<br>switchable                                                                               |     | 32/64/<br>125/<br>250/<br>500/<br>1000 |     | Hz     |  |

| Nonlinearity                       | NL                | best fit straight line                                                                                                    |     | ±2                                     |     | %FS    |  |

|                                    | TSTx              | depending on sensitivity/                                                                                                 |     | 0.7g*S <sub>x</sub>                    |     | LSB    |  |

| Self Test Response                 | TSTy              |                                                                                                                           |     | 2.0g*S <sub>y</sub>                    |     | LSB    |  |

|                                    | TSTz              | acceleration range                                                                                                        |     | 0.6g*S <sub>z</sub>                    |     | LSB    |  |

| Output Noise                       | n <sub>rms</sub>  | rms,<br>Nominal $V_{DD}$<br>supplies $T_A$ =25°C,<br>BW = 1kHz                                                            |     | 2                                      |     | mg/√Hz |  |

| MECHANICAL CHARACTERISTICS         |                   |                                                                                                                           |     |                                        |     |        |  |

| Cross Axis<br>Sensitivity          | Ī                 | relative contribution between 3 axes                                                                                      |     | 2                                      |     | %      |  |

| Alignment Error                    | $\delta_{a}$      | relative to package outline                                                                                               |     | ±0.5                                   |     | 0      |  |

BST-BMA220-DS003-08 | Revision 1.15 | August 2011

Bosch Sensortec

### 2. Absolute maximum ratings

All voltages below are given with respect to GND.

Table 2: Absolute maximum ratings

| Parameter                 | Condition                             | Min  | Max             | Units |

|---------------------------|---------------------------------------|------|-----------------|-------|

| Voltage at supply pad     | $V_{\text{DDD}}$ and $V_{\text{DDA}}$ | -0.3 | 2.0             | V     |

|                           | $V_{DDIO}$                            | -0.3 | 4.25            | V     |

| Voltage at any logic pad  | Non-supply pad                        | -0.3 | $V_{DDIO}$ +0.3 | V     |

| Storage temperature range | rel. humidity <=65%                   | -50  | +150            | °C    |

|                           | duration ≤ 200µs                      |      | 10,000          | g     |

| Mechanical shock          | duration ≤ 1.0ms                      |      | 2,000           | g     |

|                           | free fall onto<br>hard surfaces       |      | 1.8             | m     |

| ESD                       | HBM, at any pin                       |      | 2               | kV    |

| LOD                       | CDM                                   |      | 500             | V     |

### 3. Block diagram

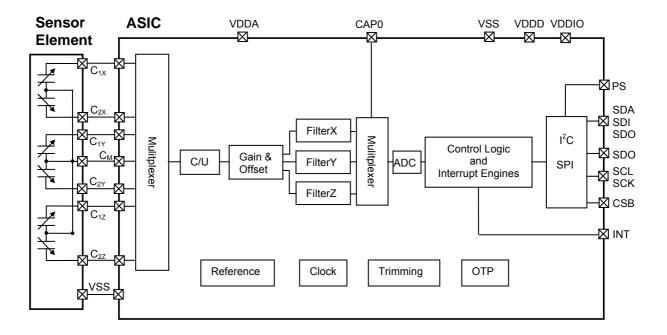

The following figure describes the functionality of the two basic parts of the sensor module, namely mechanical sensor element and evaluating ASIC.

Figure 1: Block diagram BMA220

### 4. Global memory map

The memory map below shows all externally accessible data registers which are needed to operate BMA220. The left columns show the memory addresses. The columns in the middle depict the content of each register bit. The colors of the bits indicate whether they are read-only, write-only or read- and writable. The memory is volatile so that the writable content has to be rewritten after each power-on.

The extended address space greater than 0x19 (SPI) / 0x32 (I<sup>2</sup>C) is not shown. These registers are reserved for further Bosch factory testing and trimming.

| Register<br>Address<br>(I <sup>2</sup> C) | Register<br>Address<br>(SPI) | bit7                       | bit6       | bit5         | bit4           | bit3        | bit2             | bit1         | bit0         | default after power-up |

|-------------------------------------------|------------------------------|----------------------------|------------|--------------|----------------|-------------|------------------|--------------|--------------|------------------------|

| 0x32                                      | 0x19                         |                            |            |              | soft           | reset       |                  |              |              | 0x00                   |

| 0x30                                      | 0x18                         |                            |            |              | sus            | pend        |                  |              |              | 0x00                   |

| 0x2E                                      | 0x17                         |                            |            | unused       |                |             | WDT_TO_en        | WDT_TO_sel   | SPI3         | 0x00                   |

| 0x2C                                      | 0x16                         |                            |            |              | rese           | erved       |                  |              |              | 0x00                   |

| 0x2A                                      | 0x15                         |                            |            |              | rese           | erved       |                  |              |              | 0x00                   |

| 0x28                                      | 0x14                         |                            |            |              | rese           | erved       |                  |              |              | 0x00                   |

| 0x26                                      | 0x13                         |                            |            |              | rese           | erved       |                  |              |              | 0x00                   |

| 0x24                                      | 0x12                         |                            |            |              | rese           | erved       |                  |              |              | 0x10                   |

| 0x22                                      | 0x11                         |                            | unused     |              | sbist_sign     | sbist (c    | off,x,y,z)       | range        | e[1:0]       | 0x00                   |

| 0x20                                      | 0x10                         | serial_high_bw             |            | unused       |                |             | filt_config[3:0] |              |              | 0x00                   |

| 0x1E                                      | 0x0F                         | unused                     | sleep_en   |              | sleep_dur[2:0] |             | en_x_channel     | en_y_channel | en_z_channel | 0x07                   |

| 0x1C                                      | 0x0E                         | reset_int                  |            | lat_int[2:0] |                | en_low      | en_high_x        | en_high_y    | en_high_z    | 0x00                   |

| 0x1A                                      | 0x0D                         | en_data                    | en_orient  | en_slope_x   | en_slope_y     | en_slope_z  | en_tt_x          | en_tt_y      | en_tt_z      | 0x00                   |

| 0x18                                      | 0x0C                         |                            | unused     |              | tt_int         | low_int     | high_int         | data_int     | slope_int    | 0x00                   |

| 0x16                                      | 0x0B                         | orient_int                 |            | orient[2:0]  |                | int_first_x | int_first_y      | int_first_z  | int_sign     | 0x00                   |

| 0x14                                      | 0x0A                         |                            | unused     |              | tip_en         |             | cking [1:0]      |              | np[1:0]      | 0x08                   |

| 0x12                                      | 0x09                         | orient_ex                  | slope_filt |              |                | th[3:0]     |                  |              | dur[1:0]     | 0x45                   |

| 0x10                                      | 0x08                         | tt_filt                    |            | tt_tr        | 1[3:0]         |             |                  | tt_dur[2:0]  |              | 0xB5                   |

| 0xE                                       | 0x07                         | low_h                      | ny[1:0]    |              |                | low_d       | lur[5:0]         |              |              | 0x7F                   |

| 0xC                                       | 0x06                         |                            |            | h[3:0]       |                |             | high_            | th[3:0]      |              | 0x4E                   |

| 0xA                                       | 0x05                         | high_hy[1:0] high_dur[5:0] |            |              |                | 0x7F        |                  |              |              |                        |

| 0x8                                       | 0x04                         | acc_z<5:0> 0 0             |            |              |                |             | 0x00             |              |              |                        |

| 0x6                                       | 0x03                         | acc_y<5:0> 0 0             |            |              |                |             |                  | 0x00         |              |                        |

| 0x4                                       | 0x02                         | acc_x<5:0> 0 0             |            |              |                |             |                  | 0x00         |              |                        |

| 0x2                                       | 0x01                         |                            |            |              |                | ion ID      |                  |              |              | 0x00                   |

| 0x0                                       | 0x00                         |                            |            |              | Chi            | p ID        |                  |              |              | 0xDD                   |

Figure 2: Memory map

#### Note:

From SPI  $\rightarrow$  I<sup>2</sup>C use burst address increment in 0x02h steps.

#### 4.1 Control registers

#### 4.1.1 3-wire SPI mode selection

The BMA220 supports both 4-wire and 3-wire SPI. The protocols are exactly the same except for the fact that in 3-wire mode, the SDI pin is also used for data output.

The default mode is 4-wire SPI. If 3-wire SPI should be used, the SPI3 bit in register 0x17 (SPI) must be set to '1'.

#### 4.1.2 Low-power mode configuration

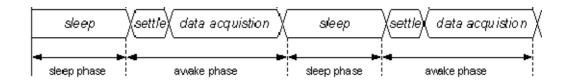

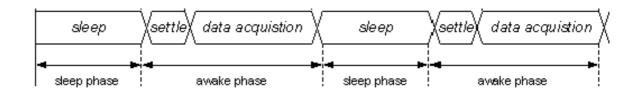

The BMA220 supports a low-power mode. In this low-power mode, the chip wakes up periodically, enables the interrupt controller and goes back to sleep if no interrupt has occurred. The procedure is the following:

- 1. Wake-up.

- 2. Enable analog front-end and convert acceleration data until the low-pass filters have settled

- 3. Enable integrated interrupt controller and evaluate interrupt conditions. Once the interrupt conditions have been evaluated and **no** interrupt has occurred, the chip goes back to sleep. If no interrupt is enabled, the acceleration for x-, y- and z-axes are converted once and then the chip goes back to sleep.

- 4. Sleep for the programmed duration.

Figure 3: sleep and awake phases

The low-power mode can be enabled by setting the <code>sleep\_en</code> bit in Reg. 0x0F (SPI) / 0x1E ( $l^2$ C) and by enabling the data ready interrupt (or any other interrupt, see chapter 5). The sleep duration can be configured via the <code>sleep\_dur</code> bits in Reg 0x0F (SPI) / 0x1E ( $l^2$ C).

Table 3: Sleep durations for low-power mode

| sleep_dur setting | Sleep Duration |

|-------------------|----------------|

| 000               | 2ms            |

| 001               | 10ms           |

| 010               | 25ms           |

| 011               | 50ms           |

| 100               | 100ms          |

| 101               | 500ms          |

| 110               | 1s             |

| 111               | 2s             |

#### 4.1.3 Low-power mode dimensioning

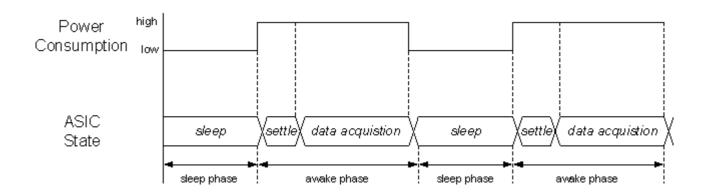

The power saving that can be achieved depends on the programmed sleep duration and the configured bandwidth. Figure 4 explains the power consumption in relation to the different ASIC states (sleep and awake phases).

Figure 4: Sleep and awake phase

If a low bandwidth is selected, the time required for filter settling might be the dominating time. Refer to table 2 for the appropriate dimensioning of the attainable current saving.

Table 4: Approximate awake phase times for 1 data sample

| Filter cut-off | Settling time |

|----------------|---------------|

| 32 Hz          | 16690µs       |

| 64 Hz          | 8690µs        |

| 125 Hz         | 4690µs        |

| 250 Hz         | 2690µs        |

| 500 Hz         | 1690µs        |

| 1000 Hz        | 1190µs        |

#### 4.1.4 Channel activation / de-activation

In order to optimize further power consumption of the BMA220, data evaluation of individual axes can be deactivated. Per default, all three axes are active. If the user wants to disable one or more axes, the appropriate  $en_?\_channel$  bits at address 0x0F (SPI) / 0x1E ( $I^2C$ ) must be set to '0'.

Page 12

#### 4.1.5 Soft-reset

The BMA220 can be put into a soft-reset state by performing a read from the soft-reset address. To bring the chip back into operation, another read must be performed from the same memory address. The reading returns value 0xFF if the system was in soft reset mode; otherwise it returns value 0x00.

Please note that all internal configuration data programmed by the user will be lost.

#### 4.1.6 Suspend mode

The BMA220 can be put into a suspend mode e.g. to easily achieve a power consumption below  $1\mu A$  by performing a read from the suspend address. To bring the chip back into normal mode operation, another read must be performed from the same memory address. The reading returns value 0xFF if the system was in suspend mode, otherwise it returns value 0x00.

Please note, that during suspend, all analog modules expect for power-on-reset will be disabled. Only reads through the serial interface are supported during suspend.

#### 4.2 Setting registers

#### 4.2.1 Acceleration range and sensitivity setting

The BMA220 has four different range settings for the full scale acceleration range. In dependence of the use case always the lowest full scale range with the maximum resolution should be selected. Please refer to literature to find out, which full scale acceleration range, which sensitivity or which resolution is the ideal one.

This can be configured via the register bits range[1:0] at address 0x11 (SPI) / 0x22 (SPI).

The following table shows the range bits with corresponding scale and resolution.

Table 5: Acceleration resolution

| range[1:0] | Full Scale | Sensitivity | Resolution   | Example use case          |

|------------|------------|-------------|--------------|---------------------------|

| '00'       | ±2g        | 16 LSB / g  | 62.5mg / LSB | Orientation recognition   |

| '01'       | ±4g        | 8 LSB / g   | 125mg / LSB  | Gaming                    |

| '10'       | ±8g        | 4 LSB / g   | 0.25g / LSB  | Garining                  |

| '11'       | ±16g       | 2 LSB / g   | 0.5g / LSB   | Shock vibration detection |

Page 13

#### 4.2.2 Filter and bandwidth configuration

The BMA220 has a digital filter that can be configured by setting the corresponding register bits  $filter\_config[3:0]$  at address 0x10 (SPI) / 0x20 ( $I^2C$ ). For compatibility reasons the settings are defined based on BMA120. To always ensure an ideal cut off frequency of the filter the BMA220 is adjusting the sample rate automatically.

Table 6: Digital filter configuration

| filter_config[3:0]               | 0x5  | 0x4  | 0x3   | 0x2   | 0x1   | 0x0  |

|----------------------------------|------|------|-------|-------|-------|------|

| digital filter cut-off frequency | 32Hz | 64Hz | 125Hz | 250Hz | 500Hz | 1kHz |

The internal SC-filter has a fix cut-off frequency at 1 KHz. In addition to the internal SC-filter a digital filter is available which is providing a filtered and an unfiltered data stream for all of the 3 axes of acceleration.

If application specific reasons require a bandwidth configuration <32Hz, please contact your Bosch Sensortec representative.

#### 4.3 Data registers

#### 4.3.1 Acceleration data read-out

The acceleration data can be read-out through addresses 0x02 (SPI) / 0x04 (I<sup>2</sup>C) through 0x04 (SPI) / 0x08 (I<sup>2</sup>C). The acceleration data is in 2's complement according to the table below.

An efficient way to read out the acceleration data in I<sup>2</sup>C or SPI mode is the burst-accesses. During such an access, the BMA220 automatically increments the read address after each byte. By using this kind of access, the data transferred over the I<sup>2</sup>C bus can be reduced by up to 50%.

Decimal value Acceleration (in 2g range mode)

+ 31

Table 7: Acceleration register content

0 0g ... ... -32 - 2.0g

+ 1.94g

Per default, the bandwidth of the data being read-out is limited by the internal low-pass filters according to the filter configuration. However, it is possible to read-out data only  $\mathbf{1}^{\text{st}}$  order filtered (1 kHz) even though the internal filters are configured differently.

The reason for this feature is that the interrupt controller may operate on low-bandwidth data while the external master still needs to operate on high-bandwidth data.

Unfiltered (1kHz high-bandwidth) data can be read-out through the serial interface when the serial\_high\_bw bit is set to '1'. Per default, filtered data is read-out through the serial interface.

#### 4.3.2 Chip / revision ID

The chip ID and the revision ID can be read-out through addresses 0x00 (SPI &  $I^2C$ ) and 0x01 (SPI) / 0x02 ( $I^2C$ ).

Table 8: Chip and revision ID

| Chip ID | Revision ID |

|---------|-------------|

| 0xDD    | 0x00        |

Page 15

#### 4.4 Interrupt control registers

The BMA220 features a programmable interrupt controller that directly supports common mobile applications like tap sensing detection, orientation recognition and any-motion detection.

Supported types of interrupts:

- Any-motion (slope) detection

- Tap/double-tap sensing

- Orientation recognition

- Low-g detection

- High-g detection

- Data-ready interrupt

The configuration and status register bits of all interrupt engines and the exact interrupt functionality are given in chapter 5.

### 5. Interrupt controllers

The BMA220 integrates a programmable interrupt controller. It can be configured via  $SPI/I^2C$  to monitor individual axes (X-, Y- and Z-axis) and check whether certain conditions apply (e.g. the acceleration on one axis exceeds a certain threshold). The interrupt controller of the BMA220 is capable of checking for certain conditions simultaneously.

If at least one of the configured conditions applies, an interrupt (logic '1') is issued through the INT pin of the sensor. More details about the triggering condition (e.g. the type of the interrupt or the axis that triggered the interrupt) are saved in internal status registers and can be read out through the digital interface.

It is recommended to reset the interrupt controller by setting reset\_int to '1' when the interrupt settings has been set or changed.

#### 5.1 Latched vs. non-latched modes

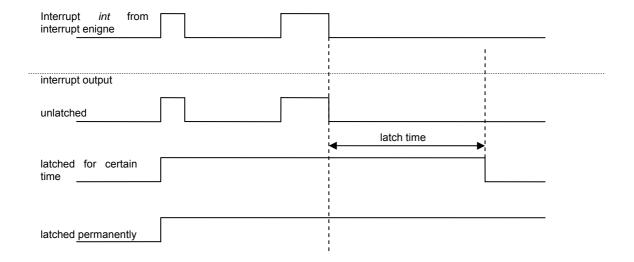

The interrupt controller can be used in two modes

- Latched mode: Once one of the configured interrupt conditions applies, the INT pin is asserted and must be reset by the external master through the digital interface.

- Non-Latched mode: The interrupt controller clears the INT signal once the interrupt condition no longer applies.

The interrupt output can be programmed by  $lat_int[2:0]$  to be either unlatched ('000') or latched permanently ('111') or have the latch time of 0.25s('001')/0.5s('010')/1s('011')/2s('100')/4s ('101')/8s('110'). The setting of these bits applies to all types of interrupts.

Figure 5: Interrupt output

Page 17

#### 5.2 Supported types of interrupts

The following interrupt modes are provided by the BMA220.

- Any-motion (slope) detection

- Tap/double-tap sensing

- Orientation recognition

- Low-g detection

- High-g detection

- Data-ready interrupt

#### 5.3 Power-saving modes

In order to reduce power consumption of the sensor itself, the BMA220 supports a low-power mode in which the ASIC wakes up periodically, checks whether any of the configured interrupt conditions apply and then either goes back to sleep (no interrupt) or stays awake (interrupt).

The BMA220's PMU (power management unit) controls the transitions from the 'awake state' into the 'sleep state' and vice versa.

In normal mode, the interrupt controller is permanently turned on to continuously process the incoming data. In low-power mode, the interrupt controller will be turned on by the PMU once the chip has fully woken up. The time it takes before the sensor can go back to sleep is determined by the active interrupt engines. Once all active engines indicate that no interrupt condition applies, the PMU will switch the sensor back into sleep state.

Furthermore the applied interrupt condition can be used not only to enable the low-power mode of the sensor itself but for the whole system. This enables a dramatically reduced power consumption of the whole system. The result is an extended operation and stand-by time e.g. of mobile devices in an order of magnitude.

Page 18

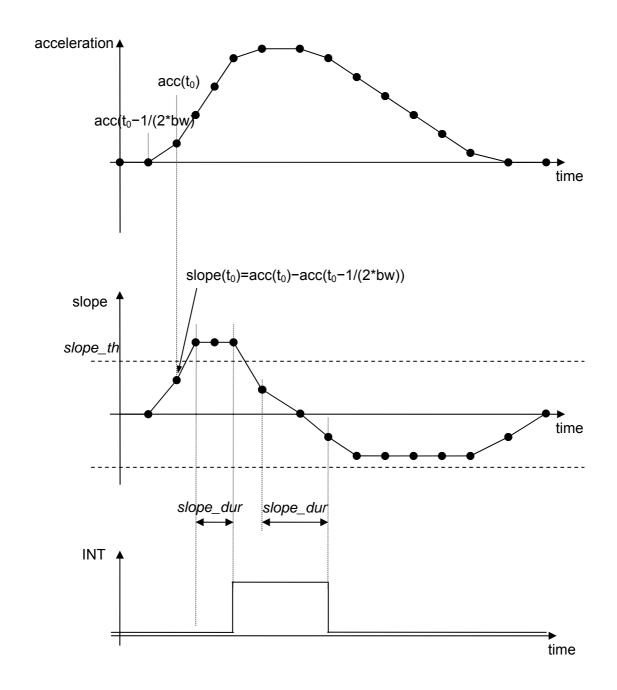

#### 5.4 Any-motion (slope) detection

The any-motion detection uses the slope between two successive acceleration signals to detect changes in motion. It generates an interrupt when a preset threshold  $slope\_th$  is exceeded. The threshold can be configured between 0 and the maximum acceleration value corresponding to the selected measurement range. The time difference between the successive acceleration signals depends on the bandwidth of the configurable low pass filter and corresponds roughly to 1/(2\*bandwidth) ( $\Delta t = 1/(2*bw)$ ).

In order to suppress failure signals, the interrupt is only generated if a certain number *slope\_dur* of consecutive slope data points is above the slope threshold *slope\_th*.

If the same number of data points falls below the threshold, the interrupt is reset.

The criteria for any-motion detection are fulfilled and the slope interrupt is generated if any of the enabled channels exceeds the threshold *slope\_th* for *slope\_dur* consecutive times. As soon as all the enabled channels fall or stay below this threshold for *slope\_dur* consecutive times the interrupt is reset unless interrupt signal is latched.

The any-motion interrupt logic sends out the signals of the axis that has triggered the interrupt (slope\_first\_x, slope\_first\_y, slope\_first\_z) and the signal of motion direction (slope\_sign).

When serial interface is active, any-motion detection logic is enabled if any of the any-motion enable register bits is set. To disable the any-motion interrupt, clear all the axis enable bits.

In the dedicated wake-up mode (6.1), all three axes are enabled for any-motion detection whether the individual axis enable bits are set or not.

Figure 6: Any-motion (slope) interrupt detection

The following table shows the signals used in any-motion detection. After reset, a default value will be assigned to each register.

Page 20

Table 9: Control and status register for any motion detection

| Name                                            | Register<br>Address<br>(SPI) * | Description                                                                                                                                                                | Number of bits         | Reset-value                |

|-------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|

| en_slope_x<br>en_slope_y<br>en_slope_z          | 0x0D.5<br>0x0D.4<br>0x0D.3     | enable slope detection on x-axis<br>enable slope detection on y-axis<br>enable slope detection on z-axis                                                                   | 3                      | "000"                      |

| slope_th                                        | 0x09[5:2]                      | define the threshold level of the slope 1 LSB threshold is 1 LSB of acc_data                                                                                               | SLOPE_T<br>H_NUM<br>4  | SLOPE_TH_I<br>NIT ("0001") |

| slope_dur                                       | 0x09[1:0]                      | define the number of consecutive slope data points above slope_th which are required to set the interrupt  ("00" = 1,"01" = 2,"10" = 3, "11" = 4)                          | SLOPE_D<br>UR_NUM<br>2 | SLOPE_DUR<br>_INIT ("01")  |

| slope_filt                                      | 0x09.6                         | defines whether filtered or unfiltered acceleration data should be used (evaluated) ('0'=unfiltered, '1'=filtered)                                                         | 1                      | '1'                        |

| slope_int                                       | 0x0C.0                         | whether slope interrupt has been triggered                                                                                                                                 | 1                      | '0'                        |

| slope_first_x<br>slope_first_y<br>slope_first_z |                                | whether x-axis has triggered the interrupt (0=no, 1=yes) whether y-axis has triggered the interrupt (0=no, 1=yes) whether z-axis has triggered the interrupt (0=no, 1=yes) | 3                      | "000"                      |

| slope_sign                                      |                                | global register bit for all interrupts define the slope sign of the triggering signal (0=positive slope, 1=negative slope)                                                 | 1                      | '0'                        |

<sup>\*</sup> For determining the corresponding I<sup>2</sup>C register address, please refer to figure 2 in chapter 4 (memory map)

BST-BMA220-DS003-08 | Revision 1.15 | August 2011

Bosch Sensortec

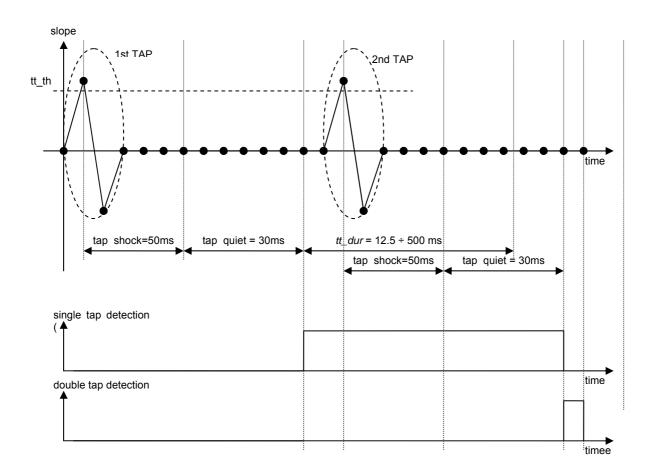

Figure 7: Tap sensing interrupt detection

When a tap-sensing interrupt is triggered, the following details can be read from the corresponding registers: the axis that has triggered the interrupt (*tt\_first\_x*, *tt\_first\_y*, *tt\_first\_z*) and the motion direction of the triggering acceleration signal (*tt\_sign*).

Page 22

#### 5.5 Tap-sensing

Tap sensing has the same functionality as a common laptop touch-pad. If 2 taps occur within a short time, a pre-defined action will be performed by the system. If time between 2 taps is too long or too short no action happens.

When the serial interface is activated, tap sensing is enabled if any of the tap sensing enable register bits are set ( $en_t t_x$ ,  $en_t t_y$ ,  $en_t t_z$ ). To disable the tap sensing interrupt, clear all the axis enable bits.

When the preset threshold *tt\_th* is exceeded, a tap-shock is detected. The tap sensing interrupt is generated only when a second tap is detected within a specified period of time.

The slope between two successive acceleration data has to exceed *tt\_th* to detect a tap-shock. The time difference between the two successive acceleration values depends on the bandwidth of the low pass filter. It roughly corresponds to 1/(2\*bandwidth).

The time delay *tt\_dur* between two taps is typically between 12,5ms and 500ms. The threshold is typically between 0.7g and 1.5g in 2g measurement range. Due to different coupling between sensor and device shell (housing) and different measurement ranges of the sensor these parameters are configurable.

The criteria for tap sensing are fulfilled and the interrupt is generated if the second tap occurs after  $tap\_quiet$  and within  $tt\_dur$ . The tap sensing direction is determined by the 1<sup>st</sup> tap. During  $tt\_quiet$  period (30ms) no taps should occur. If a tap occurs during  $tap\_quiet$  period it will be connoted as new tap.

The slope detection interrupt logic stores the direction of the (first) tap-shock in a status register. This register will be locked for *tap\_shock=*50ms in order to prevent other slopes to overwrite this information.

When a tap sensing interrupt is triggered, the signals of the axis that has triggered the interrupt  $(tt\_first\_x, tt\_first\_y, tt\_first\_z)$  and the signal of motion direction  $(tt\_sign)$  are stored in the corresponding registers.

The axis on which the biggest slope occurs will trigger the first tap. The second tap will be triggered by any axis (not necessarily same as the first tap).

The register *tap\_en* defines whether single tap or double tap shall be detected.

In dedicated tap sensing mode, all three axes are enabled for double tap sensing detection.

Table 10: Control and status register for tap sensing

| Name                                   | Register<br>Address<br>(SPI) * | Description                                                                                                                                                                | Number of bits      | Reset-value          |

|----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|

| en_tt_x<br>en_tt_y<br>en_tt_z          | 0x0D.2<br>0x0D.1<br>0x0D.0     | enable tap sensing detection on x-axis enable tap sensing detection on y-axis enable tap sensing detection on z-axis                                                       | 3                   | "000"                |

| tt_th                                  | 0x08[6:3]                      | define the threshold level of the tap<br>sensing slope<br>1 LSB is 2*(LSB of acc_data)                                                                                     | TT_TH_NUM<br>4      | TT_TH_INIT<br>"0110" |

| tt_dur                                 | 0x08[2:0]                      | define the maximum delay of the<br>second tap after the shock<br>suppression (50, 105, 150, 219,<br>250, 375, 500, 700)ms                                                  | TT_DUR_NU<br>M<br>3 | TT_DUR_INIT<br>"101" |

| tt_filt                                | 0x08.7                         | defines whether filtered or unfiltered acceleration data should be used (evaluated) ('0'=unfiltered, '1'=filtered)                                                         | 1                   | <b>'1'</b>           |

| tip_en                                 | 0x0A.4                         | whether tap or double-tap shall be detected (0= double tap, 1=tap)                                                                                                         | 1                   | '0'                  |

| tt_int                                 | 0x0C.4                         | whether tap sensing interrupt has been triggered (0=no, 1=yes)                                                                                                             | 1                   | <b>'0'</b>           |

| tt_samp                                | 0x0A[1:0]                      | number of data to be sampled after wake-up '00' => 2 data '01' => 4 data '10' => 8 data '11' => 16 data                                                                    | 2                   | '00'                 |

| tt_first_x<br>tt_first_y<br>tt_first_z |                                | whether x-axis has triggered the interrupt (0=no, 1=yes) whether y-axis has triggered the interrupt (0=no, 1=yes) whether z-axis has triggered the interrupt (0=no, 1=yes) | 3                   | "000"                |

| tt_sign                                |                                | give the slope sign of the triggering signal (0=positive, 1=negative)                                                                                                      | 1                   | '0'                  |

<sup>\*</sup> For determining the corresponding I<sup>2</sup>C register address, please refer to figure 2 in chapter 4 (memory map)

BST-BMA220-DS003-08 | Revision 1.15 | August 2011

Bosch Sensortec

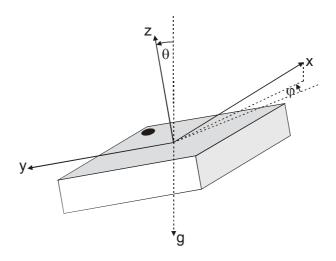

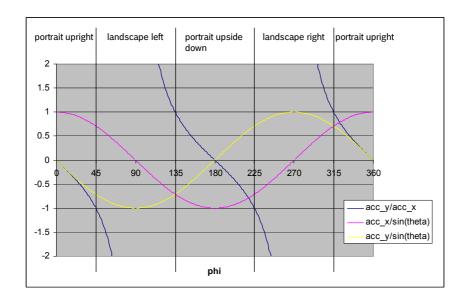

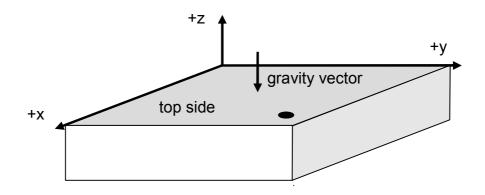

#### 5.6 Orientation recognition

The orientation recognition feature informs on an orientation change of the sensor with respect to the gravitational field vector g. The measured acceleration vector components with respect to the gravitational field look as follows.

[with respect to graviational field vector g (black dot = pin 1 identifier)]

Figure 8: Definition of acceleration-vector components

```

acc_x = 1g \cdot sin\theta \cdot cos\phi

acc_y = -1g \cdot sin\theta \cdot sin\phi

acc_z = 1g \cdot cos\theta

\rightarrow acc_y/acc_x = -tan\phi

```

The output register is called *orient* and defined in the following way:

```

'0xx' upward looking (z>0):

'000' portrait upright (315°<\phi<45°)

'001' portrait upside down (135°<\phi<225°)

'010' landscape left (45°<\phi<135°)

'011' landscape right (225°<\phi<315°)

'1xx' downward looking (z<0), xx as before

```

Figure 9: Orientation definition and interrupt thresholds with respect to the angle phi φ

The criteria for portrait/landscape switching is fulfilled and the interrupt is generated when the threshold  $|acc_y/acc_x|=1$  is crossed (i.e. 45°, 135°, 225°, 315°). As soon as the interrupt is set, no new interrupt is generated within the hysteresis level of 0.66< $|acc_y/acc_x|<1.66$  corresponding to a hysteresis interval of  $\pm 13\%$  around the threshold.

It is possible to block the orientation detection depending on certain conditions (no orientation interrupt will be triggered). This orientation interrupt blocking feature is configurable via the *orient\_blocking*[1:0] bits in the following manner:

- '00' → interrupt blocking is completely disabled.

- '01'  $\rightarrow$  no interrupt is generated, when |z|>0.9g OR |x|+|y| < 0.4g OR when the slopes of the acceleration data exceeds 0.2g (sample-to-sample).

- '10'  $\rightarrow$  no interrupt is generated, when |z|>0.9g OR |x|+|y| < 0.4g OR while the slopes of the acceleration data exceeds 0.3g (sample-to-sample).

- '11'  $\rightarrow$  no interrupt is generated, when |z|>0.9g OR |x|+|y| < 0.4g OR while the slopes of the acceleration data exceeds 0.4g (sample-to-sample).

For all states where interrupt blocking through slope detection is used, the interrupt should be re-enabled after the slope has been below the threshold for 3 times in a row.

For all states where interrupt blocking is enabled, in order to trigger the interrupt, the orientation should remain the same (stable) until the timer runs out (for ~100ms). The timer starts to count when orientation changes between two consecutive samples. If the orientation changes while timer is still counting, the timer is restarted.

The criteria for switching from upward to downward looking fulfilled and the interrupt is generated when the threshold z=0g is crossed. As soon as the interrupt is set, no new interrupt is generated within the hysteresis level of -0.4g<z<0.4g (i.e. ±25° tilt around vertical position).

Page 26

The given specification is valid for an upright mounted PCB. In order to enable also horizontal mounting, x and z axis can be exchanged via the register *orient\_ex*. The x-, y-, z-axis will keep right-hand principle after the exchange.

When serial interface is active, orientation detection is enabled if the enable bit  $en\_orient$  is set. To disable the orientation interrupt, clear the enable bit.

When the dedicated orientation mode is active, the orientation is given by certain output pins corresponding to the above-given definition of the *orient* register. For details on the output pins see section 6.1.

In case the orientation interrupt condition has been satisfied and interrupt is not latched, *int* signal is asserted for one data sampling period unless no-reset condition applies.

Table 11: Control and status register for orientation recognition

| Name            | Register<br>Address<br>(SPI) * | Description                                                                                                                                                                                                                                                     | Number of bits | Reset-<br>value          |

|-----------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|

| orient_ex       | 0x09.7                         | exchange x- and z-axis in algorithm, i.e x or z is relevant axis for upward/downward looking recognition (0=z, 1=x)                                                                                                                                             | 1              | '0'                      |

| Orient          | 0x0B[6:4]                      | give the orientation of the sensor<br>with respect to the gravitational<br>force                                                                                                                                                                                | 3              | ORIENT<br>_INIT<br>'000' |

| orient_int      | 0x0B.7                         | whether orientation interrupt has been triggered (0=no, 1=yes)                                                                                                                                                                                                  | 1              | '0'                      |

| en_orient       | 0x0D.6                         | enable signal for orientation detection                                                                                                                                                                                                                         | 1              | '0'                      |

| orient_blocking | 0x0A                           | Enable/configure orientation interrupt disable criteria. '00' -> no slope, no wait '01' -> no slope, wait-only (~100ms) '10' -> wait 100ms +  z -criteria,  x + y -criteria and <0.2g slope '11' -> wait 100ms +  z -criteria,  x + y -criteria and <0.4g slope | 2              | '10'                     |

<sup>\*</sup> For determining the corresponding I<sup>2</sup>C register address, please refer to figure 2 in chapter 4 (memory map)

#### 5.7 Low-g detection

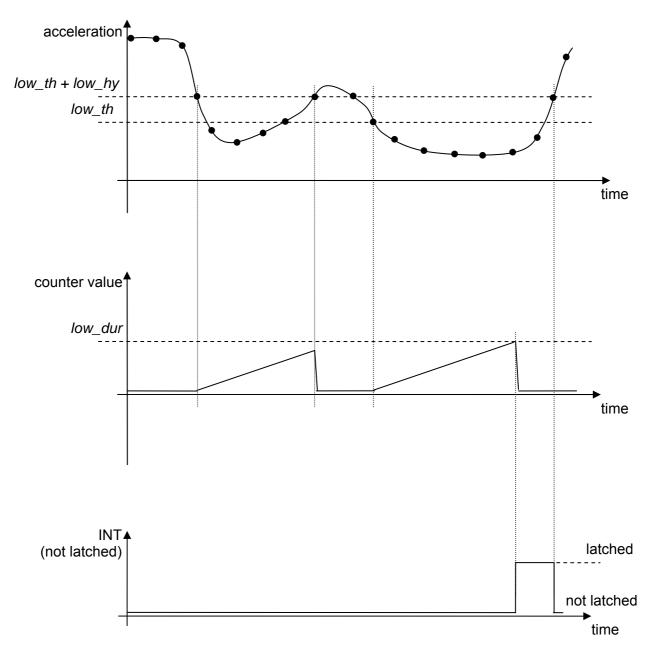

For freefall detection, the absolute values of the acceleration data of all axes are observed (global criteria). A low-g situation is likely to occur when all axes fall below a lower threshold  $low\_th$ . The interrupt will be generated if the measured acceleration falls below the threshold and stays below the hysteresis level  $low\_th+low\_hy$  for a minimum number of data points ( $low\_dur$ ). Thus, the duration of a released interrupt is depending on the data sampling rate which is related to the bandwidth.

Figure 10: Low-g interrupt detection

Table 12: Control and status register for low-g detection

| Name    | Register<br>Address<br>(SPI) * | Description                                                                                                | Number of bits   | Reset-value                       |

|---------|--------------------------------|------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------|

| Low_th  | 0x06[7:4]                      | define the low-g threshold level 1 LSB is 2*(LSB of acc_data)                                              | LOW_TH_NUM<br>4  | LOW_TH_INIT<br>"0100"             |

| Low_hy  | 0x07[7:6]                      | define the low-g hysteresis level 1 LSB is 2*(LSB of acc_data)                                             | LOW_HY_NUM<br>2  | LOW_HY_INI<br>T<br>"01"           |

| low_dur | 0x07[5:0]                      | define the number of measured data which has to be lower than low_th+low_hy to set the interrupt (max. 64) | LOW_DUR_NUM<br>6 | LOW_DUR_IN<br>IT<br>"111111" (3F) |

| en_low  | 0x0E.3                         | enable signal for low-g<br>detection                                                                       | 1                | <b>'</b> 0'                       |

| low_int | 0x0C.3                         | whether low-g interrupt has been triggered (0=no, 1=yes)                                                   | 1                | <b>'</b> 0'                       |

<sup>\*</sup> For determining the corresponding I<sup>2</sup>C register address, please refer to figure 2 in chapter 4 (memory map)

**BOSCH**

#### 5.8 High-g detection

For indicating high-g events, an upper threshold can be programmed. The threshold *high\_th*, the hysteresis *high\_hy* and the duration *high\_dur* are defined analogously to the low-g interrupt. The interrupt is generated if one of the three channels exceeds the threshold *high\_th* and does not fall below hysteresis level *high\_th-high\_hy* for minimum number of data points (*high\_dur*).

When the high-g interrupt is triggered, the signals of the axis that has triggered the interrupt (high\_first\_x, high\_first\_y, high\_first\_z) and the signal of motion direction (high\_sign) will be stored in the corresponding status registers.

Table 13: Control and status register for high-g detection

| Name                                         | Register<br>address<br>(SPI) * | Description                                                                                                                                                                               | Number of bits        | Reset-value                        |

|----------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|

| high_th                                      | 0x06[3:0]                      | define the high-g threshold<br>level<br>1 LSB is 2*(LSB of acc_data)                                                                                                                      | HIGH_TH_NU<br>M<br>4  | HIGH_TH_INI<br>T<br>"1110"         |

| high_hy                                      | 0x05[7:6]                      | define the high-g hysteresis<br>level<br>1 LSB is 2*(LSB of acc_data)                                                                                                                     | HIGH_HY_NU<br>M<br>2  | HIGH_HY_INI<br>T<br>"01"           |

| high_dur                                     | 0x05[5:0]                      | define the number of<br>measured signals which has<br>to be higher than<br>high_th+high_hy to set the<br>interrupt (max. 64)                                                              | HIGH_DUR_N<br>UM<br>6 | HIGH_DUR_I<br>NIT<br>"011111" (3F) |

| en_high_x en_high_y en_high_z                | 0x0E.2<br>0x0E.1<br>0x0E.0     | enable high-g detection on x-axis (0=disabled, 1=enabled) enable high-g detection on x-axis (0=disabled, 1=enabled) enable high-g detection on x-axis (0=disabled, 1=enabled)             | 3                     | "000"                              |

| high_int                                     | 0x0C.2                         | whether high-g interrupt has<br>been triggered (0=no, 1=yes)                                                                                                                              | 1                     | <b>'</b> 0'                        |

| high_first_x<br>high_first_y<br>high_first_z |                                | whether x-axis has triggered<br>the interrupt (0=no, 1=yes)<br>whether y-axis has triggered<br>the interrupt (0=no, 1=yes)<br>whether z-axis has triggered<br>the interrupt (0=no, 1=yes) | 3                     | "000"                              |

| high_sign                                    |                                | give the slope sign of the triggering signal (0=positive, 1=negative)                                                                                                                     | 1                     | '0'                                |

<sup>\*</sup> For determining the corresponding I<sup>2</sup>C register address, please refer to figure 2 in chapter 4 (memory map)

#### 5.9 Data ready detection

This interrupt provides the possibility of synchronously reading out data from the BMA220 without missing a single data point. The data update detection monitors the *data\_update* signals for all axes. It generates an interrupt as soon as the acceleration values for all enabled axes have been updated. The signal *en\_x\_channel*, *en\_y\_channel* and *en\_z\_channel* are the enable signals for the data conversion from each axis accordingly. The three enable signals can be configured by users (see section 4.1.4). For example, if all three axes are enabled, the interrupt is generated after updated signals for x-, y-, and z-axes have been detected.

When data ready detection is activated, all other interrupts are not propagated to the INT pin. However their status can still be obtained from the appropriate registers.

When the data-ready interrupt is not latched, the interrupt is cleared automatically after ~150µs.

Table 14: Control and status register for low

| Name     | Description                                                   | Number of bits | Reset-value |

|----------|---------------------------------------------------------------|----------------|-------------|

| en_data  | enable signal for data-ready detection                        | 1              | <b>'0'</b>  |

| data_int | whether data-ready interrupt has been triggered (0=no, 1=yes) | 1              | <b>'</b> 0' |

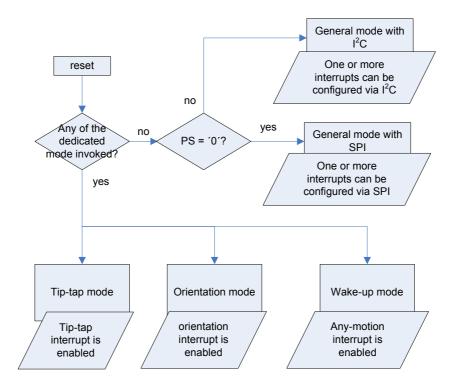

### 6. Operation modes

Depending on the configuration the BMA220 is able to operate in two different types of modes

- General mode: A serial interface is active (SPI or  $I^2C$ ). Several interrupt engines may be activated in parallel. Through the serial interface, the external master (e.g.  $\mu C$ ) can configure the interrupts of the BMA220 and read-out information about the current interrupt status.

- Dedicated mode: No serial interface is present. Internal default settings for all interrupt engines must be used. In these modes, only one interrupt engine can be active at a time. Currently, dedicated modes exist for the orientation interrupt, the tap sensing interrupt and the any-motion interrupt. The dedicated mode allows the sensor to be operated as a stand alone device, e.g. without any μC and without dealing with any acceleration data. So, in a very user friendly and convenient way taps/double-taps, orientation changes and wake-ups can be processed by a simple μC-less system.

A flow chart of the different modes is depicted in figure 11:

Figure 11: Interrupt modes

Page 32

Table 15: Mode selection

| Mode                  | PS | SCK | INT |

|-----------------------|----|-----|-----|

| SPI                   | 0  |     |     |

| I <sup>2</sup> C      | 1  |     |     |

| Dedicated orientation | Z  | 0   |     |

| Dedicated tap sensing | Z  | 1   | 0   |

| Dedicated wake-<br>up | Z  | 1   | 1   |

Please note that the PS must be connected to the appropriate supply (or left floating) at start-up (reset). The "Z-detection" circuit will be turned off when a stable value at the PS pin has been detected. Thus, the dedicated modes can be only activated after reset. Switching from one interface mode to another during operation may work but can not be guaranteed by the ASIC. The reason for this limitation is that the circuitry for z-detection consumes several µA.

For debugging/test purposes, turning-off the z-detection circuitry can be suppressed by setting the <code>comp\_always\_on</code> bit within the OTP memory range.

Table 16: Pin assignments for all operation modes

|                   | Pin #       | 2           | 1          | 10                          | 12             | 5        | 11         | 6    | 3                 | 4                | 7                | 8, 9 |

|-------------------|-------------|-------------|------------|-----------------------------|----------------|----------|------------|------|-------------------|------------------|------------------|------|

| Mo                | ode         | SDI         | SDO        | CSB                         | SCK            | INT      | PS         | CAP0 | V <sub>DDIO</sub> | V <sub>DDD</sub> | V <sub>DDA</sub> | GND  |

| SPI 4             | 4 wire      | SDI         | SDO        | CSB                         | SCK            | INT      | GND        | NC   | $V_{DDIO}$        | $V_{DDD}$        | $V_{DDA}$        | GND  |

| SPI 3             | 3 wire      | SDA         | NC         | CSB                         | SCK            | INT      | GND        | NC   | $V_{DDIO}$        | $V_{DDD}$        | $V_{DDA}$        | GND  |

| l <sup>2</sup>    | °C          | SDA         | NC         | I <sup>2</sup> C lsb_invert | SCL            | INT      | $V_{DDIO}$ | NC   | $V_{DDIO}$        | $V_{DDD}$        | $V_{DDA}$        | GND  |

| Dedicated         | Orientation | ORIENT_0    | ORIENT_1   | sleep_time                  | GND            | ORIENT_2 | NC         | NC   | $V_{DDIO}$        | $V_{DDD}$        | $V_{DDA}$        | GND  |

| mode<br>(w/o μC); | Tap sensing | SINGLE_TAP  | DOUBLE_TAP | sleep on                    | $V_{DDIO}$     | GND      | NC         | NC   | $V_{DDIO}$        | $V_{DDD}$        | $V_{DDA}$        | GND  |

| stand-alone       | Wake-up     | WAKE_UP_INT | NC         | sleep_time                  | $V_{\rm DDIO}$ | VDDIO    | NC         | NC   | $V_{DDIO}$        | $V_{DDD}$        | $V_{DDA}$        | GND  |

Page 33

### 6.1 Dedicated Modes (µC-less / stand alone)

After reset (POR, soft-reset or reset pin) the system monitors the pin PS (Protocol Select). If the pin is unconnected, an internal module detects the floating state and enables one of the dedicated modes depending on the other select pins (SCK, INT).

There are three different dedicated modes:

- Orientation detection mode: only orientation interrupt detection is enabled.

- Tap/double-tap detection mode: only tap sensing interrupt detection is enabled.

- Wake-up detection mode: only wake-up interrupt detection is enabled.

In dedicated mode, the interrupt engine uses default settings for all configuration registers. Those default settings are loaded after reset and are listed in section 5. Changing the default configuration of the registers is not possible while the chip is in the dedicated mode. Currently, in orientation and wake-up mode, the user can select between two different sleep durations via the CSB pin:

Table 17: Sleep durations for dedicated modes

| <b>Dedicated Mode</b> | CSB | Sleep duration |

|-----------------------|-----|----------------|

| Dedicated             | 0   | 100ms          |

| orientation           | 1   | 1s             |

| Dedicated wake-up     | 0   | 10ms           |

| Dedicated wake-up     | 1   | 500ms          |

| Dedicated tap-        | 0   | No sleep       |

| sensing               | 1   | 2ms            |

Table 18: Filter bandwidths for dedicated modes

| Dedicated Mode        | Bandwidth |

|-----------------------|-----------|

| Dedicated orientation | 32Hz      |

| Dedicated wake-up     | 16Hz      |

| Dedicated tap-sensing | 1kHz      |

Page 34

### 6.2 Digital interface modes

The BMA220 supports two different digital interfaces (SPI and I<sup>2</sup>C). The currently active general interface is determined by the primary input PS. The configuration of interrupt engines is fully customizable via the defined digital interface.

- SPI Active Mode: The SPI interface is enabled while PS is externally connected to GND (logic '0' detected).

- I<sup>2</sup>C Active Mode: The I<sup>2</sup>C interface is enabled while PS is externally connected to V<sub>DDIO</sub> (logic '1' detected).

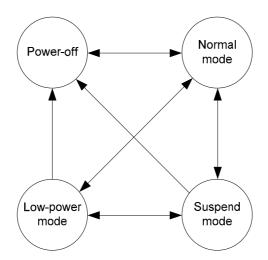

#### 6.3 Low-power mode and suspend mode

The BMA220 is optimized for low power consumption. Note: Simply switching-off of the power supplies ( $V_{DDD}$  and/or  $V_{DDA}$ ) is not a defined low-power mode.

The deactivation of  $V_{DDD}$  while  $V_{DDA}$  is active (or vice versa) is not recommended for permanent operation. With respect to the application it might be useful to switch-off  $V_{DDIO}$  while  $V_{DDD}$  and  $V_{DDA}$  are active. This condition is supported and will lead to a reduction of current consumption. The sensor register map will be reset.

To reduce current consumption in a defined way, the BMA220 supports two energy saving modes: a *suspend* mode and a *low-power mode*.

During normal mode operation, all analog modules are held powered-up and the clock for all digital modules is active. During *low-power mode*, the analog modules in the rate channel are held powered down and the clock of the digital rate, filter and trimming modules is gated. The average typical current consumption during sleep phase ( $i_{low\_power\_mode}$ ) can be estimated by the following equation:

First approximation: i<sub>sleep</sub> = i<sub>suspend</sub>

$$extstyle extstyle ext$$

For sleep phase time setting ( $t_{sleep}$ ) refer to chapter 4.1.2 table 3. For approximate awake phase time ( $t_{awake}$ ) refer to chapter 4.1.3 table 4. For current consumption in normal mode ( $i_{active}$ ) refer to chapter 1. For current consumption in suspend mode ( $i_{suspend}$ ) refer to chapter 1.

Example: Bandwidth (BW) = 1kHz, nominal supplies

- resulting awake phase for  $1^{st}$  data sample  $(t_{awake}) = 1190 \mu s = 1.190 \mu s$

- resulting sleep time (t<sub>sleep</sub>) = 50 ms

$$\textit{\varnothing typ.} \quad i_{low\_power\_mod\,e} \approx \frac{t_{sleep} \cdot i_{suspend} + t_{active} \cdot i_{active}}{t_{sleep} + t_{awake}} \approx \frac{50ms \cdot 1\mu A + 1,190ms \cdot 250\mu A}{50ms + 1,190ms} \approx 6,8\mu A$$

#### 6.4 Mode transition via interface

While the SPI or the I<sup>2</sup>C interfaces are active, transitions between the individual modes can be triggered via register accesses.

- 1. **Low power:** The BMA220 switches into low-power mode after *setting* the sleep\_en register depicted in the memory map. While the BAA220 is in low-power mode, a period wake-up is performed (please refer to section 4.1.2). Normal mode operation is resumed after *writing a '0'* to the sleep en register. The sleep register is user accessible.

- 2. **Suspend:** The BMA220 is put into suspend mode by *reading* from the suspend address. A subsequent read switches back to the previous state. Concluding, a read from the suspend address toggles the suspend register.

Figure 12: Energy saving mode transitions

#### 6.5 Self test mode

The sensor features an on-chip self-test mode. The self test is realized by a physical deflection of the seismic mass due to an applied electrostatic force. Thus, it provides full testing of the complete signal evaluation path including the micromachined sensor structure and the evaluation ASIC.

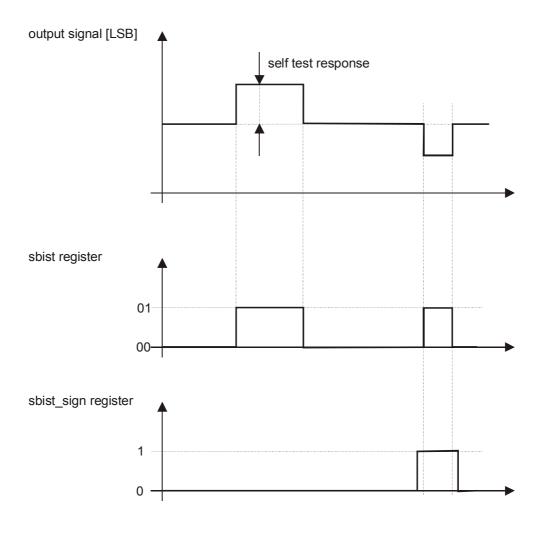

The self test mode can be activated individually for each axis by setting the the *sbist* register to the corresponding value ('01'=x-axis, '10'=y-axis, '11'=z-axis). The self test works in all acceleration ranges. By setting the *sbist\_sign* register to '1', the polarity of the self test signal can be changed from positive to negative.

The self test response remains as a static offset on the output as long as the *sbist* register is not set back to '00'. While the self test is activated, any acceleration or gravitational force applied to the sensor will be observed in the output signal as a superposition of both acceleration and self test signal.

Figure 13: Self-test mode

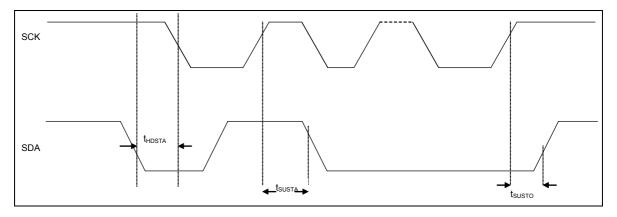

# 7. Interfaces

The BMA220 can connect to the host system via three interfaces:

- SPI (3-wire, 4-wire)

- I<sup>2</sup>C

- Dedicated mode pins (for μC-less- or stand-alone operation, see section 6.1)

In SPI and I<sup>2</sup>C mode, the BMA220 supports two commands: **read** and **write**. The ASIC can be entirely controlled through those commands. A detailed register to address mapping can be found in section 4.

It should be noted that there is no way to access internal control or configuration registers while the BMA220 is in one of its dedicated modes.

In I<sup>2</sup>C and SPI mode, the internal registers can be accessed via a 7-bit address. Each read- and write-cycle accesses 8 bits only.

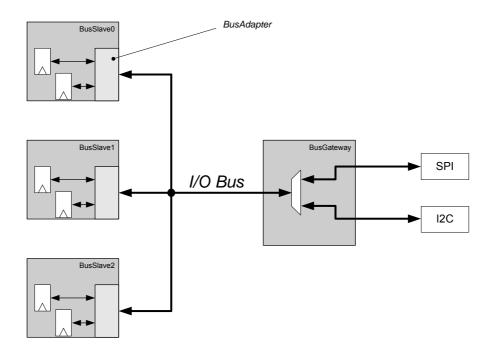

Figure 14: BMA220 I/O bus concept

The SPI and I<sup>2</sup>C interfaces are connected to the internal *bus gateway* which activates either one of the two interfaces according to the current mode. All internal digital modules accessible via the serial interfaces are called *bus slave*. Each slave is connected to the internal bus through a *bus adapter*.

Page 39

# 7.1 General digital interface description

In general there are two common digital protocols selectable, the serial interfaces I<sup>2</sup>C and SPI. By default, SPI is used in the standard 4-wire configuration. The SPI interface may be configured by SW to operate in 3-wire interface mode, instead of standard 4-wire mode.

The two serial interfaces are mapped onto the same pads. An external pin is needed to switch between the interfaces. When this protocol select pin (PS) is connected to VSS, SPI is selected as the current interface; when the select pin is connected to  $V_{DDIO}$ ,  $I^2C$  is used as the interface. When select pin is left floating, one of the dedicated modes is selected.

The BMA220 doesn't provide a functional analog output of the three axes since there is just CAP0 available in the package.

Table 19: Interface pin name

| PIN Name    | PIN description                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------|

| CSB         | SPI serial enable bar                                                                                          |

| SCK/SCL     | SPI serial clock (SCK)<br>I <sup>2</sup> C serial clock (SCL)                                                  |

| SDI/SDO/SDA | SPI serial data input (SDI) SPI serial data output in 3-wire SPI mode (SDO) I <sup>2</sup> C serial data (SDA) |

| SDO         | SPI serial data output                                                                                         |

#### 7.2 SPI interface

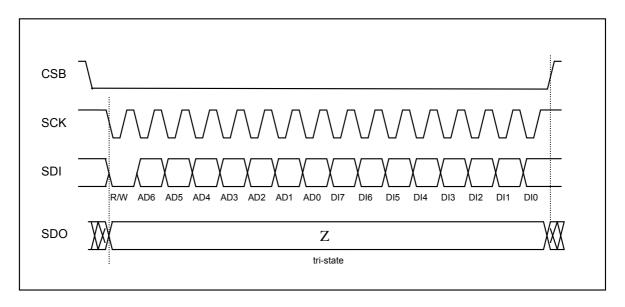

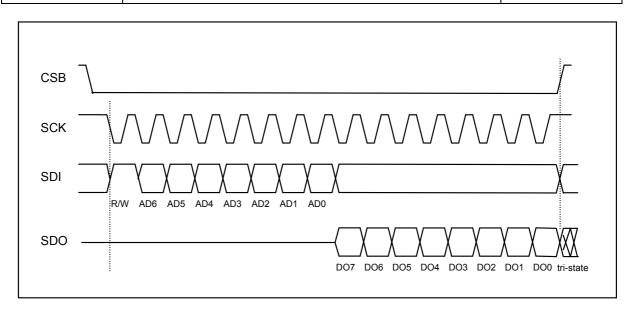

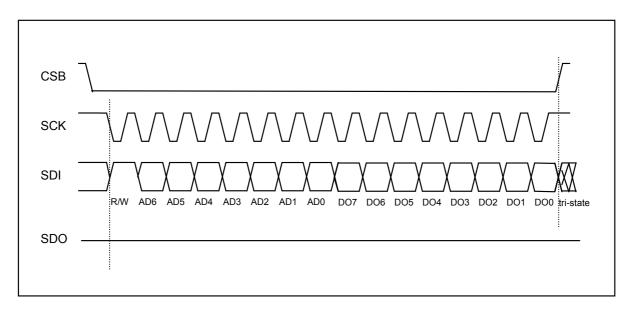

The SPI interface integrated in BMA220 is a slave SPI. 16-bit protocols are used for single byte reading and writing. Multiple bytes read-out is also possible. However, multiple bytes write is not supported. The BMA220 supports SPI only in SPI mode 3 (CPOL = 1, CPHA = 1).

4-wire SPI and 3-wire SPI are using same protocols. The communication starts with a read/write control bit followed by 7 bits address and at least 8 bits data. In case of reading out of acceleration data from all axes the chip provides the option to use an automatic incremented read command to read more than one byte (multiple read). This is activated when the SPI serial enable pin CSB is held low during the data readout. Thus data from next address will be automatically read out if the CSB are kept low for another 8 SPI clock cycles.

# 4-wire SPI protocol and timing

4-wire SPI is the default serial interface. It interacts with the outside world using CSB (chip select low active), SCK (serial clock), SDI (serial data input) and SDO (serial data output).

The communication starts when the CSB is pulled low by the SPI master and stops when CSB is pulled high. SCK is also controlled by SPI master. During the transitions on CSB, SCK must be high. SDI and SDO are driven at the falling edge of SCK and should be captured at the rising edge of SCK.

Single byte write/read commands use 16-bits protocol.

Bit0: Read/Write bit. When 0, the data SDI is written into the chip. When 1, the data SDO from the chip is read.

Bit1-7: Address AD(6:0).

Bit8-15: when in write mode, these are data SDI, which will be written into the address. When in read mode, these are the data SDO, which are read from the address.

Figure 15: 4-wire SPI write command

Write command is completed in 16 clock cycles. During the entire write cycle SDO remains in high-impedance state.

Figure 16: 4-wire SPI read command

Read command is completed in 16 clock cycles or in multiple of 8 in case of multiple byte read. In multiple-read cycle further blocks of 8 clock periods will be extended for each acknowledged data.

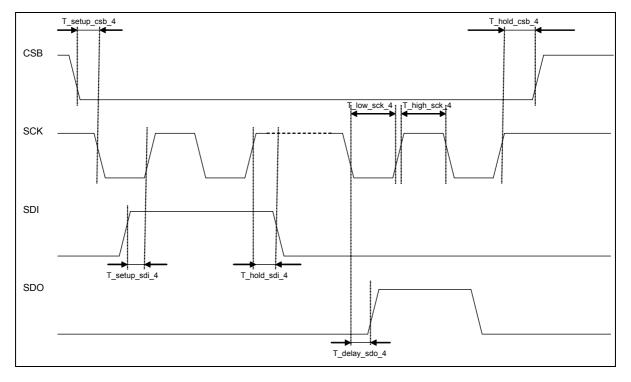

Figure 17: Timing diagram of 4-wire SPI cycle

Table 20: SPI Timing

| Parameter      | Symbol      | Condition                | Min      | Units |

|----------------|-------------|--------------------------|----------|-------|

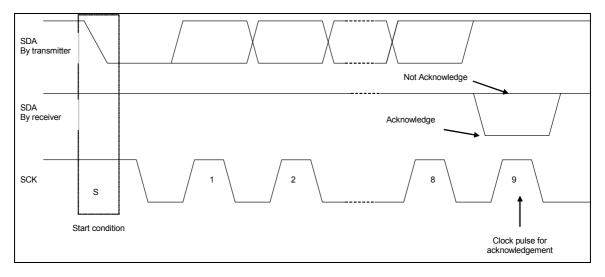

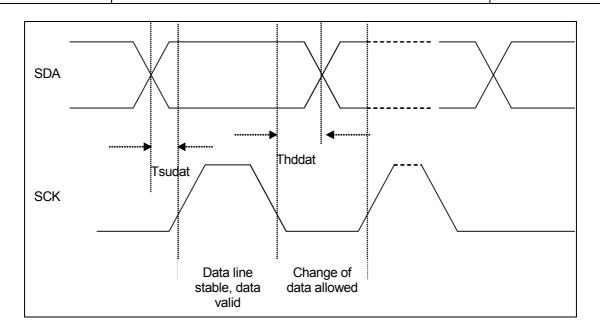

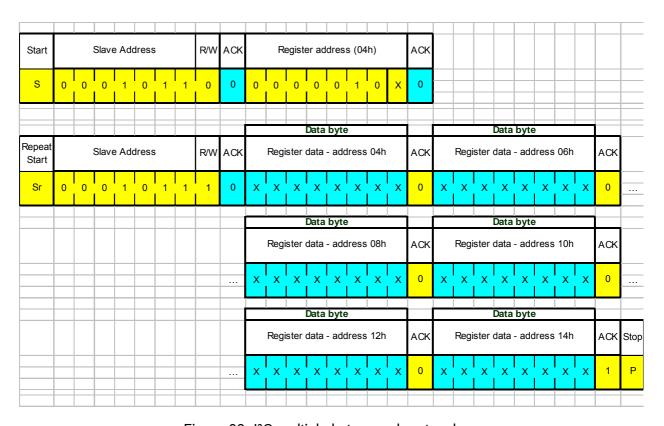

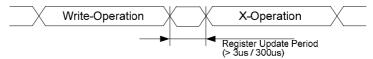

| CSB lead time  | T_setup_csb |                          | 10       |       |