# Low-Power Quad-Channel Microphone ADC with TDM Output

## **Analog Input and ADC Features**

- 91-dB dynamic range (A-weighted) @ 0-dB gain

- -84-dB THD+N @ 0-dB gain

- Four fully differential inputs: Four analog mic/line inputs

- Four analog programmable gain amplifiers

- -6 to +12 dB, in 0.5-dB steps

- +10 or +20 dB boost for mic input

- Four mic bias generators

- MUTE pin for quick mic mute and programmable quick power down

### **Digital Processing Features**

- Volume control, mute, programmable high-pass filter, noise gate

- Two digital mic (DMIC) interfaces

## **Digital Output Features**

- Two DMIC SCLK generators

- Four-channel I2S output or TDM output. Four CS53L30s can be used to output 16 channels of 24-bit 16-kHz sample rate data on a single TDM line.

## **System Features**

- Native (no PLL required) support for 6-/12-MHz, 6.144-/ 12.288-MHz, 5.6448-/11.2896-MHz, or 19.2-MHz master clock rates and 8- to 48-kHz audio sample rates

- Master or Slave Mode. Clock dividers can be used to generate common audio clocks from single-master clock input.

- Low power consumption

- Less than 4.5-mW stereo (16 kHz) analog mic record

- Less than 2.5-mW mono (8 kHz) analog mic record

- Selectable mic bias and digital interface logic voltages

- High-speed (400-kHz) I<sup>2</sup>C control port

- Available in 30-ball WLCSP and 32-pin QFN

## **Applications**

- Voice-recognition systems

- Advanced headsets and telephony systems

- Voice recorders

- Digital cameras and video cameras

### **General Description**

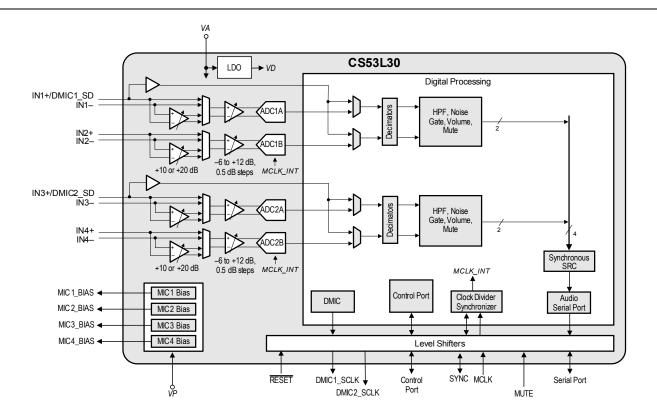

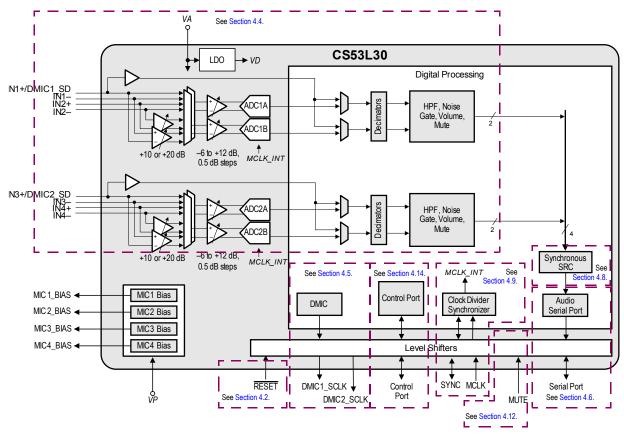

The CS53L30 is a high-performance, low-power, quad-channel ADC. It is designed for use in multiple-mic applications while consuming minimal board space and power.

The flexible ADC inputs can accommodate four channels of analog mic or line-input data in differential, pseudodifferential, or single-ended mode, or four channels of digital mic data. The analog input path includes a +10- to +20-dB boost and a -6- to +12-dB PGA. Digital mic data bypasses the analog gain circuits and is fed directly to the decimators.

Four mic bias generators are integrated into the device. The device also includes two digital mic serial clock outputs.

The CS53L30 includes several digital signal processing features such as high-pass filters, noise gate, and volume control.

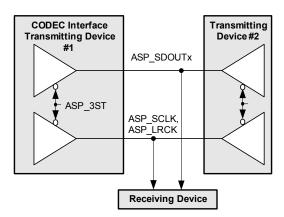

The device can output its four channels of audio data over two I<sup>2</sup>S ports or a single TDM port. Additionally, up to four CS53L30s can be used to output up to 16 channels of data over a single TDM line. This is done by setting the appropriate frame slots for each device, and each device then alternates between outputting data and setting the output pin to high impedance.

The CS53L30 can operate as a serial port clock master or slave. In Master Mode, clock dividers are used to generate the internal master clock and audio clocks from either the 6-/12-MHz, 6.144-/12.288-MHz, 5.6448-/11.2896-MHz, or 19.2-MHz master clock.

The device is powered from VA, a 1.8-V nominal supply and VP, a typical battery supply. An internal LDO on the VA supply powers the device's digital core. The VP supply powers the mic bias generators and the AFE.

The CS53L30 is controlled by an  $I^2C$  control port. A reset pin is also included. The device is available in a 30-ball 0.4-mm pitch WLCSP package and 32-pin 5 x 5-mm QFN package.

## **Table of Contents**

| 1 Pin Descriptions                                                  | 7 Register Descriptions                     | . 47 |

|---------------------------------------------------------------------|---------------------------------------------|------|

| 1.1 WLCSP                                                           | 7.1 Device ID A and B                       | . 47 |

| 1.2 QFN                                                             | 7.2 Device ID C and D                       |      |

| 1.3 Pin Descriptions                                                | 7.3 Device ID E                             |      |

| 2 Typical Connection Diagram7                                       | 7.4 Revision ID                             |      |

| 3 Characteristics and Specifications9                               |                                             |      |

| Table 3-1. Recommended Operating Conditions                         | 7.6 MCLK Control                            | . 48 |

| Table 3-2. Absolute Maximum Ratings                                 | 7.7 Internal Sample Rate Control            | . 48 |

| Table 3-3. Combined ADC On-Chip Analog, Digital Filter, SRC, and    | 7.8 Mic Bias Control                        | . 49 |

| DMIC Characteristics                                                | 7.9 ASP Configuration Control               | . 49 |

| Table 3-4. ADC High-Pass Filter (HPF) Characteristics 9             | 7.10 ASP Control 1                          | . 49 |

| Table 3-5. Analog-Input-to-Serial-Port Characteristics              | 7.11 ASP TDM TX Control 1–4                 |      |

| Table 3-6. MIC BĬAS Characteristics11                               | 7.12 ASP TDM TX Enable 1–6                  |      |

| Table 3-7. Power-Supply Rejection Ratio (PSRR) Characteristics 11   | 7.13 ASP Control 2                          | . 50 |

| Table 3-8. Power Consumption                                        | 7.14 Soft Ramp Control                      | . 50 |

| Table 3-9. Switching Specifications—Digital Mic Interface 14        | 7.15 LRCK Control 1                         |      |

| Table 3-10. Specifications—I <sup>2</sup> S                         | 7.16 LRCK Control 2                         | . 51 |

| Table 3-11. Switching Specifications—Time-Division Multiplexed      | 7.17 MUTE Pin Control 1                     |      |

| (TDM) Mode                                                          | 7.18 MUTE Pin Control 2                     |      |

| Table 3-12. Switching Specifications—I <sup>2</sup> C Control Port  | 7.19 Input Bias Control 1                   | . 52 |

| Table 3-13. Digital Interface Specifications and Characteristics 17 | 7.20 Input Bias Control 2                   | . 52 |

| Table 3-14. Thermal Overload Detection Characteristics              | 7.21 DMIC1 Stereo Control                   |      |

| 4 Functional Description18                                          | 7.22 DMIC2 Stereo Control                   | . 52 |

| 4.1 Overview                                                        | 7.23 ADC1/DMIC1 Control 1                   |      |

| 4.2 Resets                                                          | 7.24 ADC1/DMIC1 Control 2                   |      |

| 4.3 Interrupts                                                      | 7.25 ADC1 Control 3                         | . 53 |

| 4.4 Capture-Path Inputs                                             | 7.26 ADC1 Noise Gate Control                |      |

| 4.5 Digital Microphone (DMIC) Interface                             | 7.27 ADC1A/1B AFE Control                   |      |

| 4.6 Serial Ports                                                    | 7.28 ADC1A/1B Digital Volume                |      |

| 4.7 TDM Mode                                                        | 7.29 ADC2/DMIC2 Control 1                   | . 55 |

| 4.8 Synchronous Sample-Rate Converter (SRC)                         | 7.30 ADC2/DMIC2 Control 2                   |      |

| 4.9 Multichip Synchronization Protocol                              | 7.31 ADC2 Control 3                         | . 55 |

| 4.10 Input Path Source Selection and Powering                       | 7.32 ADC2 Noise Gate Control                |      |

| 4.11 Thermal Overload Notification                                  | 7.33 ADC2A/2B AFE Control                   |      |

| 4.12 MUTE Pin                                                       | 7.34 ADC2A/2B Digital Volume                | . 56 |

| 4.13 Power-Up and Power-Down Control                                | 7.35 Device Interrupt Mask                  | . 57 |

| 4.14 I <sup>2</sup> C Control Port                                  | 7.36 Device Interrupt Status                | . 5/ |

| 4.15 QFN Thermal Pad                                                | 8 Parameter Definitions                     | . 58 |

| 5 Systems Applications                                              |                                             |      |

| 5.1 Octal Microphone Array to the Audio Serial Port                 | 9.1 Digital Filter Response                 | . 58 |

| 5.2 Power-Up Sequence                                               | 9.2 PĞA Gain Linearity                      | . 62 |

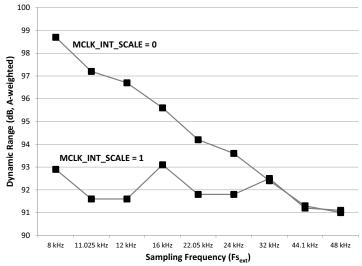

| 5.3 Power-Down Sequence                                             | 9.3 Dynamic Range Versus Sampling Frequency |      |

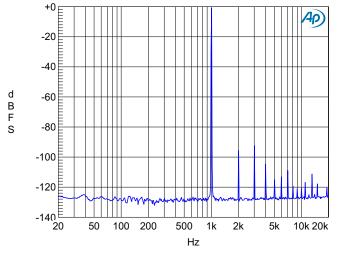

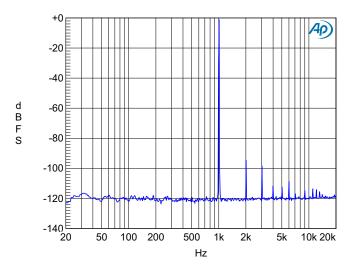

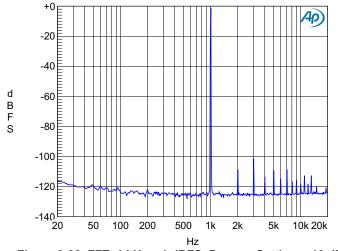

| 5.4 Capture-Path Inputs                                             | 9.4 FFTs                                    |      |

| 5.5 MCLK Jitter                                                     | 10 Package Dimensions                       |      |

| 5.6 Frequency Response Considerations                               | 10.1 WLCSP Package                          |      |

| 5.7 Connecting Unused Pins                                          | 10.2 QFN Package                            |      |

| 6 Register Quick Reference45                                        | 11 Thermal Characteristics                  |      |

|                                                                     | 12 Ordering Information                     |      |

|                                                                     | 13 Revision History                         | . 67 |

## 1 Pin Descriptions

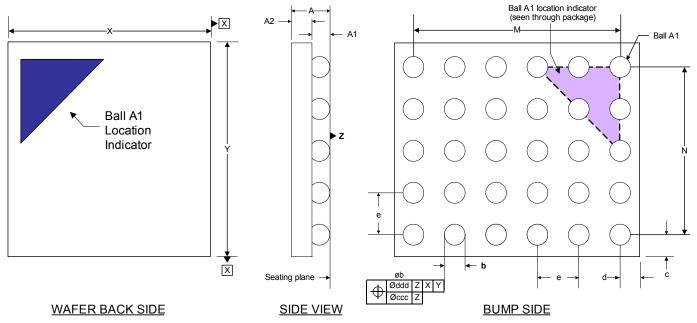

## 1.1 WLCSP

Figure 1-1. Top-Down (Through-Package) View—30-Ball WLCSP Package

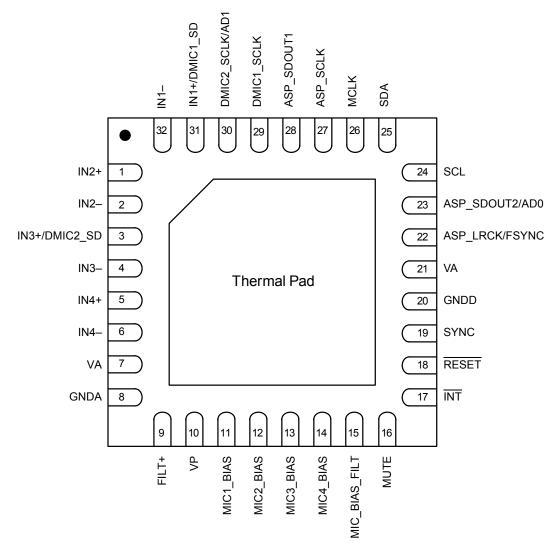

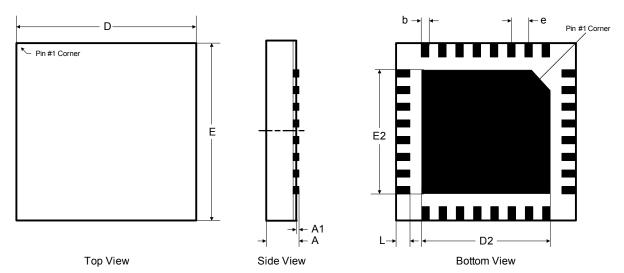

## 1.2 QFN

Figure 1-2. Top-Down (Through-Package) View—32-Pin QFN Package

# 1.3 Pin Descriptions

Table 1-1. Pin Descriptions

| Name                                           | Ball<br>#            | Pin<br>#          | Power<br>Supply | I/O | Description                                                                                                                             | Internal<br>Connection | Driver | Receiver                       | State at<br>Reset |

|------------------------------------------------|----------------------|-------------------|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------|--------------------------------|-------------------|

|                                                |                      |                   |                 |     | Capture-Path Pins 🦲                                                                                                                     |                        |        |                                |                   |

| IN1+/DMIC1_SD<br>IN2+<br>IN3+/DMIC2_SD<br>IN4+ | A1<br>A2<br>A3<br>A4 | 31<br>1<br>3<br>5 | VA              | I   | Noninverting Inputs/DMIC Inputs. Positive analog inputs for the stereo ADCs when CH_TYPE = 0 (default) or DMIC inputs when CH_TYPE = 1. | Programmable           | _      | Hysteresis<br>on CMOS<br>input | _                 |

| IN1-<br>IN2-<br>IN3-<br>IN4-                   | B1<br>B2<br>B3<br>B4 | 32<br>2<br>4<br>6 | VA              | I   | Inverting Inputs. Negative analog inputs for the stereo ADCs when CH_TYPE = 0 (default) or unused when CH_TYPE = 1.                     |                        | _      | Hysteresis<br>on CMOS<br>input | _                 |

| Table 1-1. | Pin | Descriptions | (Cont.) |

|------------|-----|--------------|---------|

|------------|-----|--------------|---------|

| Name                                             | Ball<br>#            | Pin<br>#             | Power<br>Supply | I/O | Description                                                                                                                                                                                                                                               | Internal<br>Connection | Driver                         | Receiver                       | State at<br>Reset |

|--------------------------------------------------|----------------------|----------------------|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|--------------------------------|-------------------|

|                                                  |                      |                      |                 |     | Filter pins                                                                                                                                                                                                                                               |                        |                                |                                |                   |

| MIC_BIAS_FILT                                    | D6                   | 15                   | VP              | I   | Microphone Bias Voltage Filter. Filter connection for the internal quiescent voltage used for the MICx_BIAS outputs.                                                                                                                                      | _                      | _                              | _                              | _                 |

| FILT+                                            | A6                   | 9                    | VA              | 0   | Positive Reference Filter. Positive reference voltage filter for internal sampling circuits.                                                                                                                                                              | _                      | _                              | _                              | _                 |

|                                                  |                      |                      |                 |     | Analog Outputs 🎢                                                                                                                                                                                                                                          |                        |                                |                                |                   |

| MIC1_BIAS<br>MIC2_BIAS<br>MIC3_BIAS<br>MIC4_BIAS | C4<br>C5<br>C6<br>D5 | 11<br>12<br>13<br>14 | VP              | 0   | <b>Microphone Bias Voltage.</b> Low-noise bias supply for an external mic.                                                                                                                                                                                | _                      | _                              | _                              | Hi-Z              |

|                                                  |                      |                      |                 |     | Digital I/O                                                                                                                                                                                                                                               |                        |                                |                                |                   |

| INT                                              | _                    | 17                   | VA              | 0   | Interrupt. Outgoing interrupt signal generated upon registering an error (fault).                                                                                                                                                                         | _                      | CMOS<br>open-drain<br>output   | _                              | Hi-Z              |

| RESET                                            | E5                   | 18                   | VA              | I   | <b>Reset.</b> The device enters a low power mode when this pin is driven low.                                                                                                                                                                             | _                      | _                              | Hysteresis<br>on CMOS<br>input | _                 |

| SYNC                                             | D4                   | 19                   | VA              | I/O | Multidevice Synchronization Signal. Synchronization output when SYNC_EN is set, otherwise it is a synchronization input. Defaults to input.                                                                                                               | Weak<br>pulldown       | CMOS<br>output                 | Hysteresis<br>on CMOS<br>input | Hi-Z              |

| SCL                                              | D3                   | 24                   | VA              | I   | <b>Serial Control Port Clock.</b> Serial clock for the I <sup>2</sup> C port.                                                                                                                                                                             | _                      | _                              | Hysteresis<br>on CMOS<br>input | _                 |

| SDA                                              | E2                   | 25                   | VA              | I/O | <b>Serial Control Data.</b> Bidirectional data pin for the I <sup>2</sup> C port.                                                                                                                                                                         | _                      | CMOS<br>open-drain<br>output   | Hysteresis<br>on CMOS<br>input | _                 |

| MCLK                                             | E1                   | 26                   | VA              | I   | Master Clock. Clock source for device's core.                                                                                                                                                                                                             | Weak<br>pulldown       | _                              | Hysteresis<br>on CMOS<br>input | _                 |

| ASP_SCLK                                         | D2                   | 27                   | VA              | I/O | Audio Serial Clock. Audio bit clock. Input in Slave Mode, output in Master Mode.                                                                                                                                                                          | Weak<br>pulldown       | CMOS<br>output                 | Hysteresis<br>on CMOS<br>input | Hi-Z              |

| ASP_LRCK/<br>FSYNC                               | C3                   | 22                   | VA              | I/O | Audio Left/Right Clock/Frame SYNC. Identifies the start of each serialized PCM data word and indicates the active channel on each serial PCM audio data line. Input in Slave Mode, output in Master Mode.                                                 | Weak<br>pulldown       | CMOS<br>output                 | Hysteresis<br>on CMOS<br>input | Hi-Z              |

| ASP_SDOUT1                                       | D1                   | 28                   | VA              | 0   | Audio Data Output. Output for the two's complement serial PCM data. Channels 1 and 2 are output in I <sup>2</sup> S Mode, while all four channels of data are output on this single pin in TDM Mode.                                                      | Weak<br>pulldown       | Tristateable<br>CMOS<br>output | _                              | Hi-Z              |

| ASP_SDOUT2/<br>AD0                               | E3                   | 23                   | VA              | I/O | Audio Data Output/Address Select. Output for the two's-complement serial PCM data. Channels 3 and 4 are output in I <sup>2</sup> S Mode. Along with DMIC2_SCLK/AD1, immediately sets the I <sup>2</sup> C address when RESET is deasserted. Default is 0. | Weak<br>pulldown       | Tristateable<br>CMOS<br>output | _                              | Hi-Z              |

| DMIC1_SCLK                                       | C2                   | 29                   | VA              | 0   | Digital MIC Interface 1 Serial Clock. High speed clock output to the digital mics.                                                                                                                                                                        | Weak<br>pulldown       | CMOS<br>output                 | _                              | Hi-Z              |

| Name               | Ball<br># | Pin<br># | Power Supply | I/O | Description                                                                                                                                                                                                          | Internal<br>Connection | Driver         | Receiver                       | State at<br>Reset |

|--------------------|-----------|----------|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|--------------------------------|-------------------|

| DMIC2_SCLK/<br>AD1 | C1        | 30       | VA           | I/O | Digital MIC Interface 2 Serial Clock/ Address Select. High speed clock output to the digital mics. Along with ASP_ SDOUT2/AD0, immediately sets the I <sup>2</sup> C address when RESET is deasserted. Default is 0. | Weak<br>pulldown       | CMOS<br>output | _                              | Hi-Z              |

| MUTE               | E6        | 16       | VA           | I   | <b>Mute.</b> Asserting this pin mutes all four channels. Also can be programmed to power down modules as configured in the MUTE pin control registers.                                                               | Weak<br>pulldown       | _              | Hysteresis<br>on CMOS<br>input | _                 |

|                    |           |          |              |     | Power 💮                                                                                                                                                                                                              |                        |                |                                |                   |

| VA                 | A5        | 7<br>21  | N/A          | I   | Analog/Digital Power. Power supply for analog circuitry and digital circuitry via internal LDO.                                                                                                                      | _                      | _              | _                              | _                 |

| VP                 | В6        | 10       | N/A          | I   | <b>Analog Power.</b> Power supply for mic bias.                                                                                                                                                                      | _                      | _              | _                              | _                 |

| GNDA               | B5        | 8        | N/A          | I   | Analog Ground. Ground reference.                                                                                                                                                                                     | _                      | _              | _                              | _                 |

| GNDD               | E4        | 20       | N/A          | I   | Digital Ground. Ground reference.                                                                                                                                                                                    | _                      | _              | _                              | _                 |

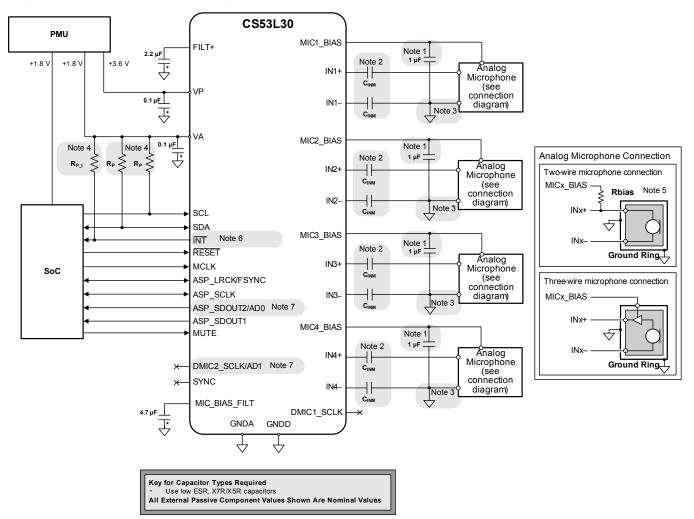

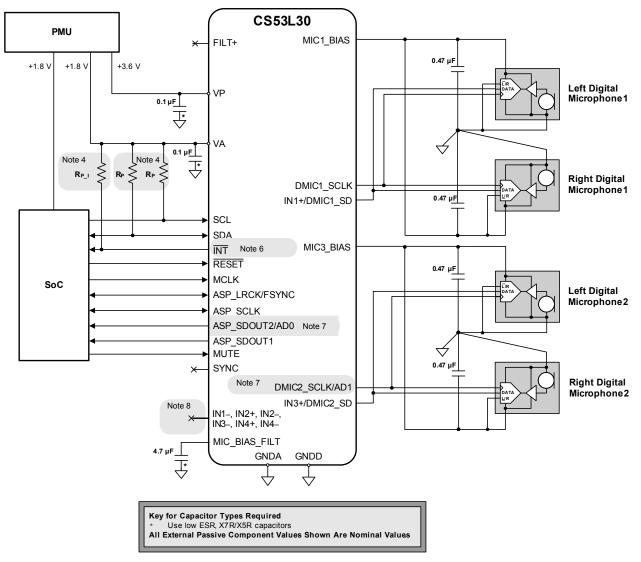

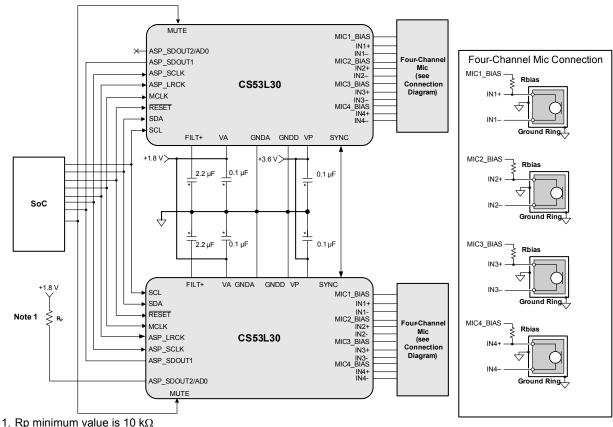

# 2 Typical Connection Diagram

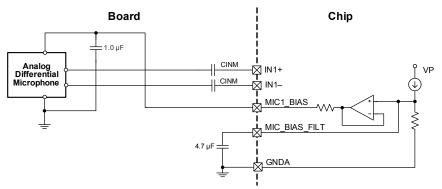

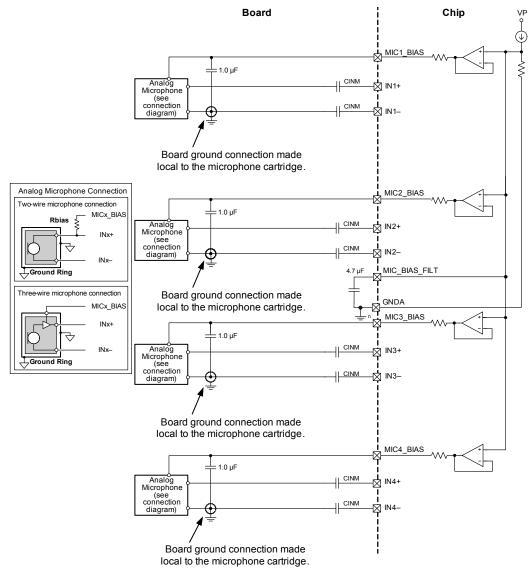

Figure 2-1. Typical Connection Diagram—Analog Microphone Connections

Figure 2-2. Typical Connection Diagram—Digital Microphone Connections

- 1. The MICx\_BIAS compensation capacitor must be 1 µF (nominal values indicated, can vary from the nominal by ±20%). This value is bounded by the stability of the amplifier and the maximum rise-time specification of the output.

- The DC-blocking capacitor, C<sub>INM</sub>, forms a high-pass filter whose corner frequency is determined by the capacitor value and the input impedance. See Table 3-5 and Section 4.4.2.

- 3. The reference terminal of the INx inputs connects to the ground pin of the mic cartridge in the pseudodifferential case. In a fully differential configuration, the reference terminal of the INx inputs connects to the inverting output terminal of differential mic.

- 4. R<sub>P I</sub> and R<sub>P</sub> can be calculated by using the values in Table 3-14.

- 5. The value of  $R_{BIAS}$ , the bias resistor for electret condenser mics, is dictated by the mic cartridge.

- 6. The INT pin is provided only on the QFN package.

- 7. ASP\_SDOUT2/AD0 and DMIC2\_SCLK/AD1 have internal pull-downs that allow for the default I²C address with no external components. See Table 3-14 for typical and maximum pull-down values. If an I²C physical address other than the default is desired, then external resistor termination to VA is required. The minimum value resistor allowed on these I/O pins is 10 kΩ. The time constant resulting from the pull-up/pull-down resistor and the total net capacitance should be considered when determining the time required for the pin voltage to settle before RESET is deasserted.

- 8. Unconnected INx pins can be terminated with an internal weak\_vcm or weak pull-down by setting the termination in the INxy\_BIAS bits. See Section 5.7, Section 7.19, and Section 7.20.

## 3 Characteristics and Specifications

Section 8 provides additional details about parameter definitions.

#### **Table 3-1. Recommended Operating Conditions**

Test conditions: GNDA = GNDD = 0 V; all voltages are with respect to ground.

| Parameters <sup>1</sup>           |                | Symbol             | Min  | Max      | Unit |

|-----------------------------------|----------------|--------------------|------|----------|------|

| DC power supply                   | Analog/Digital | VA                 | 1.71 | 1.89     | V    |

|                                   | VP_MIN = 1     | VP                 | 3.2  | 5.25     | V    |

|                                   | VP_MIN = 0     |                    | 3.0  | 5.25     | V    |

| External voltage applied to pin 2 | VA domain pins | V <sub>IN-AI</sub> | -0.3 | VA + 0.3 | V    |

|                                   | VP domain pins | $V_{IN-PI}$        | -0.3 | VP + 0.3 | V    |

| Ambient temperature               | Commercial     | T <sub>A</sub>     | -10  | +70      | °C   |

<sup>1.</sup> Device functional operation is guaranteed within these limits; operation outside them is not guaranteed or implied and may reduce device reliability.

#### Table 3-2. Absolute Maximum Ratings

Test conditions: GNDA = GNDD = 0 V; all voltages are with respect to ground.

| Parameters                                    |              | Symbol           | Min  | Max  | Units |

|-----------------------------------------------|--------------|------------------|------|------|-------|

| DC power supply Ar                            | alog/digital | VA               | -0.3 | 2.22 | V     |

|                                               | Mic bias     | VP               | -0.3 | 5.6  | V     |

| Input current <sup>1</sup>                    |              | I <sub>in</sub>  | _    | ±10  | mA    |

| Ambient operating temperature (power applied) |              | T <sub>A</sub>   | -50  | +115 | °C    |

| Storage temperature (no power applied)        |              | T <sub>stg</sub> | -65  | +150 | °C    |

**CAUTION:** Operation at or beyond these limits may permanently damage the device.

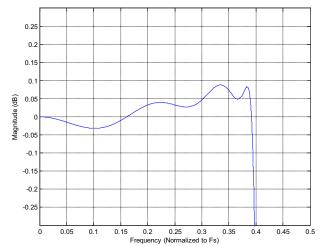

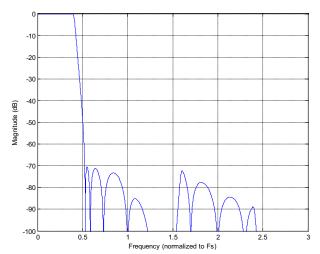

#### Table 3-3. Combined ADC On-Chip Analog, Digital Filter, SRC, and DMIC Characteristics

Test conditions (unless otherwise specified): T<sub>A</sub> = +25°C; MCLK = 12.288 MHz; characteristics do not include the effects of external AC-coupling capacitors. Path is INx to SDOUT. Analog and digital gains are all set to 0 dB; HPF disabled.

|                                         |                      | Parameters <sup>1</sup>                  |                | Min   | Тур                                            | Max  | Units |

|-----------------------------------------|----------------------|------------------------------------------|----------------|-------|------------------------------------------------|------|-------|

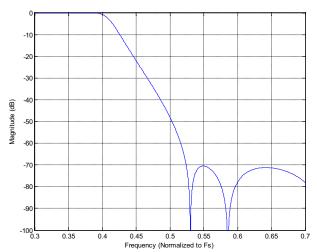

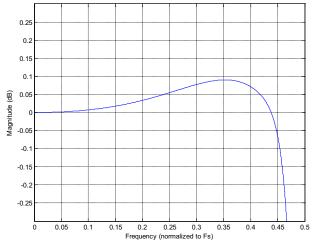

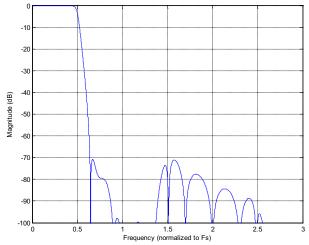

| Fs <sub>int</sub> = Fs <sub>ext</sub> = | ADC notch filter on  | Passband –(                              | 0.05-dB corner | _     | 0.391                                          | _    | Fs    |

| Fs = 48 kHz [2]                         | (ADCx_NOTCH_         | -                                        | -3.0-dB corner | _     | 0.410                                          | _    | Fs    |

|                                         | DIS = 0)             | Passband ripple (0 Hz to 0.394 Fs; norma | lized to 0 Hz) | -0.13 | _                                              | 0.14 | dB    |

|                                         |                      | Stopband @ -70 dB                        |                | _     | 0.492                                          | _    | Fs    |

|                                         |                      | Total group delay                        |                | _     | 15.3/Fs <sub>int</sub> + 6.5/Fs <sub>ext</sub> | _    | S     |

|                                         | ADC notch filter off | Passband –(                              | 0.05-dB corner | -     | 0.445                                          |      | Fs    |

|                                         | (ADCx_NOTCH_         | -                                        | -3.0-dB corner | _     | 0.470                                          | _    | Fs    |

|                                         | DIS = 1)             | Passband ripple (0 Hz to 0.447 Fs; norma | lized to 0 Hz) | -0.09 | _                                              | 0.14 | dB    |

|                                         |                      | Stopband @ -70 dB                        |                | _     | 0.639                                          | _    | Fs    |

|                                         |                      | Total group delay                        |                | _     | 15.5/Fs <sub>int</sub> + 6.6/Fs <sub>ext</sub> | _    | S     |

<sup>1.</sup> Specifications are normalized to Fs and can be denormalized by multiplying by Fs.

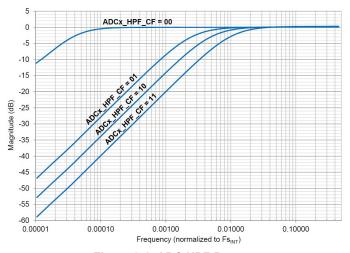

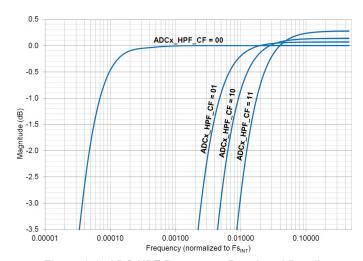

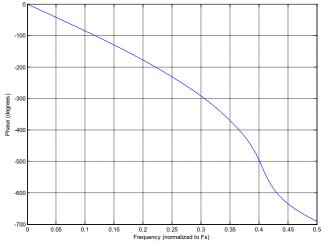

### Table 3-4. ADC High-Pass Filter (HPF) Characteristics

Test conditions (unless specified otherwise): Analog and digital gains are all set to 0 dB; ADCx\_HPF\_CF = 00.

|                               | Parameters <sup>1</sup>                                      | Min | Тур                     | Max  | Units             |

|-------------------------------|--------------------------------------------------------------|-----|-------------------------|------|-------------------|

| Passband <sup>2</sup>         | -0.05-dB corner                                              | _   | 3.57x10 <del>-4</del>   | _    | Fs <sub>int</sub> |

|                               | -3.0-dB corner                                               | _   | 3.88x10 <sup>-5</sup>   | _    | Fs <sub>int</sub> |

| Passband ripple (0.417x10-3 F | s to 0.417 Fs; normalized to 0.417 Fs)                       | _   | _                       | 0.01 | dB                |

| Phase deviation @ 0.453 x 10  | <sup>-3</sup> Fs                                             | _   | 4.896                   | _    | 0                 |

| Filter settling time 3        | ADCx_HPF_CF = 00 (3.88 x $10^{-5}$ x Fs <sub>int</sub> mode) | _   | 12260/Fs <sub>int</sub> | _    | S                 |

|                               | ADCx_HPF_CF = 01 (2.5 x $10^{-3}$ x Fs <sub>int</sub> mode)  | _   | 200/Fs <sub>int</sub>   | _    | S                 |

|                               | ADCx_HPF_CF = 10 (4.9 x $10^{-3}$ x Fs <sub>int</sub> mode)  |     | 100/Fs <sub>int</sub>   | _    | S                 |

|                               | ADCx_HPF_CF = 11 (9.7 x $10^{-3}$ x Fs <sub>int</sub> mode)  | _   | 50/Fs <sub>int</sub>    | _    | s                 |

<sup>1.</sup> Response scales with Fsint. Specifications are normalized to Fsint and are denormalized by multiplying by Fsint.

<sup>2.</sup> The maximum over/under voltage is limited by the input current.

<sup>1.</sup>Any pin except supplies. Transient currents of up to ±100 mA on the capture-path pins do not cause SCR latch-up.

<sup>2.</sup> See Section 5.6 for information about combined filter response when Fsint is not equal to Fsext.

<sup>2.</sup> Characteristics do not include effects of the analog HPF filter formed by the external AC-coupling capacitors and the input impedance.

<sup>3.</sup> Required time for the magnitude of the DC component present at the output of the HPF to reach 5% of the applied DC signal.

#### Table 3-5. Analog-Input-to-Serial-Port Characteristics

Test conditions (unless otherwise specified): Fig. 2-1 shows CS53L30 connections; input is a full-scale 1-kHz sine wave; ADCx\_PREAMP = +10 dB; ADCx\_PGA\_VOL = 0 dB; GNDA = GNDD = 0; voltages are with respect to ground; parameters can vary with VA, typical performance data taken with VA = 1.8 V, VP = 3.6 V, min/max performance data taken with VA = 1.8 V, VP = 3.6 V; VA = 1.8 V, VP = 3.6 V; VA = 1.8 V, VP = 3.6 V; measurement bandwidth is 20 Hz-20 kHz; LRCK = Fs = 48 kHz.

|                                        | Paramete                       |                                                                                                                                |                                                                     | Min                         | Тур                                                     | Max                         | Units                           |

|----------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|---------------------------------------------------------|-----------------------------|---------------------------------|

| Dynamic range <sup>2</sup>             | Preamp setting: Bypass, PGA    | setting: 0 dB                                                                                                                  | A-weighted<br>unweighted                                            | 87<br>85                    | 93<br>91                                                | _                           | dB<br>dB                        |

|                                        | Preamp setting: Bypass, PGA    | setting: +12 dB                                                                                                                | A-weighted unweighted                                               | 80<br>78                    | 86<br>84                                                | _                           | dB<br>dB                        |

|                                        | Preamp setting: +10 dB, PGA    | G                                                                                                                              | A-weighted unweighted                                               | 84<br>82                    | 90<br>88                                                | _                           | dB<br>dB                        |

|                                        | Preamp setting: +10 dB, PGA    |                                                                                                                                | A-weighted unweighted                                               | 74<br>72                    | 80<br>78                                                | _                           | dB<br>dB                        |

|                                        | Preamp setting: +20 dB, PGA    | · ·                                                                                                                            | A-weighted unweighted                                               | 78<br>76                    | 84<br>82                                                |                             | dB<br>dB                        |

|                                        | Preamp setting: +20 dB, PGA    |                                                                                                                                | A-weighted unweighted                                               | 66<br>64                    | 72<br>70                                                | _                           | B<br>B<br>B                     |

| Total harmonic                         | Preamp setting: Bypass, PGA    |                                                                                                                                | –1 dB                                                               | _                           | -84                                                     | <b>–</b> 78                 | dB                              |

| distortion + noise 3                   | Preamp setting: Bypass, PGA    |                                                                                                                                | –1 dB                                                               | _                           | -80                                                     | -74                         | dB                              |

|                                        | Preamp setting: +10 dB, PGA    | setting: 0 dB                                                                                                                  | –1 dB                                                               | _                           | -76                                                     | <del>-</del> 70             | dB                              |

|                                        | Preamp setting: +10 dB, PGA    | setting: +12 dB                                                                                                                | –1 dB                                                               | _                           | -63                                                     | <b>–</b> 57                 | dB                              |

|                                        | Preamp setting: +20 dB, PGA    | setting: 0 dB                                                                                                                  | –1 dB                                                               | _                           | -70                                                     | -64                         | dB                              |

|                                        | Preamp setting: +20 dB, PGA    | setting: +12 dB                                                                                                                | –1 dB                                                               | _                           | -62                                                     | -56                         | dB                              |

| Common-mode reje                       | ction <sup>4</sup>             | -                                                                                                                              |                                                                     | _                           | 70                                                      | _                           | dB                              |

| DC accuracy                            | Interchannel gain mismatch 5   |                                                                                                                                |                                                                     | _                           | ±0.2                                                    | _                           | dB                              |

|                                        | Gain drift 5                   |                                                                                                                                |                                                                     | _                           | ±100                                                    | _                           | ppm/°C                          |

|                                        | PGA A/B gain                   |                                                                                                                                | G <sub>MIN</sub><br>G <sub>MAX</sub><br>ΔG                          | -6.25<br>11.75<br>0.375     | -6<br>12<br>0.5                                         | -5.75<br>12.25<br>0.625     | dB<br>dB<br>dB                  |

|                                        | Preamp A/B gain                |                                                                                                                                | G <sub>MIN</sub><br>G <sub>MAX</sub>                                | 9.5<br>19.9                 | 10<br>20                                                | 10.5<br>20.5                | dB<br>dB                        |

|                                        | Offset error 6                 |                                                                                                                                |                                                                     | _                           | 128                                                     | _                           | LSB                             |

| Phase accuracy                         | Multichip interchannel phase i | mismatch 7                                                                                                                     |                                                                     | _                           | 0.5                                                     | _                           | 0                               |

|                                        | Interchannel phase mismatch    | 8                                                                                                                              |                                                                     | _                           | 0.5                                                     | _                           | 0                               |

| Input                                  | Interchannel isolation 8       |                                                                                                                                | 217 Hz<br>1 kHz<br>20 kHz                                           |                             | 90<br>90<br>80                                          | _                           | dB<br>dB<br>dB                  |

|                                        |                                | Preamp setting: 0 dl<br>Preamp setting: +10 dl<br>Preamp setting: +10 dB,<br>Preamp setting: +20 dl<br>Preamp setting: +20 dB, | B, PGA setting: 0 dB<br>PGA setting: +12 dB<br>B, PGA setting: 0 dB | 0.78•VA<br>—<br>—<br>—<br>— | 0.82•VA<br>0.258•VA<br>0.064•VA<br>0.081•VA<br>0.020•VA | 0.88•VA<br>—<br>—<br>—<br>— | Vpp<br>Vpp<br>Vpp<br>Vpp<br>Vpp |

|                                        | Input impedance 10             |                                                                                                                                | Preamp setting: 0 dB<br>ting: +10 or +20 dB;                        | 45<br>0.9                   | 50<br>1                                                 | _                           | kΩ<br>MΩ                        |

| DC voltage at INx (pin floating) 11,12 | Preamp setting: Bypass         | ·                                                                                                                              | ADCx_PDN = 0<br>ADCx_PDN = 1                                        | _                           | 0.42•VA<br>0.50•VA                                      | _                           | V                               |

|                                        | Preamp setting: +10 dB or +2   | 0 dB                                                                                                                           | ADCx_PDN = 0<br>ADCx_PDN = 1                                        | _                           | 0.39•VA<br>0.50•VA                                      | _                           | V<br>V                          |

- 1. Measures are referred to the applicable typical full-scale voltages. Applies to all THD+N and dynamic range values in the table.

- 2.INx dynamic range test configuration (pseudodifferential) Includes noise from MICx\_BIAS output (2.7-V setting) through a series 2.21-k $\Omega$  resistor connected to INx. Input signal is –60 dB down from the corresponding full-scale signal input voltage.

- 3. Input signal amplitude is relative to typical full-scale signal input voltage.

- 4 INx CMRR test configuration

- 5. Measurements taken at all defined full-scale signal input voltages.

- 6.SDOUT code with ADC\_HPF\_EN = 1, DIG\_BOOSTx = 0. The offset is added at the ADC output; if two ADC sources are mixed, their offsets add.

- 7. Measured between two CS53L30 chips with input pairs IN1 selected and driven from same source with an MCLK of 19.2 MHz, 16-kHz sample rate, and 8-kHz full-scale sine wave with preamp gain of +20 dB and PGA gain of +12 dB.

- 8. Measured between input pairs (IN1 to INx, IN2 to INx, IN3 to INx, IN4 to INx) with +20 dB preamp gain and +12 dB PGA gain.

- 9.ADC full-scale input voltage is measured between INx+ and INx- with the preamp set to bypass and the PGA set to 0-dB gain. Maximum input signal level for INx depends on the preamp and PGA gain settings described in Section 5.4.1. The digital output level corresponding to ADC full-scale input is less than 0 dBFS due to signal attenuation through the SRC; see Table 4-4.

- 10.Measured between INx+ and INx-.

- 11.INx pins are biased as specified when weak VCM is selected in the input bias control registers; see Section 7.19 and Section 7.20.

- 12. Changing gain settings to Bypass Mode may cause audible artifacts due to the difference in DC operating points between modes.

#### Table 3-6. MIC BIAS Characteristics

Test conditions (unless otherwise specified): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0; all voltages are with respect to ground; VA = 1.8 V, VP = 3.6 V, T<sub>A</sub> = +25°C; only one bias output is powered up at a time; MCLK\_INT\_SCALE = 0.

|                                       | Parameters                                                                                                                                          | Min          | Тур             | Max          | Units          |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------------|----------------|

| Output voltage <sup>1</sup>           | MIC_BIAS_CTRL = 01 (1.8-V mode)<br>MIC_BIAS_CTRL = 10 (2.7-V mode)                                                                                  | 1.71<br>2.61 | 1.80<br>2.75    | 1.89<br>2.86 | V              |

| Mic bias startup delay <sup>2</sup>   |                                                                                                                                                     | _            | 10              | _            | ms             |

| Rise time <sup>3</sup>                | I <sub>OUT</sub> = 500 μA, MIC_BIAS_CTRL = 01 (1.8-V mode)<br>I <sub>OUT</sub> = 500 μA, MIC_BIAS_CTRL = 10 (2.7-V mode)<br>I <sub>OUT</sub> = 2 mA | _<br>_<br>_  | 0.2<br>0.5<br>— | _<br>_<br>3  | ms<br>ms<br>ms |

| DC output current (I <sub>OUT</sub> ) | Per output                                                                                                                                          | _            | —               | 2            | mA             |

| Integrated output noise               | f = 100 Hz–20 kHz                                                                                                                                   | _            | 3               | _            | μVrms          |

| Dropout voltage <sup>4</sup>          |                                                                                                                                                     | _            | _               | 340          | mV             |

| PSRR reduction voltage <sup>5</sup>   |                                                                                                                                                     | _            | _               | 500          | mV             |

| Output resistance (R <sub>OUT</sub> ) | I <sub>OUT</sub> = 2-mA                                                                                                                             | _            | 30              | _            | Ω              |

- 1. The output voltage includes attenuation due to the MIC BIAS output resistance (R<sub>OUT</sub>).

- 2. Startup delay times are approximate and vary with MCLK<sub>INT</sub> frequency. If MCLK\_INT\_SCALE = 1, the startup delay time is scaled up by the MCLK<sub>INT</sub> scaling factor. The MCLK<sub>INT</sub> scaling factor is 1, 2, or 4, depending on Fs<sub>EXT</sub>. See Table 4-2.

- 3. From 10% to 90% of typical output voltage. External capacitor on MICx\_BIAS is as shown in Fig. 2-1.

- 4. Dropout voltage indicates the point where an output's voltage starts to vary significantly with reductions to its supply voltage. When the VP supply voltage drops below the programmed MICx\_BIAS output voltage plus the dropout voltage, the MICx\_BIAS output voltage progressively decreases as its supply decreases.

- Dropout voltage is measured by reducing the VP supply until MICx\_BIAS drops 10 mV from its initial voltage with the default typical test condition VP voltage (= 3.6 V, as in test conditions listed above). The difference between the VP supply voltage and the MICx\_BIAS voltage at this point is the dropout voltage. For instance, if the initial MICx\_BIAS output is 2.86 V when VP = 3.6 V and VP = 3.19 V when MICx\_BIAS drops to 2.85 V (-10 mV), the dropout voltage is 340 mV (3.19 V 2.85 V).

- 5.PSRR voltage indicates the point where an output's supply PSRR starts to degrade significantly with supply voltage reductions. When the VP supply voltage drops below the programmed MICx\_BIAS output voltage plus the PSRR reduction voltage, the MICx\_BIAS output's PSRR progressively decreases as its supply decreases.

- PSRR reduction voltage is measured by reducing the VP supply until MICx\_BIAS PSRR @ 217 Hz falls below 100 dB. The difference between the VP supply voltage and the MICx\_BIAS voltage at this point is the PSRR reduction voltage. For instance, if the MICx\_BIAS PSRR falls to 99.9 dB when VP is reduced to 3.25 V and the MICx\_BIAS output voltage is 2.75 V at that point, PSRR reduction voltage is 500 mV (3.25 V 2.75 V).

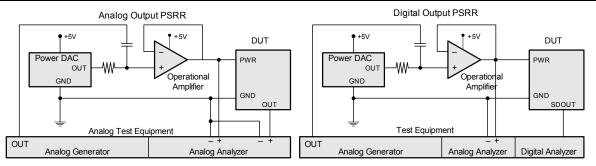

#### Table 3-7. Power-Supply Rejection Ratio (PSRR) Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; input test signal held low (all zero data); GNDA = GNDD = 0; voltages are with respect to ground; VA = 1.8 V, VP = 3.6 V; T<sub>A</sub> = +25°C.

| Parameters 1                                                  |        | Min | Typical | Max | Units |

|---------------------------------------------------------------|--------|-----|---------|-----|-------|

| INx (32-dB analog gain)                                       | 217 Hz | _   | 70      | _   | dB    |

| PSRR with 100-mVpp signal AC coupled to VA supply             | 1 kHz  | _   | 70      |     | dB    |

|                                                               | 20 kHz | _   | 55      | _   | dB    |

| MICx_BIAS (MICx_BIAS = 2.7-V mode, I <sub>OUT</sub> = 500 μA) | 217 Hz | _   | 105     | _   | dB    |

| PSRR with 100 mVpp signal AC coupled to VA supply             | 1 kHz  | _   | 100     |     | dB    |

| $VP_MIN = 0 (3.0 V)$                                          | 20 kHz | _   | 95      | _   | dB    |

| MICx_BIAS (MICx_BIAS = 2.7-V mode, I <sub>OUT</sub> = 500 μA) | 217 Hz | _   | 105     | _   | dB    |

| PSRR with 100 mVpp signal AC coupled to VA supply             | 1 kHz  | _   | 100     | _   | dB    |

| VP_MIN = 1 (3.2 V)                                            | 20 kHz | _   | 95      | _   | dB    |

| MICx_BIAS (MICx_BIAS = 2.7-V mode, I <sub>OUT</sub> = 500 μA) | 217 Hz | _   | 90      | _   | dB    |

| PSRR with 100 mVpp signal AC coupled to VP supply             | 1 kHz  | _   | 90      |     | dB    |

| $VP_MIN = 0 (3.0 V)$                                          | 20 kHz | _   | 70      | _   | dB    |

| MICx_BIAS (MICx_BIAS = 2.7-V mode, I <sub>OUT</sub> = 500 μA) | 217 Hz | _   | 120     | _   | dB    |

| PSRR with 1 Vpp signal AC coupled to VP supply                | 1 kHz  | _   | 115     | _   | dB    |

| VP_MIN = 1 (3.2 V)                                            | 20 kHz | _   | 105     | _   | dB    |

1.PSRR test configuration: Typical PSRR can vary by approximately 6 dB below the indicated values.

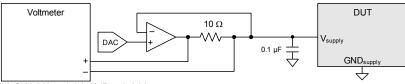

#### **Table 3-8. Power Consumption**

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0 V; voltages are with respect to ground; performance data taken with VA = 1.8 V, VP = 3.6 V; T<sub>A</sub> = +25°C; MCLK = 12.288 MHz; serial port set to Slave Mode; digital volume = 0 dB; no signal on any input; control port inactive; MCLK\_INT\_SCALE = 1.

|   |        | (Soo To                                             | Use Cases <sup>1</sup> ble 3-9 for register field settings.)      | Typical<br>(µ   | Current<br>A)   | Total Power |

|---|--------|-----------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------|-------------|

|   |        | (See Tal                                            | ble 3-9 for register field settings.)                             | i <sub>VA</sub> | i <sub>VP</sub> | (μνν)       |

| 1 |        | Standby <sup>2</sup>                                |                                                                   | 2               | 0               | 4           |

| 2 | Α      | Quiescent 3                                         | MCLK low, MCLK_DIS = x, PDN_ULP = 1, PDN_LP = x                   | 7               | 1               | 17          |

|   | В      |                                                     | MCLK active, MCLK_DIS = 1, PDN_ULP = 1, PDN_LP = x                | 54              | 1               | 101         |

|   | C<br>D |                                                     | MCLK low, MCLK_DIS = x, PDN_ULP = 0, PDN_LP = 1                   | 103             | 19              | 253         |

| 2 |        | Contura analas mis innut                            | MCLK active, MCLK_DIS = 1, PDN_ULP = 0, PDN_LP = 1                | 134             | 19              | 308         |

| 3 | A      | Capture, analog mic input,<br>ADCx PREAMP = +20 dB, | Fs <sub>ext</sub> = 48 kHz, mono input, MICx_BIAS_PDN = 1         | 1998            | 58              | 3805        |

|   | В      | ADCX_PREAMIP = 120 dB,<br>ADCX_PGA_VOL = +12 dB     | Fs <sub>ext</sub> = 48 kHz, mono input, MICx_BIAS_PDN = 0         | 2003            | 147             | 4136        |

|   | С      | / B 6 A _ 1 6 A _ 1 6 A _ 1 6 A _ 1                 | Fs <sub>ext</sub> = 16 kHz, mono input, MICx_BIAS_PDN = 1         | 1423            | 58              | 2770        |

|   | D      |                                                     | Fs <sub>ext</sub> = 16 kHz, mono input, MICx_BIAS_PDN = 0         | 1432            | 147             | 3107        |

|   | Е      |                                                     | Fs <sub>ext</sub> = 8 kHz, mono input, MICx_BIAS_PDN = 1          | 1046            | 58              | 2092        |

|   | F      |                                                     | Fs <sub>ext</sub> = 8 kHz, mono input, MICx_BIAS_PDN = 0          | 1053            | 147             | 2425        |

|   | G      |                                                     | Fs <sub>ext</sub> = 48 kHz, stereo input, MICx_BIAS_PDN = 1       | 2697            | 81              | 5147        |

|   | Н      |                                                     | Fs <sub>ext</sub> = 48 kHz, stereo input, MICx_BIAS_PDN = 0       | 2702            | 243             | 5739        |

|   | I      |                                                     | Fs <sub>ext</sub> = 16 kHz, stereo input, MICx_BIAS_PDN = 1       | 1955            | 81              | 3811        |

|   | J      |                                                     | Fs <sub>ext</sub> = 16 kHz, stereo input, MICx_BIAS_PDN = 0       | 1960            | 243             | 4405        |

|   | K      |                                                     | Fs <sub>ext</sub> = 8 kHz, stereo input, MICx_BIAS_PDN = 1        | 1494            | 81              | 2981        |

|   | L      |                                                     | Fs <sub>ext</sub> = 8 kHz, stereo input, MICx_BIAS_PDN = 0        | 1498            | 243             | 3573        |

|   | M      |                                                     | Fs <sub>ext</sub> = 48 kHz, four-channel input, MICx_BIAS_PDN = 1 | 4138            | 145             | 7969        |

|   | N      |                                                     | Fs <sub>ext</sub> = 48 kHz, four-channel input, MICx_BIAS_PDN = 0 | 4141            | 454             | 9087        |

|   | 0      |                                                     | Fs <sub>ext</sub> = 16 kHz, four-channel input, MICx_BIAS_PDN = 1 | 3033            | 145             | 5981        |

|   | Р      |                                                     | Fs <sub>ext</sub> = 16 kHz, four-channel input, MICx_BIAS_PDN = 0 | 3040            | 454             | 7106        |

|   | Q      |                                                     | Fs <sub>ext</sub> = 8 kHz, four-channel input, MICx_BIAS_PDN = 1  | 2397            | 145             | 4836        |

|   | R      |                                                     | Fs <sub>ext</sub> = 8 kHz, four-channel input, MICx_BIAS_PDN = 0  | 2403            | 454             | 5959        |

| 4 | Α      | Capture, analog line input,                         | Fs <sub>ext</sub> = 48 kHz, four-channel input, MICx_BIAS_PDN = 1 | 3151            | 145             | 6193        |

|   | В      | ADCx_PREAMP = 0 dB,                                 | Fs <sub>ext</sub> = 16 kHz, four-channel input, MICx_BIAS_PDN = 1 | 2059            | 145             | 4227        |

|   | С      | ADCx_PGA_VOL = 0 dB                                 | Fs <sub>ext</sub> = 8 kHz, four-channel input, MICx_BIAS_PDN = 1  | 1429            | 145             | 3092        |

| 5 | Α      | Capture, digital mic input                          | Fs <sub>ext</sub> = 48 kHz, four-channel input, MICx_BIAS_PDN = 0 | 2433            | 352             | 5645        |

|   | В      |                                                     | Fs <sub>ext</sub> = 16 kHz, four-channel input, MICx_BIAS_PDN = 0 | 1366            | 352             | 3725        |

|   | С      |                                                     | Fs <sub>ext</sub> = 8 kHz, four-channel input, MICx_BIAS_PDN = 0  | 881             | 352             | 2852        |

1. Power consumption test configuration. The current draw on the power supply pins is derived from the measured voltage drop across a 10-Ω series resistor between the associated supply source and the voltage supply pin.

2. Standby configuration: Clock/data lines are held low; RESET = LOW; VA = 1.8 V, VP = 3.6 V

3. Quiescent configuration: data lines held low; RESET = HIGH

### Table 3-9. Register Field Settings

| _ |             |         |     |          |               |               |               |               |               |               | <u></u>        |                |    |           | _        |    |           |                   | and Sett           | _                 |                    |                   |                    |                   |                    |           |           |         |

|---|-------------|---------|-----|----------|---------------|---------------|---------------|---------------|---------------|---------------|----------------|----------------|----|-----------|----------|----|-----------|-------------------|--------------------|-------------------|--------------------|-------------------|--------------------|-------------------|--------------------|-----------|-----------|---------|

|   |             |         |     |          | 1             |               |               |               |               |               |                |                | Λŧ | yı        | วเษ      | ır | iei       | us (              |                    | mie               |                    |                   |                    | 1                 |                    |           |           |         |

|   | Jse<br>ases | PDN_ULP |     | ار ار    | MIC1_BIAS_PDN | MIC2_BIAS_PDN | MIC3_BIAS_PDN | MIC4_BIAS_PDN | MIC_BIAS_CTRL | ASP_RATE[3:0] | ASP_SDOUT1_PDN | ASP_SDOUT2_PDN |    | ADC1A_PDN |          |    | ADC2B_PDN | ADC1A_PREAMP[1:0] | ADC1A_PGA_VOL[5:0] | ADC1B_PREAMP[1:0] | ADC1B_PGA_VOL[5:0] | ADC2A_PREAMP[1:0] | ADC2A_PGA_VOL[5:0] | ADC2B_PREAMP[1:0] | ADC2B_PGA_VOL[5:0] | DMIC1_PDN | DMIC2_PDN | ASP_M/S |

| 1 |             |         |     |          |               |               | _             | _             | _             | _             | _              | _              | _  | _         | _        | _  | _         | _                 |                    | _                 | _                  | —                 | _                  | _                 | _                  |           | _         | _       |

| 2 | Α           | 1 -     |     |          | _             | - —           | _             | _             | _             |               | _              | _              | _  | _         | _        | _  | _         | _                 |                    | _                 | _                  | —                 | _                  | _                 |                    | _         | —         | —       |

|   | В           | 1 -     | _ 1 | _        | _             | _             | _             | _             | _             | _             | _              | _              | _  | _         | _        | _  | _         | _                 |                    | _                 | _                  | _                 | _                  | _                 | _                  | _         | _         | _       |

|   | С           | 0 '     | 1 – |          |               |               | _             | _             | _             | _             | _              | _              | _  | _         | <u> </u> | _  | _         | _                 |                    | _                 | _                  | _                 | _                  | _                 | _                  | _         | —         | _       |

|   | D           | 0 '     | 1 1 | <u> </u> |               |               | _             | _             | _             | _             | _              | _              |    | _         | _        |    | _         | _                 | _                  | —                 | _                  | —                 | _                  | _                 | _                  | _         | —         | —       |

| 3 | Α           | ,       | 0 ( | ) —      | 1             | 1             | 1             | 1             | _             | 1100          |                | 1              | 0  | 0         | 1        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   | 011000             | 1         | 1         | 0       |

|   | В           | 0 (     | 0 ( | ) —      | 0             | 1             | 1             | 1             | 10            | 1100          | 0              | 1              | 0  | 0         | 1        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   |                    | 1         | 1         | 0       |

|   | С           | 0 (     | 0 ( | ) 1      | 1             | 1             | 1             | 1             | _             | 0101          | 0              | 1              | 0  | 0         | 1        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   |                    | 1         | 1         | 0       |

|   | D           | 0 (     | 0 ( | ) 1      | 0             | 1             | 1             | 1             | 10            | 0101          | 0              | 1              | 0  | 0         | 1        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   | 011000             | 1         | 1         | 0       |

|   | Е           | 0 (     | 0 ( | ) 1      | 1             | 1             | 1             | 1             | _             | 0001          | 0              | 1              | 0  | 0         | 1        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   |                    | 1         | 1         | 0       |

|   | F           | 0 (     | 0 ( | ) 1      | 0             | 1             | 1             | 1             | 10            | 0001          | 0              | 1              | 0  | 0         | 1        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   |                    | 1         | 1         | 0       |

|   | G           | 0 (     | 0 ( | ) —      | 1             | 1             | 1             | 1             | _             | 1100          | 0              | 1              | 0  | 0         | 0        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   |                    | 1         | 1         | 0       |

|   | Н           | 0 (     | 0 ( | ) —      | 0             | 0             | 1             | 1             | 10            | 1100          | 0              | 1              | 0  | 0         | 0        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   |                    | 1         | 1         | 0       |

|   | I           | 0 (     | 0 ( | ) 1      | 1             | 1             | 1             | 1             | _             | 0101          | 0              | 1              | 0  | 0         | 0        | 1  | 1         |                   |                    | ı                 | 011000             |                   |                    | ı                 |                    | 1         | 1         | 0       |

|   | J           | 0 (     | 0 ( | ) 1      | 0             | 0             | 1             | 1             | 10            | 0101          | 0              | 1              | 0  | 0         | 0        | 1  | 1         |                   |                    |                   | 011000             |                   |                    |                   | 011000             | 1         | 1         | 0       |

|   | K           | 0 (     | 0 ( | ) 1      | 1             | 1             | 1             | 1             | _             | 0001          | 0              | 1              | 0  | 0         | 0        | 1  | 1         |                   |                    | ı                 | 011000             |                   |                    | ı                 | 011000             | 1         | 1         | 0       |

|   | L           | 0 (     | 0 ( | ) 1      | 0             | 0             | 1             | 1             | 10            | 0001          | 0              | 1              | 0  | 0         | 0        | 1  | 1         | 10                | 011000             | 10                | 011000             | 10                | 011000             | 10                | 011000             | 1         | 1         | 0       |

|   | M           | 0 (     | 0 ( | ) —      | 1             | 1             | 1             | 1             | _             | 1100          | 0              | 0              | 0  | 0         | 0        | 0  | 0         |                   |                    |                   | 011000             |                   |                    | 10                | 011000             | 1         | 1         | 0       |

|   | Ν           | 0 (     | 0 ( | ) —      | 0             | 0             | 0             | 0             | 10            | 1100          | 0              | 0              | 0  | 0         | 0        | 0  | 0         | 10                | 011000             | 10                | 011000             | 10                | 011000             | 10                | 011000             | 1         | 1         | 0       |

|   | 0           | 0 (     | 0 ( | 1        | 1             | 1             | 1             | 1             | _             | 0101          | 0              | 0              | 0  | 0         | 0        | 0  | 0         |                   | 011000             |                   |                    |                   |                    | _                 | 011000             | 1         | 1         | 0       |

|   | Р           | 0 (     | 0 ( | 1        | 0             | 0             | 0             | 0             | 10            | 0101          | 0              | 0              | 0  | 0         | 0        | 0  | 0         |                   | 011000             |                   |                    |                   |                    |                   | 011000             | 1         | 1         | 0       |

|   | Q           | 0 (     | 0 ( | 1        | 1             | 1             | 1             | 1             | _             | 0001          | 0              | 0              | 0  | 0         | 0        | 0  | 0         | 10                | 011000             | 10                | 011000             | 10                | 011000             | 10                | 011000             | 1         | 1         | 0       |

|   | R           | 0 (     | 0 ( | 1        | 0             | 0             | 0             | 0             | 10            | 0001          | 0              | 0              | 0  | 0         | 0        | 0  | 0         | 10                | 011000             | 10                | 011000             | 10                | 011000             | 10                | 011000             | 1         | 1         | 0       |

| 4 | Α           | 0 (     | 0 ( | ) —      | 1             | 1             | 1             | 1             | _             | 1100          | 0              | 0              | 0  | 0         | 0        | 0  | 0         | 00                | 000000             | 00                | 000000             | 00                | 000000             | 00                | 000000             | 1         | 1         | 0       |

|   | В           | 0 (     | 0 ( | 1        | 1             | 1             | 1             | 1             | _             | 0101          | 0              | 0              | 0  | 0         | 0        | 0  | 0         |                   |                    |                   | 000000             |                   |                    |                   |                    | 1         | 1         | 0       |

|   | С           | 0 (     | 0 ( | 1        | 1             | 1             | 1             | 1             | _             | 0001          | 0              | 0              | 0  | 0         | 0        | 0  | 0         | 00                | 000000             | 00                | 000000             | 00                | 000000             | 00                | 000000             | 1         | 1         | 0       |

| 5 | Α           | 0 (     | 0 ( | ) —      | 0             | 0             | 0             | 0             | 10            | 1100          | 0              | 0              | 0  | 0         | 0        | 0  | 0         | <u> </u>          | _                  | _                 | _                  | _                 | _                  | _                 | _                  | 0         | 0         | 0       |

|   | В           | 0 (     | 0 ( | 1        | 0             | 0             | 0             | 0             | 10            | 0101          | 0              | 0              | 0  | 0         | 0        | 0  | 0         |                   | _                  | <u> </u>          | _                  | _                 | _                  | —                 | _                  | 0         | 0         | 0       |

|   | С           | 0 (     | 0 0 | 1        | 0             | 0             | 0             | 0             | 10            | 0001          | 0              | 0              | 0  | 0         | 0        | 0  | 0         | _                 | _                  |                   |                    | _                 | _                  | <u> </u>          | _                  | 0         | 0         | 0       |

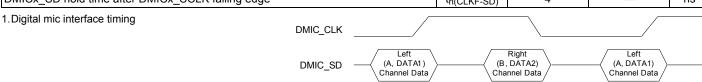

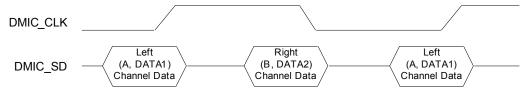

#### Table 3-10. Switching Specifications—Digital Mic Interface

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0 V; voltages are with respect to ground; parameters can vary with VA, typical performance data taken with VA = 1.8 V, VP = 3.6 V, min/max performance data taken with VA = 1.8 V, VP = 3.6 V;  $T_A = +25^{\circ}\text{C}$ ; logic 0 = ground, logic 1 = VA; DMIC\_DRIVE = 0 (normal); input timings are measured at  $V_{IL}$  and  $V_{IH}$  thresholds, and output timings are measured at  $V_{OL}$  and  $V_{OH}$  thresholds (see Table 3-14).

| Parameters 1,2                                       | Symbol                  | Min | Max    | Units |

|------------------------------------------------------|-------------------------|-----|--------|-------|

| Output clock (DMICx_SCLK) frequency                  | 1/t <sub>P</sub>        |     | 3.2[3] | MHz   |

| DMICx_SCLK duty cycle <sup>4</sup>                   |                         | 45  | 55     | %     |

| DMICx_SCLK rise time (10% to 90% of VA) 4            | t <sub>r</sub>          | _   | 21     | ns    |

| DMICx_SCLK fall time (90% to 10% of VA) <sup>4</sup> | t <sub>f</sub>          | _   | 13     | ns    |

| DMICx_SD setup time before DMICx_SCLK rising edge    | t <sub>s(SD-CLKR)</sub> | 10  | _      | ns    |

| DMICx_SD hold time after DMICx_SCLK rising edge      | t <sub>h(CLKR-SD)</sub> | 4   | _      | ns    |

| DMICx_SD setup time before DMICx_SCLK falling edge   | t <sub>s(SD-CLKF)</sub> | 10  | _      | ns    |

| DMICx_SD hold time after DMICx_SCLK falling edge     | t <sub>h(CLKF-SD)</sub> | 4   | _      | ns    |

- 2. Oversampling rate of the digital mic must match the oversampling rate of the CS53L30 internal decimators.

- 3. The output clock frequency follows the internal MCLK rate divided by 2 or 4, as set in the ADCx/DMICx control registers (see DMIC1\_SCLK\_DIV on p. 53 and DMIC2\_SCLK\_DIV on p. 55). DMICx\_SCLK is further divided by up to a factor of 4 when MCLK\_INT\_SCALE is set (see p. 48). MCLK source deviation from nominal supported rates is applied directly to the output clock rate by the same factor (e.g., a +100-ppm offset in the frequency of MCLK becomes a +100-ppm offset of DMICx\_SCLK.

- 4. Timing guaranteed with pull-up or pull-down resistor, with a minimum value 10 kΩ tied to DMIC2\_SCLK/AD1 for I2C address determination.

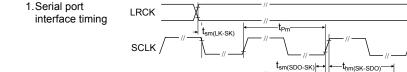

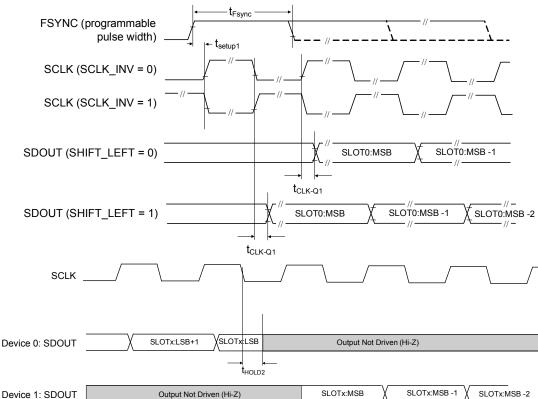

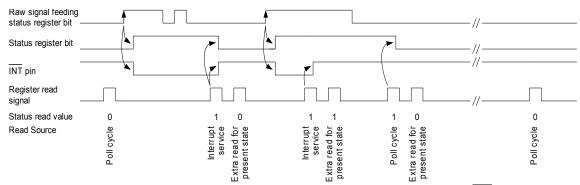

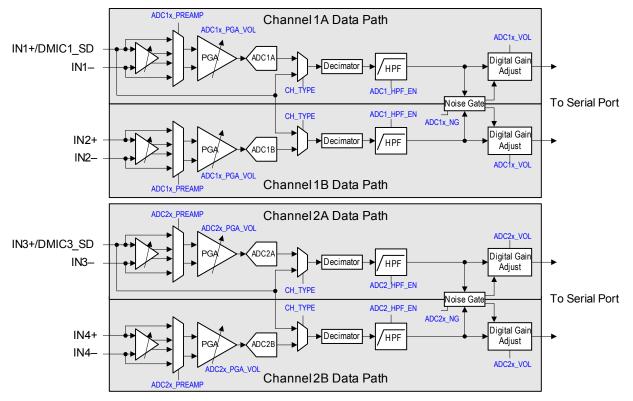

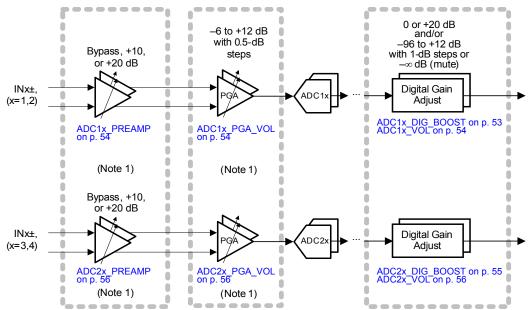

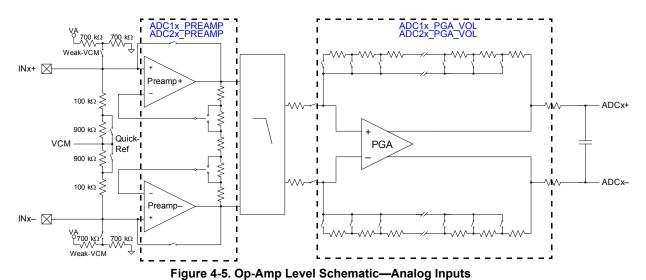

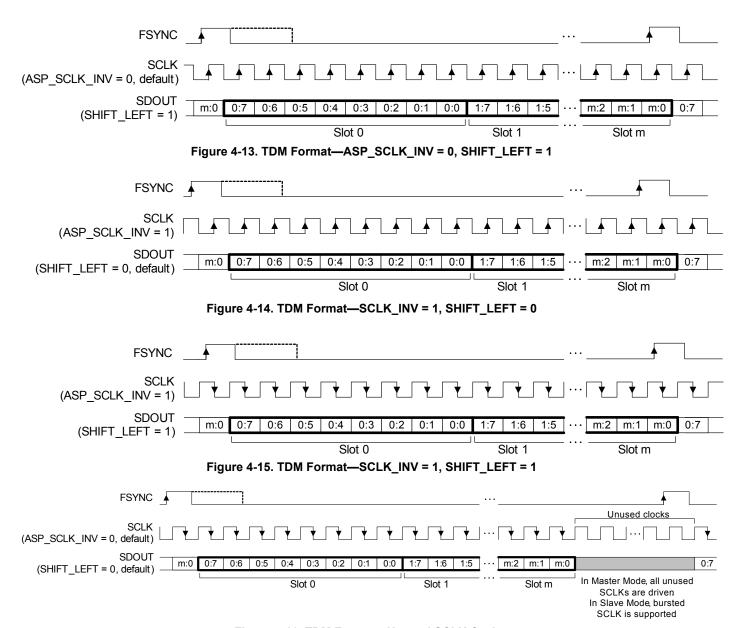

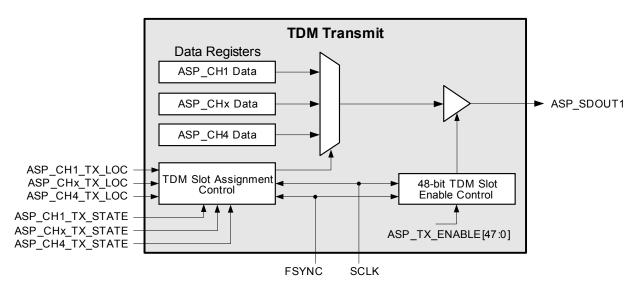

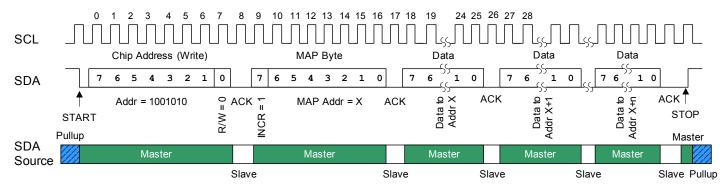

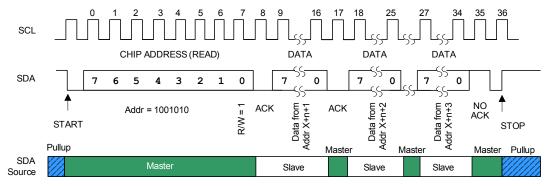

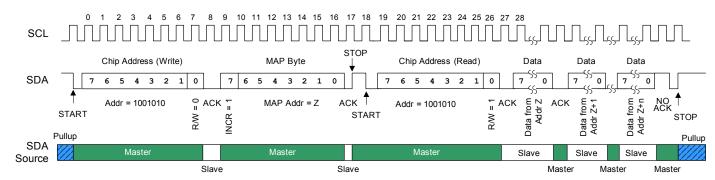

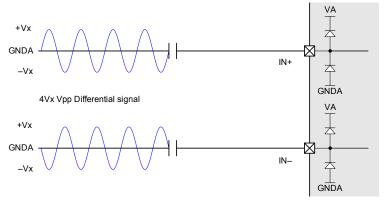

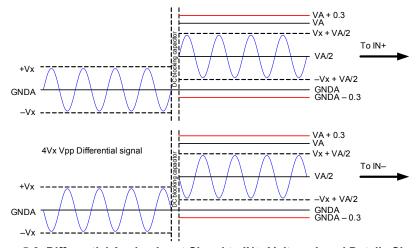

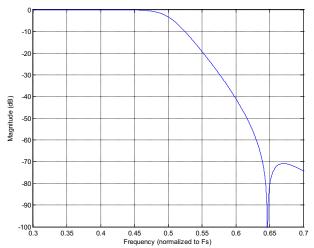

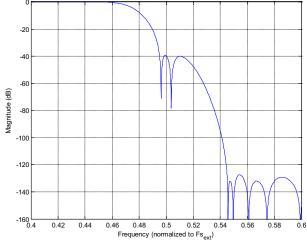

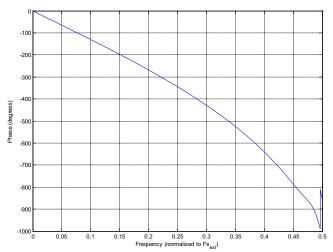

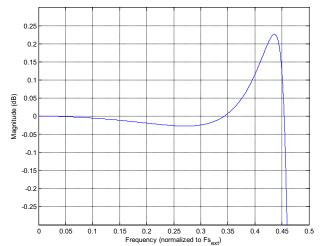

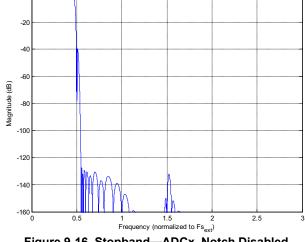

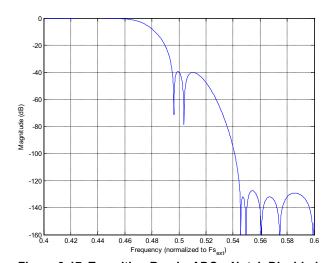

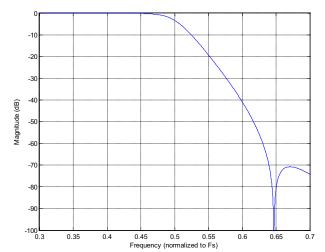

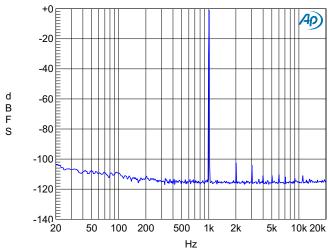

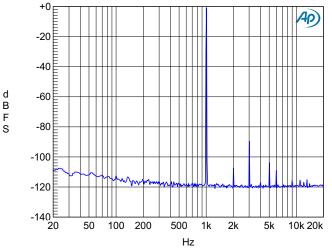

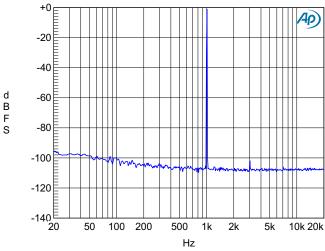

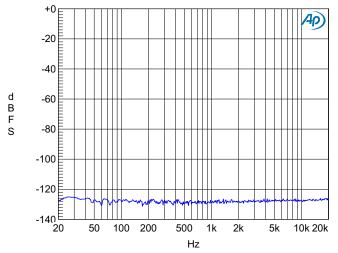

#### Table 3-11. Specifications—I2S