# 3.3 V Zero Delay Buffer

#### **Features**

- Zero input-output propagation delay, adjustable by capacitive load on FBK input

- Multiple configurations

- Multiple low-skew outputs

- 10 MHz to 133 MHz operating range

- 90 ps typical peak cycle-to-cycle jitter at 15 pF, 66 MHz

- Space-saving 8-pin 150-mil small outline integrated circuit (SOIC) package

- 3.3 V operation

- Industrial temperature available

### **Functional Description**

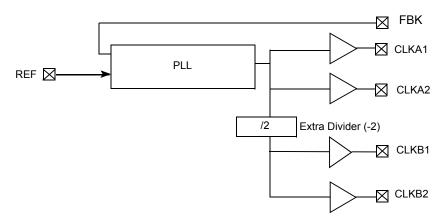

The CY2304 is a 3.3 V zero delay buffer designed to distribute high-speed clocks in PC, workstation, datacom, telecom, and other high performance applications.

The part has an on-chip phase-locked loop (PLL) that locks to an input clock presented on the REF pin. The PLL feedback is

required to be driven into the FBK pin, and can be obtained from one of the outputs. The input-to-output skew is guaranteed to be less than 250 ps, and output-to-output skew is guaranteed to be less than 200 ps.

The CY2304 has two banks of two outputs each.

The CY2304 PLL enters a power down state when there are no rising edges on the REF input. In this mode, all outputs are three-stated and the PLL is turned off, resulting in less than 25  $\mu$ A of current draw.

Multiple CY2304 devices can accept the same input clock and distribute it in a system. In this case, the skew between the outputs of two devices is guaranteed to be less than 500 ps.

The CY2304 is available in two different configurations, as shown in Available Configurations. The CY2304-1 is the base part, where the output frequencies equal the reference if there is no counter in the feedback path.

The CY2304-2 allows the user to obtain Ref and 1/2x or 2x frequencies on each output bank. The exact configuration and output frequencies depends on which output drives the feedback pin.

For a complete list of related documentation, click here.

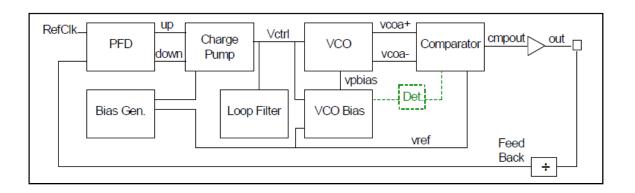

## **Logic Block Diagram**

## **Available Configurations**

| Device   | FBK from    | Bank A Frequency | Bank B Frequency |

|----------|-------------|------------------|------------------|

| CY2304-1 | Bank A or B | Reference        | Reference        |

| CY2304-2 | Bank A      | Reference        | Reference/2      |

| CY2304-2 | Bank B      | 2 × Reference    | Reference        |

Cypress Semiconductor Corporation

Document Number: 38-07247 Rev. \*N

## Contents

| Pin Configurations          | 3 |

|-----------------------------|---|

| Pin Definitions             |   |

| Zero Delay and Skew Control | 4 |

| Maximum Ratings             | 5 |

| Operating Conditions        | 5 |

| Electrical Characteristics  | 5 |

| Switching Characteristics   |   |

| Operating Conditions        |   |

| Electrical Characteristics  |   |

| Switching Characteristics   |   |

| Switching Waveforms         |   |

| Ordering Information        |   |

| Ordering Code Definitions   |   |

| Package Diagram             |   |

| Acronyms                    |   |

| Document Conventions                         | 13 |

|----------------------------------------------|----|

| Units of Measure                             | 13 |

| Appendix: Silicon Errata for                 |    |

| the Zero Delay Clock Buffers, CY2304         | 14 |

| Part Numbers Affected                        | 14 |

| CY2304 Errata Summary                        | 14 |

| CY2303 Qualification Status of fixed silicon | 14 |

| Document History Page                        | 16 |

| Sales, Solutions, and Legal Information      | 17 |

| Worldwide Sales and Design Support           | 17 |

| Products                                     | 17 |

| PSoC® Solutions                              | 17 |

| Cypress Developer Community                  | 17 |

| Technical Support                            | 17 |

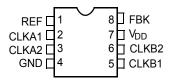

## **Pin Configurations**

Figure 1. 8-pin SOIC pinout

## **Pin Definitions**

8-pin SOIC

| Pin | Signal               | Description                                   |  |

|-----|----------------------|-----------------------------------------------|--|

| 1   | REF [1]              | Input reference frequency, 5 V tolerant input |  |

| 2   | CLKA1 [2]            | Clock output, Bank A                          |  |

| 3   | CLKA2 <sup>[2]</sup> | Clock output, Bank A                          |  |

| 4   | GND                  | Ground                                        |  |

| 5   | CLKB1 <sup>[2]</sup> | Clock output, Bank B                          |  |

| 6   | CLKB2 <sup>[2]</sup> | Clock output, Bank B                          |  |

| 7   | $V_{DD}$             | 3.3 V supply                                  |  |

| 8   | FBK                  | PLL feedback input                            |  |

- Notes

1. Weak pull-down.

2. Weak pull-down on all outputs.

## **Zero Delay and Skew Control**

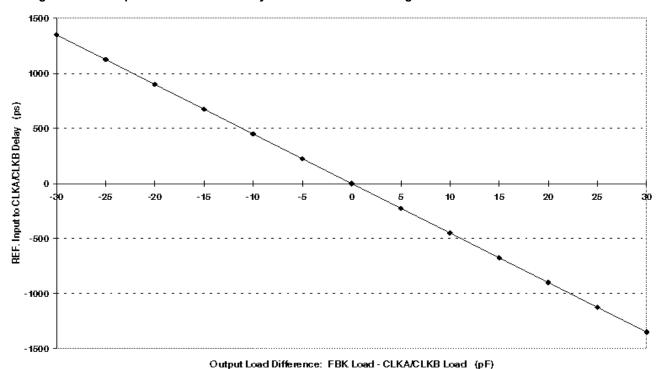

Figure 2. REF. Input to CLKA/CLKB Delay vs. Difference in Loading Between FBK Pin and CLKA/CLKB Pins

To close the feedback loop of the CY2304, the FBK pin can be driven from any of the four available output pins. The output driving the FBK pin is driving a total load of 7 pF, with any additional load that it drives. The relative loading of this output (with respect to the remaining outputs) can adjust the input-output delay. This is shown in Figure 2.

For applications requiring zero input-output delay, all outputs including the one providing feedback must be equally loaded. If input-output delay adjustments are required, use the graph shown in Figure 2 to calculate loading differences between the feedback output and remaining outputs.

For zero output-output skew, be sure to load outputs equally. For further information on using CY2304, refer to the application note AN1234 - Understanding Cypress's Zero Delay Buffers.

## **Maximum Ratings**

Supply voltage to ground potential ............ -0.5~V to +7.0 VDC input voltage (except Ref) .......... -0.5 V to  $V_{DD}$  + 0.5 V DC input voltage REF ......-0.5 V to 7 V

| Storage temperature65 °C to +150 °                      | С |

|---------------------------------------------------------|---|

| Junction temperature 150 °                              | С |

| Static discharge voltage (per MIL-STD-883, Method 3015) | V |

## **Operating Conditions**

For CY2304SXC Commercial Temperature Devices

| Parameter       | Description                                                                                                | Min  | Max | Unit |

|-----------------|------------------------------------------------------------------------------------------------------------|------|-----|------|

| $V_{DD}$        | Supply voltage                                                                                             | 3.0  | 3.6 | V    |

| T <sub>A</sub>  | Operating temperature (ambient temperature)                                                                | 0    | 70  | °C   |

| C <sub>L</sub>  | Load capacitance (below 100 MHz)                                                                           | _    | 30  | pF   |

|                 | Load capacitance (from 100 MHz to 133 MHz)                                                                 | _    | 15  | pF   |

| C <sub>IN</sub> | Input capacitance [3]                                                                                      | _    | 7   | pF   |

| t <sub>PU</sub> | Power-up time for all $V_{\text{DD}}$ s to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | 50  | ms   |

## **Electrical Characteristics**

For CY2304SXC Commercial Temperature Devices

| Parameter                 | Description               | Test Conditions                                                 | Min | Max   | Unit |

|---------------------------|---------------------------|-----------------------------------------------------------------|-----|-------|------|

| V <sub>IL</sub>           | Input LOW voltage         |                                                                 | _   | 0.8   | V    |

| V <sub>IH</sub>           | Input HIGH voltage        |                                                                 | 2.0 | _     | V    |

| $I_{IL}$                  | Input LOW current         | V <sub>IN</sub> = 0 V                                           | _   | 50.0  | μА   |

| I <sub>IH</sub>           | Input HIGH current        | $V_{IN} = V_{DD}$                                               | _   | 100.0 | μА   |

| $V_{OL}$                  | Output LOW voltage [4]    | I <sub>OL</sub> = 8 mA (-1, -2)                                 | _   | 0.4   | V    |

| V <sub>OH</sub>           | Output HIGH voltage [4]   | I <sub>OH</sub> = -8 mA (-1, -2)                                | 2.4 | _     | V    |

| I <sub>DD</sub> (PD mode) | Power-down supply current | REF = 0 MHz                                                     | _   | 12.0  | μА   |

| I <sub>DD</sub>           | Supply current            | Unloaded outputs, 100 MHz REF, Select inputs at $V_{DD}$ or GND | _   | 45.0  | mA   |

|                           |                           | Unloaded outputs, 66 MHz REF (-1, -2)                           | _   | 32.0  | mA   |

|                           |                           | Unloaded outputs, 33 MHz REF (-1, -2)                           | -   | 18.0  | mA   |

Document Number: 38-07247 Rev. \*N

Applies to both REF clock and FBK.

Parameter is guaranteed by design and characterization. Not 100% tested in production.

## **Switching Characteristics**

For CY2304SXC Commercial Temperature Devices

| Parameter [5]     | Name                                                    | Test Conditions                                                 | Min  | Тур  | Max   | Unit |

|-------------------|---------------------------------------------------------|-----------------------------------------------------------------|------|------|-------|------|

| t <sub>1</sub>    | Output frequency                                        | 30 pF load, all devices                                         | 10   | _    | 100   | MHz  |

| t <sub>1</sub>    | Output frequency                                        | 15 pF load, -1, -2 devices                                      | 10   | -    | 133.3 | MHz  |

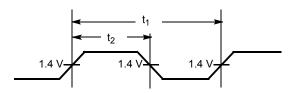

| t <sub>DC</sub>   | Duty cycle $^{[6]} = t_2 \div t_1 (-1, -2)$             | Measured at 1.4 V,<br>F <sub>OUT</sub> = 66.66 MHz, 30-pF load  | 40.0 | 50.0 | 60.0  | %    |

| t <sub>DC</sub>   | Duty cycle $^{[6]} = t_2 \div t_1 (-2)$                 | Measured at 1.4 V,<br>F <sub>OUT</sub> = 83.0 MHz, 15-pF load   | 40.0 | 50.0 | 60.0  | %    |

| t <sub>DC</sub>   | Duty cycle $^{[6]} = t_2 \div t_1 (-1, -2)$             | Measured at 1.4 V,<br>F <sub>OUT</sub> < 50 MHz, 15-pF load     | 45.0 | 50.0 | 55.0  | %    |

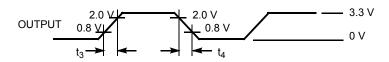

| t <sub>3</sub>    | Rise time <sup>[6]</sup> (-1, -2)                       | Measured between 0.8 V and 2.0 V, 30-pF load                    | -    | _    | 2.20  | ns   |

| t <sub>3</sub>    | Rise time <sup>[6]</sup> (-1, -2)                       | Measured between 0.8 V and 2.0 V, 15-pF load                    | _    | _    | 1.50  | ns   |

| t <sub>4</sub>    | Fall time <sup>[6]</sup> (-1, -2)                       | Measured between 0.8 V and 2.0 V, 30-pF load                    | _    | _    | 2.20  | ns   |

| t <sub>4</sub>    | Fall time <sup>[6]</sup> (-1, -2)                       | Measured between 0.8 V and 2.0 V, 15 pF load                    | _    | _    | 1.50  | ns   |

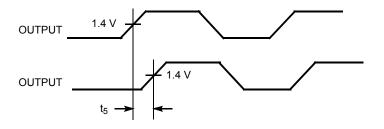

| t <sub>5</sub>    | Output-to-output skew on same Bank (-1, -2) [6]         | All outputs equally loaded                                      | _    | _    | 200   | ps   |

|                   | Output bank A to output bank B skew (-1)                | All outputs equally loaded                                      | _    | _    | 200   | ps   |

|                   | Output bank A to output bank B skew (-2)                | All outputs equally loaded                                      | _    | _    | 400   | ps   |

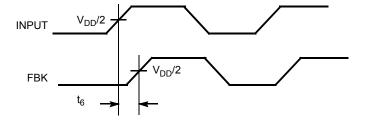

| t <sub>6</sub>    | Skew, REF rising edge to FBK rising edge <sup>[6]</sup> | Measured at V <sub>DD</sub> /2                                  | _    | 0    | ±250  | ps   |

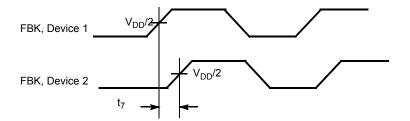

| t <sub>7</sub>    | Device-to-device skew [6]                               | Measured at V <sub>DD</sub> /2 on the FBK pins of devices       | _    | 0    | 500   | ps   |

| t <sub>J</sub>    | Cycle-to-cycle jitter [6] (-1)                          | Measured at 66.67 MHz, loaded outputs, 15-pF load               | _    | 90   | 175   | ps   |

|                   |                                                         | Measured at 66.67 MHz, loaded outputs, 30-pF load               | _    | _    | 200   | ps   |

|                   |                                                         | Measured at 133.3 MHz, loaded outputs, 15-pF load               | _    | _    | 100   | ps   |

| t <sub>J</sub>    | Cycle-to-cycle jitter [6] (-2)                          | Measured at 66.67 MHz, loaded outputs 30-pF load                | -    | _    | 400   | ps   |

|                   |                                                         | Measured at 66.67 MHz, loaded outputs 15-pF load                | -    | _    | 375   | ps   |

| t <sub>LOCK</sub> | PLL lock time <sup>[6]</sup>                            | Stable power supply, valid clocks presented on REF and FBK pins | -    | _    | 1.0   | ms   |

#### Notes

<sup>5.</sup> All parameters are specified with loaded output.6. Parameter is guaranteed by design and characterization. Not 100% tested in production.

## **Operating Conditions**

For CY2304SXI Industrial Temperature Devices

| Parameter       | Description                                 | Min | Max | Unit |

|-----------------|---------------------------------------------|-----|-----|------|

| $V_{DD}$        | Supply voltage                              | 3.0 | 3.6 | V    |

| T <sub>A</sub>  | Operating temperature (ambient temperature) | -40 | 85  | °C   |

| C <sub>L</sub>  | Load capacitance (below 100 MHz)            |     | 30  | pF   |

|                 | Load capacitance (from 100 MHz to 133 MHz)  | _   | 15  | pF   |

| C <sub>IN</sub> | Input capacitance                           | -   | 7   | pF   |

## **Electrical Characteristics**

For CY2304SXI Industrial Temperature Devices

| Parameter                 | Description               | Test Conditions                                             | Min | Max   | Unit |

|---------------------------|---------------------------|-------------------------------------------------------------|-----|-------|------|

| V <sub>IL</sub>           | Input LOW voltage         |                                                             | _   | 0.8   | V    |

| V <sub>IH</sub>           | Input HIGH voltage        |                                                             | 2.0 | _     | V    |

| I <sub>IL</sub>           | Input LOW current         | V <sub>IN</sub> = 0 V                                       | _   | 50.0  | μА   |

| I <sub>IH</sub>           | Input HIGH current        | $V_{IN} = V_{DD}$                                           | _   | 100.0 | μА   |

| V <sub>OL</sub>           | Output LOW voltage [7]    | I <sub>OL</sub> = 8 mA (-1, -2)                             | _   | 0.4   | V    |

| V <sub>OH</sub>           | Output HIGH voltage [7]   | I <sub>OH</sub> = –8 mA (-1, -2)                            | 2.4 | _     | V    |

| I <sub>DD</sub> (PD mode) | Power-down supply current | REF = 0 MHz                                                 | _   | 25.0  | μА   |

| I <sub>DD</sub>           | Supply current            | Unloaded outputs, 100 MHz, Select inputs at $V_{DD}$ or GND | _   | 45.0  | mA   |

|                           |                           | Unloaded outputs, 66 MHz REF (-1, -2)                       | _   | 35.0  | mA   |

|                           |                           | Unloaded outputs, 33 MHz REF (-1, -2)                       | _   | 20.0  | mA   |

## **Thermal Resistance**

| Parameter [8] | Description                           | Test Conditions                                                                                 | 8-pin SOIC | Unit |

|---------------|---------------------------------------|-------------------------------------------------------------------------------------------------|------------|------|

| - 0/1         | 0                                     | Test conditions follow standard test methods and procedures for measuring thermal impedance, in | 140        | °C/W |

| 30            | Thermal resistance (junction to case) | accordance with EIA/JESD51.                                                                     | 54         | °C/W |

- 7. Parameter is guaranteed by design and characterization. Not 100% tested in production.8. These parameters are guaranteed by design and are not tested.

# **Switching Characteristics**

for CY2304SXI Industrial Temperature Devices

| Parameter [9]     | Name                                             | Test Conditions                                                   | Min  | Тур  | Max   | Unit |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------|------|------|-------|------|

| t <sub>1</sub>    | Output frequency                                 | 30-pF load, All devices                                           | 10   | _    | 100   | MHz  |

| t <sub>1</sub>    | Output frequency                                 | 15-pF load, All devices                                           | 10   | -    | 133.3 | MHz  |

| t <sub>DC</sub>   | Duty cycle $^{[10]} = t_2 \div t_1 (-1, -2)$     | Measured at 1.4 V, F <sub>OUT</sub> = 66.66<br>MHz,<br>30-pF load | 40.0 | 50.0 | 60.0  | %    |

| t <sub>DC</sub>   | Duty cycle [10] = $t_2 \div t_1$ (-2)            | Measured at 1.4 V,<br>F <sub>OUT</sub> = 83.0 MHz, 15-pF load     | 40.0 | 50.0 | 60.0  | %    |

| t <sub>DC</sub>   | Duty cycle [10] = $t_2 \div t_1$ (-1, -2)        | Measured at 1.4 V,<br>F <sub>OUT</sub> < 50 MHz, 15-pF load       | 45.0 | 50.0 | 55.0  | %    |

| t <sub>3</sub>    | Rise time <sup>[10]</sup> (-1, -2)               | Measured between 0.8 V and 2.0 V, 30-pF load                      | _    | _    | 2.50  | ns   |

| t <sub>3</sub>    | Rise time <sup>[10]</sup> (-1, -2)               | Measured between 0.8 V and 2.0 V, 15-pF load                      | _    | _    | 1.50  | ns   |

| t <sub>4</sub>    | Fall time <sup>[10]</sup> (-1, -2)               | Measured between 0.8 V and 2.0 V, 30-pF load                      | -    | _    | 2.50  | ns   |

| t <sub>4</sub>    | Fall time <sup>[10]</sup> (-1, -2)               | Measured between 0.8 V and 2.0 V, 15-pF load                      | -    | _    | 1.50  | ns   |

| t <sub>5</sub>    | Output-to-output skew on same bank (-1, -2) [10] | All outputs equally loaded                                        | -    | _    | 200   | ps   |

|                   | Output bank A to output bank B skew (-1)         | All outputs equally loaded                                        | _    | _    | 200   | ps   |

|                   | Output bank A to output bank B skew (-2)         | All outputs equally loaded                                        | -    | _    | 400   | ps   |

| t <sub>6</sub>    | Skew, REF rising edge to FBK rising edge [10]    | Measured at V <sub>DD</sub> /2                                    | -    | 0    | ±250  | ps   |

| t <sub>7</sub>    | Device-to-device skew [10]                       | Measured at V <sub>DD</sub> /2 on the FBK pins of devices         | _    | 0    | 500   | ps   |

| t <sub>J</sub>    | Cycle-to-cycle jitter [10] (-1)                  | Measured at 66.67 MHz, loaded outputs, 15-pF load                 | -    | _    | 180   | ps   |

|                   |                                                  | Measured at 66.67 MHz, loaded outputs, 30-pF load                 | _    | _    | 200   | ps   |

|                   |                                                  | Measured at 133.3 MHz, loaded outputs, 15-pF load                 | _    | _    | 100   | ps   |

| t <sub>J</sub>    | Cycle-to-cycle jitter [10] (-2)                  | Measured at 66.67 MHz, loaded outputs, 30-pF load                 | -    | _    | 400   | ps   |

|                   |                                                  | Measured at 66.67 MHz, loaded outputs, 15-pF load                 | -    | _    | 380   | ps   |

| t <sub>LOCK</sub> | PLL lock time <sup>[10]</sup>                    | Stable power supply, valid clocks presented on REF and FBK pins   | -    | -    | 1.0   | ms   |

#### Notes

All parameters are specified with loaded output.

Parameter is guaranteed by design and characterization. Not 100% tested in production.

## **Switching Waveforms**

Figure 3. Duty Cycle Timing

Figure 4. All Outputs Rise/Fall Time

Figure 5. Output-Output Skew

Figure 6. Input-Output Skew

Figure 7. Device-Device Skew

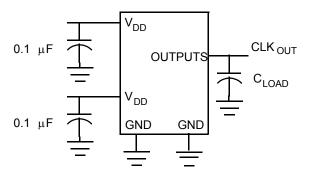

Figure 8. Test Circuit # 1

Test circuit for all parameters

## **Ordering Information**

| Ordering Code | Package Type                                     | Operating Range |  |

|---------------|--------------------------------------------------|-----------------|--|

| Pb-free       |                                                  |                 |  |

| CY2304SXC-1   | 8-pin SOIC (150 Mils)                            | Commercial      |  |

| CY2304SXC-1T  | 8-pin SOIC (150 Mils) – Tape and Reel            | Commercial      |  |

| CY2304SXI-1   | 8-pin SOIC (150 Mils)                            | Industrial      |  |

| CY2304SXI-1T  | 8-pin SOIC (150 Mils) – Tape and Reel Industrial |                 |  |

| CY2304SXC-2   | 8-pin SOIC (150 Mils) Commercial                 |                 |  |

| CY2304SXC-2T  | 8-pin SOIC (150 Mils) – Tape and Reel Commercial |                 |  |

| CY2304SXI-2   | 8-pin SOIC (150 Mils) Industrial                 |                 |  |

| CY2304SXI-2T  | 8-pin SOIC (150 Mils) – Tape and Reel Industrial |                 |  |

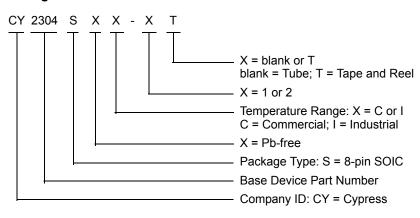

## **Ordering Code Definitions**

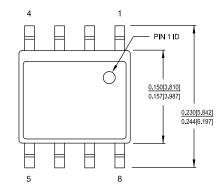

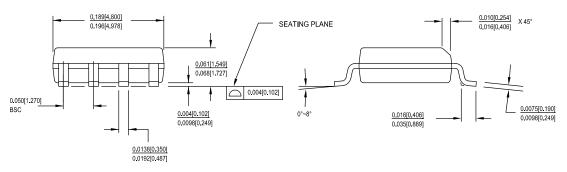

## **Package Diagram**

Figure 9. 8-pin SOIC (150 Mils) Package Outline, 51-85066

- PIN 1 ID IS OPTIONAL,

ROUND ON SINGLE LEADFRAME

RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART#   |               |  |

|---------|---------------|--|

| S08.15  | STANDARD PKG  |  |

| SZ08.15 | LEAD FREE PKG |  |

| SW8.15  | LEAD FREE PKG |  |

51-85066 \*H

## **Acronyms**

| Acronym | Description                      |  |

|---------|----------------------------------|--|

| PLL     | Phase Locked Loop                |  |

| SOIC    | Small Outline Integrated Circuit |  |

## **Document Conventions**

## **Units of Measure**

| Symbol | Unit of Measure |  |

|--------|-----------------|--|

| °C     | degree Celsius  |  |

| MHz    | megahertz       |  |

| μΑ     | microampere     |  |

| mA     | milliampere     |  |

| ms     | millisecond     |  |

| ns     | nanosecond      |  |

| pF     | picofarad       |  |

| ps     | picosecond      |  |

| V      | volt            |  |

### Appendix: Silicon Errata for the Zero Delay Clock Buffers, CY2304

This section describes the errors, workaround solution and silicon design fixes for Cypress zero delay clock buffers belonging to the families CY2304. Details include errata trigger conditions, scope of impact, available workarounds, and silicon revision applicability. Contact your local Cypress Sales Representative if you have questions.

#### **Part Numbers Affected**

#### Table 1. Part Numbers Affected

| Part Number  | Device Variants |

|--------------|-----------------|

| CY2304SXC-1  | All Variants    |

| CY2304SXC-1T | All Variants    |

| CY2304SXC-2  | All Variants    |

| CY2304SXC-2T | All Variants    |

| CY2304SXI-1  | All Variants    |

| CY2304SXI-1T | All Variants    |

| CY2304SXI-2  | All Variants    |

| CY2304SXI-2T | All Variants    |

#### CY2304 Errata Summary

| Items                             | Part Number | Fix Status                                              |

|-----------------------------------|-------------|---------------------------------------------------------|

| Start up lock time issue [CY2304] | All         | Silicon fixed. New silicon available from WW 10 of 2013 |

#### CY2303 Qualification Status of fixed silicon

Product Status: In production

Qualification report last updated on 11/27/2012

http://www.cypress.com/?rID=72595

#### 1. Start up lock time issue

#### ■ Problem Definition

Output of CY2304 fails to locks within 1 ms upon power up (as per datasheet spec)

#### ■ Parameters Affected

PLL lock time

### ■ Trigger Condition(s)

Start up

#### ■ Scope of Impact

It can impact the performance of system and its throughput

#### ■ Workaround

Apply reference input (RefClk) before power up ( $V_{DD}$ ). If RefClk is applied after power up, noise gets coupled on the output and propagates back to the PLL causing it to take higher time to acquire lock. If reference input is present during power up, noise will not propagate to the PLL and device will start up normally without problems.

#### ■ Fix Status

This issue is due to design marginality. Two minor design modifications have been made to address this problem.

- a. Addition of VCO bias detector block as shown in the following figure keeps comparator power down till VCO bias is present and thereby eliminating the propagation of noise to feedback.

- b. Bias generator enhancement for successful initialization.

# **Document History Page**

| _    |         | Orig. of      | Submission |                                                                                                                                                                                                                                                                                                     |  |

|------|---------|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rev. | ECN     | Change        | Date       | Description of Change                                                                                                                                                                                                                                                                               |  |

| **   | 110512  | SZV           | 12/11/01   | Change from Spec number: 38-01010 to 38-07247                                                                                                                                                                                                                                                       |  |

| *A   | 112294  | CKN           | 03/04/02   | On Pin Configuration Diagram (p.1), swapped CLKA2 and CLKA1                                                                                                                                                                                                                                         |  |

| *B   | 113934  | CKN           | 05/01/02   | Added Operating Conditions for CY2304SI-X Industrial Temperature Devices p. 4                                                                                                                                                                                                                       |  |

| *C   | 121851  | RBI           | 12/14/02   | Power up requirements added to Operating Conditions Information                                                                                                                                                                                                                                     |  |

| *D   | 308436  | RGL           | 01/26/05   | Added Lead-free Devices                                                                                                                                                                                                                                                                             |  |

| *E   | 2542331 | AESA          | 09/18/08   | Updated template. Added Note "Not recommended for new designs." Removed part number CY2304SI-2 and CY2304SI-2T. Changed Lead-Free to Pb-Free. Changed IDD (PD mode) from 12.0 to 25.0 $\mu$ A. Deleted Duty Cycle parameters for F <sub>OUT</sub> < 50.0 MHz for commercial and industrial devices. |  |

| *F   | 2673353 | KVM /<br>PYRS | 03/13/09   | Reverted IDD (PD mode) and Duty Cycle parameters back to the values in revision *D: Changed IDD (PD mode) from 25 to 12 $\mu$ A for commercial devices. Added Duty Cycle parameters for F <sub>OUT</sub> < 50.0 MHz for commercial and industrial devices.                                          |  |

| *G   | 2906571 | KVM           | 04/07/10   | Removed parts CY2304SC-1, CY2304SC-1T, CY2304SC-2, CY2304SC-2T, CY2304SI-1, CY2304SI-1T from the ordering information table. Updated Package Diagram.                                                                                                                                               |  |

| *H   | 3072674 | BASH          | 10/27/2010 | Corrected part number in all table titles (pages 3 to 5) from CY2304SC-X and CY2304SI-X to CY2304SXC and CY2304SXI. Removed "except t <sub>8</sub> " from Figure 7                                                                                                                                  |  |

| *    | 3162681 | BASH          | 02/04/2011 | Updated to new template.                                                                                                                                                                                                                                                                            |  |

| *J   | 3204827 | CXQ           | 03/24/2011 | Added duty cycle spec for 83.0 MHz output condition.                                                                                                                                                                                                                                                |  |

| *K   | 4018186 | CINM          | 06/10/2013 | Updated Package Diagram:<br>spec 51-85066 – Changed revision from *D to *F.<br>Added Appendix: Silicon Errata for the Zero Delay Clock Buffers, CY2304.                                                                                                                                             |  |

| *L   | 4291190 | CINM          | 02/25/2014 | Updated to new template. Completing Sunset Review.                                                                                                                                                                                                                                                  |  |

| *M   | 4578443 | AJU           | 11/25/2014 | Updated Functional Description: Added "For a complete list of related documentation, click here." at the end.                                                                                                                                                                                       |  |

| *N   | 5270465 | PSR           | 05/13/2016 | Added Thermal Resistance. Updated Package Diagram: spec 51-85066 – Changed revision from *F to *H. Updated to new template.                                                                                                                                                                         |  |

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Wireless/RF

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc **Touch Sensing** cypress.com/touch **USB Controllers** cypress.com/usb

cypress.com/wireless

#### PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | Projects | Video | Blogs | Training | Components

### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2001-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 38-07247 Rev. \*N Revised May 13, 2016 Page 17 of 17

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Cypress Semiconductor:

<u>CY2304SXC-1</u> <u>CY2304SXC-1T</u> <u>CY2304SXC-2</u> <u>CY2304SXC-2T</u> <u>CY2304SXI-1</u> <u>CY2304SXI-1T</u> <u>CY2304SXI-1T</u> <u>CY2304SXI-2T</u>