# THIS SPEC IS OBSOLETE

**Spec No**: 38-07521

Spec Title: CY25901 SPREAD SPECTRUM CLOCK GENERATOR

Sunset Owner: Christopher Martin (CXQ)

Replaced by: None

# Spread Spectrum Clock Generator

#### **Features**

- Supports clock requirements for Spread Spectrum

- 40-MHz Spread Spectrum clock output

- Reference clock output

- Two spread bandwidths: 1%, 3%

- External clock or Cera-Lock input

- 3.3V operation

- 8-pin SOIC package

## **Table 1. Function Table**

## Description

The CY25901 clock generator provides a low-electromagnetic interference (EMI) clock output. It features Spread Spectrum technology, a modulation technique designed specifically for reducing EMI at the fundamental frequency and its harmonics.

|                |      |        | CLKOUT (Spread Spectrum)    |                            |  |  |  |

|----------------|------|--------|-----------------------------|----------------------------|--|--|--|

| SSSEL          | SSON | REFOUT | CY25901SC                   | CY25901SC-1                |  |  |  |

| 0              | 0    | XIN    | = XIN ± 0.35% (0.7% center) | = XIN ± 0.5% (1.0% center) |  |  |  |

| 1              | 0    | XIN    | = XIN ± 1.20% (2.4% center) | = XIN ± 1.5% (3.0% center) |  |  |  |

| X (don't care) | 1    | XIN    | = XIN (No Spread)           | = XIN (No Spread)          |  |  |  |

## **Pin Description**

| Pin No. | Name   | I/O | Description                                                                                                                                                |

|---------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CLKOUT | 0   | Spread Spectrum Clock Output. See Table 1 for frequency selections.                                                                                        |

| 2       | VDD    | PWR | Power Supply.                                                                                                                                              |

| 3       | VSS    | PWR | Common Ground.                                                                                                                                             |

| 4       | XIN    | _   | Oscillator Buffer Input. Connect to an external parallel resonant crystal or externally generated reference clock.                                         |

| 5       | XOUT   | 0   | Oscillator Buffer Output. Connect to an external parallel resonant crystal. Do not connect when an externally generated reference clock is applied at XIN. |

| 6       | SSSEL  | I   | Spread Spectrum Select Input. See Table 1. internally pulled up.                                                                                           |

| 7       | REFOUT | 0   | Buffered Output of XIN.                                                                                                                                    |

| 8       | SSON#  | 1   | Spread Spectrum Enable Input. When asserted low, Spread Spectrum is enabled. Internally pulled down.                                                       |

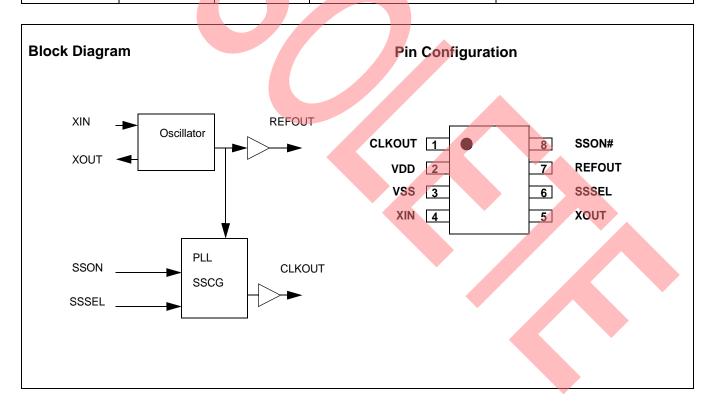

## **Spread Spectrum Clock Generator**

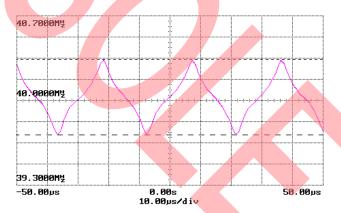

Spread Spectrum Clock Generator (SSCG) is a frequency modulation technique used to reduce EMI radiation generated by repetitive digital signals, mainly clocks. A clock radiates EM energy at its fundamental frequency as well as its harmonics. Spread Spectrum distributes this energy over a small frequency bandwidth, and decreasing the peak value of

radiated energy over the spectrum. This technique is achieved by modulating the clock around or below the center of its reference frequency by a certain percentage (which also determines the energy distribution bandwidth).

The SSCG function is enabled when SSON pin is set to low. Resulting in a spread bandwidth that is center spread, amount as selected by SSSEL (see *Table 1*).

Figure 1. Modulation Frequency Profile

Figure 2. Spread Spectrum

Document #: 38-07521 Rev. \*A Page 2 of 5

## **Absolute Maximum Ratings**

| Parameter          | Description                       | Condition                   | Min. | Max.                 | Unit |

|--------------------|-----------------------------------|-----------------------------|------|----------------------|------|

| $V_{DD}$           | Core Supply Voltage               |                             | -0.5 | 4.6                  | V    |

| V <sub>IN</sub>    | Input Voltage                     | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> +0.5 | VDC  |

| T <sub>S</sub>     | Temperature, Storage              | Non Functional              | -65  | 150                  | °C   |

| T <sub>A</sub>     | Temperature, Operating Ambient    | Functional                  | -10  | 85                   | °C   |

| T <sub>J</sub>     | Temperature, Junction             | Functional                  | -    | 150                  | °C   |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000 | _                    | V    |

| UL-94              | Flammability Rating               | @1/8 in.                    | V-0  |                      |      |

| MSL                | Moisture Sensitivity Level 1      |                             |      |                      |      |

## DC Specifications

| Parameter       | Description                                 | Condition                         | Min.     | Тур.     | Max.     | Unit |

|-----------------|---------------------------------------------|-----------------------------------|----------|----------|----------|------|

| $V_{DD}$        | Operating Voltage                           | 3.3V @ ±10%                       | 2.97     | 3.3      | 3.63     | V    |

| $V_{IL}$        | Input Low Voltage <sup>[1]</sup>            | SSON# and SSSEL                   | _        | _        | 0.8      | V    |

| V <sub>IH</sub> | Input High Voltage <sup>[1]</sup>           | Inputs                            | 2.2      | _        | _        | V    |

| VthXIN          | XIN Threshold Voltage                       | XIN                               | 0.3*VDDC | 0.5*VDDC | 0.7*VDDC | V    |

| I <sub>DD</sub> | Dynamic Supply Current                      | V <sub>DD</sub> = 3.3V and CL = 0 | _        | 20       | 25       | mΑ   |

| I <sub>IL</sub> | Input Low Current                           | SSSEL = VSS                       | -55      | -30      | _        | μΑ   |

| I <sub>IH</sub> | Input High Current                          | SSON = V <sub>DD</sub>            | -        | 30       | 55       | μΑ   |

| V <sub>OL</sub> | Output Low Voltage                          | 1 <sub>OL</sub> = 4.0 mA          | _        | _        | 0.4      | V    |

| V <sub>OH</sub> | Output High Voltage                         | $I_{OH} = -4.0 \text{ mA}$        | 2.4      | _        | _        | V    |

| C <sub>IN</sub> | Input Capacitance                           | SSON# and SSSEL Inputs            | -        | 5        | 10       | pF   |

| C <sub>X</sub>  | XIN, XOUT Capacitance <sup>[2]</sup>        | XIN and XOUT                      | -        | 5        | _        | pF   |

| PU/PD           | Pull-up/Pull-down Resistance <sup>[1]</sup> | SSON# and SSSEL Inputs            | 50       | 100      | 200      | kΩ   |

## AC Specifications<sup>[3]</sup>

| Parameter          | Description                                 | Condition                          | Min. | Тур. | Max. | Unit |

|--------------------|---------------------------------------------|------------------------------------|------|------|------|------|

| F <sub>IR</sub>    | Input Frequency Range                       |                                    | 36   | 40   | 44   | MHz  |

| E <sub>RXIN</sub>  | XIN Edge Rate                               | XIN driven by external clock       | -    | 1    | -    | V/nS |

| T <sub>DCXIN</sub> | XIN Duty Cycle                              | XIN driven by external clock       | 40   | 50   | 60   | %    |

| T <sub>R</sub>     | Outputs Rise Time <sup>[4]</sup>            | REFOUT, CLKOUT                     | -    | -    | 3    | ns   |

| T <sub>F</sub>     | Outputs Fall Time <sup>[4]</sup>            | REFOUT, CLKOUT                     |      | -    | 3    | ns   |

| BW%1               | CY25901SC, Spread %                         | SSON=0,SSSEL = 0                   | 0.5  | 0.7  | 0.9  | %    |

| BW%2               | CY25901SC, Spread %                         | SSON=0,SSSEL = 1                   | 1.7  | 2.4  | 3.1  | %    |

| BW%3               | CY25901SC-1, Spread %                       | SSON=0,SSSEL = 0                   | 0.7  | 1    | 1.3  | %    |

| BW%4               | CY25901SC-1, Spread %                       | SSON=0,SSSEL = 1                   | 2.1  | 3    | 3.9  | %    |

| T <sub>PU</sub>    | Power up to Stable Output <sup>[5]</sup>    | All output clocks                  | -    | -    | 3    | ms   |

| $T_{DC}$           | CLKOUT Duty Cycle <sup>[5]</sup>            | CL = 15pF                          | 45   | 50   | 55   | %    |

| T <sub>CCJ</sub>   | REFOUT Cycle to Cycle jitter <sup>[5]</sup> | CL = 15pF                          | _    | 110  | 200  | ps   |

| T <sub>CCJ</sub>   | CLKOUT Cycle to Cycle jitter <sup>[5]</sup> | CL = 15pF                          | _    | 110  | 200  | ps   |

| Fmod               | Frequency Modulation Rate                   | SSON# = GND Internally pulled down | _    | 31   | _    | kHz  |

| Matan              |                                             |                                    |      |      |      | •    |

- SSSEL has internal pull-up and SSON has pull-down resistors.

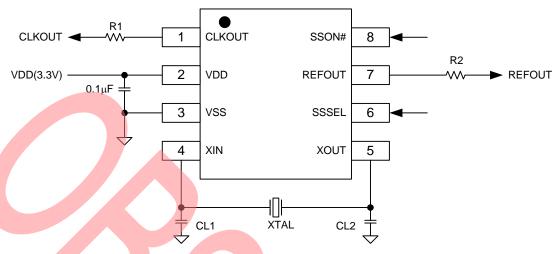

In applications if a crystal is used for the input reference clock, refer to crystal manufacturer's specifications for the required crystal load capacitor value.

Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with fully loaded outputs. All outputs loaded with 15 pF.

Measured between 0.2\*VDD and 0.8\*VDD Volts.

Triggering is done at 1.5V VDDC.

## **Application Schematic**

Figure 3. Application Schematic

Use crystal or cera-lock filter manufacturer's recommended values for CL1 and CL2 load capacitors, 0.1- $\mu$ F bypass capacitor for power pins should always be used and placed close to their V<sub>DD</sub> pin. R1 and R2 are series termination resistors for impedance matching.

## **Ordering Information**

| Part Number   | P   | Package Type |  | Production Flow |

|---------------|-----|--------------|--|-----------------|

| CY25901SXC-1  | TBD |              |  | TBD             |

| CY25901SXC-1T | TBD |              |  | TBD             |

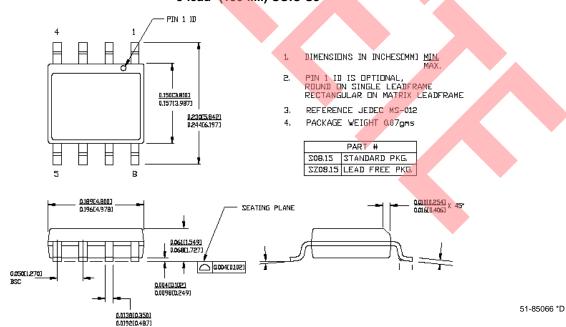

### **Package Drawing and Dimensions**

## 8-lead (150-Mil) SOIC S8

All product and company names mentioned in this document are the trademarks of their respective holders.

# **Document History Page**

| Document Title: CY25901 Spread Spectrum Clock Generator Document Number: 38-07521 |         |          |     |                       |  |  |

|-----------------------------------------------------------------------------------|---------|----------|-----|-----------------------|--|--|

| REV. ECN NO. Issue Date Orig. of Change Description of Change                     |         |          |     | Description of Change |  |  |

| **                                                                                | 124075  | 02/19/03 | RGL | New Datasheet         |  |  |

| *A                                                                                | 2939214 | 05/28/10 | CXQ | Obsolete document.    |  |  |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Cypress Semiconductor:

CY25901SXC-1 CY25901SXC-1T