# MoBL-USB™ TX2UL USB 2.0 ULPI Transceiver

#### **Features**

The Cypress MoBL-USB™ TX2UL is a low voltage high speed (HS) USB 2.0 UTMI+ Low Pin Interface (ULPI) Transceiver. The TX2UL is specifically designed for mobile handset applications by offering tiny package options and low power consumption.

- USB 2.0 Full Speed and High Speed compliant transceiver

- Multi range (1.8 V to 3.3 V) I/O voltages

- Fully compliant ULPI link interface

- 8-bit SDR ULPI data path

- UTMI+ level 0 support

- Support USB device mode only

- Integrated oscillator

- Integrated phase locked loop (PLL) 13, 19.2, 24, or 26 MHz reference

- Integrated USB pull-up and termination resistors

- 3.0 V to 5.775 V VBATT input

- Chip select pin

- Single ended device RESET input

- UART pass through mode

- ESD compliance:

- $\hfill \mbox{\for JESD22-A114D 8 kV Contact human body model (HBM) for DP, DM, and <math display="inline">\hfill \mbox{\for V}_{SS}$  pins

- □ IEC61000 4-2 8 kV contact discharge

- □ IEC61000 4-2 15 kV air discharge

- Support for industrial temperature range: (-40 °C to 85 °C)

- Low power consumption for mobile applications:

- □ 5 µA nominal sleep mode

- □ 30 mA nominal active HS transfer

- Small package for mobile applications:

□ 2.14 x 1.76 mm 20-pin WLCSP 0.4 mm pitch

□ 4 x 4 mm 24-pin QFN

### **Applications**

- Mobile phones

- PDAs

- Portable media players (PMPs)

- DTV applications

- Portable GPS units

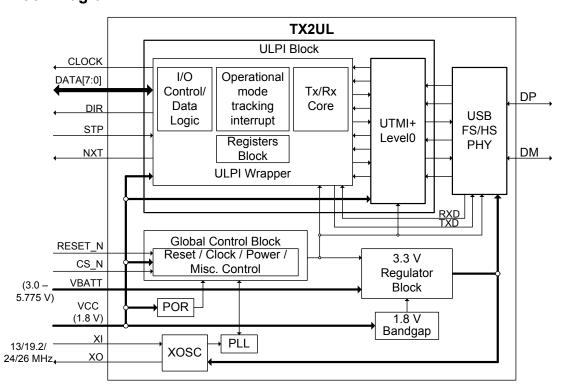

# **TX2UL Block Diagram**

# Contents

| Functional Overview                            | 3    |

|------------------------------------------------|------|

| UTMI+ Low Pin Interface (ULPI)                 | 3    |

| Oscillator (OSC)                               |      |

| Phase Locked Loop (PLL)                        | 3    |

| Power On Reset (POR)                           |      |

| Reset (RESET N)                                |      |

| DP and DM pins                                 | 3    |

| Chip Select (CS_N)                             |      |

| USB2 Transceiver Macrocell Interface (UTMI+)   |      |

| Global Control                                 |      |

| Full Speed and                                 |      |

| High Speed USB Transceivers (FS/HS)            | 3    |

| USB Pull up and Intr Detect,                   |      |

| Termination Resistors (Pull up/TERM)           | 3    |

| UART Pass Through Mode                         |      |

| Clocking                                       |      |

| Power Domains                                  |      |

| Operation Modes                                | 5    |

| VID and PID                                    |      |

| Pinouts                                        | 7    |

| Synchronous Operation Modes                    | 9    |

| ULPI Transmit Command Byte (TX CMD)            | 9    |

| ULPI Receive Command Byte (RX CMD)             |      |

| USB Data Transmit (NOPID)                      |      |

| USB Data Transmit (PID)                        | . 11 |

| USB Packet Receive                             | .11  |

| Immediate Register Read and Write              | . 12 |

| Immediate Register Read and Write              |      |

| Aborted by USB Receive                         | . 13 |

| Back to Back Immediate Register Read and Write |      |

| and USB Receive                                | . 14 |

| Configuration Mode                       | 16 |

|------------------------------------------|----|

| Configuration Mode in 20-Pin CSP package | 16 |

| Configuration Mode in 24-Pin QFN package |    |

| Power On Reset (POR)                     |    |

| Register                                 | 16 |

| Register Map                             | 16 |

| Immediate Register Set                   | 17 |

| Function Control Register                | 17 |

| Interface Control Register               | 18 |

| Debug Register                           | 18 |

| Scratch Register                         | 18 |

| Carkit Control Register                  | 18 |

| Drive Strength and                       |    |

| Slew Rate Configuration Register         | 19 |

| USB Interface Control Register           |    |

| Absolute Maximum Ratings                 | 20 |

| Operating Conditions                     | 20 |

| DC Characteristics                       |    |

| AC Characteristics                       |    |

| Ordering Information                     |    |

| Ordering Code Definitions                |    |

| Package Diagram                          |    |

| Acronyms                                 |    |

| Document Conventions                     |    |

| Document History Page                    |    |

| Sales, Solutions, and Legal Information  |    |

| Worldwide Sales and Design Support       |    |

| Products                                 |    |

| PSoC® Solutions                          |    |

| Cypress Developer Community              |    |

| Technical Support                        | 30 |

#### Functional Overview

#### **UTMI+ Low Pin Interface (ULPI)**

This block conforms to the ULPI specification. It supports the 8-bit wide SDR data path. The primary I/Os of this block support multi-range LVCMOS signaling from 1.8 V to 3.3 V ( $\pm 5\%$ ). The level used is automatically selected by the voltage applied to V<sub>CCIO</sub> and is set at any voltage between 1.8 V and 3.3 V.

#### Oscillator (OSC)

This block meets the requirements of both the on-chip PLL and the USB-IF requirements for clock parameters. It is a fundamental mode parallel resonant oscillator with a maximum ESR of  $60~\Omega$ . It supports the following:

- Integrated Crystal Oscillator 13, 19.2, 24, or 26 MHz crystal

- 13, 19.2, 24, or 26 MHz LVCMOS single ended input clock on XI

#### Phase Locked Loop (PLL)

The PLL meets all clock stability requirements imposed by this device and the USB standard. It supports all requirements to make the device compliant to the USB 2.0 specifications. It also has a fractional multiplier that enables it to supply the correct frequency to the device when it is presented with a 13, 19.2, 24, or 26 MHz reference clock.

#### Power On Reset (POR)

This block provides a POR signal (internal) based on the input supply. An internal POR is generated when  $V_{CC}$  input rises above VPOR(trip).

#### Reset (RESET\_N)

The three major functions of RESET\_N pin are as follows:

- Reset TX2UL

- Place TX2UL into Sleep Mode

- Place TX2UL into Configuration Mode

When the RESET\_N pin is asserted (low) for tSTATE (tSTATE is specified in Table 21 on page 21), the TX2UL enters either Sleep Mode or Configuration Mode depending on the CS\_N state. When RESET\_N is asserted while CS\_N is asserted, TX2UL enters Sleep Mode. When RESET\_N is asserted for tSTATE while CS\_N is deasserted, TX2UL enters Configuration Mode. In these modes, all the pins in the ULPI interface are tristated. If the RESET\_N pin is not used, it must be pulled high. For information about different modes of configuration, see Table 5 on page 5.

#### **DP and DM pins**

The DP and DM pins are the differential pins for the USB. They must be connected to the corresponding DP and DM pins of the USB receptacle.

#### Chip Select (CS\_N)

This signal pin is available only in 24-pin QFN package. The two major functions of CS N are as follows:

- Tristate the ULPI bus output pins

- Associate with RESET\_N to place TX2UL in the Sleep mode When the CS\_N pin is deasserted (high), all the pins in the ULPI interface are tristated.

#### **USB2** Transceiver Macrocell Interface (UTMI+)

This block conforms to the UTMI+ Level 0 standard. It performs all the UTMI to USB translation.

#### **Global Control**

This block is the digital control logic that ties the blocks of the device together. Its functions include pull up control, over current protect control, and more.

#### Full Speed and High Speed USB Transceivers (FS/HS)

The FS and HS Transceivers comply fully with the USB 2.0 specifications.

# USB Pull up and Intr Detect, Termination Resistors (Pull up/TERM)

These blocks contain the USB pull-up and termination resistors as specified by the USB 2.0 specification.

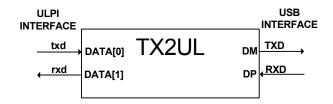

#### **UART Pass Through Mode**

TX2UL supports Carkit UART Pass Through Mode. When the Carkit Mode bit in the Interface Control register is set, it enables the Link to communicate through the DP/DM to a remote system using UART signaling. By default, the clock is powered down when the TX2UL enters Carkit Mode. Entering and exiting the Carkit Mode is identical to the Serial Mode. Table 1, Table 2, and Figure 1 show the UART Signal Mapping between the DP/DM and DATA[1:0] at ULPI interface.

Table 1. UART Signal Mapping at ULPI Interface

| Signal   | Maps to   | Direction | Description                      |

|----------|-----------|-----------|----------------------------------|

| txd      | DATA[0]   | IN        | UART TXD signal routed to DM pin |

| rxd      | DATA[1]   | OUT       | UART RXD signal routed to DP pin |

| Reserved | DATA[7:2] | -         | Reserved                         |

Table 2. UART Signal Mapping at USB Interface

| Signal | Maps to | Direction | Description     |

|--------|---------|-----------|-----------------|

| TXD    | DM      | OUT       | UART TXD signal |

| RXD    | DP      | INT       | UART RXD signal |

Figure 1. UART Signal Mapping in Pass Through Mode

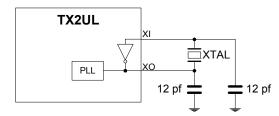

#### Clocking

TX2UL supports external crystal and clock inputs at the 13, 19.2, 24, and 26 MHz frequencies. The internal PLL applies the proper clock multiply option depending on the input frequency. For applications that use an external clock source to drive XI, the XO pin (in the 24-pin QFN package) is left floating. TX2UL has an on-chip oscillator circuit that uses an external 13, 19.2, 24, or 26 MHz (±100 ppm) crystal with the following characteristics:

- Parallel resonant

- Fundamental mode

- 750 µW drive level

- 12 pF (5 percent tolerance) load capacitors

- 150 ppm

TX2UL operates on one of two primary clock sources:

- LVCMOS square wave clock input driven on the XI pin

- Crystal generated sine wave clock on the XI and XO pins

The selection between input clock source and frequency on the XI pin is determined by the *Chip Configuration* register loaded through the RESET\_N during Configuration Mode. The external clock source requirements are shown in Figure 3 on page 5.

Figure 2. Crystal Configuration

\* 12 pF capacitor values assumes a trace capacitance of 3 pF per side on a four layer FR4 PCA

**Table 3. External Clock Requirements**

| Parameter | Description                                  | Speci | ification | Unit    |

|-----------|----------------------------------------------|-------|-----------|---------|

|           | Description                                  | Min   | Max       | - Ollit |

| Vn        | Supply voltage noise at frequencies < 50 MHz | _     | 20        | mV p-p  |

| PN_100    | Input phase noise at 100 Hz                  | _     | 75        | dBc/Hz  |

| PN_1k     | Input phase noise at 1 kHz offset            | _     | 104       | dBc/Hz  |

| PN_10k    | Input phase noise at 10 kHz offset           | _     | 120       | dBc/Hz  |

| PN_100k   | Input phase noise at 100 kHz offset          | _     | 128       | dBc/Hz  |

| PN_1M     | Input phase noise at 1 MHz offset            | _     | 130       | dBc/Hz  |

|           | Duty cycle                                   | 30    | 70        | %       |

|           | Maximum frequency deviation                  | _     | 150       | ppm     |

#### **Power Domains**

The TX2UL has three power supply domains:

- V<sub>CC</sub>

- V<sub>IO</sub>

- $\blacksquare V_{BATT}$

TX2UL has two grounds:

- V<sub>SS</sub>

- V<sub>SSBATT</sub>

$V_{CC}$

This is the core 1.8 V power supply for the TX2UL. It can range anywhere from 1.7 V to 1.9 V during actual operation.

$V_{IO}$

This is the 1.8 V to 3.3 V multi range supply to the I/O ring. It can range anywhere from 1.7 V to 3.6 V during actual operation.

#### $V_{BATT}$

This is the battery input supply that powers the 3.3 V regulator block. It can range anywhere from 3.0 to 5.775 V during actual operation.

#### Voltage Regulator

The internal 3.3 V regulator block regulates the VBATT supply to the internal 3.3 V supply for the USBIO and XOSC blocks. If the supply voltage at VBATT is below 3.3 V, the regulator block switches the VBATT supply directly for the USBIO and XOSC blocks.

#### Power Supply Sequence

TX2UL does not require a power supply sequence. All power supplies are independently sequenced without damaging the part. All supplies are up and stable for the device to function properly. The analog block contains circuitry that senses the power supply to determine when all supplies are valid.

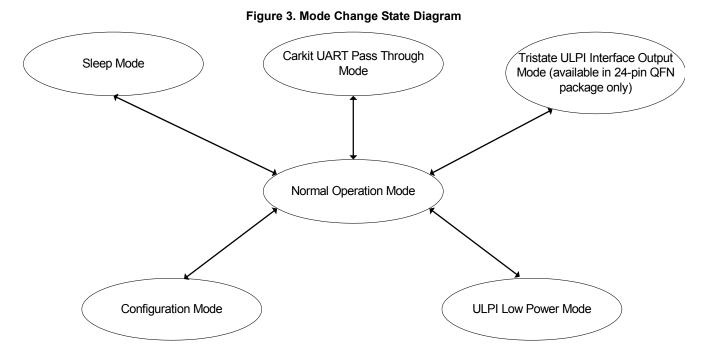

#### **Operation Modes**

There are six operation modes available in TX2UL. They are:

- Normal operation mode

- Configuration mode

- ULPI low power mode

- Sleep mode

- Carkit UART pass through mode

- Tristate ULPI interface output mode (only available in 24-pin QFN package)

When changing the operation modes, if the current and changing modes are not the normal operation Mode, TX2UL first changes to the normal operation mode. For example, to change from

ULPI low power mode to Sleep mode, TX2UL changes to normal operation mode first, and then to Sleep mode. The Mode Change State diagram in Figure 3 shows the mode change path of TX2UL. The entries of the six operations modes (20-pin CSP package has five operation modes) are listed in Table 4 and Table 5. There are three mode change transactions that require the RESET\_N assert or deassert with tSTATE (see Table 21 on page 21 for tSTATE). The three mode change transactions are:

- Change from normal operation mode to configuration mode; RESET N is required to assert with tSTATE

- Change from configuration mode to normal operation mode; RESET\_N is required to de-assert with tSTATE

- Change from normal operation mode to sleep mode; RESET\_N is required to assert with tSTATE

Table 4. TX2UL 20-Pin CPS Package Operation Modes

| RESET_N                                 | Mode                                                                                                                                                |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (Low)                                 | Sleep mode                                                                                                                                          |

| 1 (High)                                | Normal operation mode                                                                                                                               |

| 1 (High)                                | Enter into ULPI low power mode by setting SuspendM register bit (in Function Control Register) to 0 during the normal operation mode.               |

| 1 (High)                                | Enter into Carkit UART pass through mode by setting Carkit mode register bit (in Interface Control Register) to 1 during the normal operation mode. |

| 0 (Low)<br>when<br>Power On<br>(VCC On) | Enter into Configuration Mode                                                                                                                       |

Table 5. TX2UL 24-Pin QFN Package Operation Modes

| CS_N     | RESET_N  | Mode                                                                                                                                                |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (Low)  | 0 (Low)  | Sleep mode                                                                                                                                          |

| 0 (Low)  | 1 (High) | Normal operation mode                                                                                                                               |

| 0 (Low)  | 1 (High) | Enter into ULPI low power mode by setting SuspendM register bit (in Function Control Register) to 0 during the normal operation mode.               |

| 0 (Low)  | 1 (High) | Enter into Carkit UART pass through mode by setting Carkit Mode register bit (in Interface Control Register) to 1 during the normal operation mode. |

| 1 (High) | 0 (Low)  | Configuration mode                                                                                                                                  |

| 1 (High) | 1 (High) | Tristate ULPI interface output pins                                                                                                                 |

The operation and configuration modes are described in the sections Operation Modes on page 5 and Configuration Mode on page 16 respectively. The ULPI low power mode and Sleep mode are described in the following sections.

#### ULPI Low Power Mode

In this mode, the link optionally places the TX2UL in low power mode when the USB is suspended. TX2UL powers down all the circuitry except for the interface pins and full speed receiver. To enter low power mode, the link must set SuspendM in the Function Control register to 0b. The TX2UL clock is stopped for a minimum of five cycles after TX2UL accepts the register write. To exit low power mode, the link signals TX2UL to exit the mode by asynchronously asserting a signal, STP. The TX2UL wakes up its internal circuitry and when it meets the ULPI timing requirements, it deasserts DIR. The SuspendM register is set to 1b.

#### Sleep Mode

Sleep mode is entered by asserting RESET\_N during the Normal Operation Mode. When RESET\_N is driven low for tSTATE (see

Table 21 on page 21 for tSTATE requirement) while CS\_N is low, TX2UL enters Sleep Mode. VCC must remain supplied (ON) during the sleep mode. This mode powers down all internal circuitry except the RESET\_N pin and the chip\_config register. The ULPI interface bus is tristated.

During the Sleep Mode ensure that:

- The ULPI interface I/Os are either floating or driven high by the link

- DP and DM are either floating or pull to 0 V

- Deassert RESET N to exit the Sleep Mode

#### VID and PID

The VID and PID are hard coded into Product ID and Vendor ID registers (read only) as shown in Table 6.

Table 6. Immediate Register Values for VID and PID

| Field Name            | Size (bit) | Address (6 bits) |    |     |     | Value |

|-----------------------|------------|------------------|----|-----|-----|-------|

| rieiu Name            | Size (bit) | Rd               | Wr | Set | Clr | value |

| Vendor ID (VID) Low   | 8          | 00h              | -  | -   | -   | B4h   |

| Vendor ID (VID) High  | 8          | 01h              | -  | -   | -   | 04h   |

| Product ID (PID) Low  | 8          | 02h              | -  | -   | -   | 03h   |

| Product ID (PID) High | 8          | 03h              | -  | -   | -   | 68h   |

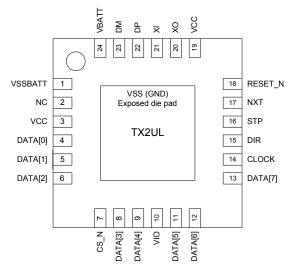

#### **Pinouts**

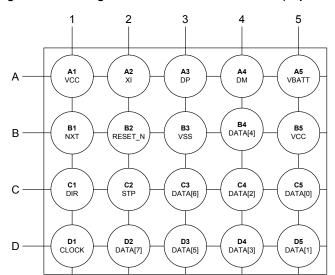

TX2UL is available in 20-ball WLCSP and 24-pin QFN package. The pin assignment is shown in Figure 4 and Figure 5

Figure 4. Pin Assignment - TX2UL 20-Ball WLCSP (Top View)

Table 7. Pin Definitions - TX2UL 20-Ball WLCSP

| Name                  | Ball No. | Туре  | Voltage       | Description                                                                                                                                                                                             |  |

|-----------------------|----------|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>ULPI Link Inte</b> | rface    |       |               |                                                                                                                                                                                                         |  |

| DATA[0]               | C5       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| DATA[1]               | D5       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| DATA[2]               | C4       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| DATA[3]               | D4       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| DATA[4]               | B4       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| DATA[5]               | D3       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| DATA[6]               | C3       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| DATA[7]               | D2       | I/O   | 1.8 V         | ULPI data to/from link                                                                                                                                                                                  |  |

| CLOCK                 | D1       | 0     | 1.8 V         | ULPI clock                                                                                                                                                                                              |  |

| NXT                   | B1       | 0     | 1.8 V         | ULPI next signal                                                                                                                                                                                        |  |

| STP                   | C2       | Ι     | 1.8 V         | ULPI stop signal                                                                                                                                                                                        |  |

| DIR                   | C1       | 0     | 1.8 V         | ULPI direction                                                                                                                                                                                          |  |

| USB                   |          |       |               |                                                                                                                                                                                                         |  |

| DP                    | A3       | I/O   | USB           | USB D-plus signal                                                                                                                                                                                       |  |

| DM                    | A4       | I/O   | USB           | USB D-minus signal                                                                                                                                                                                      |  |

| Miscellaneous         | 3        | •     |               |                                                                                                                                                                                                         |  |

| RESET_N               | B2       | I     | 1.8 V         | Global reset. When RESET_N is asserted during the VCC power on, TX2UL enters configuration mode. During normal operation mode, asserting RESET_N resets the TX2UL and enter into the power saving mode. |  |

| XI                    | A2       | ı     | 1.8 V         | LVCMOS single ended clock of frequency 13, 19.2, 24, or 26 MHz                                                                                                                                          |  |

| POWER and G           | ROUND    |       |               |                                                                                                                                                                                                         |  |

| VCC                   | B5, A1   | Power | 1.8 V         | Low voltage supply for the digital core and I/O                                                                                                                                                         |  |

| VBATT                 | A5       | Power | 3.0 - 5.775 V | High voltage supply for USB                                                                                                                                                                             |  |

| VSS                   | В3       | GND   | 0 V           | Common ground                                                                                                                                                                                           |  |

Document Number: 001-15775 Rev. \*N

Figure 5. Pin Assignment - TX2UL 24-Pin QFN (Top View)

Table 8. Pin Definitions - TX2UL 24-Pin QFN

| Pin No.    | Type                                                  | Voltage                               | Description                                                                                                  |

|------------|-------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------|

|            | 1300                                                  | Tollago                               | Doodipaon                                                                                                    |

|            | I/O                                                   | 18-33V                                | ULPI data to/from link                                                                                       |

| · ·        |                                                       |                                       | ULPI data to/from link                                                                                       |

|            |                                                       |                                       | ULPI data to/from link                                                                                       |

|            |                                                       |                                       | ULPI data to/from link                                                                                       |

| _          |                                                       |                                       | ULPI data to/from link                                                                                       |

|            |                                                       |                                       | ULPI data to/from link                                                                                       |

|            |                                                       |                                       | ULPI data to/from link                                                                                       |

| 13         | I/O                                                   |                                       | ULPI data to/from link                                                                                       |

| 14         | 0                                                     |                                       | ULPI clock                                                                                                   |

| 17         |                                                       |                                       | ULPI next signal                                                                                             |

| 16         | 1                                                     | 1.8 - 3.3 V                           | ULPI stop signal                                                                                             |

| 15         | 0                                                     | 1.8 - 3.3 V                           | ULPI direction                                                                                               |

|            |                                                       |                                       |                                                                                                              |

| 22         | I/O                                                   | USB                                   | USB D-plus signal                                                                                            |

| 23         | I/O                                                   | USB                                   | USB D-minus signal                                                                                           |

|            |                                                       |                                       |                                                                                                              |

| 7          | l                                                     | 1.8 - 3.3 V                           | When CS_N is de-asserted, all pins at ULPI interface are tristated                                           |

| 18         | I                                                     | 1.8 - 3.3 V                           | Device chip global reset. When RESET_N is asserted, TX2UL is in reset and enters into the power saving mode. |

| 21         | I                                                     | 1.8 V                                 | Crystal or LVCMOS single ended clock of frequency 13, 19.2, 24, or 26 MHz                                    |

| 20         | 0                                                     | 1.8 - 3.3 V                           | Crystal                                                                                                      |

| 2          | -                                                     | -                                     | No connect                                                                                                   |

| d GROUND   |                                                       | I                                     |                                                                                                              |

| 3, 19      | Power                                                 | 1.8 V                                 | Low voltage supply for the digital core                                                                      |

| 10         | Power                                                 | 1.8 - 3.3 V                           | Power for multi-range I/Os                                                                                   |

| 24         | Power                                                 | 3.0 - 5.775 V                         | High voltage supply for USB                                                                                  |

| 1          | GND                                                   | 0                                     | USB ground                                                                                                   |

| Die Paddle | GND                                                   | 0                                     | Digital ground (core and I/O)                                                                                |

|            | 14 17 16 15 22 23 7 18 21 20 2 d GROUND 3, 19 10 24 1 | 1   1   1   1   1   1   1   1   1   1 | 1                                                                                                            |

# Synchronous Operation Modes

This section describes the synchronous mode of TX2UL ULPI interface protocol.

#### **ULPI Transmit Command Byte (TX CMD)**

The Link initiates transfers to TX2UL by sending the Transmit Command Byte as shown in Table 9. TX CMD byte consists of a 2-bit command code and a 6-bit payload.

Table 9. Transmit Command (TX CMD) Byte Format

| Byte Name | Command Code Data (7:6) | Command P | Payload Data (5:0) | Command Description                                                                                                                                     |

|-----------|-------------------------|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special   | 00b                     | 000000b   | (NOOP)             | No operation. 00h is the idle value of the data bus. The Link drives NOOP by default.                                                                   |

|           |                         | XXXXXXb   | (RSVD)             | Reserved command space. Values other than those mentioned give undefined behavior.                                                                      |

| Transmit  | 01b                     | 000000b   | (NOPID)            | Transmit USB data that does not have a PID, such as chirp and resume signalling. The TX2UL starts transmitting on the USB beginning with the next byte. |

|           |                         | 00XXXXb   | (PID)              | Transmit USB packet. data (3:0) indicates USB packet identifier PID (3:0)                                                                               |

|           |                         | XXXXXXb   | (RSVD)             | Reserved Command space. Values other than those mentioned give undefined behavior.                                                                      |

| RegWrite  | 10b                     | 101111b   | (EXTW)             | Extended register write command. 8-bit address available in the next cycle.                                                                             |

|           |                         | XXXXXXb   | (REGW)             | Register write command with 6-bit immediate address.                                                                                                    |

| RegRead   | 11b                     | 101111b   | (EXTR)             | Extended register read command. 8-bit address available in the next cycle.                                                                              |

|           |                         | XXXXXXb   | (REGR)             | Register read command with 6-bit immediate address.                                                                                                     |

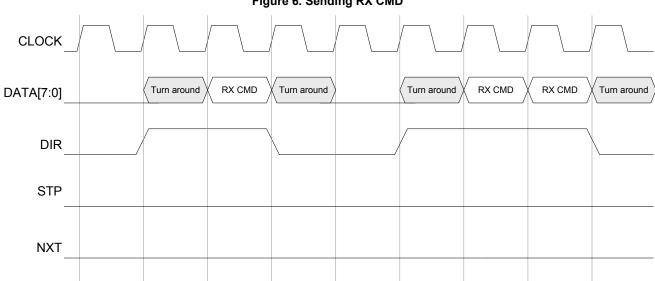

#### **ULPI Receive Command Byte (RX CMD)**

The Receive Command Byte, as shown in Table 10, is sent by TX2UL to update the link with LineState and USB receive information. The USB receive information includes LineState, RxActive, and RxError. After a USB transmit, TX2UL sends RX CMD with LineState indicating EOP to the link. For High Speed, EOP is the squelch to squelch transition on LineState. Figure 7 on page 10 shows how TX2UL sends RX CMD information to the link. The first packet shows a single RX CMD. If back to back changes are detected, TX2UL keeps DIR asserted and sends back to back RX CMDs as shown in the second packet.

Table 10. Receive Command (RX CMD) Byte Format

| Data | Name      | Description and Value                                                         |                |   |  |  |

|------|-----------|-------------------------------------------------------------------------------|----------------|---|--|--|

| 1:0  | LineState | ULPI LineState signals.<br>DATA[0] = LineState (0)<br>DATA[1] = LineState (1) |                |   |  |  |

| 3:2  | Reserved  |                                                                               |                |   |  |  |

| 5:4  | RxEvent   | Encoded UTMI event signa                                                      |                |   |  |  |

|      |           | Value                                                                         | Value RxActive |   |  |  |

|      |           | 00                                                                            | 0              | 0 |  |  |

|      |           | 01                                                                            | 1              | 0 |  |  |

|      |           | 11                                                                            | 1              | 1 |  |  |

|      |           | 10                                                                            | X              | X |  |  |

| 7:6  | Reserved  |                                                                               | -1             | 1 |  |  |

Document Number: 001-15775 Rev. \*N Page 9 of 30

Figure 6. Sending RX CMD

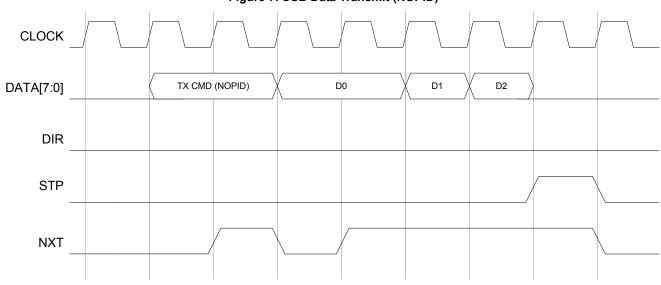

#### **USB Data Transmit (NOPID)**

In this mode, the Link transmits data on the USB without a Packet Identifier (PID) by sending a TX CMD byte of the NOPID type. TX2UL asserts NXT (see Figure 8 on page 11) in the first cycle of TX CMD and deasserts NXT when it detects STP to be high. Because this command does not contain PID data, TX2UL waits for the next data byte before beginning transmission on the USB. When the last byte is transferred by the TX2UL, the link asserts STP for one cycle and drives data to 00h if no transmit errors occur. The link does not assert STP before the first byte is transferred by the TX2UL.

Figure 7. USB Data Transmit (NOPID)

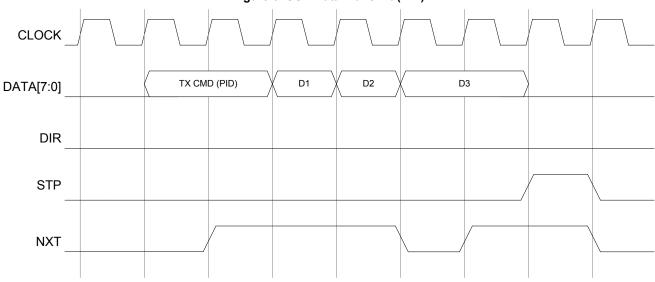

#### **USB Data Transmit (PID)**

In this mode, the link transmits data on the USB with a PID. The link first drives a TX CMD byte as illustrated in Figure 9 on page 11 to transmit a USB packet. The link sets the Command Code to 01b (Transmit) and places the USB Packet Identifier (PID) on DATA[3:0] (see Table 9 on page 9). TX2UL throttles the data using NXT such that the link provides the next byte in the cycle after NXT is detected as high.

Figure 8. USB Data Transmit (PID)

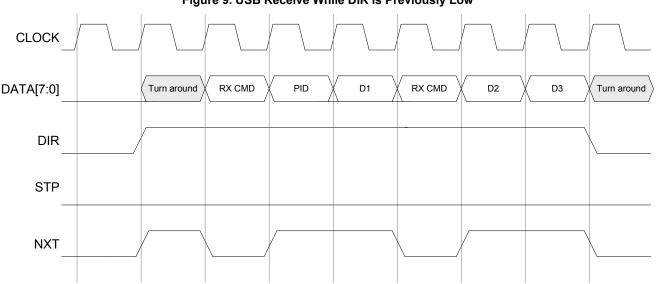

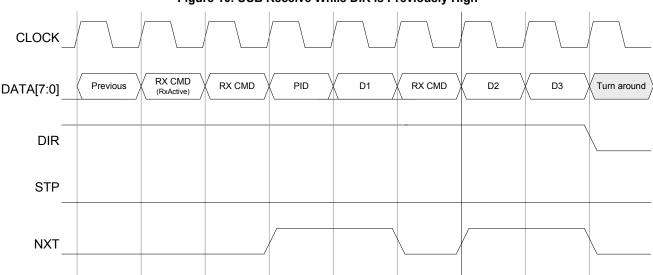

#### **USB Packet Receive**

As shown in Figure 10 on page 12, when TX2UL receives the USB data it gains ownership of the data bus by asserting DIR. The DIR is previously either high or low. If DIR is low (see Figure 9), TX2UL asserts both DIR and NXT so that the link knows immediately that this is a USB receive packet. If DIR is high (see Figure 10 on page 12), TX2UL deasserts NXT and drives an RX CMD with the RxEvent field set to the RxActive state. The TX2UL starts driving data in the following cycle or outputs RX CMD until USB data is available. Valid USB packet data is presented to the link by asserting NXT and placing a byte on the bus. When NXT is low, TX2UL drives the RX CMD byte. All RX CMD changes during the USB packet receive are signaled when NXT is low. If NXT is never low during the packet receive, all RX CMD changes are replaced with a single RX CMD update. This update is sent at the end of the USB packet receive, when the ULPI bus is available. The RX CMD update always conveys the current RX CMD values and not the previous one.

Figure 9. USB Receive While DIR is Previously Low

Document Number: 001-15775 Rev. \*N

Figure 10. USB Receive While DIR is Previously High

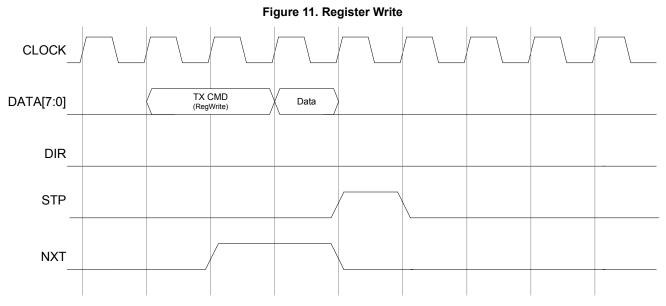

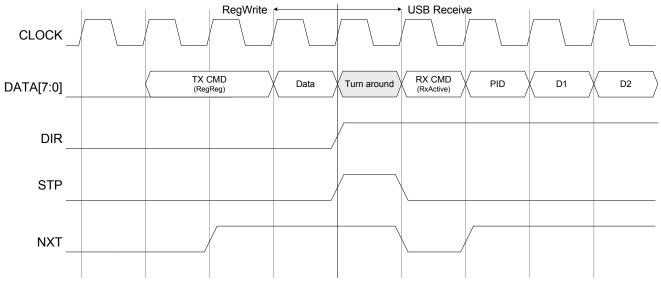

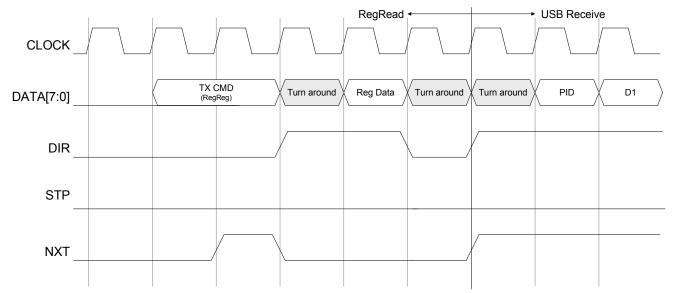

#### Immediate Register Read and Write

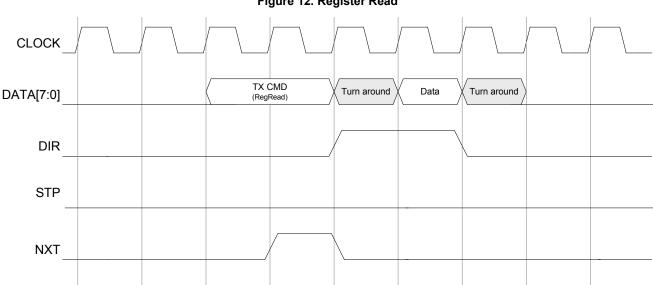

An immediate register is accessed by sending the TX CMD byte first (see Figure 11 and Figure 12 on page 13). This byte is sent as a regread or regwrite command, depending on the intended operation.

For a register write (see Figure 11), the link first sends a register write TX CMD byte and waits for NXT to assert. After NXT asserts, the link sends the register write data and waits for NXT to assert again. After the second assertion is detected, the link asserts STP in the following cycle to complete the operation. The TX2UL detects this STP assertion before it can accept another transmit command. If the TX2UL aborts rewrite by asserting DIR, the link repeats the entire process again when the bus is idle.

For a register read (see Figure 12 on page 13), the link sends a register read command and waits for NXT to assert. In the cycle after NXT asserts, the TX2UL asserts DIR to gain control of the data bus. In the cycle, after DIR asserts the TX2UL returns the register read data. The TX2UL does not assert NXT when DIR is asserted during the register read operation, even during the cycle when the register read data is returned. If the TX2UL aborts the regread by asserting DIR earlier than shown in Figure 12 on page 13, the link retries the regread when the bus is idle.

Document Number: 001-15775 Rev. \*N

#### Figure 12. Register Read

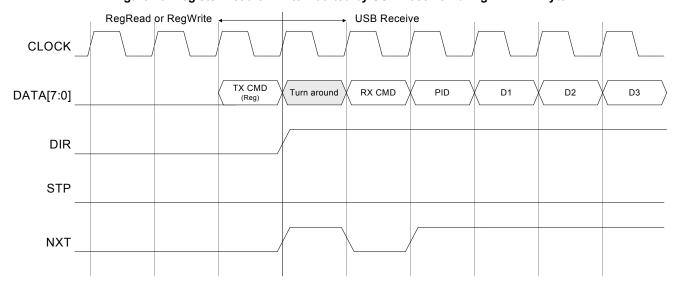

### Immediate Register Read and Write Aborted by USB Receive

A register read is the only instance where ULPI does not use NXT to acquire data. The NXT signal is asserted only during USB receive to distinguish this type of receive from other types of data transfers.

Register read and write operations are aborted when the TX2UL sends a RX CMD, except during the cycle where register read data is returned to the link.

TX2UL asserts both DIR and NXT whenever a register read or write is aborted by a USB receive during the initial transmit command byte or in the same cycle that the register read data returned to the link.

Figure 13. Register Read or Write Aborted by USB Receive During TX CMD Byte

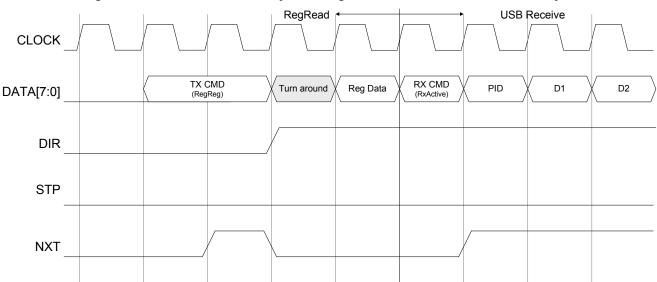

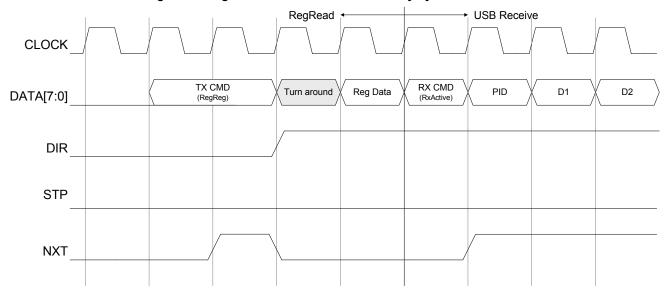

#### Back to Back Immediate Register Read and Write and USB Receive

When a USB receive occurs in the same cycle that the register read data is returned to the link, the TX2UL first returns the register read data, not a RX CMD byte (see Figure 14).

When a USB receive occurs in the cycle immediately after a register read completes, the TX2UL places the USB receive data back-to-back with the register read (see Figure 15). The link accepts back-to-back packets where DIR does not deassert between packets. If DIR asserts during the same cycle that STP is asserted at the end of a register write, then the TX2UL considers the register write to have successfully executed (see Figure 16 on page 15).

When a USB receive starts in the cycle after the register read data is returned to the link, it results in two cycles of bus turnaround when DIR deasserts for a single cycle (see Figure 17 on page 15).

Figure 14. USB Receive in Same Cycle as Register Read Data. USB Receive is Delayed

Figure 16. Register Write Followed Immediately by a USB Receive During STP Assertion

Figure 17. Register Read Followed by a USB Receive

### **Configuration Mode**

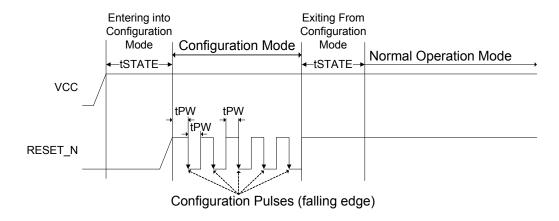

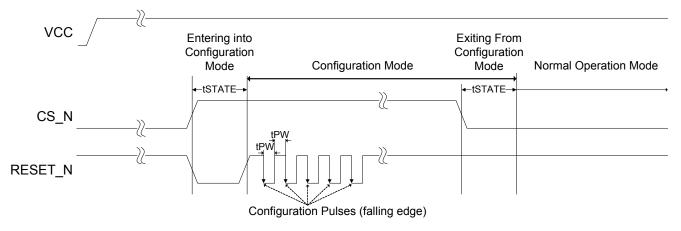

TX2UL is configured in the input clock type and frequency for the XI and XO in Configuration Mode. The 20-pin CSP package and the 24-pin QFN package have different procedures to enter configuration mode.

#### Configuration Mode in 20-Pin CSP package

To enter configuration mode, keep the RESET\_N low during  $V_{CC}$  Power On for tSTATE (see Figure 19 on page 22 for the timing diagraming and Table 21 on page 21 for the tSTATE timing requirement). When TX2UL enters configuration mode, the peripheral controller (link device) generates the pulses (falling edge) at the RESET\_N pin to configure TX2UL. TX2UL configures its internal oscillator base on number of received pulses at the RESET\_N pin. When the configuration is completed, deassert RESET\_N (high) for tSTATE to exit the Configuration. If the TX2UL needs to enter the Configuration Mode again, it must go through the following power cycle:  $V_{CC}$  Off  $\Re \rightarrow RESET_N$  Low  $\Re \rightarrow V_{CC}$  On.

#### Configuration Mode in 24-Pin QFN package

To enter configuration mode keep the RESET\_N pin pulled low for tSTATE (see Figure 20 on page 22 for the timing diagraming and Table 21 on page 21 for the tSTATE timing requirement) while deasserting CS\_N (high). When TX2UL enters configuration mode, the peripheral controller (link device) generates the pulses (falling edge) at the RESET\_N pin to configure TX2UL. TX2UL configures its internal oscillator base on number of received pulses at the RESET\_N pin. When the configuration is completed, assert the CS\_N (low) for tSTATE (see Figure 21 on page 21 for the timing) to exit the configuration mode. Figure 19 on page 22 shows the timing diagram of entering and exiting configuration mode. The configuration options are listed in

Table 11. The TX2UL is defaulted to 26 MHz with single end clock input (to XI).

Table 11. TX2UL Configuration Options

| Number of Pulses at<br>RESET_N Pin during<br>Configuration Mode | Configuration Description          |

|-----------------------------------------------------------------|------------------------------------|

| 0 pulses                                                        | 26 MHz clock input on XI (default) |

| 1 pulses                                                        | 19.2 MHz clock input on XI         |

| 2 pulses                                                        | 24.0 MHz clock input on XI         |

| 3 pulses                                                        | 13.0 MHz clock input on XI         |

| 4 pulses                                                        | 26 MHz crystal on XI/XO            |

| 5 pulses                                                        | 19.2 MHz crystal on XI/XO          |

| 6 pulses                                                        | 24.0 MHz crystal on XI/XO          |

| 7 pulses                                                        | 13.0 MHz crystal on XI/XO          |

#### Power On Reset (POR)

TX2UL has an internal power on reset (POR) block that provides power on reset and power management control functionality. This POR function complies with all the parameters required by the ULPI specification.

#### Register

TX2UL provides an immediate register set that is defined by the ULPI specification for control and configuration functions.

#### **Register Map**

The ULPI specifications define an immediate register set with a 6-bit address that forms a part of the transmit command byte, as shown in shown in Table 12.

Table 12. Register Map

| Field Name                     | Size (bits) |        | Addres | s (6bits) |     |

|--------------------------------|-------------|--------|--------|-----------|-----|

|                                |             | Rd     | Wr     | Set       | Clr |

| Immediate Register Set         | -           |        |        | •         | •   |

| Vendor ID Low                  | 8           | 00h    | -      | -         | -   |

| Vendor ID High                 | 8           | 01h    | -      | -         | -   |

| Product ID Low                 | 8           | 02h    | -      | -         | -   |

| Product ID High                | 8           | 03h    | -      | -         | -   |

| Function Control               | 8           | 04-06h | 04h    | 05h       | 06h |

| Interface Control              | 8           | 07-09h | 07h    | 08h       | 09h |

| Debug                          | 8           | 15h    | -      | -         | -   |

| Scratch Register               | 8           | 16-18h | 16h    | 17h       | 18h |

| Carkit Control (Optional)      | 8           | 19-1Bh | 19h    | 1Ah       | 1Bh |

| Vendor Specific Register Set   | 1           |        | U.     | •         | •   |

| Drive Strength and Slew Rate   | 8           | 31h    | 31h    | -         | -   |

| USB Interface Control Register | 8           | 35h    | 35h    | -         | -   |

Document Number: 001-15775 Rev. \*N

Table 13 to Table 17 on page 18 define the read, write, set, and clear register options. The following are the conventions:

- Rd or rd = Read

- Wr or wr = Write

- Set or s = Set

- Clr or c = Clear

#### **Immediate Register Set**

The details of all immediate registers of TX2UL are shown in Table 6 on page 6, Table 18 on page 19, and Table 20 on page 21.

#### **Function Control Register**

Control ULPI Function Setting of TX2UL

Table 13. Function Control Register (Address: 04h - 06h [read], 04h [write], 05h [set], 06h [clear])

| Bit | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                         | Access    | Reset Value |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|

| 1:0 | XcvrSelect | Selects the required transceiver speed.  00b: Enable HS transceiver  01b: Enable FS transceiver  10b: Reserved  11b: Enable FS transceiver for LS packets.                                                                                                                                                                                                                                          | rd/wr/s/c | 01b         |

| 2   | TermSelect | Controls the internal 1.5 K pull up resistor and 45 HS terminations.                                                                                                                                                                                                                                                                                                                                | rd/wr/s/c | 0b          |

| 4:3 | OpMode     | Selects the required bit encording style during transmit.  00b: Normal operation  01b: Non-driving  10b: Disable bit stuff and NRZI encoding  11b: Do not automatically add SYNC and EOP when transmitting. It is used only for HS packets.                                                                                                                                                         | rd/wr/s/c | 00b         |

| 5   | Reset      | Active high transceiver reset. After the link sets this bit, TX2UL asserts DIR and resets ULPI core. When the reset is completed, DIR is de-asserted and automatically clears this bit. After de-asserting DIR, TX2UL re-asserts DIR and sends and RX CMD update to the link. The link waits for DIR to de-assert before using ULPI bus. It does not reset the ULPI interface or ULPI register set. | rd/wr/s/c | 0b          |

| 6   | SuspendM   | Active low. Put TX2UL into Low Power Mode. TX2UL powers down all blocks except the full speed receiver and ULPI interface pins. TX2UL sets this bit to '1' when it exits from low power mode.  0b: Enter into low power mode  1b: Normal operation mode                                                                                                                                             | rd/wr/s/c | 1b          |

| 7   | Reserved   |                                                                                                                                                                                                                                                                                                                                                                                                     | rd        | х           |

#### **Interface Control Register**

This register enables alternative interface and TX2UL features.

Table 14. Interface Control Register (Address: 07h - 09h [read], 07h [write], 08h [set], 09h [clear])

| Bit | Field Name                   | Description                                                                                                                                                                                                                                                          | Access    | Reset Value |

|-----|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|

| 1:0 | Reserved                     |                                                                                                                                                                                                                                                                      | rd        | xxb         |

| 2   | CarkitMode                   | Changes the ULPI interface to carkit interface that support UART pass through mode. This bit is cleared when it exits from carkit UART pass through mode.  0b: Disable serial carkit mode  1b: Enable serial carkit mode                                             | rd/wr/s/c | 0b          |

| 6:3 | Reserved                     |                                                                                                                                                                                                                                                                      | rd        | xxxxb       |

| 7   | Interface Protect<br>Disable | Controls circuitry built into TX2UL for protecting the ULPI interface when the link tristates STP and DATA[7:0]. Any pull ups or pull downs employed by this feature are disabled 0b: Enable the interface Protect Circuit 1b: Disable the Interface Protect Circuit | rd/wr/s/c | 0b          |

#### **Debug Register**

This register indicates the current value of various signals useful for debugging.

Table 15. Debug Register (Address: 15h [read only])

| Bit | Field Name | Description                                | Access | Reset Value |

|-----|------------|--------------------------------------------|--------|-------------|

| 0   | LineState0 | Contains the current value of LineState(0) | rd     | 0b          |

| 1   | LineState1 | Contains the current value of LineState(1) | rd     | 0b          |

| 7:2 | Reserved   |                                            | rd     | 000000b     |

#### Scratch Register

This register is for testing purpose only. The link can read, write, set and clear this register.

Table 16. Scratch Register (Address: 16h - 18h [read], 16h [write], 17h [set], 18h [clear])

| Bit | Field Name | Description                                                                                                | Access    | Reset Value |

|-----|------------|------------------------------------------------------------------------------------------------------------|-----------|-------------|

| 7:0 |            | Empty register byte for testing purposes. The link software reads, writes, sets, and clears this register. | rd/wr/s/c | 0000000b    |

#### **Carkit Control Register**

This register controls the TXD and RXD in carkit UART pass through mode. It has no control function if the CarkitMode bit in Interface Control Register is not set.

Table 17. Carkit Control Register (Address: 19h - 1Bh [read], 19h [write], 1Ah [set], 1Bh [clear])

| Bit | Field Name | Description                                  | Access    | Reset Value |

|-----|------------|----------------------------------------------|-----------|-------------|

| 1:0 | Reserved   |                                              | rd        | xxb         |

| 2   | TxdEn      | Routes TXD signal from DATA[0] pin to DM pin | rd/wr/s/c | 0b          |

| 3   | RxdEn      | Routes RXD signal from DP pin to DATA[1] pin | rd/wr/s/c | 0b          |

| 7:4 | Reserved   |                                              | rd        | xxxxb       |

Document Number: 001-15775 Rev. \*N Page 18 of 30

#### **Drive Strength and Slew Rate Configuration Register**

This register is mapped to the vendor specific registers address. This register configures the drive strength and slew rate of the outputs.

# Table 18. Drive Strength and Slew Rate Configuration Register (Address: 31h [read], 31h [write])

| Bit | Field Name    | Description                                                                                                                                                     | Access | Reset Value |

|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|

| 1:0 | DriveStrength | Configure the drive strength on the output pins 00b: Full drive strength 01b: Three quarter drive strength 10b: half drive strength 11b: Quarter drive strength | rd/wr  | 00b         |

| 2   | SlewRate      | Configure the slew rate on the output pins 0b: slow slew rate 1b: fast slew rate                                                                                | rd/wr  | 0b          |

| 7:3 | Reserved      |                                                                                                                                                                 | rd     | 00000b      |

#### **USB Interface Control Register**

This register is mapped to the vendor specific registers address. This register enables or disables the USB interface.

#### Table 19. USB Interface Control Register (Address: 35h [read], 35h [write])

| Bit | Field Name | Description                                                              | Access | Reset Value |

|-----|------------|--------------------------------------------------------------------------|--------|-------------|

| 1:0 | Reserved   | When write to this register, this field must be filled in 0s             | rd     | 00b         |

| 2   | UsbEnable  | USB interface control 0b: Disable USB interface 1b: Enable USB interface | rd/wr  | 0b          |

| 7:3 | Reserved   | When write to this register, this field must be filled in 0s             | rd     | 00000b      |

# **Absolute Maximum Ratings**

| DC voltage applied to outputs in high Z state                                 | -0.5 V to VCC + 0.5 V |

|-------------------------------------------------------------------------------|-----------------------|

| Static discharge voltage (ESD) from JESD22-A114                               | > 2000 V              |

| Latch up current                                                              | > 200 mA              |

| Maximum output short circuit current for all I/O configurations. (Vout = 0 V) | –100 mA               |

|                                                                               |                       |

| Operating Conditions                                                          |                       |

| Operating Conditions  Ambient temperature under bias (T <sub>A</sub> )        |                       |

|                                                                               | –40 °C to +85 °C      |

| Ambient temperature under bias (T <sub>A</sub> )                              |                       |

| Ambient temperature under bias (T <sub>A</sub> ) Industrial                   | 1.7 V to 1.9 V        |

# **DC Characteristics**

Table 20. DC Specifications for All Voltage Supplies

| Parameter              | Description                                                                                   | Conditions                                                                                    | Min         | Тур              | Max        | Unit |

|------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------|------------------|------------|------|

| VCC                    | Core voltage supply                                                                           |                                                                                               | 1.7         | 1.8              | 1.9        | V    |

| VIO                    | ULPI interface I/O voltage supply (this I/O supply is not available on 20-Ball WLCSP package) |                                                                                               | 1.7         | 1.8, 2.5,<br>3.3 | 3.6        | V    |

| VBATT                  | Crystal voltage supply                                                                        |                                                                                               | 3.0         | _                | 5.775      | V    |

| V <sub>POR(trip)</sub> | Power on reset trip voltage                                                                   |                                                                                               | 1.0         | _                | 1.5        | V    |

| V <sub>IH1</sub>       | Input HIGH voltage 1                                                                          | All ports except USB,<br>2.0 V ≤ VIO < 3.6 V                                                  | 0.625 × VIO | _                | VIO + 0.3  | V    |

| V <sub>IH2</sub>       | Input HIGH voltage 2                                                                          | All ports except USB,<br>1.7 V ≤ VIO < 2.0 V                                                  | VIO, 0.4    | _                | VIO + 0.3  | V    |

| V <sub>IL</sub>        | Input LOW voltage                                                                             |                                                                                               | -0.3        | _                | 0.25 × VIO | V    |

| V <sub>OH</sub>        | Output HIGH voltage                                                                           | $I_{OH}(MAX) = 0.1 \text{ mA}$                                                                | 0.9 × VIO   | _                | -          | V    |

| V <sub>OL</sub>        | Output LOW voltage                                                                            | I <sub>OL</sub> (MIN) = 0.1 mA                                                                | _           | _                | 0.1 × VIO  | V    |

| I <sub>IX</sub>        | Input leakage current                                                                         | All I/O signals held at VDDQ                                                                  | 1           | _                | 1          | μА   |

| I <sub>OZ</sub>        | Output leakage current                                                                        | All I/O signals held at VDDQ                                                                  | 1           | _                | 1          | μА   |

| ICC                    | Supply current                                                                                | Continuous Receive                                                                            | _           | 30               | 65         | mA   |

|                        |                                                                                               | Continuous Transmit                                                                           | _           | 30               | 65         | mA   |

|                        |                                                                                               | ULPI Low Power Mode<br>(Suspend)<br>VCC = 1.8 V                                               | -           | 300              | 750        | μА   |

|                        |                                                                                               | Sleep Mode - ULPI interface bus is either Hz or drive High - DP and DM must be Hz or pull low | _           | 5                | 40         | μА   |

| I <sub>PU</sub>        | Pull up current                                                                               | Interface protect enabled;<br>STP pin only; V <sub>I</sub> = 0 V                              | -13         | _                | -80        | μА   |

| I <sub>PD</sub>        | Pull down current                                                                             | Interface protect enabled; DATA[7:0] only; V <sub>I</sub> = VIO                               | 16          | _                | 90         | μА   |

# **AC Characteristics**

Table 21. ULPI Timing Parameters

| Parameter | Description                          | Min | Max   | Unit |

|-----------|--------------------------------------|-----|-------|------|

| tCS       | Setup time for control input         | 5.8 | -     | ns   |

| tDS       | Setup time for data input            | 5.8 | -     | ns   |

| tCH       | Hold time for control input          | 0   | -     | ns   |

| tDH       | Hold time for data input             | 0   | _     | ns   |

| tCD       | Output delay time for control output | 7.6 | 9.0   | ns   |

| tDD       | Output delay time for data output    | 7.6 | 9.0   | ns   |

| tSTATE    | Mode state change time               | 500 | _     | μS   |

| tPW       | Pulse width                          | 200 | 10000 | ns   |

CLOCK

Control In (STP)

DATA[7:0] In

Control out (DIR, NXT)

DATA [7:0] Out

Figure 18. ULPI Timing Diagram

Figure 19. 20-Pin CSP Package Configuration Mode Entry Timing Diagram

Figure 20. 24-Pin QFN Package Configuration Mode Entry Timing Diagram

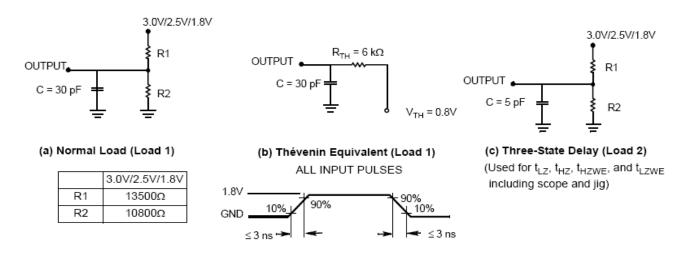

Figure 21. AC Test Loads and Waveforms

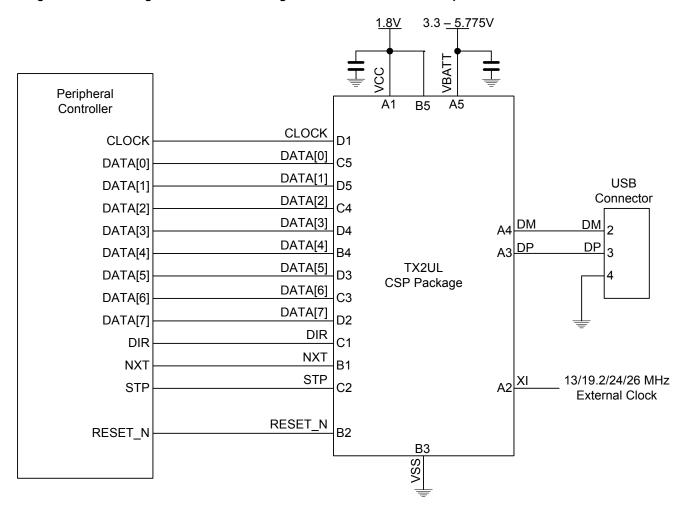

Figure 22. Connecting 20-Ball WLCSP Package TX2UL with a Standard Peripheral Controller with External Clock

# **Ordering Information**

| Ordering Code     | Package Type                  | Support Clock Input Frequencies (MHz) |

|-------------------|-------------------------------|---------------------------------------|

| CY7C68003-20FNXIT | 20-ball WLCSP – Tape and Reel | 13, 19.2, 24, 26                      |

| CY7C68003-24LQXI  | 24-pin QFN                    | 13, 19.2, 24, 26                      |

| CY7C68003-24LQXIT | 24-pin QFN – Tape and Reel    | 13, 19.2, 24, 26                      |

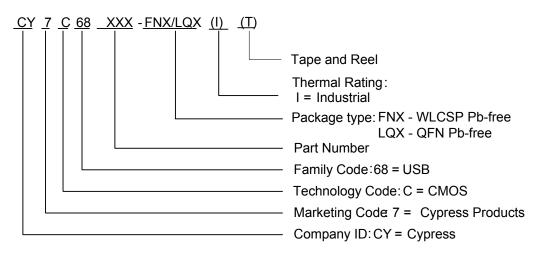

# **Ordering Code Definitions**

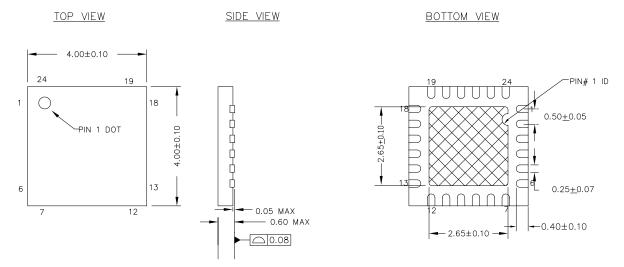

# **Package Diagram**

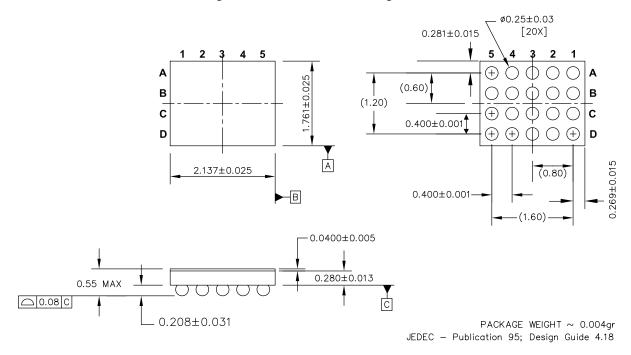

Figure 23. 20-Pin WLCSP Package Outline

ALL DIMENSION ARE IN MM

001-13856 \*C

Figure 24. 24-Pin QFN Package Outline

#### NOTES:

- 1. HATCH IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC # MO-248

- 3. PACKAGE WEIGHT:  $29 \pm 3 \text{ mg}$

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-13937 \*E

# **Acronyms**

Table 22. Acronyms Used in this Document

| Acronym | Description                                         |

|---------|-----------------------------------------------------|

| ASIC    | application specific integrated circuit             |

| CPU     | central processing unit                             |

| DID     | device identifier                                   |

| DSP     | digital signal processor                            |

| EEPROM  | electrically erasable programmable read only memory |

| EPP     | enhanced parallel port                              |

| ECC     | error correction code                               |

| FIFO    | first in first out                                  |

| GPIF    | general programmable interface                      |

| GPIO    | general purpose input / output                      |

| HBM     | human body model                                    |

| I/O     | input output                                        |

| PDA     | personal digital assistant                          |

| PLL     | phase lock loop                                     |

| PID     | product identifier                                  |

| SIE     | serial interface engine                             |

| SOF     | start of frame                                      |

| USB     | universal serial bus                                |

| VID     | vendor identifier                                   |

| WLCSP   | wafer level chip scale package                      |

| ULPI    | UTMI+ low pin interface                             |

# **Document Conventions**

#### **Units of Measure**

Table 23. Units of Measure

| Symbol | Unit of Measure   |

|--------|-------------------|

| KHz    | kilohertz         |

| Mbytes | megabytes         |

| MHz    | megahertz         |

| μΑ     | microampere       |

| μs     | microseconds      |

| μW     | microwatts        |

| mA     | milliampere       |

| mW     | milliwatts        |

| ns     | nanoseconds       |

| ppm    | parts per million |

| pF     | picofarads        |

| V      | volts             |

# **Document History Page**

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date   | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 1094246 | VSO / XVA          | See ECN              | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *A       | 1188703 | VSO                | See ECN              | Update the tSTATE min requirement (from 200 us to 500us) in Table 21 Section Sleep Mode add (see Table 21 for tSTATE requirement) Section of Operating Conditions (page 19), the second VCC corrected to VIO. Table 19, the reference voltage for the V <sub>IH1</sub> , V <sub>IH2</sub> , V <sub>IL</sub> , V <sub>OH</sub> , and V <sub>OL</sub> has corrected from VCC to VIO.                                                                                                                                                                                                                                                                                                                            |

| *B       | 1505863 | VSO /<br>AESA      | See ECN              | Change in Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *C       | 2081867 | VSO /<br>AESA      | See ECN              | Update the ESD description in the features list. Updated the description of section ,ÄúPower Supply Sequence,Äù Updated the section of Chip Section (CS_N) Updated the section of Operation Modes - tri-state mode only available in 24-pin QFN package Updated Figure 3. Added Table 4. Updated Figure 4 and Table 7 (CSP pin assignment has been changed) Updated the section of Configuration Mode Correct the hyper link section of Immediate Register Set Correct the word of ,ÄúReserved,Äù in Table 14 Updated ULPI Timing Parameters table (table-21) Updated ULPI Timing Diagram (figure 18) Added Figure 19. Removed USB Interface Control Register section and table in page 19 Updated Figure 22. |

| *D       | 2552066 | VSO                | 08/13/2008           | In the first page, feature list, update the CSP dimension from ,Äú2.2 x 1.8 mm,Äù to ,Äú2.14 x 1.76 mm,Äù. Updated Table 12 Add USB Interface Control Register section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *E       | 2597682 | VSO /<br>AESA      | 10/28/2008           | Removed PRELIMINARY in master pages (turn into Final data sheet).  Updated data sheet template.  Updated Ordering Information table.  In the Clocking section, added a bullet ,Äò150 ppm,Äô.  Table 3:  □ changed PN_DC to PN_100  □ changed DC to 100  □ change the unit of dB to dBc/Hz  □ added a row of ,ÄúMaximum Frequency Deviation,Äù                                                                                                                                                                                                                                                                                                                                                                 |

| *F       | 2671871 | VSO /<br>PYRS      | 03/13/2009           | Updated Suspend current in Table 20 (clarified VCC = 1.8 V). Changed all TX3, TX3LP18 to TX2UL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |