# WirelessUSB™ LP 2.4 GHz Radio SoC

### **Features**

- 2.4 GHz Direct Sequence Spread Spectrum (DSSS) radio transceiver

- Operates in the unlicensed worldwide Industrial, Scientific, and Medical (ISM) band (2.400 GHz to 2.483 GHz)

- 21 mA operating current (Transmit at -5 dBm)

- Transmit power up to +4 dBm

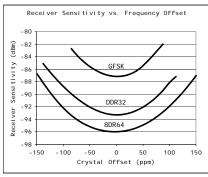

- Receive sensitivity up to -97 dBm

- Sleep Current less than 1 µA

- DSSS data rates up to 250 kbps, GFSK data rate of 1 Mbps

- Low external component count

- Auto Transaction Sequencer (ATS) no MCU intervention

- Framing, Length, CRC16, and Auto ACK

- Power Management Unit (PMU) for MCU/Sensor

- Fast Startup and Fast Channel Changes

- Separate 16-byte Transmit and Receive FIFOs

- AutoRate<sup>TM</sup> dynamic data rate reception

- Receive Signal Strength Indication (RSSI)

- Serial Peripheral Interface (SPI) control while in sleep mode

- 4 MHz SPI microcontroller interface

- Battery Voltage Monitoring Circuitry

- Supports coin-cell operated applications

- Operating voltage from 1.8 V to 3.6 V

- Operating temperature from 0 °C to 70 °C

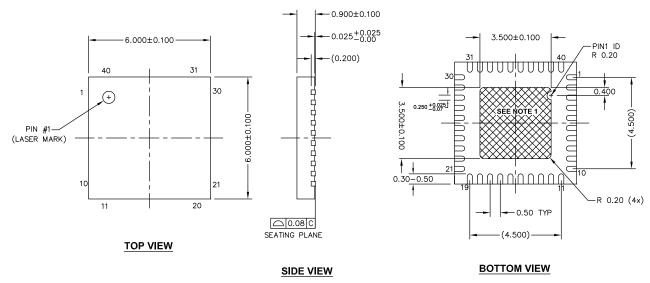

- Space saving 40-pin QFN 6 x 6 mm package

### Applications

- Wireless Keyboards and Mice

- Wireless Gamepads

- Remote Controls

- Toys

- VOIP and Wireless Headsets

- White Goods

- Consumer Electronics

- Home Automation

- Automatic Meter Readers

- Personal Health and Entertainment

## Applications Support

See www.cypress.com for development tools, reference designs, and application notes.

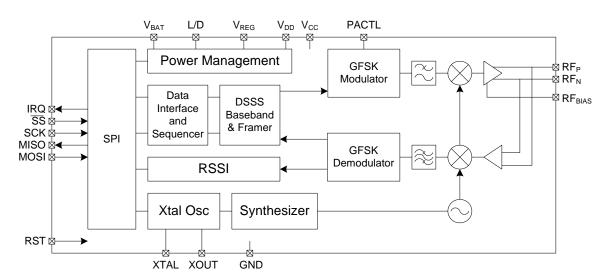

## **Logic Block Diagram**

### Contents

| Functional Description                             | 3  |

|----------------------------------------------------|----|

| Pinouts                                            |    |

| Pin Definitions                                    | 3  |

| Functional Overview                                | 4  |

| Data Transmission Modes                            | 4  |

| Link Layer Modes                                   | 4  |

| Packet Buffers                                     | 5  |

| Auto Transaction Sequencer (ATS)                   | 6  |

| Data Rates                                         | 6  |

| Functional Block Overview                          | 6  |

| 2.4 GHz Radio                                      | 6  |

| Frequency Synthesizer                              | 6  |

| Baseband and Framer                                |    |

| Packet Buffers and Radio Configuration Registers . | 6  |

| SPI Interface                                      | 6  |

| Interrupts                                         | 8  |

| Clocks                                             | 8  |

| Power Management                                   | 8  |

| Low Noise Amplifier and                            |    |

| Received Signal Strength Indication                | 9  |

| Receive Spurious Response                          | 9  |

| Application Examples                               | 10 |

| Registers                                          | 15 |

| Absolute Maximum Ratings                     | 16 |

|----------------------------------------------|----|

| Operating Conditions                         | 16 |

| DC Characteristics                           |    |

| AC Characteristics                           | 18 |

| SPI Interface                                | 18 |

| RF Characteristics                           |    |

| Radio Parameters                             | 19 |

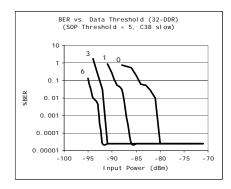

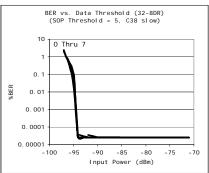

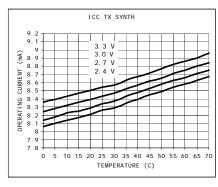

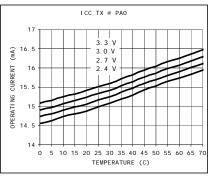

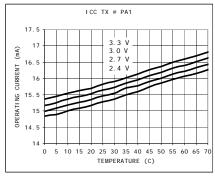

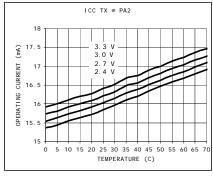

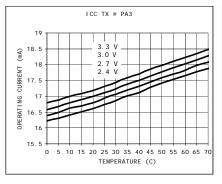

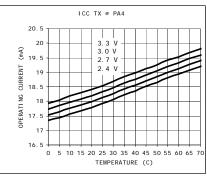

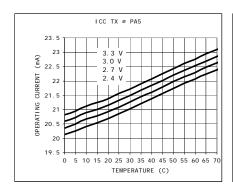

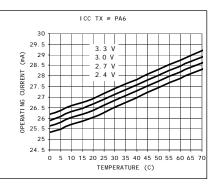

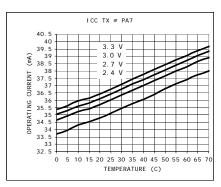

| Typical Operating Characteristics            |    |

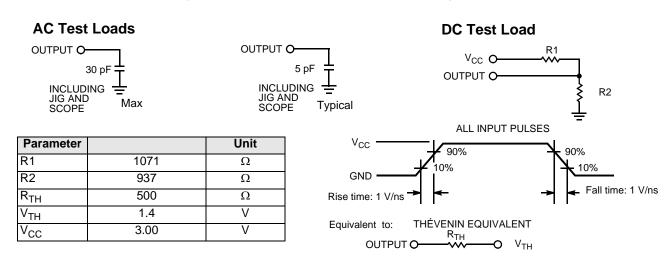

| AC Test Loads and Waveforms for Digital Pins |    |

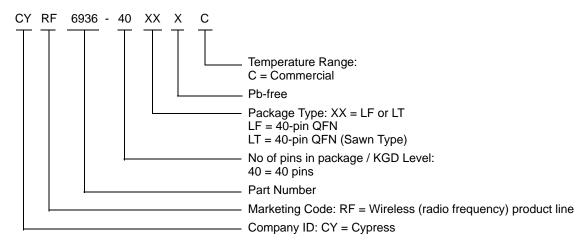

| Ordering Information                         |    |

| Ordering Code Definitions                    | 24 |

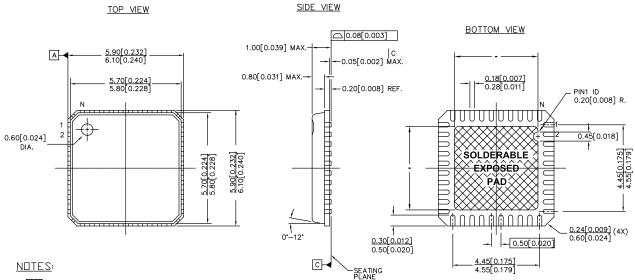

| Package Diagram                              |    |

| Acronyms                                     |    |

| Document Conventions                         | 27 |

| Units of Measure                             | 27 |

| Document History Page                        | 28 |

| Sales, Solutions, and Legal Information      | 30 |

| Worldwide Sales and Design Support           | 30 |

| Products                                     | 30 |

| PSoC® Solutions                              | 30 |

| Cypress Developer Community                  | 30 |

| Technical Support                            | 30 |

## **Functional Description**

The CYRF6936 WirelessUSB™ LP radio is a second generation member of the Cypress WirelessUSB Radio System-On-Chip (SoC) family. The CYRF6936 is interoperable with the first generation CYWUSB69xx devices. The CYRF6936 IC adds a range of enhanced features, including increased operating voltage range, reduced supply current in all operating modes, higher data rate options, reduced crystal start up, synthesizer settling, and link turnaround times.

### **Pinouts**

30 PACTL / GPIO XTAL NC 2 29 XOUT / GPIO 3 28 MISO / GPIO  $V_{\text{CC}}$ 27 MOSI / SDAT NC 4 CYRF6936 NC 5 WirelessUSB LP 26 IRQ / GPIO 40-Pin QFN 25 SCK V<sub>BAT1</sub> 6 24 SS V<sub>BAT2</sub> 8 23 NC 22 NC NC 9 \* E-PAD Bottom Side RF<sub>BIAS</sub> 10 21 NC

Figure 1. 40-pin QFN pinout

### **Pin Definitions**

| Pin Number                                                          | Name                  | Туре | Default | Description                                                                                                                        |

|---------------------------------------------------------------------|-----------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                   | XTAL                  | I    | I       | 12 MHz crystal.                                                                                                                    |

| 2, 4, 5, 9, 14,<br>15, 17, 18, 20,<br>21, 22, 23, 31,<br>32, 36, 39 | NC                    | NC   |         | Connect to GND.                                                                                                                    |

| 3, 7, 16                                                            | V <sub>CC</sub>       | Pwr  |         | $V_{CC}$ = 2.4 V to 3.6 V. Typically connected to $V_{REG}$ .                                                                      |

| 6, 8, 38                                                            | V <sub>BAT(0-2)</sub> | Pwr  |         | V <sub>BAT</sub> = 1.8 V to 3.6 V. Main supply.                                                                                    |

| 10                                                                  | RF <sub>BIAS</sub>    | 0    | 0       | RF I/O 1.8 V reference voltage.                                                                                                    |

| 11                                                                  | RF <sub>P</sub>       | I/O  | I       | Differential RF signal to and from antenna.                                                                                        |

| 12                                                                  | GND                   | GND  |         | Ground.                                                                                                                            |

| 13                                                                  | $RF_N$                | I/O  | I       | Differential RF signal to and from antenna.                                                                                        |

| 19                                                                  | RESV                  | I    |         | Must be connected to GND.                                                                                                          |

| 24                                                                  | SS                    | I    | I       | SPI enable, active LOW assertion. Enables and frames transfers.                                                                    |

| 25                                                                  | SCK                   | I    | I       | SPI clock.                                                                                                                         |

| 26                                                                  | IRQ                   | I/O  | 0       | Interrupt output (configurable active HIGH or LOW), or GPIO.                                                                       |

| 27                                                                  | MOSI                  | I/O  | I       | SPI data input pin (Master Out Slave In), or SDAT.                                                                                 |

| 28                                                                  | MISO                  | I/O  | Z       | SPI data output pin (Master In Sla <u>ve</u> Out), or GPIO (in SPI 3-pin mode). Tri-states when SPI 3PIN = 0 and SS is deasserted. |

Document Number: 38-16015 Rev. \*K

### Pin Definitions (continued)

| Pin Number  | Name             | Type | Default | Description                                                                                                                                                                                                                                                         |

|-------------|------------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29          | XOUT             | I/O  | 0       | Buffered 0.75, 1.5, 3, 6, or 12 MHz clock, PACTL, or GPIO. Tri-states in sleep mode (configure as GPIO drive LOW).                                                                                                                                                  |

| 30          | PACTL            | I/O  | 0       | Control signal for external PA, T/R switch, or GPIO.                                                                                                                                                                                                                |

| 33          | V <sub>I/O</sub> | Pwr  |         | I/O interface voltage, 1.8–3.6 V.                                                                                                                                                                                                                                   |

| 34          | RST              | I    | I       | Device reset. Internal 10 kohm pull down resistor. Active HIGH, connect through a 0.47 $\mu$ F capacitor to V <sub>BAT</sub> . Must have RST = 1 event the first time power is applied to the radio. Otherwise the state of the radio control registers is unknown. |

| 35          | V <sub>DD</sub>  | Pwr  |         | Decoupling pin for 1.8 V logic regulator, connect through a 0.47 $\mu\text{F}$ capacitor to GND.                                                                                                                                                                    |

| 37          | L/D              | 0    |         | PMU inductor/diode connection, when used. If not used, connect to GND.                                                                                                                                                                                              |

| 40          | $V_{REG}$        | Pwr  |         | PMU boosted output voltage feedback.                                                                                                                                                                                                                                |

| E-PAD       | GND              | GND  |         | Must be soldered to Ground.                                                                                                                                                                                                                                         |

| Corner Tabs | NC               | NC   |         | Do Not solder the tabs and keep other signal traces clear. All tabs are common to the lead frame or paddle which is grounded after the pad is grounded. While they are visible to the user, they do not extend to the bottom.                                       |

### **Functional Overview**

The CYRF6936 IC provides a complete WirelessUSB SPI to antenna wireless MODEMs. The SoC is designed to implement wireless device links operating in the worldwide 2.4 GHz ISM frequency band. It is intended for systems compliant with worldwide regulations covered by ETSI EN 301 489-1 V1.41, ETSI EN 300 328-1 V1.3.1 (Europe), FCC CFR 47 Part 15 (USA and Industry Canada), and TELEC ARIB\_T66\_March, 2003 (Japan).

The SoC contains a 2.4 GHz, 1 Mbps GFSK radio transceiver, packet data buffering, packet framer, DSSS baseband controller, Received Signal Strength Indication (RSSI), and SPI interface for data transfer and device configuration.

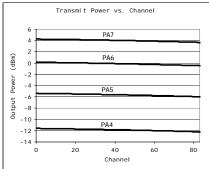

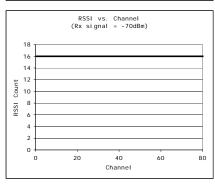

The radio supports 98 discrete 1 MHz channels (regulations may limit the use of some of these channels in certain jurisdictions).

The baseband performs DSSS spreading/despreading, Start of Packet (SOP), End of Packet (EOP) detection, and CRC16 generation and checking. The baseband may also be configured to automatically transmit Acknowledge (ACK) handshake packets whenever a valid packet is received.

When in receive mode, with packet framing enabled, the device is always ready to receive data transmitted at any of the supported bit rates. This enables the implementation of mixed-rate systems in which different devices use different data rates. This also enables the implementation of dynamic data rate systems that use high data rates at shorter distances or in a low-moderate interference environment or both. It changes to lower data rates at longer distances or in high interference environments or both.

In addition, the CYRF6936 IC has a Power Management Unit (PMU), which enables direct connection of the device to any battery voltage in the range 1.8 V to 3.6 V. The PMU conditions the battery voltage to provide the supply voltages required by the device, and may supply external devices.

### **Data Transmission Modes**

The SoC supports four different data transmission modes:

- In GFSK mode, data is transmitted at 1 Mbps, without any DSSS.

- In 8DR mode, eight bits are encoded in each derived code symbol transmitted.

- In DDR mode, two bits are encoded in each derived code symbol transmitted (As in the CYWUSB6934 DDR mode).

- In SDR mode, one bit is encoded in each derived code symbol transmitted (As in the CYWUSB6934 standard modes).

Both 64 chip and 32 chip Pseudo Noise (PN) codes are supported. The four data transmission modes apply to the data after the SOP. In particular the length, data, and CRC16 are all sent in the same mode. In general, lower data rates reduce packet error rate in any given environment.

### **Link Layer Modes**

The CYRF6936 IC device supports the following data packet framing features:

### SOP

Packets begin with a two-symbol SoP marker. This is required in GFSK and 8DR modes, but is optional in DDR mode and is not supported in SDR mode. If framing is disabled then an SOP event is inferred whenever two successive correlations are detected. The SOP\_CODE\_ADR code used for the SOP is different from that used for the "body" of the packet, and if desired may be a different length. SOP must be configured to be the same length on both sides of the link.

### Length

There are two options for detecting the end of a packet. If SOP is enabled, then the length field must be enabled. GFSK and 8DR must enable the length field. This is the first eight bits after

the SOP symbol, and is transmitted at the payload data rate. When the length field is enabled, an EoP condition is inferred after reception of the number of bytes defined in the length field, plus two bytes for the CRC16. The alternative to using the length field is to infer an EOP condition from a configurable number of successive noncorrelations; this option is not available in GFSK mode and is only recommended when using SDR mode.

### CRC16

The device may be configured to append a 16 bit CRC16 to each packet. The CRC16 uses the USB CRC polynomial with the added programmability of the seed. If enabled, the receiver verifies the calculated CRC16 for the payload data against the received value in the CRC16 field. The seed value for the CRC16 calculation is configurable, and the CRC16 transmitted may be

calculated using either the loaded seed value or a zero seed; the received data CRC16 is checked against both the configured and zero CRC16 seeds.

CRC16 detects the following errors:

- Any one bit in error.

- Any two bits in error (irrespective of how far apart, which column, and so on).

- Any odd number of bits in error (irrespective of the location).

- An error burst as wide as the checksum itself.

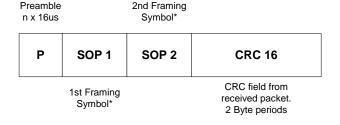

Figure 2 shows an example packet with SOP, CRC16, and lengths fields enabled, and Figure 3 shows a standard ACK packet.

Preamble 2nd Framing Symbol\* n x 16us SOP 1 Ρ SOP 2 **CRC 16 Payload Data** Length Packet 1st Framing length Symbol\* 1 Byte \*Note:32 or 64us

Figure 2. Example Packet Format

Figure 3. Example ACK Packet Format

Period

\*Note:32 or 64us

## Packet Buffers

All data transmission and reception use the 16 byte packet buffers - one for transmission and one for reception.

The transmit buffer allows loading a complete packet of up to 16 bytes of payload data in one burst SPI transaction. This is then transmitted with no further MCU intervention. Similarly, the receive buffer allows receiving an entire packet of payload data up to 16 bytes with no firmware intervention required until the packet reception is complete.

The CYRF6936 IC supports packets up to 255 bytes. However, the actual maximum packet length depends on the accuracy of the clock on each end of the link and the data mode. Interrupts are provided to allow an MCU to use the transmit and receive buffers as FIFOs. When transmitting a packet longer than 16 bytes, the MCU can load 16 bytes initially, and add further bytes to the transmit buffer as transmission of data creates space in the buffer. Similarly, when receiving packets longer than 16 bytes, the MCU must fetch received data from the FIFO periodically during packet reception to prevent it from overflowing.

### Auto Transaction Sequencer (ATS)

The CYRF6936 IC provides automated support for transmission and reception of acknowledged data packets.

When transmitting in transaction mode, the device automatically:

- starts the crystal and synthesizer

- enters transmit mode

- transmits the packet in the transmit buffer

- transitions to receive mode and waits for an ACK packet

- transitions to the transaction end state when an ACK packet is received or a timeout period expires

Similarly, when receiving in transaction mode, the device automatically:

- waits in receive mode for a valid packet to be received

- transitions to transmit mode, transmits an ACK packet

- transitions to the transaction end state (receive mode to await the next packet, and so on.)

The contents of the packet buffers are not affected by the transmission or reception of ACK packets.

In each case, the entire packet transaction takes place without any need for MCU firmware action (as long as packets of 16 bytes or less are used). To transmit data, the MCU must load the data packet to be transmitted, set the length, and set the TX GO bit. Similarly, when receiving packets in transaction mode, firmware must retrieve the fully received packet in response to an interrupt request indicating reception of a packet.

### **Data Rates**

The CYRF6936 IC supports the following data rates by combining the PN code lengths and data transmission modes described in the previous sections:

- 1000 kbps (GFSK)

- 250 kbps (32 chip 8DR)

- 125 kbps (64 chip 8DR)

- 62.5 kbps (32 chip DDR)

- 31.25 kbps (64 chip DDR)

- 15.625 kbps (64 chip SDR)

### **Functional Block Overview**

### 2.4 GHz Radio

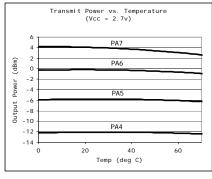

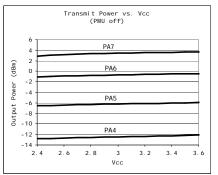

The radio transceiver is a dual conversion low IF architecture optimized for power, range, and robustness. The radio employs channel-matched filters to achieve high performance in the presence of interference. An integrated Power Amplifier (PA) provides up to +4 dBm transmit power, with an output power control range of 34 dB in seven steps. The supply current of the device is reduced as the RF output power is reduced.

Table 1. Internal PA Output Power Step Table

| PA Setting | Typical Output Power (dBm) |

|------------|----------------------------|

| 7          | +4                         |

| 6          | 0                          |

| 5          | -5                         |

| 4          | -13                        |

| 3          | -18                        |

| 2          | -24                        |

| 1          | -30                        |

| 0          | -35                        |

### Frequency Synthesizer

Before transmission or reception may begin, the frequency synthesizer must settle. The settling time varies depending on channel; 25 fast channels are provided with a maximum settling time of  $100~\mu s$ .

The 'fast channels' (less than 100  $\mu$ s settling time) are every third channel, starting at 0 up to and including 72 (for example, 0, 3, 6, 9 .... 69, 72).

### **Baseband and Framer**

The baseband and framer blocks provide the DSSS encoding and decoding, SOP generation and reception, CRC16 generation and checking, and EOP detection and length field.

### **Packet Buffers and Radio Configuration Registers**

Packet data and configuration registers are accessed through the SPI interface. All configuration registers are directly addressed through the address field in the SPI packet (as in the CYWUSB6934). Configuration registers allow configuration of DSSS PN codes, data rate, operating mode, interrupt masks, interrupt status, and so on.

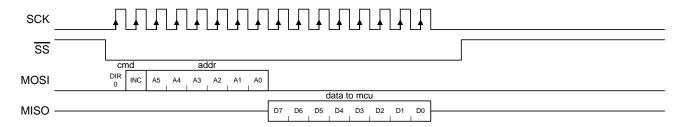

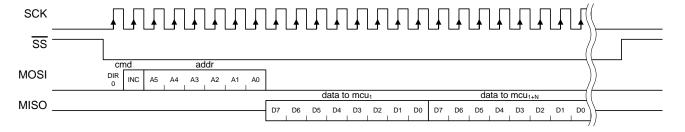

### **SPI Interface**

The CYRF6936 IC has an SPI interface supporting communication between an application MCU and one or more slave devices (including the CYRF6936). The SPI interface supports single-byte and multi-byte serial transfers using either 4-pin or 3-pin interfacing. The SPI communications interface consists of Slave Select (SS), Serial Clock (SCK), Master Out-Slave In (MOSI), Master In-Slave Out (MISO), or Serial Data (SDAT).

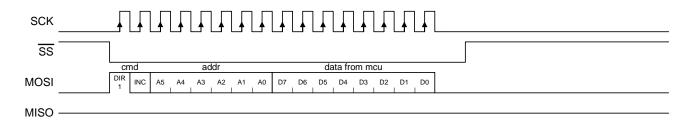

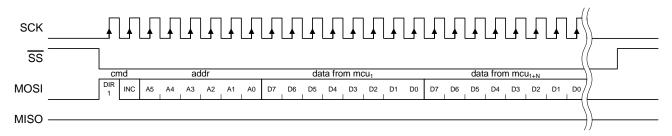

SPI communication may be described as the following:

- Command Direction (bit 7) = '1' enables SPI write transaction. A '0' enables SPI read transactions.

- Command Increment (bit 6) = '1' enables SPI auto address increment. When set, the address field automatically increments at the end of each data byte in a burst access. Otherwise the same address is accessed.

- Six bits of address

- Eight bits of data

The device receives SCK from an application MCU on the SCK pin. Data from the application MCU is shifted in on the MOSI pin. Data to the application MCU is shifted out on the MISO pin. The active LOW Slave Select (SS) pin must be asserted to initiate an SPI transfer.

The application MCU can initiate SPI data transfers using a multi-byte transaction. The first byte is the Command/Address byte, and the following bytes are the data bytes shown in Table 2 through Figure 6 on page 8.

The SPI communications interface has a burst mechanism, where the first byte can be followed by as many data bytes as required. A <u>burst</u> transaction is terminated by deasserting the slave select  $(\overline{SS} = 1)$ .

The SPI communications interface single read and burst read sequences are shown in Figure 4 on page 7 and Figure 5 on page 7, respectively.

The SPI communications interface single write and burst write sequences are shown in Figure 6 on page 8 and Figure 7 on page 8, respectively.

This interface may be optionally operated in a 3-pin mode with the MISO and MOSI functions combined in a single bidirectional data pin (SDAT). When using 3-pin mode, user firmware must ensure that the MOSI pin on the MCU is in a high impedance state except when MOSI is actively transmitting data.

The device registers may be written to or read from one byte at a time, or several sequential register locations may be written or read in a single SPI transaction using incrementing burst mode. In addition to single byte configuration registers, the device includes register files. Register files are FIFOs written to and read from using nonincrementing burst SPI transactions.

The IRQ pin function may be optionally multiplexed onto the MOSI pin. When this option is enabled, the IRQ function is not available while the SS pin is LOW. When using this configuration, user firmware must ensure that the MOSI pin on the MCU is in a high impedance state whenever the SS pin is HIGH.

The SPI interface is not dependent on the internal 12 MHz clock. Registers may therefore be read from or written to when the device is in sleep mode, and the 12 MHz oscillator disabled.

The SPI interface and the IRQ and RST pins have a separate voltage reference pin ( $V_{I/O}$ ). This enables the device to interface directly to MCUs operating at voltages below the CYRF6936 IC supply voltage.

**Table 2. SPI Transaction Format**

| Parameter |     |     | Byte 1  | Byte 1+N |

|-----------|-----|-----|---------|----------|

| Bit #     | 7   | 6   | [5:0]   | [7:0]    |

| Bit Name  | DIR | INC | Address | Data     |

Figure 4. SPI Single Read Sequence

Figure 5. SPI Incrementing Burst Read Sequence

Figure 6. SPI Single Write Sequence

Figure 7. SPI Incrementing Burst Write Sequence

### Interrupts

The device provides an interrupt (IRQ) output, which is configurable to indicate the occurrence of various different events. The IRQ pin may be programmed to be either active HIGH or active LOW, and be either a CMOS or open drain output. The available interrupts are described in the section Registers on page 15.

The CYRF6936 IC features three sets of interrupts: transmit, receive, and system interrupts. These interrupts all share a single pin (IRQ), but can be independently enabled or disabled. The contents of the enable registers are preserved when switching between transmit and receive modes.

If more than one interrupt is enabled at any time, it is necessary to read the relevant status register to determine which event caused the IRQ pin to assert. Even when a given interrupt source is disabled, the status of the condition that would otherwise cause an interrupt can be determined by reading the appropriate status register. It is therefore possible to use the devices without the IRQ pin, by polling the status registers to wait for an event, rather than using the IRQ pin.

### Clocks

A 12 MHz crystal (30 ppm or better) is directly connected between XTAL and GND without the need for external capacitors. A digital clock out function is provided, with selectable output frequencies of 0.75, 1.5, 3, 6, or 12 MHz. This output may be used to clock an external microcontroller (MCU) or ASIC. This output is enabled by default, but may be disabled.

The requirements to directly connect the crystal to the XTAL pin and GND are:

■ Nominal Frequency: 12 MHz

Operating Mode: Fundamental ModeResonance Mode: Parallel Resonant

■ Frequency Stability: ±30 ppm

■ Series Resistance: <60 ohms

■ Load Capacitance: 10 pF

■ Drive Level: 100 µW

### **Power Management**

The operating voltage of the device is 1.8 V to 3.6 V DC, which is applied to the  $V_{BAT}$  pin. The device can be shut down to a fully static sleep mode by writing to the FRC END = 1 and

END STATE = 000 bits in the XACT\_CFG\_ADR register over the SPI interface. The device enters sleep mode within 35 µs after the last SCK positive edge at the end of this SPI transaction. Alternatively, the device may be configured to automatically enter sleep mode after completing the packet transmission or reception. When in sleep mode, the on-chip oscillator is stopped, but the SPI interface remains functional. The device wakes from sleep mode automatically when the device is commanded to enter transmit or receive mode. When resuming from sleep mode, there is a short delay while the oscillator restarts. The device can be configured to assert the IRQ pin when the oscillator has stabilized.

The output voltage ( $V_{REG}$ ) of the Power Management Unit (PMU) is configurable to several minimum values between 2.4 V and 2.7 V.  $V_{REG}$  may be used to provide up to 15 mA (average load) to external devices. It is possible to disable the PMU and provide an externally regulated DC supply voltage to the device's main supply in the range 2.4 V to 3.6 V. The PMU also provides a regulated 1.8 V supply to the logic.

The PMU is designed to provide high boost efficiency (74–85% depending on input voltage, output voltage, and load) when using a Schottky diode and power inductor, eliminating the need for an external boost converter in many systems where other components require a boosted voltage. However, reasonable efficiencies (69–82% depending on input voltage, output voltage,

and load) may be achieved when using low cost components such as SOT23 diodes and 0805 inductors.

The current through the diode must stay within the linear operating range of the diode. For some loads the SOT23 diode is sufficient, but with higher loads it is not and an SS12 diode must be used to stay within this linear range of operation. Along with the diode, the inductor used must not saturate its core. In higher loads, a lower resistance/higher saturation coil such as the inductor from Sumida must be used.

The PMU also provides a configurable low battery detection function, which may be read over the SPI interface. One of seven thresholds between 1.8 V and 2.7 V may be selected. The interrupt pin may be configured to assert when the voltage on the  $V_{BAT}$  pin falls below the configured threshold. LV IRQ is not a latched event. Battery monitoring is disabled when the device is in sleep mode.

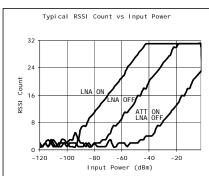

# Low Noise Amplifier and Received Signal Strength Indication

The gain of the receiver can be controlled directly by clearing the AGC EN bit and writing to the Low Noise Amplifier (LNA) bit of the RX\_CFG\_ADR register. Clearing the LNA bit reduces the receiver gain approximately 20 dB, allowing accurate reception of very strong received signals (for example, when operating a receiver very close to the transmitter). Approximately 30 dB of receiver attenuation can be added by setting the Attenuation (ATT) bit. This limits data reception to devices at very short

ranges. Disabling AGC and enabling LNA is recommended, unless receiving from a device using external PA.

When the device is in receive mode the RSSI\_ADR register returns the relative signal strength of the on-channel signal power.

When receiving, the device automatically measures and stores the relative strength of the signal being received as a five bit value. An RSSI reading is taken automatically when the SoP is detected. In addition, a new RSSI reading is taken every time the previous reading is read from the RSSI\_ADR register, allowing the background RF energy level on any given channel to be easily measured when RSSI is read while no signal is being received. A new reading can occur as fast as once every 12 µs.

### **Receive Spurious Response**

The transmitter may exhibit spurs around 50 MHz offset at levels approximately 50dB to 60dB below the carrier power. Receivers operating at the transmit spur frequency may receive the spur if the spur level power is greater than the receive sensitivity level.

The workaround for this is to program an additional byte in the packet header which contains the transmitter channel number. After the packet is received, the channel number can be checked. If the channel number does not match the receive channel then the packet is rejected.

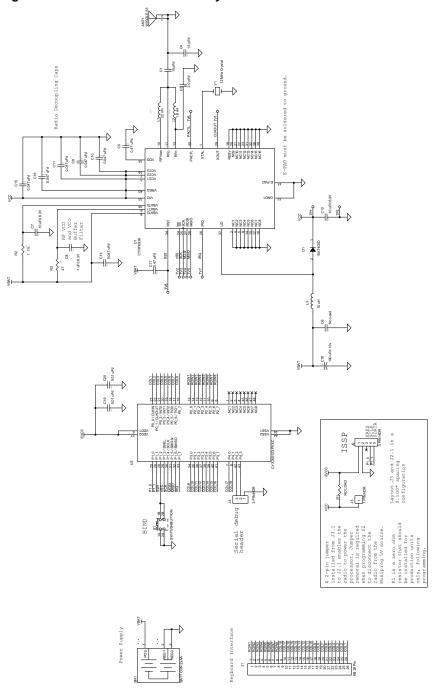

## **Application Examples**

Figure 8. Recommended Circuit for Systems where VBAT  $\leq$  2.4 V

Table 3. Recommended BoM for Systems where VBAT  $\leq$  2.4 V

| Item | Qty | <b>CY Part Number</b> | Reference                         | Description                                     | Manufacturer             | Mfr Part Number    |

|------|-----|-----------------------|-----------------------------------|-------------------------------------------------|--------------------------|--------------------|

| 1    | 1   | NA                    | ANT1                              | 2.5 GHZ H-STUB WIGGLE<br>ANTENNA FOR 63 MIL PCB | NA                       | NA                 |

| 2    | 1   | NA                    | BH1                               | BATTERY CLIPS 2AA CELL                          |                          |                    |

| 3    | 1   | 730-10012             | C1                                | CAP 15 PF 50 V CERAMIC NPO 0402                 | Panasonic                | ECJ-0EC1H150J      |

| 4    | 1   | 730-11955             | C3                                | CAP 2.0 PF 50 V CERAMIC NPO 0402                | Kemet                    | C0402C209C5GACTU   |

| 5    | 1   | 730-11398             | C4                                | CAP 1.5 PF 50 V CERAMIC NPO<br>0402 SMD         | PANASONIC                | ECJ-0EC1H1R5C      |

| 6    | 2   | 730R-13322            | C5, C17                           | CAP CER 0.47 UF 6.3 V X5R 0402                  | Murata                   | GRM155R60J474KE19D |

| 7    | 2   | 730-13037             | C12, C7                           | CAP CERAMIC 10 UF 6.3 V X5R 0805                | Kemet                    | C0805C106K9PACTU   |

| 8    | 1   | 730-13400             | C8                                | CAP 1 uF 6.3 V CERAMIC X5R 0402                 | Panasonic                | ECJ-0EB0J105M      |

| 9    | 6   | 730-13404             | C9, C10, C11,<br>C13, C15,<br>C16 | CAP 0.047 uF 16 V CERAMIC X5R 0402              | AVX                      | 0402YD473KAT2A     |

| 10   | 1   | 710-13201             | C18                               | CAP 100 UF 10 V ELECT FC                        | Panasonic - ECG          | EEU-FC1A101S       |

| 11   | 2   | 730-10794             | C20,C19                           | CAP 10000 PF 16 V CERAMIC 0402 SMD              | Panasonic - ECG          | ECJ-0EB1C103K      |

| 12   | 1   | 800-13317             | D1                                | DIODE SCHOTTKY 0.5 A 40 V<br>SOT23              | DIODES INC               | BAT400D-7-F        |

| 13   | 1   | NA                    | J1                                | PCB COPPER PADS                                 | NONE                     |                    |

| 14   | 1   | 420-11496             | J2                                | CONN HDR BRKWAY 5POS STR<br>AU PCB              | AMP Division of TYCO     | 103185-5           |

| 15   | 1   | 420-11964             | J3                                | HEADER 1 POS 0.230 HT MODII<br>.100 CL          | AMP/Tyco                 | 103185-1           |

| 16   | 1   | 800-13401             | L1                                | INDUCTOR 22 NH 2% FIXED 0603<br>SMD             | Panasonic - ECG          | ELJ-RE22NGF2       |

| 17   | 1   | 800-11651             | L2                                | INDUCTOR 1.8 NH +/3 NH FIXED 0402 SMD           | Panasonic - ECG          | ELJ-RF1N8DF        |

| 18   | 1   | 800-10594             | L3                                | COIL 10 UH 1100MA CHOKE 0805                    | Newark                   | 30K5421            |

| 19   | 1   | 630-11356             | R2                                |                                                 | Yageo                    | 9C08052A1R00FKHFT  |

| 20   | 1   | 610-13402             | R3                                | RES 47 OHM 1/16 W 5% 0402 SMD                   | Panasonic - ECG          | ERJ-2GEJ470X       |

| 21   | 1   | 800-13368             | S1                                | тн                                              | Panasonic - ECG          | EVQ-PAC07K         |

| 22   | 1   | CYRF6936-40LF<br>C    | U1                                | IC, LP 2.4 GHz RADIO SoC QFN-40                 | Cypress<br>Semiconductor | CYRF6936 Rev A5    |

| 23   | 1   | CY7C60123-PVX<br>C    | U2                                | IC WIRELESS EnCore II<br>CONTROLLER SSOP48      | Cypress<br>Semiconductor | CY7C60123-PVXC     |

| 24   | 1   | 800-13259             | Y1                                | CRYSTAL 12.00 MHZ HC49 SMD                      | eCERA                    | GF-1200008         |

| 25   | 1   | PDC-9265-*B           | PCB                               | PRINTED CIRCUIT BOARD                           | Cypress<br>Semiconductor | PDC-9265-*B        |

| 26   | 1   | 920-11206             | LABEL1                            | Serial Number                                   |                          |                    |

| 27   | 1   | 920-26504 *A          | LABEL2                            | PCA#                                            |                          | 121-26504 *A       |

Table 3. Recommended BoM for Systems where VBAT  $\leq$  2.4 V (continued)

| Item  | Qty                              | CY Part Number | Reference | Description                           | Manufacturer    | Mfr Part Number   |  |  |  |

|-------|----------------------------------|----------------|-----------|---------------------------------------|-----------------|-------------------|--|--|--|

| No Lo | Load Components - Do Not Install |                |           |                                       |                 |                   |  |  |  |

| 28    | 1                                | 730-13403      | C6        | CAP 47UF 6.3 V CERAMIC X5R<br>1210    | Panasonic       | ECJ-4YB0J476M     |  |  |  |

| 29    | 1                                | 630-10242      | R2        | RES CHIP 0.0 OHM 1/10W 5% 0805<br>SMD | Phycomp USA Inc | 9C08052A0R00JLHFT |  |  |  |

| 30    | 1                                | 730-13404      | C7        | CAP 0.047 uF 50 V CERAMIC X5R 0402    | AVX             | 0402YD473KAT2A    |  |  |  |

| 31    | 1                                | 420-10921      | J4        | HEADER 3POS FRIC STRGHT MTA<br>100    | AMP/Tyco        | 644456-3          |  |  |  |

| 32    | 1                                | 620-10519      | R1        | RES ZERO OHM 1/16W 5% 0603<br>SMD     | Panasonic - ECG | ERJ-3GEY0R00V     |  |  |  |

E-PAD must be soldered to ground. 1122TH 010 රි CND1 C6 0.047 uFd SS SCK MOSI MISO VCC C15 0.47 uFd Power Supply "CONNECT/ACTIVITY" R1 zero

Figure 9. Recommended Circuit for Systems where  $V_{BAT}$  is 2.4 V-3.6 V (PMU Disabled)

Table 4. Recommended BoM for Systems where  $V_{BAT}$  is 2.4 V–3.6 V (PMU disabled)

| Item | Qty | CY Part Number | Reference                      | Description                                     | Manufacturer                           | Mfr Part Number    |

|------|-----|----------------|--------------------------------|-------------------------------------------------|----------------------------------------|--------------------|

| 1    | 1   | NA             | ANT1                           | 2.5 GHZ H-STUB WIGGLE ANTENNA<br>FOR 32MIL PCB  | NA                                     | NA                 |

| 2    | 1   | 730-10012      | C1                             | CAP 15 PF 50 V CERAMIC NPO 0402                 | Panasonic                              | ECJ-0EC1H150J      |

| 3    | 1   | 730-11955      | C3                             | CAP 2.0 PF 50 V CERAMIC NPO 0402                | Kemet                                  | C0402C209C5GACTU   |

| 4    | 1   | 730-11398      | C4                             | CAP 1.5 PF 50 V CERAMIC NPO 0402<br>SMD         | PANASONIC                              | ECJ-0EC1H1R5C      |

| 5    | 1   | 730-13322      | C5, C15                        | CAP 0.47 uF 6.3 V CERAMIC X5R 0402              | Murata                                 | GRM155R60J474KE19D |

| 6    |     |                |                                |                                                 |                                        |                    |

| 7    | 6   | 730-13404      | C6, C7, C8,<br>C9, C10,<br>C11 | CAP 0.047 uF 16 V CERAMIC X5R 0402              | AVX                                    | 0402YD473KAT2A     |

| 8    | 1   | 730-11953      | C12                            | CAP 1500 PF 50 V CERAMIC X7R 0402               | Kemet                                  | C0402C152K5RACTU   |

| 9    | 1   | 730-13040      | C13                            | CAP CERAMIC 4.7 UF 6.3 V XR5 0805               | Kemet                                  | C0805C475K9PACTU   |

| 10   | 1   | 730-12003      | C14                            | CAP CER 2.2 UF 10 V 10% X7R 0805                | Murata<br>Electronics North<br>America | GRM21BR71A225KA01L |

| 11   | 1   | 800-13333      | D1                             | LED GREEN/RED BICOLOR 1210 SMD                  | LITEON                                 | LTST-C155KGJRKT    |

| 12   | 1   | 420-13046      | J1                             | CONN USB PLUG TYPE A PCB SMT                    | ACON                                   | UAR72-4N5J10       |

| 13   | 1   | 800-13401      | L1                             | INDUCTOR 22NH 2% FIXED 0603 SMD                 | Panasonic - ECG                        | ELJ-RE22NGF2       |

| 14   | 1   | 800-11651      | L2                             | INDUCTOR 1.8 NH +/3 NH FIXED 0402 SMD           | Panasonic - ECG                        | ELJ-RF1N8DF        |

| 15   | 1   | 610-10343      | R1                             | RES ZERO OHM 1/16W 0402 SMD                     | Panasonic - ECG                        | ERJ-2GE0R00X       |

| 16   | 1   | 610-13472      | R2                             | RES CHIP 620 OHM 1/16W 5% 0402<br>SMD           | Panasonic - ECG                        | ERJ-2GEJ621X       |

| 17   | 1   | 200-13471      | S1                             | SWITCH LT 3.5 MM X 2.9 MM 160 GF<br>SMD         | Panasonic - ECG                        | EVQ-P7J01K         |

| 18   | 1   | CYRF6936-40LFC | U1                             | IC, LP 2.4 GHz RADIO SoC QFN-40                 | Cypress<br>Semiconductor               | CYRF6936 Rev A5    |

| 19   | 1   | CY7C63803-SXC  | U2                             | IC LOW SPEED USB ENCORE II<br>CONTROLLER SOIC16 | Cypress<br>Semiconductor               | CY7C63803-SXC      |

| 20   | 1   | 800-13259      | Y1                             | CRYSTAL 12.00 MHZ HC49 SMD                      | eCERA                                  | GF-1200008         |

| 21   | 1   | PDC-9263-*B    | PCB                            | PRINTED CIRCUIT BOARD                           | Cypress<br>Semiconductor               | PDC-9263-*B        |

| 22   | 1   |                | LABEL1                         | Serial Number                                   | XXXXXX                                 |                    |

| 23   | 1   |                | LABEL2                         | PCA #                                           | 121-26305 **                           |                    |

## Registers

All registers are read and writable, except where noted. Registers may be written to or read from individually or in sequential groups.[1,2]

**Table 5. Register Map Summary**

| Address             | Mnemonic                    | b7                              | b6              | b5                  | b4                             | b3              | b2                | b1           | b0             | Default <sup>[1]</sup> | Access <sup>[1]</sup> |

|---------------------|-----------------------------|---------------------------------|-----------------|---------------------|--------------------------------|-----------------|-------------------|--------------|----------------|------------------------|-----------------------|

| 0x00                | CHANNEL_ADR                 | Not Used                        |                 |                     |                                | Channel         |                   |              |                | -1001000               | -bbbbbbb              |

| 0x01                | TX_LENGTH_ADR               |                                 | <u>I</u>        |                     | TX Le                          | ngth            |                   |              |                | 00000000               | bbbbbbbb              |

| 0x02                | TX_CTRL_ADR                 | TX GO                           | TX CLR          | TXB15<br>IRQEN      | TXB8<br>IRQEN                  | TXB0<br>IRQEN   | TXBERR<br>IRQEN   | TXC<br>IRQEN | TXE<br>IRQEN   | 00000011               | bbbbbbbb              |

| 0x03                | TX_CFG_ADR                  | Not Used                        | Not Used        | DATA CODE<br>LENGTH | DATA                           | MODE            |                   | PA SETTING   |                | 000101                 | bbbbbb                |

| 0x04                | TX_IRQ_STATUS_ADR           | OS<br>IRQ                       | LV<br>IRQ       | TXB15<br>IRQ        | TXB8<br>IRQ                    | TXB0<br>IRQ     | TXBERR<br>IRQ     | TXC<br>IRQ   | TXE<br>IRQ     |                        | rrrrrrr               |

| 0x05                | RX_CTRL_ADR                 | RX GO                           | RSVD            | RXB16<br>IRQEN      | RXB8<br>IRQEN                  | RXB1<br>IRQEN   | RXBERR<br>IRQEN   | RXC<br>IRQEN | RXE<br>IRQEN   | 00000111               | bbbbbbbb              |

| 0x06                | RX_CFG_ADR                  | AGC EN                          | LNA             | ATT                 | HILO                           | FAST<br>TURN EN | Not Used          | RXOW EN      | VLD EN         | 10010-10               | bbbbb-bb              |

| 0x07                | RX_IRQ_STATUS_ADR           | RXOW<br>IRQ                     | SOPDET<br>IRQ   | RXB16<br>IRQ        | RXB8<br>IRQ                    | RXB1<br>IRQ     | RXBERR<br>IRQ     | RXC<br>IRQ   | RXE<br>IRQ     |                        | brrrrrr               |

| 0x08                | RX_STATUS_ADR               | RX ACK                          | PKT ERR         | EOP ERR             | CRC0                           | Bad CRC         | RX Code           | RX Dat       | a Mode         |                        | rrrrrrr               |

| 0x09                | RX_COUNT_ADR                |                                 |                 | •                   | RX C                           |                 |                   |              |                | 00000000               | rrrrrrr               |

| 0x0A                | RX_LENGTH_ADR               |                                 |                 |                     | RX Le                          | ength           |                   |              |                | 00000000               | rrrrrrr               |

| 0x0B <sup>[1]</sup> | PWR_CTRL_ADR                | PMU EN                          | LVIRQ EN        | PMU Mode<br>Force   | PFET<br>disable <sup>[3]</sup> | LV              | TH                | PMU          | OUTV           | 10100000               | bbbbbbbb              |

| 0x0C                | XTAL_CTRL_ADR               | XOL                             | JT FN           | XSIRQ EN            | Not Used                       | Not Used        |                   | FREQ         |                | 000100                 | bbbbbb                |

| 0x0D                | IO_CFG_ADR                  | IRQ OD                          | IRQ POL         | MISO OD             | XOUT OD                        | PACTL OD        | PACTL<br>GPIO     | SPI 3PIN     | IRQ GPIO       | 00000000               | bbbbbbbb              |

| 0x0E                | GPIO_CTRL_ADR               | XOUT OP                         | MISO OP         | PACTL OP            | IRQ OP                         | XOUT IP         | MISO IP           | PACTL IP     | IRQ IP         | 0000                   | bbbbrrrr              |

| 0x0F                | XACT_CFG_ADR                | ACK EN                          | Not Used        | FRC END             |                                | END STATE       |                   | ACK          | ТО             | 1-000000               | b-bbbbbb              |

| 0x10                | FRAMING_CFG_ADR             | SOP EN                          | SOP LEN         | LEN EN              |                                |                 | SOP TH            |              |                | 10100101               | bbbbbbbb              |

| 0x11                | DATA32_THOLD_ADR            | Not Used                        | Not Used        | Not Used            | Not Used                       |                 | TI                | H32          |                | 0100                   | bbbb                  |

| 0x12                | DATA64_THOLD_ADR            | Not Used                        | Not Used        | Not Used            |                                | •               | TH64              |              |                | 01010                  | bbbbb                 |

| 0x13                | RSSI_ADR                    | SOP                             | Not Used        | LNA                 |                                |                 | RSSI              |              |                | 0-100000               | r-rrrrr               |

| 0x14                | EOP_CTRL_ADR <sup>[4]</sup> | HEN                             |                 | HINT                |                                |                 | E                 | OP           |                | 10100100               | bbbbbbbb              |

| 0x15                | CRC_SEED_LSB_ADR            |                                 |                 |                     | CRC SE                         |                 |                   |              |                | 00000000               | bbbbbbbb              |

| 0x16                | CRC_SEED_MSB_ADR            |                                 |                 |                     | CRC SEI                        |                 |                   |              |                | 00000000               | bbbbbbbb              |

| 0x17                | TX_CRC_LSB_ADR              |                                 |                 |                     | CRC                            |                 |                   |              |                |                        | rrrrrrr               |

| 0x18                | TX_CRC_MSB_ADR              |                                 |                 |                     | CRC                            |                 |                   |              |                |                        | rrrrrrr               |

| 0x19                | RX_CRC_LSB_ADR              |                                 |                 |                     | CRC                            |                 |                   |              |                | 11111111               | rrrrrrr               |

| 0x1A                | RX_CRC_MSB_ADR              |                                 |                 |                     | CRC                            | MSB             |                   |              |                | 11111111               | rrrrrrr               |

| 0x1B                | TX_OFFSET_LSB_ADR           |                                 |                 |                     | STRIM                          | 1 LSB           |                   |              |                | 00000000               | bbbbbbbb              |

| 0x1C                | TX_OFFSET_MSB_ADR           | Not Used                        | Not Used        | Not Used            | Not Used                       |                 | STRI              | M MSB        |                | 0000                   | bbbb                  |

| 0x1D                | MODE_OVERRIDE_ADR           | RSVD                            | RSVD            | FRC SEN             | -                              | AWAKE           | Not Used          | Not Used     | RST            | 000000                 | wwwww                 |

| 0x1E                | RX_OVERRIDE_ADR             | ACK RX                          | RXTX DLY        | MAN RXACK           | FRC<br>RXDR<br>MAN             | DIS CRC0        | DIS RXCRC         | ACE          | Not Used       | 0000000-               | bbbbbbbb<br>bbbbbbb   |

| 0x1F<br>0x26        | TX_OVERRIDE_ADR             | ACK TX<br>RSVD                  | FRC PRE<br>RSVD | RSVD<br>RSVD        | TXACK                          | OVRD ACK        | DIS TXCRC<br>RSVD | RSVD<br>RSVD | TX INV<br>RSVD | 0000000                |                       |

| 0x26<br>0x27        | CLK_OVERRIDE_ADR            | RSVD                            |                 | RSVD                | RSVD                           | RSVD            | RSVD              | RXF          | RSVD           | 00000000               | wwwwwww               |

| 0x27<br>0x28        | CLK_OVERRIDE_ADR            | RSVD                            | RSVD<br>RSVD    | RSVD                | RSVD                           | RSVD            | RSVD              | RXF          | RSVD           | 00000000               |                       |

| 0x28<br>0x29        |                             |                                 |                 |                     | RSVD                           | RSVD            |                   | RSVD         |                |                        | wwwwwww               |

|                     | RX_ABORT_ADR                | RSVD                            | RSVD            | ABORT EN            | -                              | _               | RSVD              | KSVD         | RSVD           | 00000000               | wwwwwww               |

| 0x32                | AUTO_CAL_TIME_ADR           |                                 |                 |                     | AUTO_C/                        | _               |                   |              |                | 00000011               | wwwwwww               |

| 0x35                | AUTO_CAL_OFFSET_ADR         | 50//5                           | 50/5            | D01/D               | AUTO_CAL                       |                 | 50//5             | 57.15.07     |                | 00000000               | wwwwwww               |

| 0x39                | ANALOG_CTRL_ADR             | RSVD                            | RSVD            | RSVD                | RSVD                           | RSVD            | RSVD              | RX INV       | ALL SLOW       | 00000000               | wwwwwww               |

| Register Files      | ITV DUEEED ADD              | 1                               |                 |                     | TV D "                         | as File         |                   |              |                | 1                      |                       |

| 0x20                | TX_BUFFER_ADR               | TX Buffer File                  |                 |                     |                                |                 |                   |              |                | wwwwwww                |                       |

| 0x21                | RX_BUFFER_ADR               | RX Buffer File<br>SOP Code File |                 |                     |                                |                 |                   | NI-4 -       | rrrrrrr        |                        |                       |

| 0x22                | SOP_CODE_ADR                |                                 |                 |                     |                                |                 |                   |              |                | Note 5                 | bbbbbbbb              |

| 0x23                | DATA_CODE_ADR               |                                 |                 |                     | Data Co                        |                 |                   |              |                | Note 6                 | bbbbbbbb              |

| 0x24                | PREAMBLE_ADR                |                                 |                 |                     | Preamb                         |                 |                   |              |                | Note 7                 | bbbbbbbb              |

| 0x25                | MFG_ID_ADR                  |                                 |                 |                     | MFG I                          | D File          |                   |              |                | NA                     | rrrrrrr               |

### Notes

- 1. b = read/write; r = read only; w = write only; '-' = not used, default value is undefined.

- 2. Registers must be configured or accessed only when the radio is in IDLE or SLEEP mode. The PMU, GPIOs, and RSSI registers can be accessed in Active Tx and

- 3. PFET Bit: Setting this bit to "1" disables the FET, therefore safely allowing Vbat to be connected to a separate reference from Vcc when the PMU is disabled to the radio.

4. EOP\_CTRL\_ADR[6:4] must never have the value of "000", that is, EOP Hint Symbol count must never be "0"

- 5. SOP\_CODE\_ADR default = 0x17FF9E213690C782.

- DATA\_CODE\_ADR default = 0x02F9939702FA5CE3012BF1DB0132BE6F.

PREAMBLE\_ADR default = 0x333302. The count value must be great than 4 for DDR and greater than 8 for SDR.

## **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested. Storage Temperature ......-65 °C to +150 °C Ambient Temperature with Power Applied ......-55 °C to +125 °C Supply Voltage on any power supply pin relative to V<sub>SS</sub> .....-0.3 V to +3.9 V DC Voltage to Logic Inputs  $^{[8]}$  .....-0.3 V to  $V_{I/O}$  +0.3 V DC Voltage applied to Outputs in High-Z State .....-0.3 V to V<sub>I/O</sub> +0.3 V

| Static Discharge Voltage (Digital) <sup>[9]</sup><br>Static Discharge Voltage (RF) <sup>[9]</sup> | 1100 V           |

|---------------------------------------------------------------------------------------------------|------------------|

| Latch Up Current                                                                                  | +200 mA, –200 mA |

| Operating Conditions                                                                              |                  |

| V <sub>CC</sub>                                                                                   | 2.4 V to 3.6 V   |

| V <sub>I/O</sub>                                                                                  |                  |

| V <sub>BAT</sub>                                                                                  |                  |

| T <sub>A</sub> (Ambient Temperature Under Bias) .                                                 | 0 °C to +70 °C   |

| Ground Voltage                                                                                    | 0 V              |

| F <sub>OSC</sub> (Crystal Frequency)                                                              | 12 MHz ± 30 ppm  |

### **DC Characteristics**

(T = 25 $^{\circ}$ C, V<sub>BAT</sub> = 2.4 V, PMU disabled, f<sub>OSC</sub> = 12.000000 MHz)

| Parameter                                | Description                                         | Conditions                                                          | Min                    | Тур              | Max                  | Unit |

|------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------|------------------------|------------------|----------------------|------|

| V <sub>BAT</sub>                         | Battery Voltage                                     | 0 °C-70 °C                                                          | 1.8                    | _                | 3.6                  | V    |

| V <sub>REG</sub> <sup>[10]</sup>         | PMU Output Voltage                                  | 2.4 V mode                                                          | 2.4                    | 2.43             | -                    | V    |

| V <sub>REG</sub> <sup>[10]</sup>         | PMU Output Voltage                                  | 2.7 V mode                                                          | 2.7                    | 2.73             | -                    | V    |

| V <sub>I/O</sub> <sup>[11]</sup>         | V <sub>I/O</sub> Voltage                            |                                                                     | 1.8                    | _                | 3.6                  | V    |

| V <sub>CC</sub>                          | V <sub>CC</sub> Voltage                             | 0 °C-70 °C                                                          | 2.4 <sup>[12]</sup>    | _                | 3.6                  | V    |

| V <sub>OH1</sub>                         | Output High Voltage Condition 1                     | At I <sub>OH</sub> = -100.0 μA                                      | V <sub>I/O</sub> – 0.2 | V <sub>I/O</sub> | _                    | V    |

| V <sub>OH2</sub>                         | Output High Voltage Condition 2                     | At $I_{OH} = -2.0 \text{ mA}$                                       | V <sub>I/O</sub> – 0.4 | V <sub>I/O</sub> | -                    | V    |

| $V_{OL}$                                 | Output Low Voltage                                  | At $I_{OL} = 2.0 \text{ mA}$                                        | 1                      | 0                | 0.45                 | V    |

| V <sub>IH</sub>                          | Input High Voltage                                  |                                                                     | 0.7 V <sub>I/O</sub>   | _                | V <sub>I/O</sub>     | V    |

| $V_{IL}$                                 | Input Low Voltage                                   |                                                                     | 0                      | -                | 0.3 V <sub>I/O</sub> | V    |

| I <sub>IL</sub>                          | Input Leakage Current                               | $0 < V_{IN} < V_{I/O}$                                              | -1                     | 0.26             | +1                   | μΑ   |

| C <sub>IN</sub>                          | Pin Input Capacitance                               | except XTAL, RF <sub>N</sub> , RF <sub>P</sub> , RF <sub>BIAS</sub> | _                      | 3.5              | 10                   | pF   |

| I <sub>CC</sub> (GFSK) <sup>[13]</sup>   | Average TX I <sub>CC</sub> , 1 Mbps, slow channel   | PA = 5, 2 way, 4 bytes/10 ms                                        | -                      | 0.87             | -                    | mA   |

| I <sub>CC</sub> (32-8DR) <sup>[13]</sup> | Average TX I <sub>CC</sub> , 250 kbps, fast channel | PA = 5, 2 way, 4 bytes/10 ms                                        | _                      | 1.2              | _                    | mA   |

| I <sub>SB</sub> <sup>[14]</sup>          | Sleep Mode I <sub>CC</sub>                          |                                                                     | _                      | 0.8              | 10                   | μΑ   |

| I <sub>SB</sub> <sup>[14]</sup>          | Sleep Mode I <sub>CC</sub>                          | PMU enabled                                                         | _                      | 31.4             | _                    | μΑ   |

| IDLE I <sub>CC</sub>                     | Radio off, XTAL Active                              | XOUT disabled                                                       | _                      | 1.0              | -                    | mA   |

- It is permissible to connect voltages above V<sub>I/O</sub> to inputs through a series resistor limiting input current to 1 mA. AC timing not guaranteed.

Human Body Model (HBM).

V<sub>REG</sub> depends on battery input voltage.

In sleep mode, the I/O interface voltage reference is V<sub>BAT</sub>.

In sleep mode, V<sub>CC</sub> min. can be as low as 1.8 V.

Includes current drawn while starting crystal, starting synthesizer, transmitting packet (including SOP and CRC16), changing to receive mode, and receiving ACK handshake. Device is in sleep except during this transaction.

ISB is not guaranteed if any I/O pin is connected to voltages higher than V<sub>I/O</sub>.

## DC Characteristics (continued)

(T = 25°C,  $V_{BAT}$  = 2.4 V, PMU disabled,  $f_{OSC}$  = 12.000000 MHz)

| Parameter                 | Description                        | Conditions                                                                    | Min | Тур  | Max | Unit |

|---------------------------|------------------------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

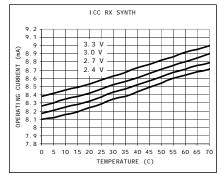

| I <sub>synth</sub>        | I <sub>CC</sub> during Synth Start |                                                                               | _   | 8.4  | _   | mA   |

| TX I <sub>CC</sub>        | I <sub>CC</sub> during Transmit    | PA = 5 (-5 dBm)                                                               | _   | 20.8 | _   | mA   |

| TX I <sub>CC</sub>        | I <sub>CC</sub> during Transmit    | PA = 6 (0 dBm)                                                                | _   | 26.2 | _   | mA   |

| TX I <sub>CC</sub>        | I <sub>CC</sub> during Transmit    | PA = 7 (+4 dBm)                                                               | _   | 34.1 | _   | mA   |

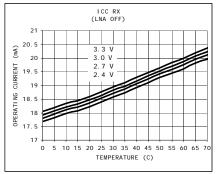

| RX I <sub>CC</sub>        | I <sub>CC</sub> during Receive     | LNA off, ATT on                                                               | _   | 18.4 | _   | mA   |

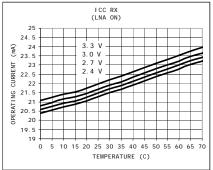

| RX I <sub>CC</sub>        | I <sub>CC</sub> during Receive     | LNA on, ATT off                                                               | _   | 21.2 | _   | mA   |

| Boost Eff                 | PMU Boost Converter Efficiency     | $V_{BAT} = 2.5 \text{ V}, V_{REG} = 2.73 \text{ V}, I_{LOAD} = 20 \text{ mA}$ | _   | 81   | _   | %    |

| I <sub>LOAD_EXT</sub> [8] | Average PMU External Load current  | V <sub>BAT</sub> = 1.8 V, V <sub>REG</sub> = 2.73 V,<br>0 °C–50 °C, RX Mode   | _   | _    | 15  | mA   |

| I <sub>LOAD_EXT</sub> [8] | Average PMU External Load current  | V <sub>BAT</sub> = 1.8 V, V <sub>REG</sub> = 2.73 V, 50 °C–70 °C, RX Mode     | _   | _    | 10  | mA   |

Document Number: 38-16015 Rev. \*K Page 17 of 30

<sup>8.</sup> I<sub>LOAD\_EXT</sub> is dependent on external components and this entry applies when the components connected to L/D are SS12 series diode and DH53100LC inductor from Sumida.

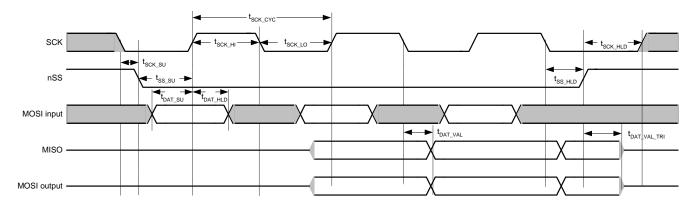

## **AC Characteristics**

### **SPI Interface**

| Parameter [9, 10]        | Description                                                                   | Min   | Тур | Max | Unit |

|--------------------------|-------------------------------------------------------------------------------|-------|-----|-----|------|

| t <sub>SCK_CYC</sub>     | SPI Clock Period                                                              | 238.1 | _   | _   | ns   |

| t <sub>SCK_HI</sub>      | SPI Clock High Time                                                           | 100   | _   | _   | ns   |

| t <sub>SCK_LO</sub>      | SPI Clock Low Time                                                            | 100   | _   | _   | ns   |

| t <sub>DAT_SU</sub>      | SPI Input Data Setup Time                                                     | 25    | _   | _   | ns   |

| t <sub>DAT_HLD</sub>     | SPI Input Data Hold Time                                                      | 10    | _   | _   | ns   |

| t <sub>DAT_VAL</sub>     | SPI Output Data Valid Time                                                    | 0     | _   | 50  | ns   |

| t <sub>DAT_VAL_TRI</sub> | SPI Output Data Tri-state (MOSI from Slave Select Deassert)                   | -     | -   | 20  | ns   |

| t <sub>SS_SU</sub>       | SPI Slave Select Setup Time before first positive edge of SCK <sup>[11]</sup> | 10    | -   | _   | ns   |

| t <sub>SS_HLD</sub>      | SPI Slave Select Hold Time after last negative edge of SCK                    | 10    | -   | _   | ns   |

| t <sub>SS_PW</sub>       | SPI Slave Select Minimum Pulse Width                                          | 20    | -   | _   | ns   |

| t <sub>SCK_SU</sub>      | SPI Slave Select Setup Time                                                   | 10    | -   | _   | ns   |

| t <sub>SCK_HLD</sub>     | SPI SCK Hold Time                                                             | 10    | -   | -   | ns   |

| t <sub>RESET</sub>       | Minimum RST Pin Pulse Width                                                   | 10    | -   | -   | ns   |

Figure 10. SPI Timing

<sup>9.</sup> AC values are not guaranteed if voltage on any pin exceeding V<sub>I/O</sub>.

10. C<sub>LOAD</sub> = 30 pF

11. SCK must start low at the time SS goes LOW, otherwise the success of SPI transactions are not guaranteed.

## **RF Characteristics**

### **Radio Parameters**

| Parameter Description                                           | Conditions                                          | Min      | Тур        | Max   | Unit     |

|-----------------------------------------------------------------|-----------------------------------------------------|----------|------------|-------|----------|

| RF Frequency Range                                              | Note 12                                             | 2.400    | _          | 2.497 | GHz      |

| Receiver (T = 25°C, V <sub>CC</sub> = V <sub>BAT</sub> = 3.0    | V, f <sub>OSC</sub> = 12.000000 MHz, BER < 1E-3)    |          |            | 1     | •        |

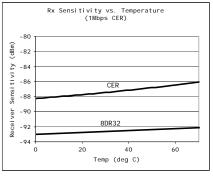

| Sensitivity 125 kbps 64-8DR                                     | BER 1E-3                                            | _        | -97        | _     | dBm      |

| Sensitivity 250 kbps 32-8DR                                     | BER 1E-3                                            | -        | -93        | -     | dBm      |

| Sensitivity                                                     | CER 1E-3                                            | -80      | -87        | _     | dBm      |

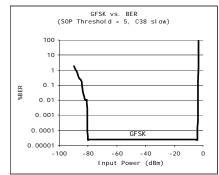

| Sensitivity GFSK                                                | BER 1E-3, ALL SLOW = 1                              | -        | -84        | -     | dBm      |

| LNA Gain                                                        |                                                     | _        | 22.8       | _     | dB       |

| ATT Gain                                                        |                                                     | _        | -31.7      | _     | dB       |

| Maximum Received Signal                                         | LNA On                                              | -15      | -6         | _     | dBm      |

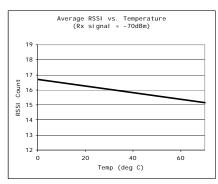

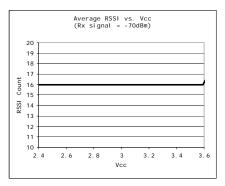

| RSSI Value for<br>PWR <sub>in</sub> –60 dBm <sup>[13]</sup>     | LNA On                                              | -        | 21         | _     | Count    |

| RSSI Slope                                                      |                                                     | _        | 1.9        | _     | dB/Count |

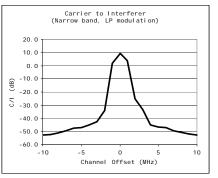

| Interference Performance (CER                                   | 1E-3)                                               |          |            | •     | •        |

| Co-channel Interference rejection Carrier-to-Interference (C/I) | C = -60 dBm                                         | -        | 9          | _     | dB       |

| Adjacent (±1 MHz) channel selectivity C/I 1 MHz                 | C = -60 dBm                                         | -        | 3          | _     | dB       |

| Adjacent (±2 MHz) channel selectivity C/I 2 MHz                 | C = -60 dBm                                         | -        | -30        | _     | dB       |

| Adjacent (≥ 3 MHz) channel selectivity C/I ≥ 3 MHz              | C = -67 dBm                                         | -        | -38        | _     | dB       |

| Out-of-Band Blocking 30<br>MHz–12.75 MHz [14]                   | C = -67 dBm                                         | -        | -30        | _     | dBm      |

| Intermodulation                                                 | $C = -64 \text{ dBm}, \Delta f = 5, 10 \text{ MHz}$ | _        | -36        | _     | dBm      |

| Receive Spurious Emission                                       |                                                     | <b>.</b> |            |       | •        |

| 800 MHz                                                         | 100 kHz ResBW                                       | _        | -79        | _     | dBm      |

| 1.6 GHz                                                         | 100 kHz ResBW                                       | _        | <b>-71</b> | _     | dBm      |

| 3.2 GHz                                                         | 100 kHz ResBW                                       | _        | -65        | _     | dBm      |

Notes

12. Subject to regulation.

13. RSSI value is not guaranteed. Extensive variation from part to part.

14. Exceptions F/3 & 5C/3.

## Radio Parameters (continued)

| Parameter Description                             | Conditions                                                    | Min | Тур             | Max | Unit  |

|---------------------------------------------------|---------------------------------------------------------------|-----|-----------------|-----|-------|

| Transmitter (T = 25°C, V <sub>CC</sub> = 3.0 V)   |                                                               |     |                 |     |       |

| Maximum RF Transmit Power                         | PA = 7                                                        | +2  | 4               | +6  | dBm   |

| Maximum RF Transmit Power                         | PA = 6                                                        | -2  | 0               | +2  | dBm   |

| Maximum RF Transmit Power                         | PA = 5                                                        | -7  | <b>-</b> 5      | -3  | dBm   |

| Maximum RF Transmit Power                         | PA = 0                                                        | _   | -35             | -   | dBm   |

| RF Power Control Range                            |                                                               | _   | 39              | _   | dB    |

| RF Power Range Control Step<br>Size               | Seven steps, monotonic                                        | _   | 5.6             | _   | dB    |

| Frequency Deviation Min                           | PN Code Pattern 10101010                                      | _   | 270             | _   | kHz   |

| Frequency Deviation Max                           | PN Code Pattern 11110000                                      | _   | 323             | _   | kHz   |

| Error Vector Magnitude (FSK error)                | >0 dBm                                                        | -   | 10              | _   | %rms  |

| Occupied Bandwidth                                | –6 dBc, 100 kHz ResBW                                         | 500 | 876             | _   | kHz   |

| Transmit Spurious Emission (PA                    | x = 7)                                                        |     |                 |     |       |

| In-band Spurious Second<br>Channel Power (±2 MHz) |                                                               | _   | -38             | _   | dBm   |

| In-band Spurious Third Channel Power (≥3 MHz)     |                                                               | _   | -44             | _   | dBm   |

| Non-Harmonically Related Spurs (800 MHz)          |                                                               | -   | -38             | _   | dBm   |

| Non-Harmonically Related Spurs (1.6 GHz)          |                                                               | -   | -34             | _   | dBm   |

| Non-Harmonically Related Spurs (3.2 GHz)          |                                                               | _   | -47             | -   | dBm   |

| Harmonic Spurs (Second Harmonic)                  |                                                               | _   | -43             | _   | dBm   |

| Harmonic Spurs (Third Harmonic)                   |                                                               | _   | -48             | _   | dBm   |

| Fourth and Greater Harmonics                      |                                                               | _   | <del>-</del> 59 | -   | dBm   |