# 12-Bit Serial Daisy-Chain CMOS D/A Converter

**DAC8143**

#### **FEATURES**

Fast, Flexible, Microprocessor Interfacing in Serially Controlled Systems

Buffered Digital Output Pin for Daisy-Chaining Multiple DACs

Minimizes Address-Decoding in Multiple DAC

Systems—Three-Wire Interface for Any Number of DACs

One Data Line

One CLK Line

One Load Line

Improved Resistance to ESD

-40°C to +85°C for the Extended Industrial Temperature Range

#### **APPLICATIONS**

Multiple-Channel Data Acquisition Systems Process Control and Industrial Automation Test Equipment Remote Microprocessor-Controlled Systems

#### **GENERAL INFORMATION**

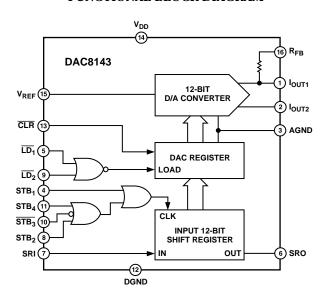

The DAC8143 is a 12-bit serial-input daisy-chain CMOS D/A converter that features serial data input and buffered serial data output. It was designed for multiple serial DAC systems, where serially daisy-chaining one DAC after another is greatly simplified.

The DAC8143 also minimizes address decoding lines enabling simpler logic interfacing. It allows three-wire interface for any number of DACs: one data line, one CLK line and one load line.

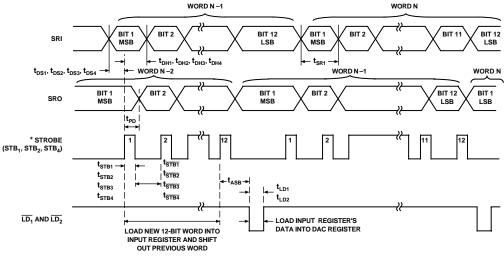

Serial data in the input register (MSB first) is sequentially clocked out to the SRO pin as the new data word (MSB first) is simultaneously clocked in from the SRI pin. The strobe inputs are used to clock in/out data on the rising or falling (user selected) strobe edges (STB<sub>1</sub>, STB<sub>2</sub>, STB<sub>3</sub>, STB<sub>4</sub>).

When the shift register's data has been updated, the new data word is transferred to the DAC register with use of  $\overline{LD_1}$  and  $\overline{LD_2}$  inputs.

Separate LOAD control inputs allow simultaneous output updating of multiple DACs. An asynchronous CLEAR input resets the DAC register without altering data in the input register.

Improved linearity and gain error performance permits reduced circuit parts count through the elimination of trimming components. Fast interface timing reduces timing design considerations while minimizing microprocessor wait states.

The DAC8143 is available in plastic packages that are compatible with autoinsertion equipment.

Plastic packaged devices come in the extended industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

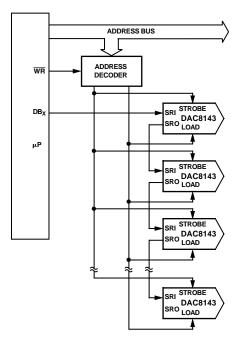

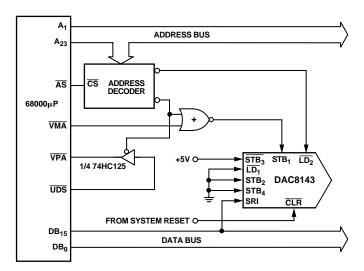

#### FUNCTIONAL BLOCK DIAGRAM

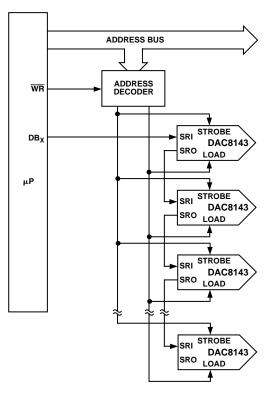

Figure 1. Multiple DAC8143s with Three-Wire Interface

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 1999

# DAC8143\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

# **DOCUMENTATION**

#### **Data Sheet**

DAC8143: 12-Bit Serial Daisy-Chain CMOS D/A Converter Data Sheet

### REFERENCE MATERIALS •

#### **Solutions Bulletins & Brochures**

• Digital to Analog Converters ICs Solutions Bulletin

### **DESIGN RESOURCES**

- DAC8143 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

## **DISCUSSIONS**

View all DAC8143 EngineerZone Discussions.

# SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# DAC8143—SPECIFICATIONS

# **ELECTRICAL CHARACTERISTICS** (@ $V_{DD} = +5 \text{ V}; V_{REF} = +10 \text{ V}; V_{OUT1} = V_{OUT2} = V_{AGND} = V_{DGND} = 0 \text{ V}; T_A = Full Temperature}$ Range specified under Absolute Maximum Ratings, unless otherwise noted.)

| Parameter                                        | Symbol            | Conditions                                                                              | Min | Typ         | Max                   | Units  |

|--------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|-----|-------------|-----------------------|--------|

| STATIC ACCURACY                                  |                   |                                                                                         |     |             |                       |        |

| Resolution                                       | N                 |                                                                                         | 12  |             |                       | Bits   |

| Nonlinearity                                     | INL               |                                                                                         |     |             | ±1                    | LSB    |

| Differential Nonlinearity <sup>1</sup>           | DNL               |                                                                                         |     |             | ±1                    | LSB    |

| Gain Error <sup>2</sup>                          | $G_{FSE}$         |                                                                                         |     |             | ±2                    | LSB    |

| Gain Tempco $(\Delta Gain/\Delta Temp)^3$        | TC <sub>GFS</sub> |                                                                                         |     |             | ±5                    | ppm/°C |

| Power Supply Rejection Ratio                     | 1 OGFS            |                                                                                         |     |             |                       | ppin   |

| $(\Delta Gain/\Delta V_{DD})$                    | PSRR              | $\Delta V_{\mathrm{DD}} = \pm 5\%$                                                      |     | ±0.0006     | +0.002                | %/%    |

| Output Leakage Current <sup>4</sup>              | I <sub>LKG</sub>  | $T_{A} = +25^{\circ}C$                                                                  |     | ±0.0000     | ±5.002                | nA     |

| Output Deakage Current                           | 1LKG              | $T_A = 125$ C $T_A = \text{Full Temperature Range}$                                     |     |             | ±25                   | nA     |

| Zero Scale Error <sup>5, 6</sup>                 | I <sub>ZSE</sub>  | $T_A = 1$ diff Temperature Range $T_A = +25^{\circ}C$                                   |     | ±0.002      | $\pm 0.03$            | LSB    |

| Zero Scale Error                                 | 1ZSE              | $T_A = 723$ C $T_A = \text{Full Temperature Range}$                                     |     | $\pm 0.002$ | $\pm 0.05$ $\pm 0.15$ | LSB    |

| Input Resistance <sup>7</sup>                    | D                 |                                                                                         | 7   | 11          | ±0.15                 | kΩ     |

| input Resistance                                 | R <sub>IN</sub>   | V <sub>REF</sub> Pin                                                                    | 1   | 11          | 15                    | KSZ    |

| AC PERFORMANCE                                   |                   |                                                                                         |     |             |                       |        |

| Output Current Settling Time <sup>3, 8</sup>     | t <sub>S</sub>    |                                                                                         |     | 0.380       | 1                     | μs     |

| AC Feedthrough Error                             |                   |                                                                                         |     |             |                       |        |

| $(V_{REF} \text{ to } I_{OUT1})^{3, 9}$          | FT                | $V_{REF} = 20 \text{ V p-p } @ \text{ f} = 10 \text{ kHz}, T_A = +25^{\circ}\text{C}$   |     |             | 2.0                   | mV p-p |

| Digital-to-Analog Glitch Energy <sup>3, 10</sup> | Q                 | $V_{REF} = 0 \text{ V}, I_{OUT} \text{ Load} = 100 \Omega, C_{EXT} = 13 \text{ pF}$     |     |             | 20                    | nVs    |

| Total Harmonic Distortion <sup>3</sup>           | THD               | $V_{REF} = 6 \text{ V rms } @ 1 \text{ kHz}$                                            |     |             |                       |        |

|                                                  |                   | DAC Register Loaded with All 1s                                                         |     |             | -92                   | dB     |

| Output Noise Voltage Density <sup>3, 11</sup>    | e <sub>n</sub>    | $10~\mathrm{Hz}$ to $100~\mathrm{kHz}$ Between $\mathrm{R_{FB}}$ and $\mathrm{I_{OUT}}$ |     |             | 13                    | nV/√Hz |

| DIGITAL INPUTS/OUTPUT                            |                   |                                                                                         |     |             |                       |        |

|                                                  | 37                |                                                                                         | 2.4 |             |                       | V      |

| Digital Input HIGH                               | $V_{IH}$          |                                                                                         | 2.4 |             | 0.0                   | 1      |

| Digital Input LOW                                | V <sub>IL</sub>   | 37 037 1537                                                                             |     |             | 0.8                   | V      |

| Input Leakage Current <sup>12</sup>              | I <sub>IN</sub>   | $V_{IN} = 0 \text{ V to } +5 \text{ V}$                                                 |     |             | ±1                    | μΑ     |

| Input Capacitance                                | C <sub>IN</sub>   | $V_{IN} = 0 V$                                                                          | ١.  |             | 8                     | pF     |

| Digital Output High                              | V <sub>OH</sub>   | $I_{OH} = -200 \mu\text{A}$                                                             | 4   |             | 0.4                   | V      |

| Digital Output Low                               | V <sub>OL</sub>   | $I_{OL} = 1.6 \text{ mA}$                                                               |     |             | 0.4                   | V      |

| ANALOG OUTPUTS                                   |                   |                                                                                         |     |             |                       |        |

| Output Capacitance <sup>3</sup>                  | C <sub>OUT1</sub> | Digital Inputs = All 1s                                                                 |     |             | 90                    | pF     |

|                                                  | $C_{OUT2}$        | Digital Inputs = All 0s                                                                 |     |             | 90                    | pF     |

| Output Capacitance <sup>3</sup>                  | C <sub>OUT1</sub> | Digital Inputs = All 0s                                                                 |     |             | 60                    | pF     |

| -                                                | $C_{OUT2}$        | Digital Inputs = All 1s                                                                 |     |             | 60                    | pF     |

| TIMING CHARACTERISTICS <sup>3</sup>              |                   |                                                                                         |     |             |                       |        |

| Serial Input to Strobe Setup Times               | too               | STB <sub>1</sub> Used as the Strobe                                                     | 50  |             |                       | ns     |

| $(t_{STB} = 80 \text{ ns})$                      | t <sub>DS1</sub>  | STB <sub>2</sub> Used as the Strobe                                                     | 20  |             |                       |        |

| (rSLB - 00 112)                                  | t <sub>DS2</sub>  | $STB_2$ Used as the Strobe $T_A = +25$ °C                                               | 10  |             |                       | ns     |

|                                                  | t <sub>DS3</sub>  | $T_A = Full$ Temperature Range                                                          | 20  |             |                       | ns     |

|                                                  | _                 | STB <sub>4</sub> Used as the Strobe                                                     | 20  |             |                       | ns     |

|                                                  | t <sub>DS4</sub>  |                                                                                         |     |             |                       | ns     |

|                                                  | t <sub>DH1</sub>  | STB <sub>1</sub> Used as the Strobe $T_A = +25^{\circ}C$                                | 40  |             |                       | ns     |

|                                                  |                   | $T_A = \text{Full Temperature Range}$                                                   | 50  |             |                       | ns     |

|                                                  | $t_{ m DH2}$      | STB <sub>2</sub> Used as the Strobe $T_A = +25^{\circ}C$                                | 50  |             |                       | ns     |

| C                                                |                   | $T_A$ = Full Temperature Range                                                          | 60  |             |                       | ns     |

| Serial Input to Strobe Hold Times                |                   | CTD Hard and Comba                                                                      | 00  |             |                       |        |

| $(t_{STB} = 80 \text{ ns})$                      | t <sub>DH3</sub>  | STB <sub>3</sub> Used as the Strobe                                                     | 80  |             |                       | ns     |

|                                                  | t <sub>DH4</sub>  | STB <sub>4</sub> Used as the Strobe                                                     | 80  |             |                       | ns     |

-2- REV. C

# **ELECTRICAL CHARACTERISTICS** (@ $V_{DD} = +5 \text{ V}$ ; $V_{REF} = +10 \text{ V}$ ; $V_{OUT1} = V_{OUT2} = V_{AGND} = V_{DGND} = 0 \text{ V}$ ; $T_A = Full$ Temperature Range specified under Absolute Maximum Ratings, unless otherwise noted.)

|                                                               |                           |                                              | I    | DAC8143 |      |       |

|---------------------------------------------------------------|---------------------------|----------------------------------------------|------|---------|------|-------|

| Parameter                                                     | Symbol                    | Conditions                                   | Min  | Typ     | Max  | Units |

| STB to SRO Propagation Delay <sup>13</sup>                    | t <sub>PD</sub>           | $T_A = +25^{\circ}C$                         |      |         | 220  | ns    |

|                                                               |                           | $T_A$ = Full Temperature Range               |      |         | 300  | ns    |

| SRI Data Pulsewidth                                           | t <sub>SRI</sub>          |                                              | 100  |         |      | ns    |

| $STB_1$ Pulsewidth $(\overline{STB_1} = 80 \text{ ns})^{14}$  | t <sub>STB1</sub>         |                                              | 80   |         |      | ns    |

| $STB_2$ Pulsewidth $(\overline{STB_2} = 100 \text{ ns})^{14}$ | t <sub>STB2</sub>         |                                              | 80   |         |      | ns    |

| $STB_3$ Pulsewidth $(\overline{STB_3} = 80 \text{ ns})^{14}$  | t <sub>STB3</sub>         |                                              | 80   |         |      | ns    |

| $STB_4$ Pulsewidth $(\overline{STB_4} = 80 \text{ ns})^{14}$  | t <sub>STB4</sub>         |                                              | 80   |         |      | ns    |

| Load Pulsewidth                                               | $t_{\rm LD1},t_{\rm LD2}$ | $T_{A} = +25^{\circ}C$                       | 140  |         |      | ns    |

|                                                               |                           | $T_A$ = Full Temperature Range               | 180  |         |      | ns    |

| LSB Strobe into Input Register                                |                           |                                              |      |         |      |       |

| to Load DAC Register Time                                     | t <sub>ASB</sub>          |                                              | 0    |         |      | ns    |

| CLR Pulsewidth                                                | t <sub>CLR</sub>          |                                              | 80   |         |      | ns    |

| POWER SUPPLY                                                  |                           |                                              |      |         |      |       |

| Supply Voltage                                                | $V_{\mathrm{DD}}$         |                                              | 4.75 | 5       | 5.25 | V     |

| Supply Current                                                | $I_{ m DD}$               | All Digital Inputs = $V_{IH}$ or $V_{IL}$    |      |         | 2    | mA    |

|                                                               |                           | All Digital Inputs = $0 \text{ V or V}_{DD}$ |      |         | 0.1  | mA    |

| Power Dissipation                                             | $P_{\mathrm{D}}$          | Digital Inputs = $0 \text{ V or V}_{DD}$     |      |         | 0.5  | mW    |

|                                                               |                           | 5 V × 0.1 mA                                 |      |         |      |       |

|                                                               |                           | Digital Inputs = $V_{IH}$ or $V_{IL}$        |      |         | 10   | mW    |

|                                                               |                           | 5 V × 2 mA                                   |      |         |      |       |

#### NOTES

Specifications subject to change without notice.

REV. C \_3\_

<sup>&</sup>lt;sup>1</sup>All grades are monotonic to 12 bits over temperature.

<sup>&</sup>lt;sup>2</sup>Using internal feedback resistor.

<sup>&</sup>lt;sup>3</sup>Guaranteed by design and not tested.

$<sup>^4</sup>$ Applies to  $I_{OUT1}$ ; all digital inputs =  $V_{IL}$ ,  $V_{REF}$  = +10 V; specification also applies for  $I_{OUT2}$  when all digital inputs =  $V_{IH}$ .

$<sup>^{5}</sup>V_{REF} = +10 \text{ V}$ , all digital inputs = 0 V.

<sup>&</sup>lt;sup>6</sup>Calculated from worst case  $R_{REF}$ :  $I_{ZSE}$  (in LSBs) =  $(R_{REF} \times I_{LKG} \times 4096) / V_{REF}$ .

<sup>&</sup>lt;sup>7</sup>Absolute temperature coefficient is less than +300 ppm/°C.

$<sup>^8</sup>I_{OUT}$ , Load = 100  $\Omega$ .  $C_{EXT}$  = 13 pF, digital input = 0 V to  $V_{DD}$  or  $V_{DD}$  to 0 V. Extrapolated to 1/2 LSB:  $t_S$  = propagation delay ( $t_{PD}$ ) +9  $\tau$ , where  $\tau$  equals measured time constant of the final RC decay.

<sup>&</sup>lt;sup>9</sup>All digital inputs = 0 V.

$<sup>^{10}</sup>V_{REF} = 0$  V, all digital inputs = 0 V to  $V_{DD}$  or  $V_{DD}$  to 0 V.

<sup>&</sup>lt;sup>11</sup>Calculations from  $e_n = \sqrt{4K \text{ TRB}}$  where:

K = Boltzmann constant, J/KR = resistance  $\Omega$

T = resistor temperature, K B = bandwidth, Hz

<sup>&</sup>lt;sup>12</sup>Digital inputs are CMOS gates; I<sub>IN</sub> typically 1 nA at +25°C.

$<sup>^{13}</sup>$ Measured from active strobe edge (STB) to new data output at SRO;  $C_L = 50$  pF.

<sup>&</sup>lt;sup>14</sup>Minimum low time pulsewidth for STB<sub>1</sub>, STB<sub>2</sub>, and STB<sub>4</sub>, and minimum high time pulsewidth for STB<sub>3</sub>.

#### ABSOLUTE MAXIMUM RATINGS

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

| II DOND                                               |

|-------------------------------------------------------|

| $V_{DD}$ to DGND                                      |

| $V_{REF}$ to DGND±25 V                                |

| $V_{RFB}$ to DGND±25 V                                |

| AGND to DGND $V_{DD}$ + 0.3 V                         |

| DGND to AGND $V_{DD}$ + 0.3 V                         |

| Digital Input Voltage Range0.3 V to V <sub>DD</sub>   |

| Output Voltage (Pin 1, Pin 2)0.3 V to V <sub>DD</sub> |

| Operating Temperature Range                           |

| FP/FS Versions40°C to +85°C                           |

| Junction Temperature+150°C                            |

| Storage Temperature65°C to +150°C                     |

| Lead Temperature (Soldering, 60 sec)+300°C            |

|                                                       |

| Package Type        | $\theta_{JA}$ * | $\theta_{ m JC}$ | Units |

|---------------------|-----------------|------------------|-------|

| 16-Lead Plastic DIP | 76              | 33               | °C/W  |

| 16-Lead SOIC        | 92              | 27               | °C/W  |

$<sup>\</sup>star \theta_{JA}$  is specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for P-DIP package;  $\theta_{JA}$  is specified for device soldered to printed circuit board for SOIC package.

#### **CAUTION**

- 1. Do not apply voltage higher than  $V_{DD}$  or less than DGND potential on any terminal except  $V_{REF}$  (Pin 15) and  $R_{FB}$  (Pin 16).

- 2. The digital control inputs are Zener-protected; however, permanent damage may occur on unprotected units from high energy electrostatic fields. Keep units in conductive foam at all times until ready to use.

- 3. Use proper antistatic handling procedures.

- 4. Absolute Maximum Ratings apply to packaged devices. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device.

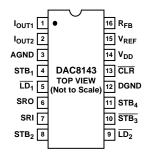

#### PIN CONNECTIONS

#### 16-Lead Epoxy Plastic DIP 16-Lead SOIC

#### **ORDERING GUIDE**

| Model     | Nonlinearity | Gain<br>Error | Temperature<br>Range | Package<br>Descriptions | Package<br>Options |  |

|-----------|--------------|---------------|----------------------|-------------------------|--------------------|--|

| DAC8143FP | ±1 LSB       | ±2 LSB        | -40°C to +85°C       | 16-Lead Plastic DIP     | N-16               |  |

| DAC8143FS | ±1 LSB       | ±2 LSB        | -40°C to +85°C       | 16-Lead SOIC            | R-16W              |  |

Die Size: 99 × 107 mil, 10,543 sq. mils.

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the DAC8143 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Ļ\_ REV. C

# **Typical Performance Characteristics—DAC8143**

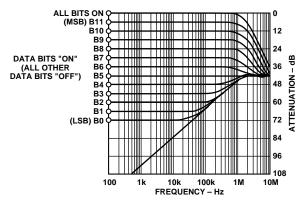

Figure 2. Multiplying Mode Frequency Response vs. Digital Code

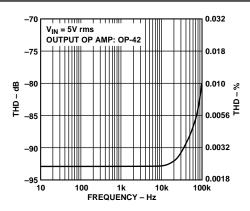

Figure 3. Multiplying Mode Total Harmonic Distortion vs. Frequency

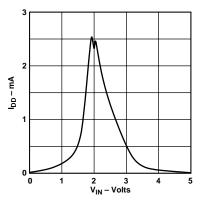

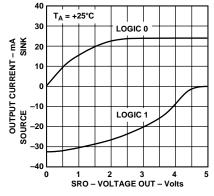

Figure 4. Supply Current vs. Logic Input Voltage

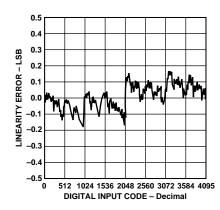

Figure 5. Linearity Error vs. Digital Code

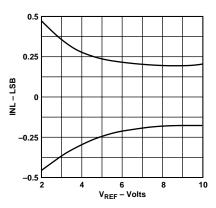

Figure 6. Linearity Error vs. Reference Voltage

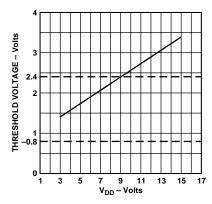

Figure 7. Logic Threshold Voltage vs. Supply Voltage

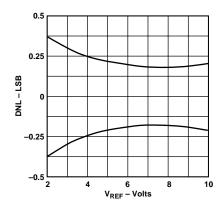

Figure 8. DNL Error vs. Reference Voltage

Figure 9. Digital Output Voltage vs. Output Current

REV. C \_5\_

# DEFINITION OF SPECIFICATIONS RESOLUTION

The resolution of a DAC is the number of states  $(2^n)$  into which the full-scale range (FSR) is divided (or resolved), where "n" is equal to the number of bits.

#### **SETTLING TIME**

Time required for the analog output of the DAC to settle to within 1/2 LSB of its final value for a given digital input stimulus; i.e., zero to full-scale.

#### **GAIN**

Ratio of the DAC's external operational amplifier output voltage to the V<sub>REF</sub> input voltage when all digital inputs are HIGH.

#### FEEDTHROUGH ERROR

Error caused by capacitive coupling from  $V_{\text{REF}}$  to output. Feedthrough error limits are specified with all switches off.

#### **OUTPUT CAPACITANCE**

Capacitance from I<sub>OUT1</sub> to ground.

#### **OUTPUT LEAKAGE CURRENT**

Current appearing at  $I_{OUT1}$  when all digital inputs are LOW, or at  $I_{OUT2}$  terminal when all inputs are HIGH.

#### **GENERAL CIRCUIT INFORMATION**

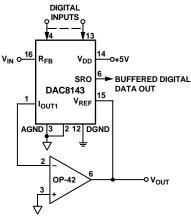

The DAC8143 is a 12-bit serial-input, buffered serial-output, multiplying CMOS D/A converter. It has an R-2R resistor ladder network, a 12-bit input shift register, 12-bit DAC register, control logic circuitry, and a buffered digital output stage.

The control logic forms an interface in which serial data is loaded, under microprocessor control, into the input shift register and then transferred, in parallel, to the DAC register. In addition, buffered serial output data is present at the SRO pin when input data is loaded into the input register. This buffered data follows the digital input data (SRI) by 12 clock cycles and is available for daisy-chaining additional DACs.

An asynchronous CLEAR function allows resetting the DAC register to a zero code (0000 0000 0000) without altering data stored in the registers.

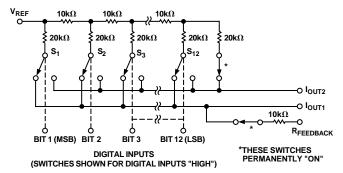

A simplified circuit of the DAC8143 is shown in Figure 10. An inversed R-2R ladder network consisting of silicon-chrome, thin-film resistors, and twelve pairs of NMOS current-steering switches. These switches steer binarily weighted currents into either  $I_{\rm OUT1}$  or  $I_{\rm OUT2}$ . Switching current to  $I_{\rm OUT1}$  or  $I_{\rm OUT2}$  yields a constant current in each ladder leg, regardless of digital input code. This constant current results in a constant input resistance at  $V_{\rm REF}$  equal to R (typically 11 k $\Omega$ ). The  $V_{\rm REF}$  input may be driven by any reference voltage or current, ac or dc, that is within the limits stated in the Absolute Maximum Ratings chart.

The twelve output current-steering switches are in series with the R-2R resistor ladder, and therefore, can introduce bit errors. It was essential to design these switches such that the switch "ON" resistance be binarily scaled so that the voltage drop across each switch remains constant. If, for example, Switch 1 of Figure 10 was designed with an "ON" resistance of  $10~\Omega$ , Switch 2 for  $20~\Omega$ , etc., a constant 5 mV drop would then be maintained across each switch.

To further ensure accuracy across the full temperature range, permanently "ON" MOS switches were included in series with the feedback resistor and the R-2R ladder's terminating resistor. The Simplified DAC Circuit, Figure 10, shows the location of these switches. These series switches are equivalently scaled to two times Switch 1 (MSB) and top Switch 12 (LSB) to maintain constant relative voltage drops with varying temperature. During any testing of the resistor ladder or  $R_{\rm FEEDBACK}$  (such as incoming inspection),  $V_{\rm DD}$  must be present to turn "ON" these series switches.

Figure 10. Simplified DAC Circuit

-6-

#### **ESD PROTECTION**

The DAC8143 digital inputs have been designed with ESD resistance incorporated through careful layout and the inclusion of input protection circuitry.

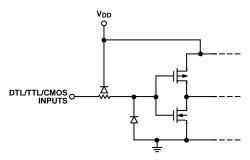

Figure 11 shows the input protection diodes. High voltage static charges applied to the digital inputs are shunted to the supply and ground rails through forward biased diodes.

These protection diodes were designed to clamp the inputs well below dangerous levels during static discharge conditions.

Figure 11. Digital Input Protection

#### **EQUIVALENT CIRCUIT ANALYSIS**

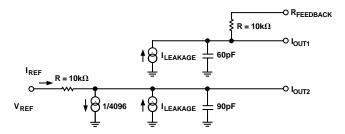

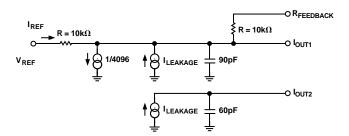

Figures 12 and 13 show equivalent circuits for the DAC8143's internal DAC with all bits LOW and HIGH, respectively. The reference current is switched to  $I_{OUT2}$  when all data bits are LOW, and to  $I_{OUT1}$  when all bits are HIGH. The  $I_{LEAKAGE}$  current source is the combination of surface and junction leakages to the substrate. The 1/4096 current source represents the constant 1-bit current drain through the ladder's terminating resistor.

Output capacitance is dependent upon the digital input code. This is because the capacitance of a MOS transistor changes with applied gate voltage. This output capacitance varies between the low and high values.

Figure 12. Equivalent Circuit (All Inputs LOW)

Figure 13. Equivalent Circuit (All Inputs HIGH)

#### DYNAMIC PERFORMANCE ANALOG OUTPUT IMPEDANCE

The output resistance, as in the case of the output capacitance, varies with the digital input code. This resistance, looking back into the  $I_{OUT1}$  terminal, varies between 11 k $\Omega$  (the feedback resistor alone when all digital input are LOW) and 7.5 k $\Omega$  (the feedback resistor in parallel with approximately 30 k $\Omega$  of the R-2R ladder network resistance when any single bit logic is HIGH). Static accuracy and dynamic performance will be affected by these variations.

The gain and phase stability of the output amplifier, board layout, and power supply decoupling will all affect the dynamic performance of the DAC8143. The use of a small compensation capacitor may be required when high speed operational amplifiers are used. It may be connected across the amplifier's feedback resistor to provide the necessary phase compensation to critically damp the output.

The considerations when using high speed amplifiers are:

- 1. Phase compensation (see Figures 16 and 17).

- Power supply decoupling at the device socket and use of proper grounding techniques.

#### **OUTPUT AMPLIFIER CONSIDERATIONS**

When using high speed op amps, a small feedback capacitor (typically 5 pF-30 pF) should be used across the amplifiers to minimize overshoot and ringing. For low speed or static applications, ac specifications of the amplifier are not very critical. In high speed applications, slew rate, settling time, openloop gain and gain/phase margin specifications of the amplifier should be selected for the desired performance. It has already been noted that an offset can be caused by including the usual bias current compensation resistor in the amplifier's noninverting input terminal. This resistor should not be used. Instead, the amplifier should have a bias current that is low over the temperature range of interest.

Static accuracy is affected by the variation in the DAC's output resistance. This variation is best illustrated by using the circuit of Figure 14 and the equation:

$$V_{ERROR} = V_{OS} \left( 1 + \frac{R_{FB}}{R_O} \right)$$

$$R_{PD} = R_{PD}$$

Figure 14. Simplified Circuit

REV. C –7–

Where  $R_0$  is a function of the digital code, and:

$R_O = 10 \text{ k}\Omega$  for more than four bits of Logic 1,

$R_O = 30 \text{ k}\Omega$  for any single bit of Logic 1.

Therefore, the offset gain varies as follows: at code 0011 1111 1111,

$$V_{ERROR1} = V_{OS} \left( 1 + \frac{10 \, k\Omega}{10 \, k\Omega} \right) = 2 \, V_{OS}$$

at code 0100 0000 0000,

$$V_{ERROR2} = V_{OS} \left( 1 + \frac{10 \, k\Omega}{30 \, k\Omega} \right) = 4/3 \, V_{OS}$$

The error difference is  $2/3 V_{OS}$ .

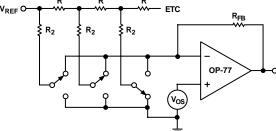

Since one LSB has a weight (for  $V_{REF}$  = +10 V) of 2.4 mV for the DAC8143, it is clearly important that  $V_{OS}$  be minimized, using either the amplifier's pulling pins, an external pulling network, or by selection of an amplifier with inherently low  $V_{OS}$ . Amplifiers with sufficiently low  $V_{OS}$  include OP77, OP97, OP07, OP27, and OP42.

#### INTERFACE LOGIC OPERATION

The microprocessor interface of the DAC8143 has been designed with multiple STROBE and LOAD inputs to maximize interfacing options. Control signals decoding may be done on chip or with the use of external decoding circuitry (see Figure 21).

Serial data is clocked into the input register and buffered output stage with  $STB_1$ ,  $STB_2$ , or  $STB_4$ . The strobe inputs are active on the rising edge.  $\overline{STB_3}$  may be used with a falling edge clock data.

Serial data output (SRO) follows the serial data input (SRI) by 12 clocked bits.

Holding any STROBE input at its selected state (i.e., STB<sub>1</sub>, STB<sub>2</sub> or STB<sub>4</sub> at logic HIGH or STB<sub>3</sub> at logic LOW) will act to prevent any further data input.

When a new data word has been entered into the input register, it is transferred to the DAC register by asserting both LOAD inputs.

The  $\overline{\text{CLR}}$  input allows asynchronous resetting of the DAC register to 0000 0000 0000. This reset does not affect data held in the input registers. While in unipolar mode, a CLEAR will result in the analog output going to 0 V. In bipolar mode, the output will go to  $-V_{\text{REF}}$ .

#### INTERFACE INPUT DESCRIPTION

STB<sub>1</sub> (Pin 4), STB<sub>2</sub> (Pin 8), STB<sub>4</sub> (Pin 11)—Input Register and Buffered Output Strobe. Inputs Active on Rising Edge. Selected to load serial data into input register and buffered output stage. See Table I for details.

STB<sub>3</sub> (Pin 10)—Input Register and Buffered Output Strobe Input. Active on Falling Edge. Selected to load serial data into input register and buffered output stage. See Table I for details.

$\overline{\text{LD}}_1$  (Pin 5),  $\overline{\text{LD}}_2$  (Pin 9)—Load DAC Register Inputs. Active Low. Selected together to load contents of input register into DAC register.

CLR (Pin 13)—Clear Input. Active Low. Asynchronous. When LOW, 12-bit DAC register is forced to a zero code (0000 0000 0000) regardless of other interface inputs.

NOTES:

- \* STROBE WAVEFORM IS INVERTED IF  $\overline{\text{STB}}_3$  IS USED TO STROBE SERIAL DATA BITS INTO INPUT REGISTER.

- \*\* DATA IS STROBED INTO AND OUT OF THE INPUT SHIFT REGISTER MSB FIRST.

Figure 15. Timing Diagram

-8-

REV. C

Table I. Truth Table

| Input R          | 43 Logic In<br>legister/<br>Output<br>STB <sub>3</sub> |                  | ol Inputs STB <sub>1</sub> | DAC Register CLR |        | ol Inputs $\overline{\text{LD}_{\scriptscriptstyle 1}}$ | DAC8143 Operation                                                                     | Notes |

|------------------|--------------------------------------------------------|------------------|----------------------------|------------------|--------|---------------------------------------------------------|---------------------------------------------------------------------------------------|-------|

| 0                | 1                                                      | 0                | <b>F</b><br>0              | X<br>X           | X<br>X | X<br>X                                                  | Serial Data Bit Loaded from SRI                                                       |       |

| 0                | ₹<br>1                                                 | 0                | 0                          | X<br>X           | X<br>X | X<br>X                                                  | into Input Register and Digital Output (SRO Pin) after 12 Clocked Bits.               | 2, 3  |

| 1<br>X<br>X<br>X | X<br>0<br>X<br>X                                       | X<br>X<br>1<br>X | X<br>X<br>X<br>1           |                  |        |                                                         | No Operation (Input Register and SRO)                                                 | 3     |

|                  |                                                        |                  |                            | 0                | X      | X                                                       | Reset DAC Register to Zero Code<br>(Code: 0000 0000 0000)<br>(Asynchronous Operation) | 1, 3  |

|                  |                                                        |                  |                            | 1 1              | 1<br>X | X<br>1                                                  | No Operation (DAC Register and SRO)                                                   | 3     |

|                  |                                                        |                  |                            | 1                | 0      | 0                                                       | Load DAC Register with the Contents of Input Register                                 | 3     |

#### NOTES

# APPLICATIONS INFORMATION UNIPOLAR OPERATION (2-QUADRANT)

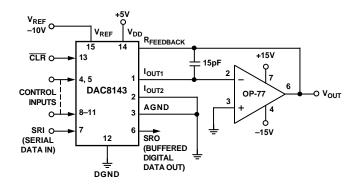

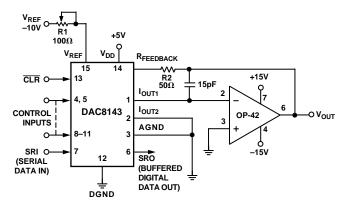

The circuit shown in Figures 16 and 17 may be used with an ac or dc reference voltage. The circuit's output will range between 0 V and +10(4095/4096) V depending upon the digital input code. The relationship between the digital input and the analog output is shown in Table II. The  $V_{REF}$  voltage range is the maximum input voltage range of the op amp or  $\pm 25$  V, whichever is lowest.

Table II. Unipolar Code Table

| Digital Inp | ut          | Nominal Analog Output<br>(V <sub>OUT</sub> as Shown           |

|-------------|-------------|---------------------------------------------------------------|

| MSB         | LSB         | in Figures 16 and 17)                                         |

| 111111      | 111111      | $-V_{REF} \left( \frac{4095}{4096} \right)$                   |

| 100000      | 000001      | $-V_{REF}\left(\frac{2049}{4096}\right)$                      |

| 100000      | 000000      | $-V_{REF}\left(\frac{2048}{4096}\right) = -\frac{V_{REF}}{2}$ |

| 011111      | 111111      | $-V_{REF}\left(\frac{2047}{4096}\right)$                      |

| 000000      | 0 0 0 0 0 1 | $-V_{REF}\left(\frac{1}{4096}\right)$                         |

| 000000      | 000000      | $-V_{REF}\left(\frac{0}{4096}\right) = 0$                     |

NOTES

<sup>2</sup>Nominal LSB magnitude for the circuits of Figures 16 and 17 is given by  $LSB = V_{REF} \left( \frac{1}{4096} \right)$  or  $V_{REF} (2^{-n})$ .

Figure 16. Unipolar Operation with High Accuracy Op Amp (2-Quadrant)

Figure 17. Unipolar Operation with Fast Op Amp and Gain Error Trimming (2-Quadrant)

$<sup>^{1}\</sup>overline{\text{CLR}}$  = 0 asynchronously resets DAC Register to 0000 0000, but has no effect on Input Register.

<sup>&</sup>lt;sup>2</sup>Serial data is loaded into Input Register MSB first, on edges shown. I is positive edge, I is negative edge.

<sup>&</sup>lt;sup>3</sup>0 = Logic LOW, 1 = Logic HIGH, X = Don't Care.

<sup>&</sup>lt;sup>1</sup>Nominal full scale for the circuits of Figures 16 and 17 is given by  $FS = -V_{REF} \left( \frac{4095}{4096} \right).$

In many applications, the DAC8143's zero scale error and low gain error, permit the elimination of external trimming components without adverse effects on circuit performance.

For applications requiring a tighter gain error than 0.024% at 25°C for the top grade part, or 0.048% for the lower grade part, the circuit in Figure 17 may be used. Gain error may be trimmed by adjusting R1.

The DAC register must first be loaded with all 1s. R1 is then adjusted until  $V_{OUT} = -V_{REF}$  (4095/4096). In the case of an adjustable  $V_{REF}$ , R1 and  $R_{FEEDBACK}$  may be omitted, with  $V_{REF}$  adjusted to yield the desired full-scale output.

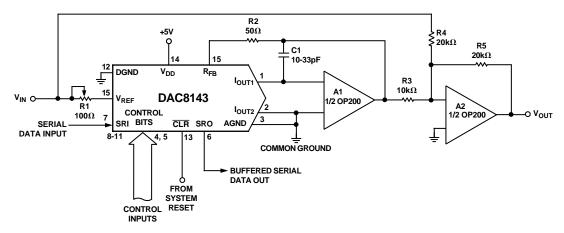

#### **BIPOLAR OPERATION (4-QUADRANT)**

Figure 18 details a suggested circuit for bipolar, or offset binary, operation. Table III shows the digital input-to-analog output relationship. The circuit uses offset binary coding. Twos complement code can be converted to offset binary by software inversion of the MSB or by the addition of an external inverter to the MSB input.

Resistor R3, R4 and R5 must be selected to match within 0.01% and must all be of the same (preferably metal foil) type to assure temperature coefficient match. Mismatching between R3 and R4 causes offset and full-scale error.

Calibration is performed by loading the DAC register with 1000 0000 0000 and adjusting R1 until  $V_{OUT}$  = 0 V. R1 and R2 may be omitted by adjusting the ratio of R3 to R4 to yield  $V_{OUT}$  = 0 V. Full scale can be adjusted by loading the DAC register with 1111 1111 1111 and adjusting either the amplitude of  $V_{REF}$  or the value of R5 until the desired  $V_{OUT}$  is achieved.

Table III. Bipolar (Offset Binary) Code Table

| Digital Input<br>MSB | LSB     | Nominal Analog Output<br>(V <sub>OUT</sub> as Shown in Figure 18) |

|----------------------|---------|-------------------------------------------------------------------|

| 11111111             | 1111    | $+V_{REF}\left(\frac{2047}{2048}\right)$                          |

| 10000000             | 0 0 0 1 | $+V_{REF}\left(\frac{1}{2048}\right)$                             |

| 10000000             | 0000    | 0                                                                 |

| 01111111             | 1111    | $-V_{REF}\left(\frac{1}{2048}\right)$                             |

| 0000 0000            | 0 0 0 1 | $-V_{REF} \left( \frac{2047}{2048} \right)$                       |

| 0000 0000            | 0 0 0 0 | $-V_{REF}\left(\frac{2048}{2048}\right)$                          |

NOTES

<sup>1</sup>Nominal full scale for the circuits of Figure 18 is given by

$$FS = V_{REF} \left( \frac{2047}{2048} \right)$$

<sup>2</sup>Nominal LSB magnitude for the circuits of Figure 18 is given by

$$LSB = V_{REF} \left( \frac{1}{2048} \right).$$

#### **DAISY-CHAINING DAC8143s**

Many applications use multiple serial input DACs that use numerous interconnecting lines for address decoding and data lines. In addition, they use some type of buffering to reduce loading on the bus. The DAC8143 is ideal for just such an application. It not only reduces the number of interconnecting lines, but also reduces bus loading. The DAC8143 can be daisy-chained with only three lines: one data line, one CLK line and one load line, see Figure 19.

Figure 18. Bipolar Operation (4-Quadrant, Offset Binary)

–10– REV. C

Figure 19. Multiple DAC8143s with Three-Wire Interface

#### ANALOG/DIGITAL DIVISION

The transfer function for the DAC8143 connect in the multiplying mode as shown in Figures 16 and 17 is:

$$V_O = -V_{IN} \left( \frac{A_1}{2^1} + \frac{A_2}{2^2} + \frac{A_3}{2^3} + \dots \frac{A_{12}}{2^{12}} \right)$$

where  $A_{\rm X}$  assumes a value of 1 for an "ON" bit and 0 for an "OFF" bit.

The transfer function is modified when the DAC is connected in the feedback of an operational amplifier as shown in Figure 20 and is:

$$V_{O} = \left(\frac{-V_{IN}}{\frac{A_{1}}{2^{1}} + \frac{A_{2}}{2^{2}} + \frac{A_{3}}{2^{3}} + \dots \frac{A_{12}}{2^{12}}}\right)$$

The above transfer function is the division of an analog voltage  $(V_{REF})$  by a digital word. The amplifier goes to the rails with all bits "OFF" since division by zero is infinity. With all bits "ON" the gain is 1 ( $\pm 1$  LSB). The gain becomes 4096 with the LSB, Bit 12, "ON".

Figure 20. Analog/Digital Divider

#### **APPLICATION TIPS**

In most applications, linearity depends on the potential of  $I_{OUT1,}$   $I_{OUT2,}$  and AGND (Pins 1, 2 and 3) being exactly equal to each other. In most applications, the DAC is connected to an external op amp with its noninverting input tied to ground (see Figures 16 and 17). The amplifier selected should have a low input bias current and low drift over temperature. The amplifier's input offset voltage should be nulled to less than  $\pm 200~\mu V$  (less than 10% of 1 LSB).

The operational amplifier's noninverting input should have a minimum resistance connection to ground; the usual bias current compensation resistor should not be used. This resistor can cause a variable offset voltage appearing as a varying output error. All grounded pins should tie to a single common ground point, avoiding ground loops. The  $V_{\rm DD}$  power supply should have a low noise level with no transients greater than +17 V.

It is recommended that the digital inputs be taken to ground or  $V_{DD}$  via a high value (1  $M\Omega)$  resistor; this will prevent the accumulation of static charge if the PC card is disconnected from the system.

Peak supply current flows as the digital input pass through the transition region (see Figure 4). The supply current decreases as the input voltage approaches the supply rails ( $V_{DD}$  or DGND), i.e., rapidly slewing logic signals that settle very near the supply rails will minimize supply current.

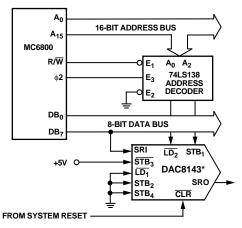

#### **INTERFACING TO THE MC6800**

As shown in Figure 21, the DAC8143 may be interfaced to the 6800 by successively executing memory WRITE instruction while manipulating the data between WRITEs, so that each WRITE presents the next bit.

In this example, the most significant bits are found in memory locations 0000 and 0001. The four MSBs are found in the lower half of 0000, the eight LSBs in 0001. The data is taken from the  $DB_7$  line.

The serial data loading is triggered by  $STB_4$  which is asserted by a decoded memory WRITE to a memory location,  $R/\overline{W}$ , and  $\Phi 2$ . A WRITE to another address location transfers data from input register to DAC register.

\*ANALOG CIRCUITRY OMITTED FOR SIMPLICITY

Figure 21. DAC8143—MC6800 Interface

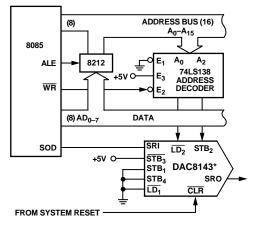

#### **DAC8143 INTERFACE TO THE 8085**

The DAC8143's interface to the 8085 microprocessor is shown in Figure 22. Note that the microprocessor's SOD line is used to present data serially to the DAC.

Data is strobed into the DAC8143 by executing memory write instructions. The strobe 2 input is generated by decoding an address location and  $\overline{WR}$ . Data is loaded into the DAC register with a memory write instruction to another address location.

Serial data supplied to the DAC8143 must be present in the right-justified format in registers H and L of the microprocessor.

\*ANALOG CIRCUITRY OMITTED FOR SIMPLICITY

Figure 22. DAC8143—8085 Interface

#### DAC8143 INTERFACE TO THE 68000

Figure 23 shows the DAC8143 configured to the 68000 microprocessor. Serial data input is similar to that of the 6800 in Figure 21.

Figure 23. DAC8143 to 68000 μP Interface

#### **OUTLINE DIMENSIONS**

Dimensions are shown in inches and (mm).

-12-

0.840 (21.34) 0.745 (18.92) 0.280 (7.11) 0.240 (6.10) 0.325 (8.25) 0.300 (7.62) 0.060 (1.52) 0.015 (0.38) 0.195 (4.95) 0.210 (5.33) MAX 0.115 (2.93) 0.130 0.160 (4.06) 0.160 (4.06) 0.015 (0.381) 0.022 (0.558) 0.100 0.070 (1.77) SEATING 0.008 (0.204) 0.014 (0.356) (2.54) 0.045 (1.15)

16-Lead Plastic DIP

(N-16)

0.4133 (10.50) 0.3977 (10.00) 0.2992 (7.60) 0.2914 (7.40) 0.4193 (10.65) 0.3937 (10.00) H → → 0.050 (1.27) BSC PIN 1 0.1043 (2.65) 0.0291 (0.74) < 45° 0.0926 (2.35) 0.0098 (0.25) 0.0192 (0.49) SEATING 0.0125 (0.32) 0.0118 (0.30) 0.0500 (1.27) 0.0040 (0.10) 0.0138 (0.35) 0.0157 (0.40) 0.0091 (0.23)

16-Lead SOIC (R-16W)

REV. C

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

DAC8143FSZ DAC8143FPZ DAC8143FSZ-REEL