# 3.3V Center Spread-Spectrum EconOscillator™

#### **General Description**

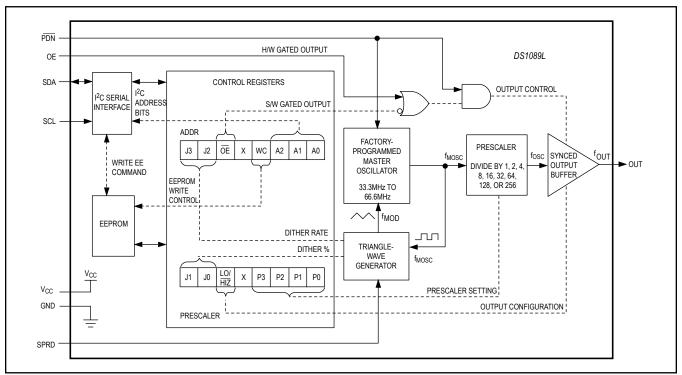

The DS1089L is a clock generator that produces a spread-spectrum (dithered) square-wave output of frequencies from 130kHz to 66.6MHz. The DS1089L is shipped from the factory programmed at a specific frequency. The DS1089L is pin-for-pin compatible with the DS1087L, however, the DS1089L dithers at equal percentages above and below the center frequency. The user still has access to the internal frequency divider, selectable ±1%, ±2%, ±4%, or ±8% dithered output, dithering rate, and programmable output power-down/disable mode through an I<sup>2</sup>C-compatible programming interface. All the device settings are stored in nonvolatile (NV) EEPROM allowing it to operate in stand-alone applications. The DS1089L also has power-down and output-enable control pins for power-sensitive applications.

#### **Applications**

- Printers

- Copiers

- Computer Peripherals

- POS Terminals

- Cable Modems

Pin Configuration and Typical Operating Circuits appear at end of data sheet.

#### **Features**

- Factory-Programmed Square-Wave Generator from 33.3MHz to 66.6MHz

- Center Frequency Remains Constant Independent of Dither Percentage

- No External Timing Components Required

- EMI Reduction

- Variable Dither Frequency

- User Programmable Down to 130kHz with Divider (Dependent on Master Oscillator Frequency)

- ±1%, ±2%, ±4%, or ±8% Selectable Dithered Output

- Glitchless Output-Enable Control

- I<sup>2</sup>C-Compatible Serial Interface

- Nonvolatile Settings

- Power-Down Mode

- Programmable Output Power-Down/Disable Mode

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE      |  |

|---------------|----------------|------------------|--|

| DS1089LU-yxx* | -40°C to +85°C | 8 μSOP (118 mil) |  |

<sup>\*</sup>See Standard Frequency Options Table.

### **Standard Frequency Options**

| PART         | FREQUENCY (MHz)  | SPREAD (±%)   | DITHER FREQUENCY                        |

|--------------|------------------|---------------|-----------------------------------------|

| DS1089LU-21G | 14.7456          | 1             | f <sub>MOSC</sub> /4096                 |

| DS1089LU-4CL | 18.432           | 2             | f <sub>MOSC</sub> /4096                 |

| DS1089LU-22F | 24.576           | 1             | f <sub>MOSC</sub> /2048                 |

| DS1089LU-23C | 33.3             | 1             | f <sub>MOSC</sub> /4096                 |

| DS1089LU-450 | 50.0             | 2             | f <sub>MOSC</sub> /4096                 |

| DS1089LU-866 | 66.6             | 4             | f <sub>MOSC</sub> /4096                 |

| DS1089LU-yxx | Fixed up to 66.6 | 1, 2, 4, or 8 | f <sub>MOSC</sub> /2048 or 4096 or 8192 |

Add "/T" for Tape and Reel.

Custom frequencies available, contact factory.

EconOscillator is a trademark of Maxim Integrated Products, Inc.

### DS1089L

# 3.3V Center Spread-Spectrum EconOscillator™

## **Absolute Maximum Ratings**

| Voltage on VCC Relative to Ground0.5V to +6.0V          | Programming Temperature Range0°C to +70°C      |

|---------------------------------------------------------|------------------------------------------------|

| Voltage on SPRD, PDN, OE, SDA,                          | Storage Temperature Range55°C to +125°C        |

| SCL Relative to Ground*0.5V to (V <sub>CC</sub> + 0.5V) | Soldering Temperature See IPC/JEDEC J-STD-020A |

| Operating Temperature Range40°C to +85°C                |                                                |

<sup>\*</sup>This voltage must not exceed 6.0V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                 | SYMBOL          | CONDITION | MIN                   | TYP | MAX               | UNITS |

|---------------------------|-----------------|-----------|-----------------------|-----|-------------------|-------|

| Supply Voltage            | V <sub>CC</sub> | (Note 1)  | 2.7                   | 3.3 | 3.6               | V     |

| High-Level Input Voltage  |                 |           | 0.7 × 1/              |     | V <sub>CC</sub> + | \/    |

| (SDA, SCL, SPRD, PDN, OE) | V <sub>IH</sub> |           | 0.7 x V <sub>CC</sub> |     | 0.3               | V     |

| Low-Level Input Voltage   | .,,             |           | 0.0                   |     | 0.3 x             |       |

| (SDA, SCL, SPRD, PDN, OE) | V <sub>IL</sub> |           | -0.3                  |     | $V_{CC}$          | V     |

### **DC Electrical Characteristics**

$(V_{CC} = +2.7V \text{ to } +3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.})$

| PARAMETER                       | SYMBOL           | CONDITION                                                      | MIN | TYP | MAX | UNITS |

|---------------------------------|------------------|----------------------------------------------------------------|-----|-----|-----|-------|

| High-Level Output Voltage (OUT) | V <sub>OH</sub>  | $I_{OH}$ = -4mA, $V_{CC}$ = min                                | 2.4 |     |     | V     |

| Low-Level Output Voltage (OUT)  | V <sub>OL</sub>  | I <sub>OL</sub> = 4mA                                          |     |     | 0.4 | V     |

| Low-Level Output Voltage (SDA)  | V <sub>OL1</sub> | 3mA sink current                                               |     |     | 0.4 | V     |

|                                 | V <sub>OL2</sub> | 6mA sink current                                               |     |     | 0.6 | V     |

| High-Level Input Current        | I <sub>IH</sub>  | V <sub>IH</sub> = V <sub>CC</sub>                              |     |     | 1   | μA    |

| Low-Level Input Current         | I <sub>IL</sub>  | V <sub>IL</sub> = 0V                                           | -1  |     |     | μA    |

| Supply Current (Active)         | Icc              | C <sub>L</sub> = 15pF, f <sub>OUT</sub> = f <sub>MOSCmax</sub> |     |     | 12  | mA    |

| Standby Current (Power-Down)    | Iccq             | Power-down mode                                                |     |     | 10  | μA    |

### **Master Oscillator Characteristics**

$(V_{CC} = +2.7V \text{ to } +3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.})$

| PARAMETER                                | SYMBOL                             | CONDITION                                                   |                                                                 | MIN            | TYP                      | MAX   | UNITS |

|------------------------------------------|------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|----------------|--------------------------|-------|-------|

| Internal Master Oscillator<br>Frequency  | f <sub>MOSC</sub>                  |                                                             |                                                                 | 33.3           |                          | 66.6  | MHz   |

| Master Oscillator Frequency<br>Tolerance | $\frac{\Delta f_{MOSC}}{f_{MOSC}}$ | V <sub>CC</sub> = 3.3V,<br>T <sub>A</sub> = +25°C (Notes 2, | V <sub>CC</sub> = 3.3V,<br>T <sub>A</sub> = +25°C (Notes 2, 10) |                |                          |       | %     |

| Voltage Frequency<br>Variation           | $\frac{\Delta f}{f_{MOSC}}$        | T <sub>A</sub> = +25°C (Note 3)                             |                                                                 | -0.75          |                          | +0.75 | %     |

| Temperature Frequency Variation          | Δf                                 | V <sub>CC</sub> = 3.3V,                                     | T <sub>A</sub> = 0°C to +85°C                                   | -0.75          |                          | +0.75 | %     |

| (Note 4)                                 | f <sub>MOSC</sub>                  | f <sub>OUT</sub> = f <sub>MOSCmax</sub>                     | $T_A = -40$ °C to 0°C                                           | -2.00          |                          | +0.75 | 70    |

|                                          |                                    | J3 = J2 = GND                                               |                                                                 |                | ±1                       |       |       |

| Dither Frequency Range                   |                                    | $J3 = GND$ , $J2 = V_{CC}$                                  |                                                                 |                | ±2                       |       | %     |

| (Note 5)                                 |                                    | $J3 = V_{CC}$ , $J2 = GND$                                  |                                                                 |                | ±4                       |       | 70    |

|                                          |                                    | $J3 = J2 = V_{CC}$                                          |                                                                 |                | ±8                       |       |       |

|                                          |                                    |                                                             |                                                                 | f <sub>M</sub> | OSC / 204                | 8     |       |

| Dither Frequency (Note 5)                | f <sub>MOD</sub>                   | $J1 = V_{CC}$ , $J0 = GND$                                  |                                                                 | f <sub>M</sub> | OSC / 409                | 96    | Hz    |

| (1.16.6.6.7)                             |                                    | J1 = J0 = V <sub>CC</sub>                                   |                                                                 |                | f <sub>MOSC</sub> / 8192 |       |       |

### **AC Electrical Characteristics**

$(V_{CC}$  = +2.7V to +3.6V,  $T_A$  = -40°C to +85°C.)

| PARAMETER                                      | SYMBOL                               | CONDITION | MIN | TYP | MAX | UNITS           |

|------------------------------------------------|--------------------------------------|-----------|-----|-----|-----|-----------------|

| Frequency Stable After PRESCALER Change        |                                      |           |     |     | 1   | Period          |

| Power-Up Time                                  | t <sub>POR</sub> + t <sub>STAB</sub> | (Note 6)  |     | 40  | 200 | μs              |

| Enable of OUT After Exiting Power-Down Mode    | <sup>t</sup> STAB                    | (Note 6)  |     |     | 512 | clock<br>cycles |

| OUT Disabled After Entering<br>Power-Down Mode | t <sub>PDN</sub>                     |           |     | 7   |     | μs              |

| Load Capacitance                               | CL                                   |           |     | 15  | 50  | pF              |

| Output Duty Cycle (f <sub>OUT</sub> )          |                                      |           |     | 50  | ·   | %               |

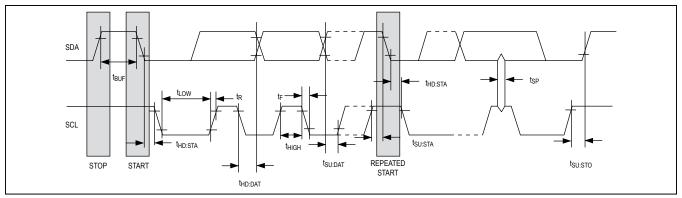

### AC Electrical Characteristics—I<sup>2</sup>c Interface

$(V_{CC} = +2.7 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted. Timing referenced to } V_{IL(MAX)} \text{ and } V_{IH(MIN)}.)$

| PARAMETER                                       | SYMBOL              | CONDITIONS | MIN TYP                | MAX | UNITS |

|-------------------------------------------------|---------------------|------------|------------------------|-----|-------|

| SCL Clock Frequency                             | f <sub>SCL</sub>    | (Note 7)   | 0                      | 400 | kHz   |

| Bus Free Time Between Stop and Start Conditions | t <sub>BUF</sub>    |            | 1.3                    |     | μs    |

| Hold Time (Repeated) Start Condition            | t <sub>HD:STA</sub> |            | 0.6                    |     | μs    |

| Low Period of SCL                               | t <sub>LOW</sub>    |            | 1.3                    |     | μs    |

| High Period of SCL                              | tHIGH               |            | 0.6                    |     | μs    |

| Data Hold Time                                  | t <sub>HD:DAT</sub> |            | 0                      | 0.9 | μs    |

| Data Setup Time                                 | t <sub>SU:DAT</sub> |            | 100                    |     | ns    |

| Start Setup Time                                | t <sub>SU:STA</sub> |            | 0.6                    |     | μs    |

| SDA and SCL Rise Time                           | t <sub>R</sub>      | (Note 8)   | 20 + 0.1C <sub>B</sub> | 300 | ns    |

| SDA and SCL Fall Time                           | t <sub>F</sub>      | (Note 8)   | 20 + 0.1C <sub>B</sub> | 300 | ns    |

| Stop Setup Time                                 | t <sub>SU:STO</sub> |            | 0.6                    |     | μs    |

| SDA and SCL Capacitive Loading                  | C <sub>B</sub>      | (Note 8)   |                        | 400 | pF    |

| EEPROM Write Time                               | t <sub>WR</sub>     | (Note 9)   | 10                     | 20  | ms    |

### **Nonvolatile Memory Characteristics**

$(V_{CC} = +2.7V \text{ to } +3.6V.)$

| PARAMETER | SYMBOL | CONDITION | MIN    | TYP | MAX | UNITS |

|-----------|--------|-----------|--------|-----|-----|-------|

| Writes    |        | +70°C     | 10,000 |     |     |       |

- Note 1: All voltages are referenced to ground.

- Note 2: This is the absolute accuracy of the master oscillator frequency at the default settings with spread disabled.

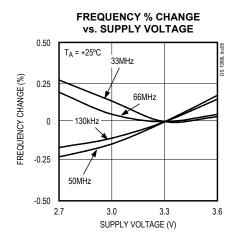

- Note 3: This is the change that is observed in master oscillator frequency with changes in voltage at  $T_A = +25$ °C.

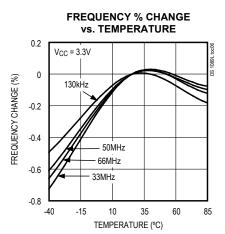

- Note 4: This is the change that is observed in master oscillator frequency with changes in temperature at V<sub>CC</sub> = 3.3V.

- Note 5: The dither deviation of the master oscillator frequency is bidirectional and results in an output frequency centered at the undithered frequency.

- Note 6: This indicates the time elapsed between power-up and the output becoming active. An on-chip delay is intentionally introduced to allow the oscillator to stabilize. t<sub>STAB</sub> is equivalent to 512 master clock cycles and will depend on the programmed master oscillator frequency.

- Note 7: Timing shown is for fast-mode (400kHz) operation. This device is also backward compatible with I2C standard-mode timing.

- Note 8: C<sub>B</sub>—total capacitance of one bus line in picofarads.

- **Note 9:** EEPROM write time applies to all the EEPROM memory and SRAM shadowed EEPROM memory when WC = 0. The EEPROM write time begins after a stop condition occurs.

- Note 10:Typical frequency shift due to aging is ±0.25%. Aging stressing includes Level 1 moisture reflow conditioning (24hr) +125°C bake, 168hr +85°C/85°RH moisture soak, and three solder reflow passes +269 +0/-5°C peak) followed by 408hr max V<sub>CC</sub> biased 125°C HTOL, 500 temperature cycles at -55°C to +125°C, 96hr +130°C/85%RH/3,6V HAST and 168hr +121°C/2 ATM Steam/Unbiased Autoclave.

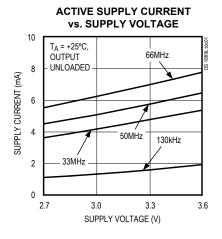

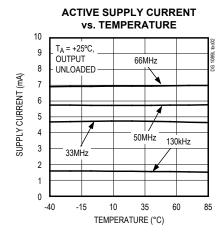

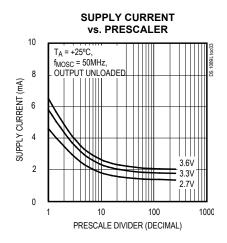

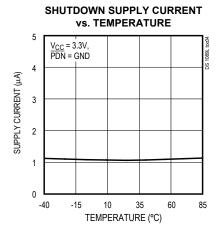

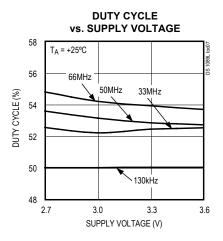

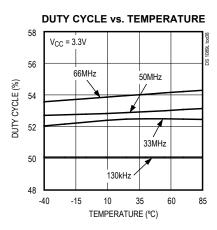

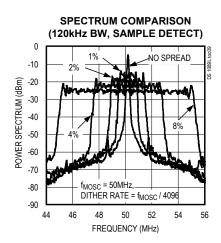

## **Typical Operating Characteristics**

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# **Typical Operating Characteristics (continued)**

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

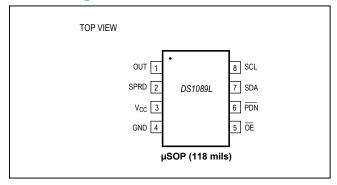

## **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                             |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUT             | Oscillator Output                                                                                                                                                    |

| 2   | SPRD            | Dither Enable. When the pin is high, the dither is enabled. When the pin is low, the dither is disabled.                                                             |

| 3   | V <sub>CC</sub> | Power Supply                                                                                                                                                         |

| 4   | GND             | Ground                                                                                                                                                               |

| 5   | OE              | Output Enable. When the pin is high, the output buffer is enabled. When the pin is low, the output is disabled but the internal master oscillator is still on.       |

| 6   | PDN             | Power-Down. When the pin is high, the master oscillator is enabled. When the pin is low, the master oscillator and the output buffer are disabled (power-down mode). |

| 7   | SDA             | I <sup>2</sup> C Serial Data. This pin is for serial data transfer to and from the device.                                                                           |

| 8   | SCL             | I <sup>2</sup> C Serial Clock. This pin is used to clock data into and out of the device.                                                                            |

### **Detailed Description**

#### **Master Oscillator**

The internal master oscillator is capable of generating a square wave with a 33.3MHz to 66.6MHz frequency range. The master oscillator frequency (f<sub>MOSC</sub>) is factory programmed, and is specified in the *Ordering Information*.

#### Prescaler

The user can program the prescaler divider to produce an output frequency ( $f_{OUT}$ ) as low as 130kHz using bits P0, P1, P2, and P3 in the PRESCALER register. The output frequency can be calculated using Equation 1. Any value programmed greater than  $2^8$  will be decoded as  $2^8$ . See Table 1 for prescaler divider settings.

#### **Equation 1**

Output Frequency (Hz)

$$f_{OSC} = \frac{f_{MOSC}}{2^x}$$

where x = P3, P2, P1, P0

**Table 1. Prescaler Divider Settings**

| BITS P3, P2,<br>P1, P0 | 2× = | fout = fosc             |

|------------------------|------|-------------------------|

| 0000                   | 1    | f <sub>MOSC</sub>       |

| 0001                   | 2    | f <sub>MOSC</sub> / 2   |

| 0010                   | 4    | f <sub>MOSC</sub> / 4   |

| 0011                   | 8    | f <sub>MOSC</sub> / 8   |

| 0100                   | 16   | f <sub>MOSC</sub> / 16  |

| 0101                   | 32   | f <sub>MOSC</sub> / 32  |

| 0110                   | 64   | f <sub>MOSC</sub> / 64  |

| 0111                   | 128  | f <sub>MOSC</sub> / 128 |

| 1000                   | 256  | f <sub>MOSC</sub> / 256 |

|                        |      |                         |

| 1111                   | 256  | f <sub>MOSC</sub> / 256 |

#### **Output Control**

Two user control signals control the output. The output enable pin (OE) gates the output buffer and the power-down pin (PDN) disables the master oscillator and turns off the output for power-sensitive applications. (**Note:** the power-down command must persist for at least two output frequency cycles plus 10µs for deglitching purposes.) On power-up, the output is disabled until power is stable and the master oscillator has generated 512 clock cycles.

Additionally, the OE input is OR'ed with the  $\overline{OE}$  bit in the ADDR register, allowing for either hardware or software gating of the output waveform (see the *Block Diagram*).

Both controls feature a synchronous enable, which ensures that there are no output glitches when the output is enabled. The synchronous enable also ensures a constant time interval (for a given frequency setting) from an enable signal to the first output transition.

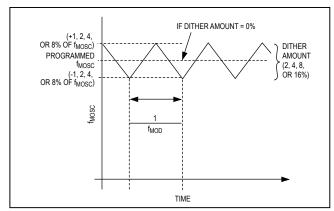

#### **Dither Generator**

The DS1089L has the ability to reduce radiated emission peaks. The output frequency can be dithered by  $\pm 1\%$ ,  $\pm 2\%$ ,  $\pm 4\%$ , or  $\pm 8\%$  symmetrically around the programmed center frequency. Although the output frequency changes when the dither is enabled, the duty cycle does not change.

The dither rate ( $f_{MOD}$ ) is controlled by the J0 and J1 bits in the PRESCALER register and is enabled with the SPRD pin. The maximum spectral attenuation occurs when the prescaler is set to 1. The spectral attenuation is reduced by 2.7dB for every factor of 2 that is used in the prescaler. This happens because the prescaler's divider function tends to average the dither in creating the lower frequency. However, the most stringent spectral emission limits are imposed on the higher frequencies where the prescaler is set to a low divider ratio.

A triangle-wave generator injects an offset element into the master oscillator to dither its output. The dither rate can be calculated based on the master oscillator frequency (see Equation 2).

#### **Equation 2**

$$f_{MOD} = \frac{f_{MOSC}}{n}$$

where  $f_{MOD}$  = dither frequency,  $f_{MOSC}$  = master oscillator frequency, and n = divider setting (see Table 2).

#### **Dither Percentage Settings**

The dither amplitude (measured in percentage of the master oscillator center frequency) is set using the J2 and J3 bits in the ADDR register. This circuit uses a sense current from the master oscillator bias circuit to adjust the amplitude of the triangle-wave signal to a voltage level that modulates the master oscillator to a percentage of its factory-programmed center frequency. This percentage is set in the application to be  $\pm 1\%$ ,  $\pm 2\%$ ,  $\pm 4\%$ , or  $\pm 8\%$  (see Table 3).

The location of bits P3, P2, P1, P0, J1, and J0 in the PRESCALER register and bits J3 and J2 in the ADDR register are shown in the *Register Summary* section.

**Table 2. Dither Frequency Settings**

| BITS J1, J0 | DITHER FREQUENCY        |

|-------------|-------------------------|

| 00          | No dither               |

| 01          | f <sub>MOSC</sub> /2048 |

| 10          | f <sub>MOSC</sub> /4096 |

| 11          | f <sub>MOSC</sub> /8192 |

**Table 3. Dither Percentage Settings**

| BITS J3, J2 | DITHER AMOUNT |

|-------------|---------------|

| 00          | ±1%           |

| 01          | ±2%           |

| 10          | ±4%           |

| 11          | ±8%           |

When dither is enabled (by selecting a dither frequency setting greater than 0 with SPRD high), the master oscillator frequency is dithered around the center frequency by the selected percentage from the programmed f<sub>MOSC</sub> (see Figure 2). For example, if f<sub>MOSC</sub> is programmed to 40MHz (factory setting) and the dither amount is programmed to ±1%, the frequency of f<sub>MOSC</sub> will dither between 39.6MHz and 40.4MHz at a modulation frequency determined by the selected dither frequency. Continuing with the same example, if J1 = 0 and J0 = 1, selecting f<sub>MOSC</sub>/2048, then the dither frequency would be 19.531kHz.

#### **Register Summary**

The DS1089L registers are used to change the dither amount, output frequency, and slave address. A bit summary of the registers is shown in Table 4. Once programmed into EEPROM, the settings only need to be reprogrammed if it is desired to reconfigure the device.

#### PRESCALER Register

Dither Frequency. The J1 and J0 bits Bits 7 to 6: control the dither frequency applied to the output. See Table 2 for divider settings. If either of bits J1 or J0 is high and SPRD is

high, dither is enabled.

Bit 5: Output Low or Hi-Z. The LO/HIZ bit determines the state of the output during power-down. While the output is deactivated, if the LO/HIZ bit is set to 0, the output will be high impedance (high-Z). If the LO/HIZ bit is set to 1, the output will be driven low.

Bit 4: Reserved.

Bits 3 to 0: Prescaler Divider. The prescaler bits (bits P3 to P0) divide the master oscillator frequency by  $2^x$  where x can be from 0 to 8. Any prescaler bit value entered that is greater than 8 will decode as 8. See Table 1 for prescaler settings.

Figure 2. Output Frequency vs. Dither Rate

#### **ADDR Register**

Bits 7 to 6: Dither Percentage. The J3 and J2 bits control the selected dither amplitude (%). When both J3 and J2 are set to 0, the default dither rate is ±1%.

Output Enable. The  $\overline{OE}$  bit and the OE pin Bit 5: state determine if the output is on when the device is active ( $\overline{PDN} = V_{IH}$ ). If (OE = 0 OR OE is high) AND the PDN pin is high, the output will be driven.

Bit 4: Reserved.

Bit 3: Write Control. The WC bit determines if the EEPROM is to be written after register contents have been changed. If WC = 0 (default), EEPROM is written automatically after a write. If WC = 1, the EEPROM is only written when the WRITE EE command is issued. See the WRITE EE Command section for more information.

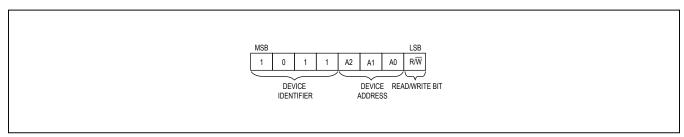

Bits 2 to 0: Address. The A0, A1, A2 bits determine the lower nibble of the I2C slave address.

Table 4. Register Summary

| _         |      |      |             |            |    |      |         |        |    |           |     |

|-----------|------|------|-------------|------------|----|------|---------|--------|----|-----------|-----|

| REGISTER  | ADDR | BIT7 | BINARY BIT0 |            |    | BIT0 | DEFAULT | ACCESS |    |           |     |

| PRESCALER | 02h  | J1   | J0          | LO/<br>HIZ | Х  | P3   | P2      | P1     | P0 | xx00xxxxb | R/W |

| ADDR      | 0Dh  | J3   | J2          | ŌĒ         | х  | WC   | A2      | A1     | A0 | xx100000b | R/W |

| WRITE EE  | 3Fh  |      |             |            | No | Data |         |        |    | _         | _   |

X = "don't care"

x = values depend on custom settings

# 3.3V Center Spread-Spectrum EconOscillator™

#### **WRITE EE Command**

The WRITE EE command is useful in closed-loop applications where the registers are frequently written. In applications where the register contents are frequently written, the WC bit should be set to 1 to prevent wearing out the EEPROM. Regardless of the value of the WC

bit, the value of the ADDR register is always written immediately to EEPROM. When the WRITE EE command has been received, the contents of the registers are written into the EEPROM, thus locking in the register settings.

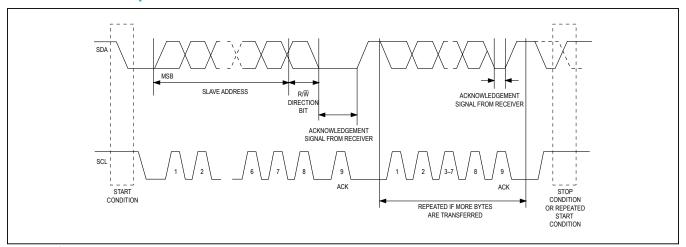

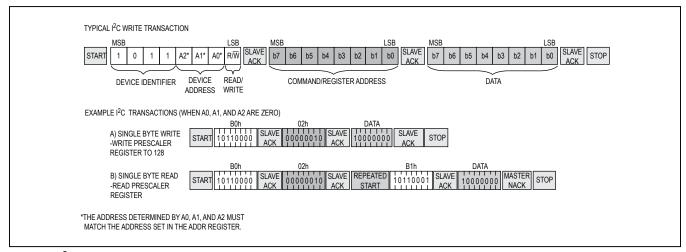

### I<sup>2</sup>C Serial Port Operation

Figure 3. I2C Data Transfer Protocol

Figure 4. Slave Address Byte

Figure 5. I2C AC Characteristics

Figure 6. I2C Transactions

### **Applications Information**

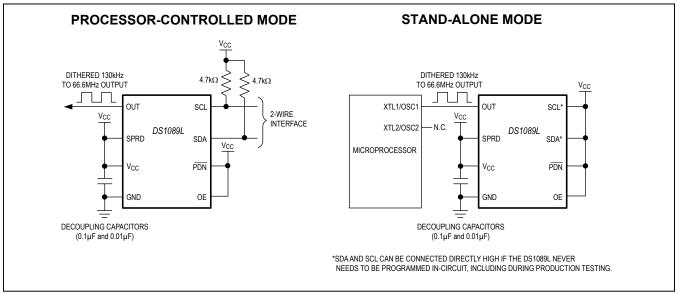

#### **Power-Supply Decoupling**

To achieve the best results when using the DS1089L, decouple the power supply with  $0.01\mu F$  and  $0.1\mu F$  high-quality, ceramic, surface-mount capacitors. Surface-mount components minimize lead inductance, which improves performance, and ceramic capacitors

tend to have adequate high-frequency response for decoupling applications. These capacitors should be placed as close to the  $V_{CC}$  and GND pins as possible.

#### **Stand-Alone Mode**

SCL and SDA cannot be left floating even in stand-alone mode. If the DS1089L will never need to be programmed in-circuit, including during production testing, SDA and SCL can be connected high.

# **Typical Operating Circuits**

## **Pin Configuration**

### **Chip Topology**

TRANSISTOR COUNT: 5985

SUBSTRATE CONNECTED TO GROUND

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

## DS1089L

# 3.3V Center Spread-Spectrum EconOscillator™

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                  | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------|------------------|

| 2                  | 5/06             |                                              | _                |

| 3                  | 2/15             | Removed automotive reference from data sheet | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# **Maxim Integrated:**

DS1089LU-140+ DS1089LU-140+T DS1089LU-21G+ DS1089LU-22F+ DS1089LU-22F+T DS1089LU-23C+

DS1089LU-266+ DS1089LU-450+ DS1089LU-4CL+ DS1089LU-4CL+T DS1089LU-866+ DS1089LU-A29+

DS1089LU-A29+T DS1089LU-C29+ DS1089LU-C29+T DS1089LU-F20+ DS1089LU-H1H+ DS1089LU-H1R+

DS1089LU-140+W DS1089LU-C29+W DS1089LU-A29+TW