# DS33X162/DS33X161/DS33X82/DS33X81/ DS33X42/DS33X41/DS33X11/DS33W41/DS33W11 Ethernet Over PDH Mapping Devices

# General Description

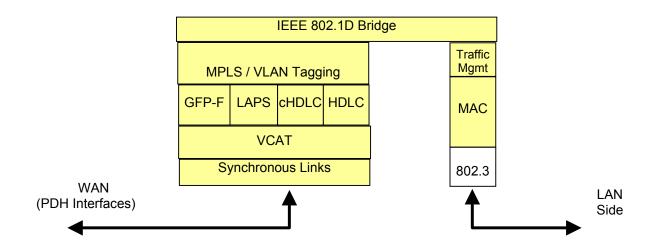

The DS33X162 family of semiconductor devices extend 10/100/1000Mbps Ethernet LAN segments by encapsulating MAC frames in GFP-F, HDLC, cHDLC, or X.86 (LAPS) for transmission over PDH/TDM data streams. The devices support the Ethernet over PDH (EoPDH) standards for the delivery of Ethernet Access Services, including eLAN, eLINE, and VLAN. The multiport devices support VCAT/LCAS for dynamic link aggregation. The serial links support bidirectional synchronous interconnect up to 52Mbps over xDSL, T1/E1/J1, T3/E3, or V.35/Optical.

The devices perform store-and-forward of frames with Ethernet traffic conditioning and bridging functions at wire speed. The programmability of classification, priority queuing, encapsulation, and bundling allows great flexibility in providing various Ethernet services. OAM flows can be extracted and inserted by an external processor to manage the Ethernet service.

The voice ports of the DS33W41 and DS33W11 easily connect to external codecs for integrated voice and data service applications.

**Applications**

Bonded Transparent LAN Service LAN Extension Ethernet Delivery Over T1/E1/J1, T3/E3, OC-1/EC-1, G.SHDSL, or HDSL2/4

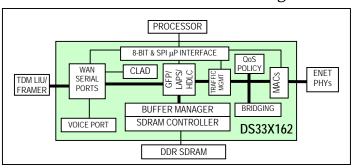

## Functional Diagram

Features

- ♦ 10/100/1000 IEEE 802.3 MAC (MII/RMII/GMII) with Autonegotiation and Flow Control

- **♦** GFP-F/LAPS/HDLC/cHDLC Encapsulation

- VCAT/LCAS Link Aggregation for Up to 16 Links

- Supports Up to 200ms Differential Delay

- ♦ Quality of Service (QoS) Support

- ♦ VLAN, Q-in-Q, 802.1p, and DSCP Support

- ♦ Ethernet Bridging and Filtering

- ♦ Add/Drop OAM Frames from μP Interface

- Traffic Shaping Through CIR/CBS Policing

- External 256Mb, 125MHz DDR SDRAM Buffer

- **♦** Parallel and SPI™ Microprocessor Interfaces

- ◆ 1.8V, 2.5V, 3.3V Supplies

- ♦ IEEE 1149.1 JTAG Support

Features continued in Section 2.

# Ordering Information

| PART      |     | PORTS    |       | PIN-           |

|-----------|-----|----------|-------|----------------|

| PARI      | TDM | ETHERNET | VOICE | <b>PACKAGE</b> |

| DS33X162+ | 16  | 2        | 0     | 256 CSBGA      |

| DS33X161+ | 16  | 1        | 0     | 256 CSBGA      |

| DS33X82+  | 8   | 2        | 0     | 256 CSBGA      |

| DS33X81+  | 8   | 1        | 0     | 256 CSBGA      |

| DS33X42+  | 4   | 2        | 0     | 256 CSBGA      |

| DS33X41+  | 4   | 1        | 0     | 256 CSBGA      |

| DS33X11+  | 1   | 1        | 0     | 144 CSBGA      |

| DS33W41+  | 4   | 1        | 1     | 256 CSBGA      |

| DS33W11+  | 1   | 1        | 1     | 256 CSBGA      |

**Note:** All devices are specified over the -40  $^{\circ}$ C to +85  $^{\circ}$ C industrial operating temperature range.

+Denotes a lead-free/RoHS-compliant package.

SPI is a trademark of Motorola, Inc.

MIXIM

Maxim Integrated Products

1

# Table of Contents

|                |                                                                                     | DETAILED DESCRIPTION                                                                                                                                                                                                                                                                                                               | .9                                                               |

|----------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 2.             | F                                                                                   | EATURE HIGHLIGHTS                                                                                                                                                                                                                                                                                                                  | 10                                                               |

|                | 2.1                                                                                 | GENERAL                                                                                                                                                                                                                                                                                                                            | 10                                                               |

|                | 2.2                                                                                 | VCAT/LCAS LINK AGGREGATION (INVERSE MULTIPLEXING)                                                                                                                                                                                                                                                                                  | 10                                                               |

|                | 2.3                                                                                 | HDLC                                                                                                                                                                                                                                                                                                                               |                                                                  |

|                | 2.3.                                                                                |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.4                                                                                 | GFP-F                                                                                                                                                                                                                                                                                                                              |                                                                  |

|                | 2.5                                                                                 | X.86 SUPPORT                                                                                                                                                                                                                                                                                                                       |                                                                  |

|                | 2.6                                                                                 | DDR SDRAM INTERFACE                                                                                                                                                                                                                                                                                                                |                                                                  |

|                | 2.7                                                                                 | MAC INTERFACES                                                                                                                                                                                                                                                                                                                     |                                                                  |

|                | 2.7.                                                                                |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.7.                                                                                |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.7.                                                                                | 4 Ethernet Traffic Scheduling                                                                                                                                                                                                                                                                                                      | 12                                                               |

|                | 2.7.                                                                                |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.7.                                                                                |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.7.<br>2.7.                                                                        |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.7.                                                                                |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.8                                                                                 |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.8.                                                                                |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 2.9                                                                                 | MICROPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                           |                                                                  |

|                | 2.10                                                                                | SLAVE SERIAL PERIPHERAL INTERFACE (SPI) FEATURES                                                                                                                                                                                                                                                                                   | 13                                                               |

|                | 2.11                                                                                | TEST AND DIAGNOSTICS                                                                                                                                                                                                                                                                                                               |                                                                  |

|                | 2.12                                                                                | SPECIFICATIONS COMPLIANCE                                                                                                                                                                                                                                                                                                          | 13                                                               |

| 3.             | . A                                                                                 | APPLICABLE EQUIPMENT TYPES                                                                                                                                                                                                                                                                                                         | 14                                                               |

| 4.             | . A                                                                                 | CRONYMS & GLOSSARY                                                                                                                                                                                                                                                                                                                 | 17                                                               |

| 5.             | . <b>D</b>                                                                          | DESIGNING WITH THE DS33X162 FAMILY OF DEVICES                                                                                                                                                                                                                                                                                      | 18                                                               |

|                | 5.1                                                                                 | IDENTIFICATION OF APPLICATION REQUIREMENTS                                                                                                                                                                                                                                                                                         | 18                                                               |

|                | 5.2                                                                                 | DEVICE SELECTION                                                                                                                                                                                                                                                                                                                   | 18                                                               |

|                | 5.3                                                                                 | ANCILLARY DEVICE SELECTION                                                                                                                                                                                                                                                                                                         | 19                                                               |

|                | 5.4                                                                                 | CIRCUIT DESIGN                                                                                                                                                                                                                                                                                                                     | 40                                                               |

|                |                                                                                     |                                                                                                                                                                                                                                                                                                                                    |                                                                  |

|                | 5.5                                                                                 | BOARD LAYOUT                                                                                                                                                                                                                                                                                                                       | 19                                                               |

|                |                                                                                     | BOARD LAYOUT                                                                                                                                                                                                                                                                                                                       | 19                                                               |

|                | 5.5<br>5.6                                                                          |                                                                                                                                                                                                                                                                                                                                    | 19<br>19                                                         |

|                | 5.5<br>5.6                                                                          | SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                               | 19<br>19<br><b>20</b>                                            |

| 6.<br>7.       | 5.5<br>5.6                                                                          | SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                               | 19<br>19<br><b>20</b><br><b>21</b>                               |

| 6.<br>7.       | 5.5<br>5.6<br>B<br>P                                                                | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS                                                                                                                                                                                                                                                                             | 19<br>19<br><b>20</b><br><b>21</b>                               |

| 6.<br>7.<br>8. | 5.5<br>5.6<br>B<br>P                                                                | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                 | 19<br>19<br><b>20</b><br><b>21</b><br>21                         |

| 6.<br>7.<br>8. | 5.5<br>5.6<br><b>B</b><br>7.1<br><b>F</b><br>8.1                                    | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION  FUNCTIONAL DESCRIPTION  PARALLEL PROCESSOR INTERFACE  1 Read-Write/Data Strobe Modes                                                                                                                                                           | 19<br>19<br><b>20</b><br><b>21</b><br>21<br>34<br>35             |

| 6.<br>7.<br>8. | 5.5<br>5.6<br><b>B</b><br>7.1<br><b>F</b><br>8.1<br>8.1.                            | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION  FUNCTIONAL DESCRIPTION  PARALLEL PROCESSOR INTERFACE  1 Read-Write/Data Strobe Modes  2 Clear on Read                                                                                                                                          | 19<br>19<br><b>20</b><br><b>21</b><br>34<br>35<br>35             |

| 6.<br>7.<br>8. | 5.5<br>5.6<br><b>B</b><br>7.1<br><b>F</b><br>8.1<br>8.1.<br>8.1.                    | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION  FUNCTIONAL DESCRIPTION  PARALLEL PROCESSOR INTERFACE  1 Read-Write/Data Strobe Modes  2 Clear on Read  3 Interrupt and Pin Modes                                                                                                               | 19<br>19<br><b>20</b><br><b>21</b><br>34<br>35<br>35<br>35       |

| 6.<br>7.<br>8. | 5.5<br>5.6<br><b>B</b><br>7.1<br><b>F</b><br>8.1<br>8.1<br>8.1<br>8.1               | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION  FUNCTIONAL DESCRIPTION  PARALLEL PROCESSOR INTERFACE  1 Read-Write/Data Strobe Modes  2 Clear on Read  3 Interrupt and Pin Modes.  4 Multiplexed Bus Operation                                                                                 | 19<br>19<br><b>20</b><br><b>21</b><br>35<br>35<br>35<br>35       |

| 6.<br>7.<br>8. | 5.5<br>5.6<br><b>B</b><br>7.1<br><b>F</b><br>8.1<br>8.1<br>8.1<br>8.1<br>8.1<br>8.1 | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION  CUNCTIONAL DESCRIPTION  PARALLEL PROCESSOR INTERFACE  1 Read-Write/Data Strobe Modes  2 Clear on Read  3 Interrupt and Pin Modes  4 Multiplexed Bus Operation  SPI SERIAL PROCESSOR INTERFACE                                                  | 19<br>19<br><b>20</b><br><b>21</b><br>35<br>35<br>35<br>35<br>35 |

| 6.<br>7.<br>8. | 5.5<br>5.6<br><b>B</b><br>7.1<br><b>F</b><br>8.1<br>8.1<br>8.1<br>8.1               | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION  CUNCTIONAL DESCRIPTION  PARALLEL PROCESSOR INTERFACE  1 Read-Write/Data Strobe Modes  2 Clear on Read  3 Interrupt and Pin Modes  4 Multiplexed Bus Operation  SPI SERIAL PROCESSOR INTERFACE  CLOCK STRUCTURE                                 | 19<br>20<br>21<br>21<br>34<br>35<br>35<br>35<br>35<br>36<br>37   |

| 6.<br>7.<br>8. | 5.5<br>5.6<br><b>B</b><br>7.1<br><b>F</b><br>8.1<br>8.1<br>8.1<br>8.1<br>8.2<br>8.3 | SOFTWARE DEVELOPMENT  BLOCK DIAGRAMS  PIN DESCRIPTIONS  PIN FUNCTIONAL DESCRIPTION  CUNCTIONAL DESCRIPTION  PARALLEL PROCESSOR INTERFACE  1 Read-Write/Data Strobe Modes  2 Clear on Read  3 Interrupt and Pin Modes  4 Multiplexed Bus Operation  SPI SERIAL PROCESSOR INTERFACE  CLOCK STRUCTURE  1 Serial Interface Clock Modes | 19<br>20<br>21<br>34<br>35<br>35<br>35<br>36<br>37<br>39         |

| 8.4 RESETS  | S AND LOW-POWER MODES                                  | 39         |

|-------------|--------------------------------------------------------|------------|

|             | ZATION AND CONFIGURATION                               |            |

|             | RESOURCES                                              |            |

|             | ORT RESOURCES                                          |            |

|             | INTERRUPTS                                             |            |

|             | RDING MODES AND WAN CONNECTIONS                        |            |

|             | warding Modeswarding Modes                             |            |

|             | N Connections                                          |            |

|             | eue Configuration                                      |            |

| •           | WIDTH CAPABILITIES (THROUGHPUT)                        |            |

|             | AL (WAN)                                               |            |

| 8.11.1 Void | ce Support (DS33W11 and DW33W41 Only)                  | 52<br>52   |

| 8.12 LINK   | AGGREGATION AND LINK CAPACITY ADJUSTMENT (VCAT/LCAS)   | 53         |

| 8.12.1 VC   | AT/LCAS Control Frame for T3/E3                        | 5 <u>4</u> |

|             | AT/LCAS Configuration and Operation                    |            |

|             | k Capacity Adjustment Scheme (LCAS)                    |            |

| 8.12.4 Alai | rms and Conditions related to VCAT/LCAS                | 57         |

|             | rer/Buffer Manager                                     |            |

|             | / CONTROL                                              |            |

|             | I Duplex Flow control                                  |            |

|             | f Duplex Flow control                                  |            |

|             | RNET INTERFACES                                        |            |

|             | III Mode                                               |            |

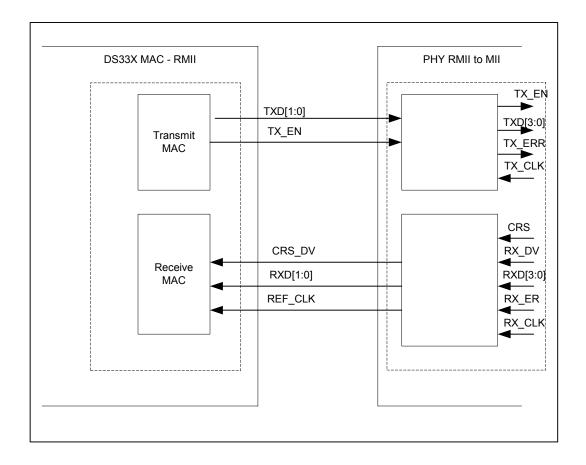

|             | Mode                                                   |            |

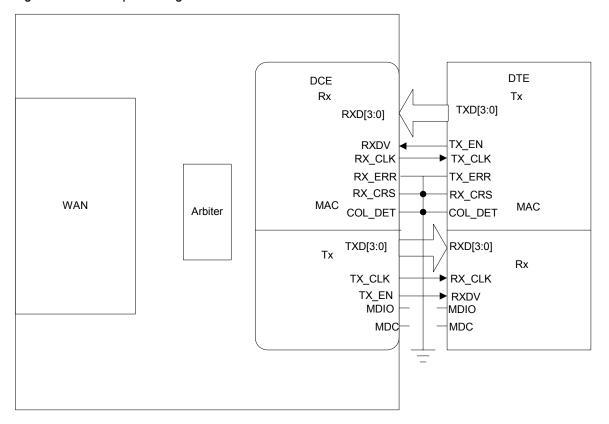

|             | E and DCE Mode                                         |            |

|             | III Mode                                               |            |

| 8.16 QUAL   | ITY OF SERVICE (QOS) FEATURES                          | 67         |

|             | AN Forwarding by VID (IEEE 802.1q)                     |            |

|             | gramming the VLAN ID Table                             |            |

| 8.16.3 Pric | ority Coding with VLAN Tags (IEEE 802.1p)              | 69         |

| 8.16.4 Pric | prity Coding with Multiple (Q-in-Q) VLAN Tags          | 70         |

|             | prity Coding with DSCP                                 |            |

|             | gramming the Priority Table                            |            |

|             | SUPPORT WITH FRAME TRAPPING, EXTRACTION, AND INSERTION |            |

|             | me Trapping                                            |            |

|             | me Extraction and Frame Insertion                      |            |

|             | M by Ethernet Destination Address (DA)                 |            |

|             | M by IP Address                                        |            |

|             | M by VLAN TagMP Support                                |            |

|             | GING AND FILTERING                                     |            |

|             | dge Filter Table Reset                                 |            |

|             | RNET MAC                                               |            |

|             | Y MII Management Block and MDIO Interface              |            |

|             | ernet MAC Management Counters for RFC2819 RMON         |            |

|             | grammable Ethernet Destination Address Filtering       |            |

|             | RNET FRAME ENCAPSULATION                               |            |

|             | nsmit Packet Processor (Encapsulator)                  |            |

|             | ceive Packet Processor (Decapsulator)                  |            |

|             | P-F Encapsulation and Decapsulation                    |            |

|             | 6 Encoding and Decoding                                |            |

|             | LC Encoding and Decoding                               |            |

|             | DLC Encoding And Decoding                              |            |

|             | CBS CONTROLLER                                         |            |

|             | ATIONS INFORMATION                                     |            |

| V. AFFLICA  | \                                                      |            |

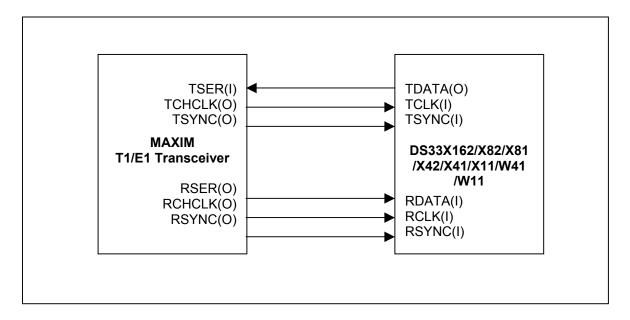

| 9.1 Interfacing to Maxim T1/E1 Transceivers                |              |

|------------------------------------------------------------|--------------|

| 9.2 Interfacing to Maxim T3/E3 Transceivers                |              |

| 10. DEVICE REGISTERS                                       | 105          |

| 10.1 REGISTER BIT MAPS                                     | 106          |

| 10.1.1 Global Register Bit Map                             |              |

| 10.1.2 MAC Indirect Register Bit Map                       |              |

| 10.2 GLOBAL REGISTER DEFINITIONS                           |              |

| 10.2.1 Microport Registers                                 |              |

| 10.2.2 MAC 1 Interface Access Registers                    |              |

| 10.2.3 MAC 2 Interface Access Registers                    |              |

| 10.3 ETHERNET INTERFACE REGISTERS                          |              |

| 10.3.1 WAN Extraction and Transmit LAN registers           |              |

| 10.3.2 Receive LAN Register Definitions                    |              |

| 10.3.3 Bridge Filter Registers                             |              |

| 10.4 ARBITER REGISTERS                                     |              |

| 10.4.1 Arbiter Register Bit Descriptions                   |              |

| 10.5 PACKET PROCESSOR (ENCAPSULATOR) REGISTERS             | 230          |

| 10.6 DECAPSULATOR REGISTERS                                |              |

| 10.7 VCAT/LCAS REGISTERS                                   | 245          |

| 10.7.1 Transmit VCAT Registers                             | 245          |

| 10.7.2 VCAT Receive Register Description                   |              |

| 10.8 SERIAL INTERFACE REGISTERS                            |              |

| 10.8.1 Serial Interface Transmit and Common Registers      |              |

| 10.8.2 Serial Interface Transmit Register Bit Descriptions |              |

| 10.8.3 Transmit Per Serial Port Register Description       |              |

| 10.8.4 Transmit Voice Port Register Description            |              |

| 10.8.5 Receive Per Serial Port Register Description        |              |

| 10.8.7 MAC Registers                                       |              |

| 11. FUNCTIONAL TIMING                                      |              |

|                                                            |              |

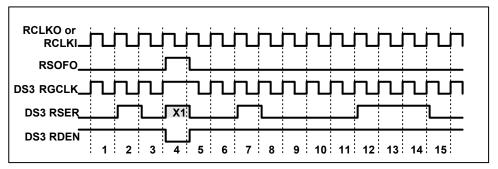

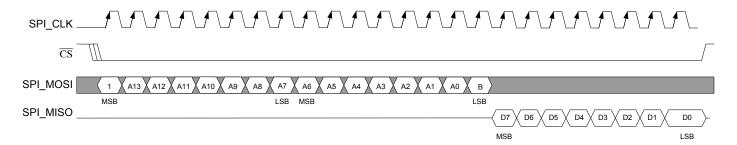

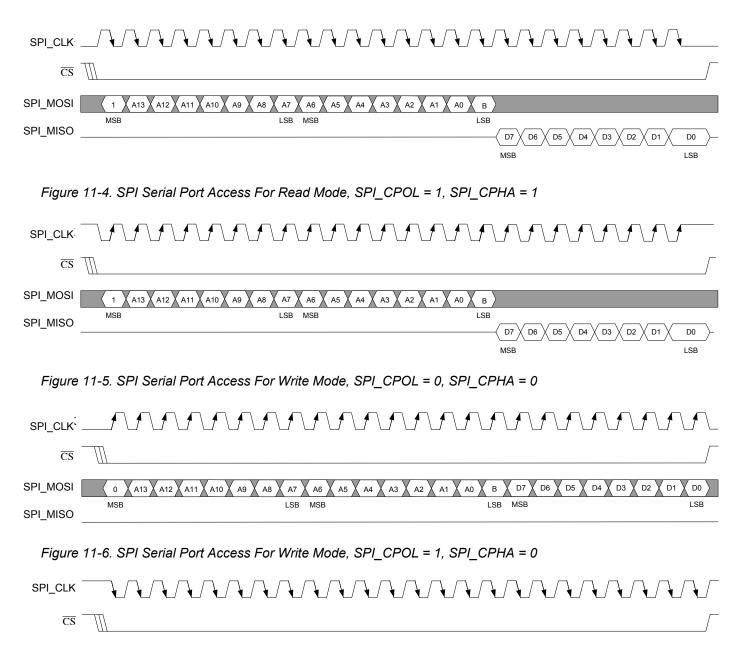

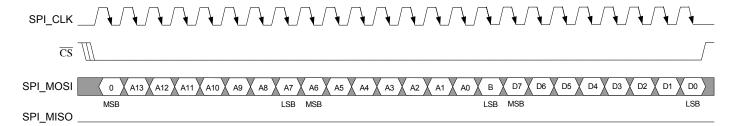

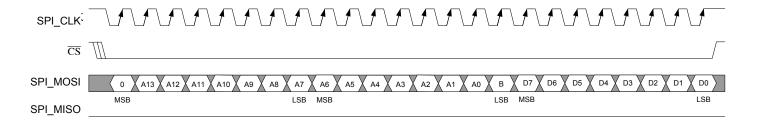

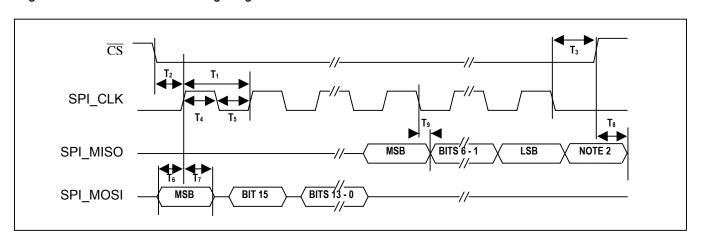

| 11.1 FUNCTIONAL SPI INTERFACE TIMING                       |              |

| 11.1.1 SPI Transmission Format and CPHA Polarity           |              |

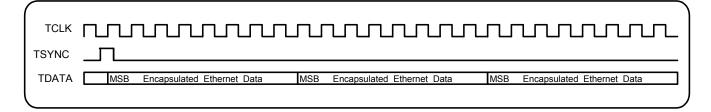

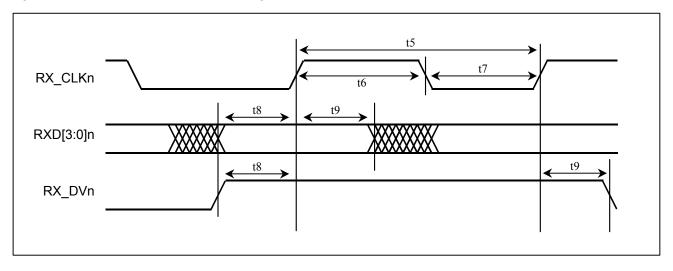

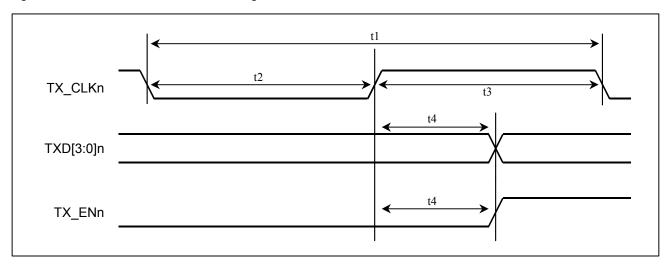

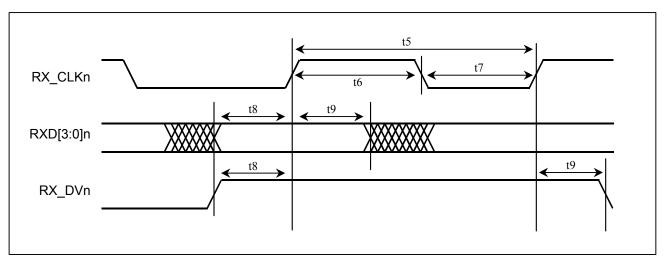

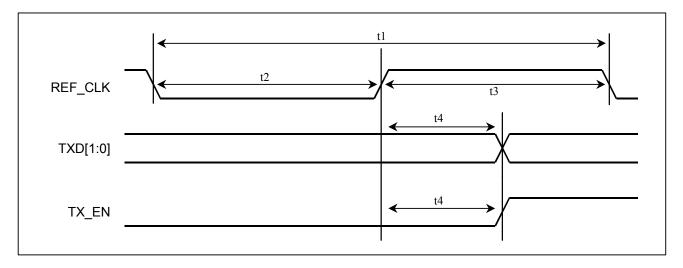

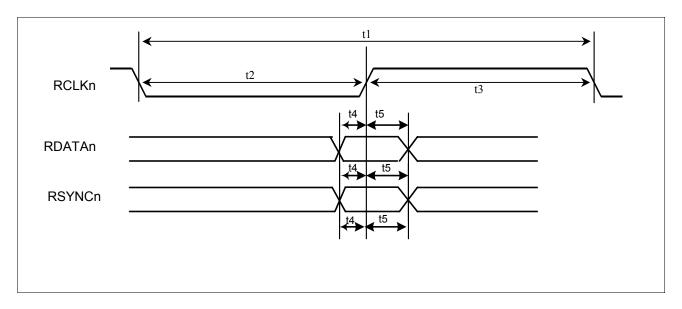

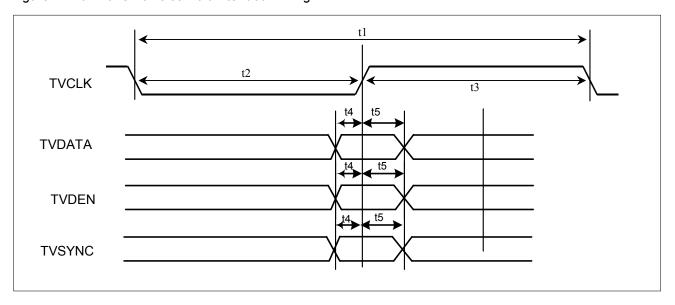

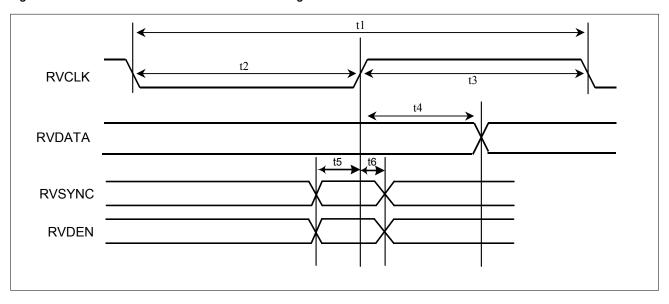

| 11.2 FUNCTIONAL SERIAL INTERFACE TIMING                    |              |

|                                                            |              |

| 11.4 MII/RMII AND GMII INTERFACES                          |              |

| 12. OPERATING PARAMETERS                                   | 339          |

| 12.1 THERMAL CHARACTERISTICS                               | 341          |

| 12.2 TRANSMIT AND RECEIVE GMII INTERFACE                   | 342          |

| 12.3 TRANSMIT AND RECEIVE MII INTERFACE                    | 344          |

| 12.4 TRANSMIT AND RECEIVE RMII INTERFACE                   | 346          |

| 12.5 MDIO INTERFACE                                        | 348          |

| 12.6 TRANSMIT AND RECEIVE WAN INTERFACE                    | 349          |

| 12.7 TRANSMIT AND RECEIVE VOICE PORT INTERFACE             | 351          |

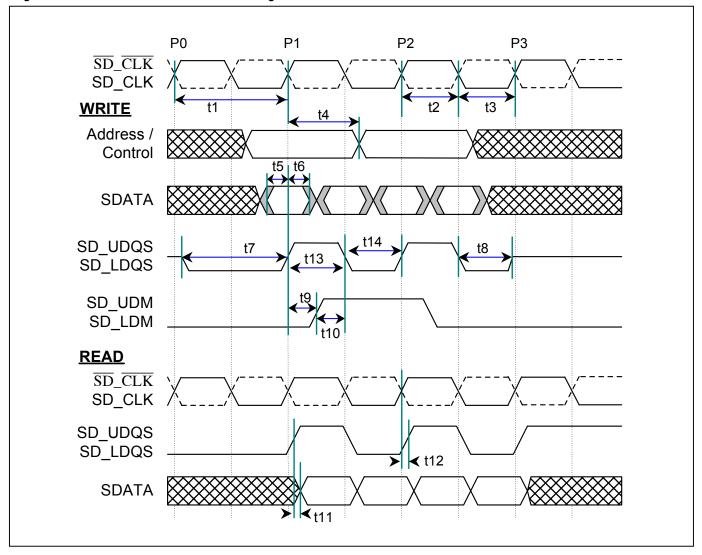

| 12.8 DDR SDRAM INTERFACE                                   | 353          |

| 12.9 AC CHARACTERISTICS—MICROPROCESSOR BUS INTERFACE       | CE TIMING355 |

| 12.10 JTAG INTERFACE                                       | 362          |

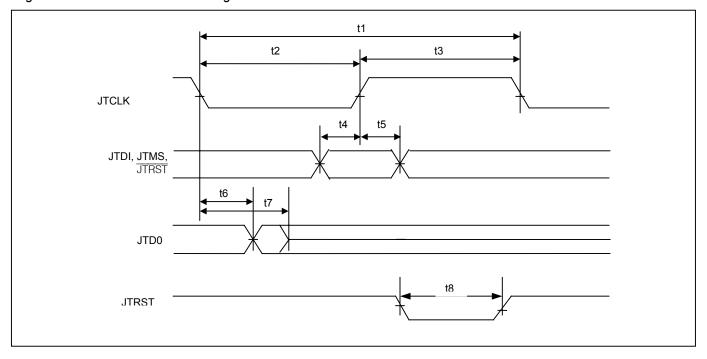

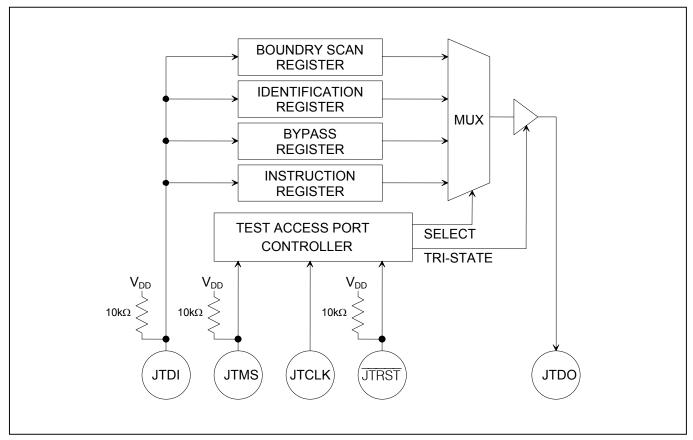

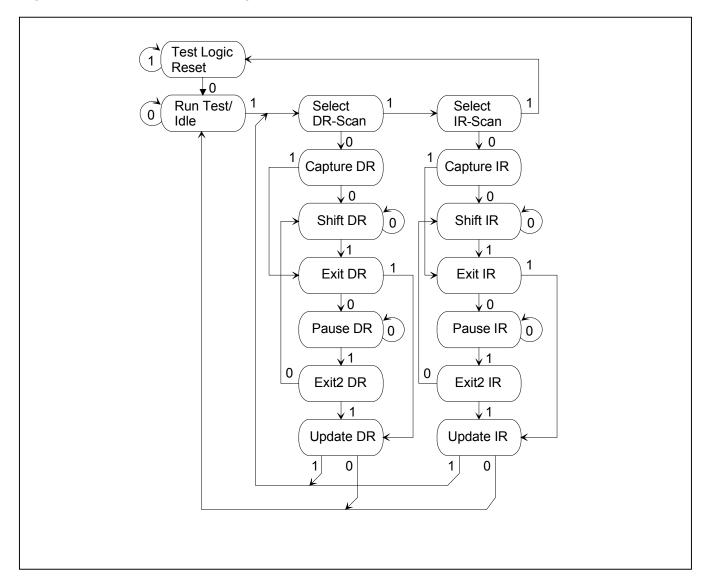

| 13. JTAG INFORMATION                                       | 363          |

| 13.1 JTAG TAP CONTROLLER STATE MACHINE DESCRIPTION         |              |

| 13.1.1 TAP Controller State Machine                        |              |

| 13.2 INSTRUCTION REGISTER                                  |              |

| 13.2.1 SAMPLE:PRELOAD                                      |              |

|                                                            |              |

| 13.2.   | 2 BYPASS                                                       | 367 |

|---------|----------------------------------------------------------------|-----|

| 13.2.   |                                                                |     |

| 13.2.   |                                                                |     |

| 13.2.   |                                                                |     |

| 13.2.   |                                                                |     |

| 13.3    | JTAG ID CODES                                                  | 368 |

| 13.4    | Test Registers                                                 | 368 |

| 13.4.   | 1 Boundary Scan Register                                       | 368 |

| 13.4.   |                                                                |     |

| 13.4.   | 3 Identification Register                                      | 368 |

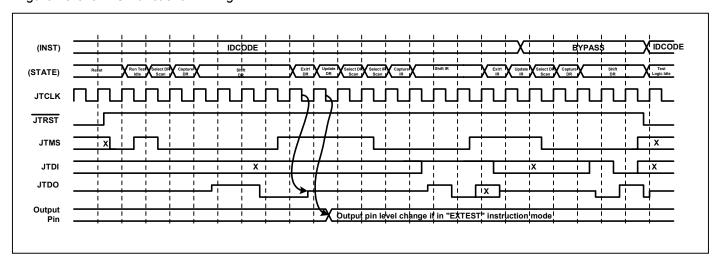

| 13.5    | JTAG FUNCTIONAL TIMING                                         | 369 |

| 14. PII | N CONFIGURATION                                                | 370 |

| 14.1    | DS33X162/X161/X82/X81/X42/X41 Pin Configuration—256-Ball CSBGA | 370 |

| 14.2    | DS33W41/DS33W11 PIN CONFIGURATION—256-BALL CSBGA               |     |

| 14.3    | DS33X11 PIN CONFIGURATION—144-BALL CSBGA                       |     |

| _       | ACKAGE INFORMATION                                             |     |

|         |                                                                |     |

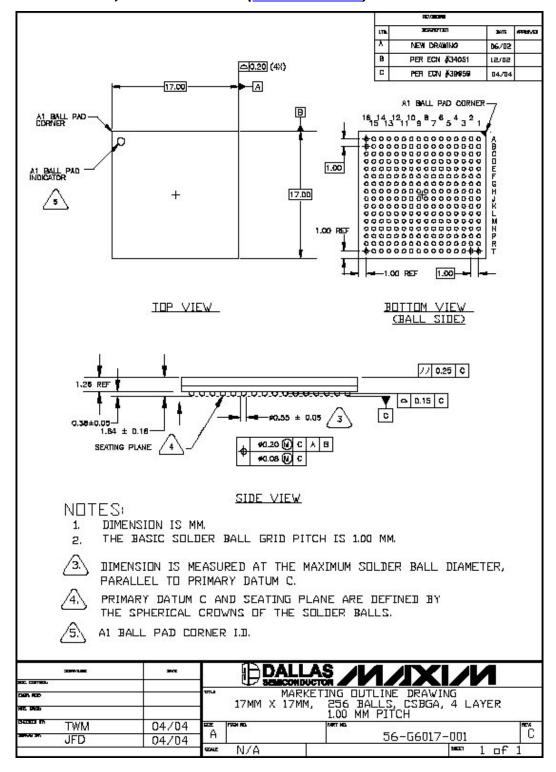

| 15.1    | 256-BALL CSBGA, 17MM x 17MM (56-G6017-001)                     |     |

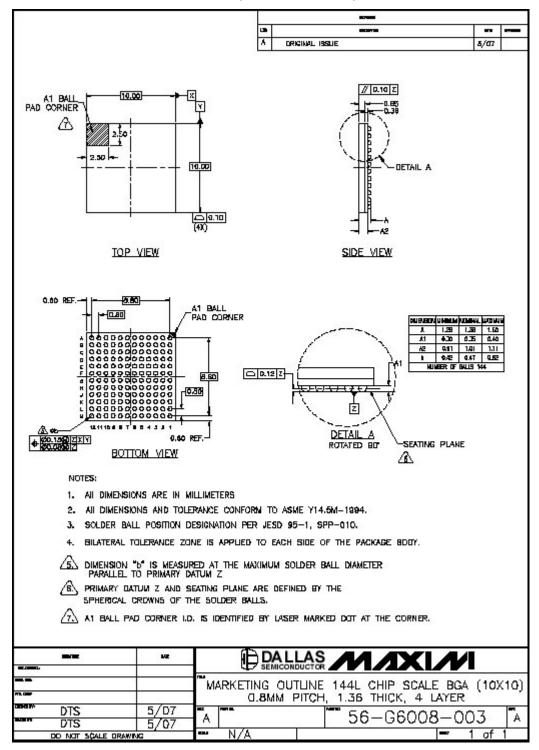

| 15.2    | 144-BALL CSBGA, 10MM x 10MM (56-G6008-003)                     | 374 |

| 16. DC  | DCUMENT REVISION HISTORY                                       | 375 |

|         |                                                                |     |

# List of Figures

| Figure 3-1. Standardized Ethernet Transport over Multiple T1/E1 Lines               |     |

|-------------------------------------------------------------------------------------|-----|

| Figure 3-2. Standardized Ethernet Transport over a Single T1/E1 Line                |     |

| Figure 3-3. Remote IP DSLAM T1/E1 Trunk Card                                        |     |

| Figure 6-1. Simplified Logical Block Diagram                                        | 20  |

| Figure 7-1. 256-Ball, 17mm x 17mm CSBGA Pinout (DS33X162/X161/X82/X81/X42/X41)      | 31  |

| Figure 7-2. 256-Ball, 17mm x 17mm CSBGA Pinout (DS33W41/DS33W11)                    | 32  |

| Figure 7-3. 144-Ball, 10mm x 10mm, CSBGA Pinout (DS33X11)                           |     |

| Figure 8-1. Clocking Diagram                                                        |     |

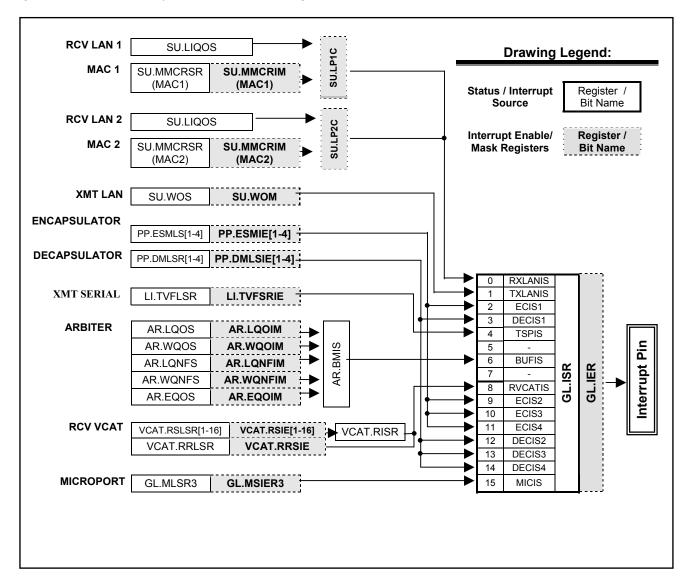

| Figure 8-2. Device Interrupt Information Flow Diagram                               | 42  |

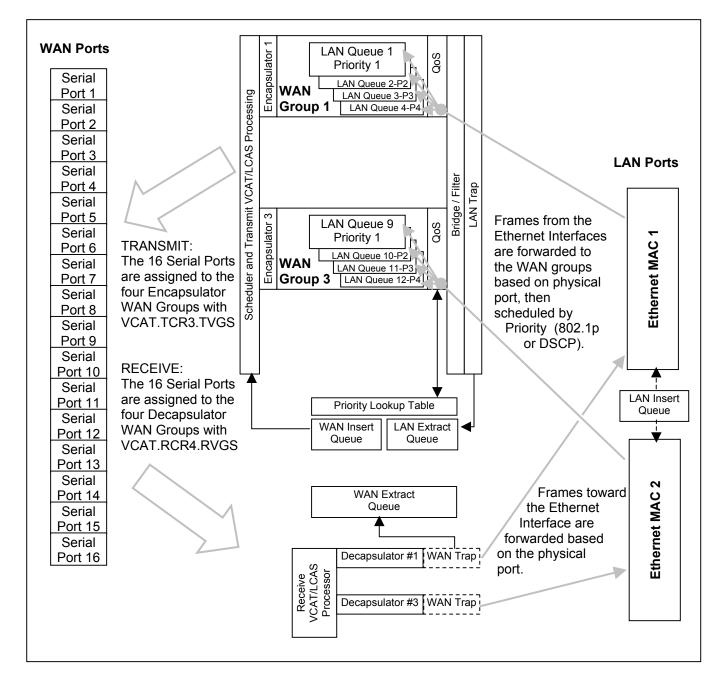

| Figure 8-3. Forwarding Mode 1: Single Ethernet Port with Priority Forwarding        | 44  |

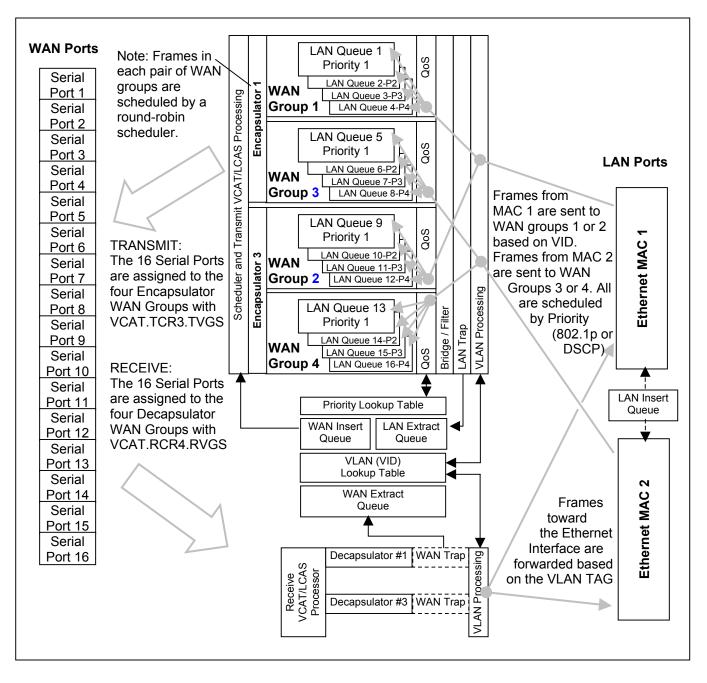

| Figure 8-4. Forwarding Mode 2: One or Two Ethernet Port Forwarding with Scheduling  |     |

| Figure 8-5. Forwarding Mode 3: Single Ethernet Port with LAN-VLAN Forwarding        |     |

| Figure 8-6. Forwarding Mode 4: 1 Ethernet port with Port ID and LAN-VLAN Forwarding |     |

| Figure 8-7. Forwarding Mode 5: Full LAN-to-WAN and WAN-to-LAN VLAN Forwarding       |     |

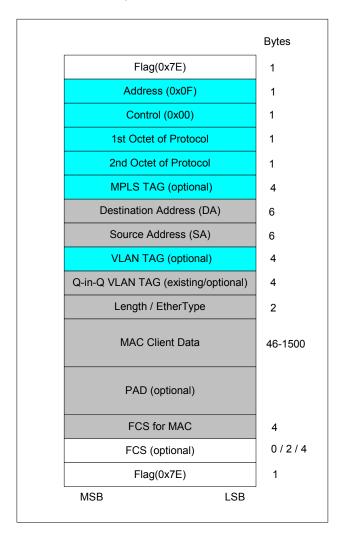

| Figure 8-8. IEEE 802.3 Ethernet Frame                                               |     |

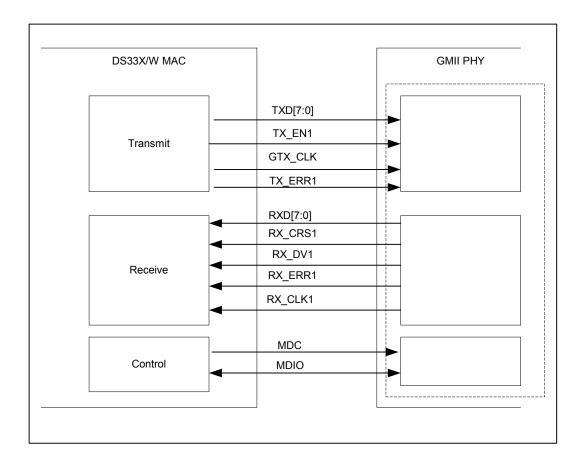

| Figure 8-9. Example Configuration of GMII Interface (DTE Mode Only)                 |     |

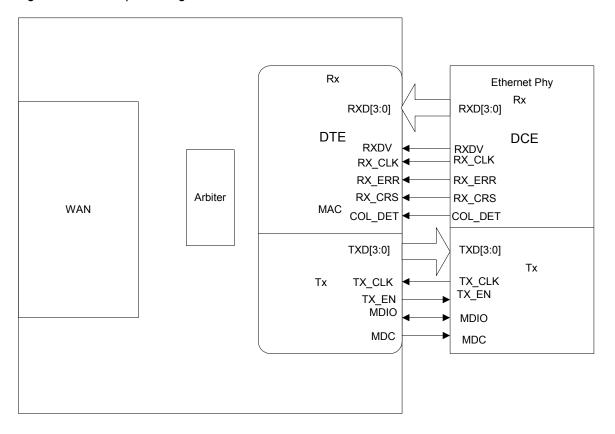

| Figure 8-10. Example Configuration as DTE connected to an Ethernet PHY in MII Mode  | 63  |

| Figure 8-11. Example Configuration as a DCE in MII Mode                             | 65  |

| Figure 8-12. RMII Interface (DTE Mode Only)                                         |     |

| Figure 8-13. IEEE 802.1Q and 802.1p Field Format                                    |     |

| Figure 8-14. VLAN Q-in-Q Field Format                                               |     |

| Figure 8-15. Differentiated Services Code Point (DSCP) Header Information           | 71  |

| Figure 8-16. Supported Trapped Ethernet Frame Types                                 |     |

| Figure 8-17. MII Management Frame                                                   |     |

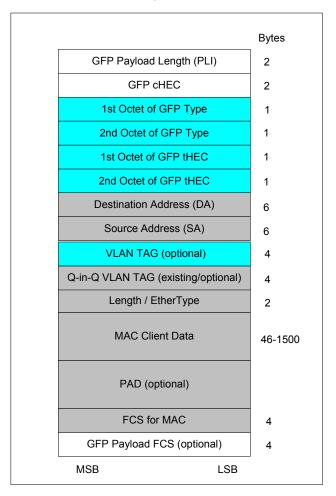

| Figure 8-18. GFP-F NULL Encapsulated Frame Format                                   |     |

|                                                                                     |     |

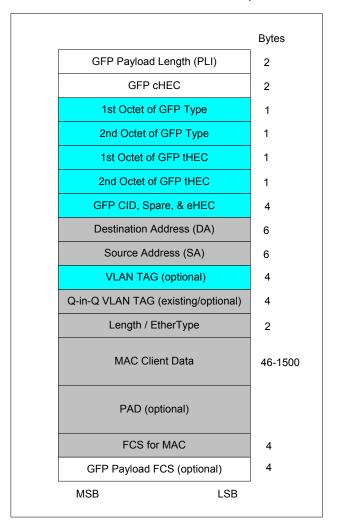

| Figure 8-19. GFP-F LINEAR EXTENSION Encapsulated Frame Format                       |     |

| Figure 8-20. LAPS / X.86 Encapsulated Frame Format                                  |     |

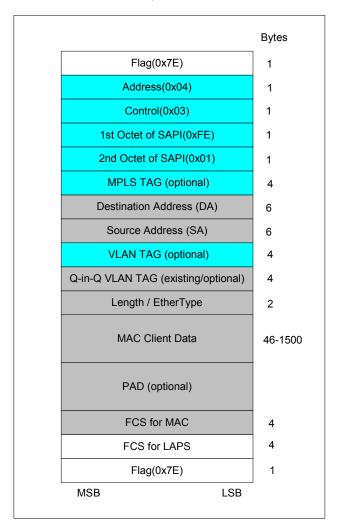

| Figure 8-21. HDCL Encapsulated Frame Format                                         |     |

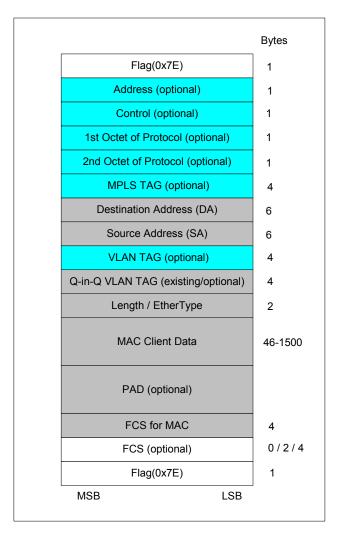

| Figure 8-22. cHDLC Encapsulated Frame Format                                        |     |

| Figure 9-1. Interfacing with T1/E1 Transceivers                                     |     |

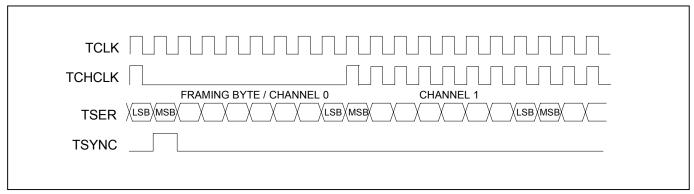

| Figure 9-2. Example Functional Timing: DS2155 E1 Transmit-Side Boundary Timing      |     |

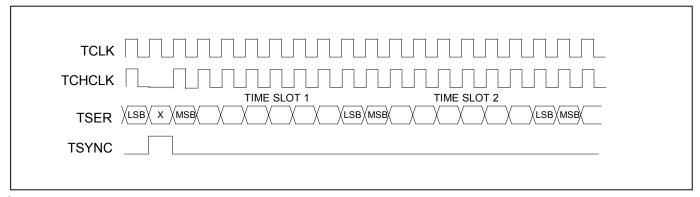

| Figure 9-3. Example Functional Timing: DS2155 T1 Transmit-Side Boundary Timing      |     |

| Figure 9-4. Example Functional Timing: DS2155 E1 Receive-Side Boundary Timing       |     |

| Figure 9-5. Example Functional Timing: DS2155 T1 Receive-Side Boundary Timing       |     |

| Figure 9-6. Interfacing with T3/E3 Transceivers                                     |     |

| Figure 9-7. Example Functional Timing: DS3170 DS3 Transmit-Side Boundary Timing     |     |

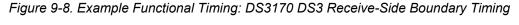

| Figure 9-8. Example Functional Timing: DS3170 DS3 Receive-Side Boundary Timing      |     |

| Figure 11-1. SPI Serial Port Access For Read Mode, SPI_CPOL=0, SPI_CPHA = 0         |     |

| Figure 11-2. SPI Serial Port Access For Read Mode, SPI_CPOL = 1, SPI_CPHA = 0       |     |

| Figure 11-3. SPI Serial Port Access For Read Mode, SPI_CPOL = 0, SPI_CPHA = 1       |     |

| Figure 11-4. SPI Serial Port Access For Read Mode, SPI_CPOL = 1, SPI_CPHA = 1       |     |

| Figure 11-5. SPI Serial Port Access For Write Mode, SPI_CPOL = 0, SPI_CPHA = 0      |     |

| Figure 11-6. SPI Serial Port Access For Write Mode, SPI_CPOL = 1, SPI_CPHA = 0      |     |

| Figure 11-7. SPI Serial Port Access For Write Mode, SPI_CPOL = 0, SPI_CPHA = 1      |     |

| Figure 11-8. SPI Serial Port Access For Write Mode, SPI_CPOL = 1, SPI_CPHA = 1      | 332 |

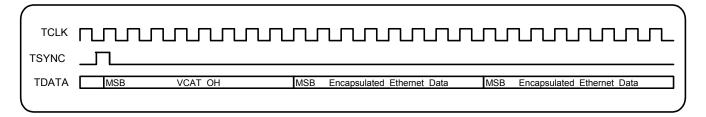

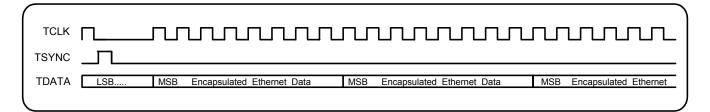

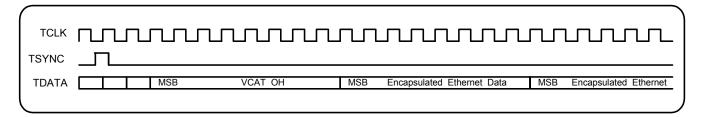

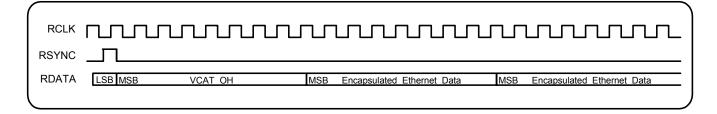

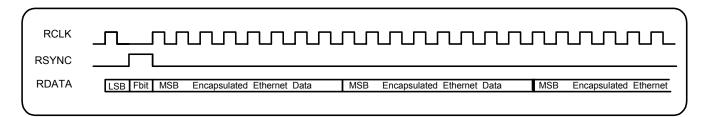

| Figure 11-9. Transmit Serial Port Interface, without VCAT                           | 333 |

| Figure 11-10. Transmit Serial Port Interface with VCAT                              | 333 |

| Figure 11-11. Transmit Serial Port Interface, with Gapped Clock                     | 333 |

| Figure 11-12. Transmit Serial Port Interface with VCAT, early TSYNC (2 cycles)      |     |

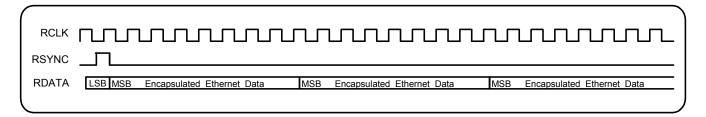

| Figure 11-13. Receive Serial Port Interface, without VCAT, rising edge sampling     |     |

| Figure 11-14. Receive Serial Port Interface with VCAT, rising edge sampling         |     |

| Figure 11-15. Receive Serial Port Interface with Gapped Clock (T1)                  |     |

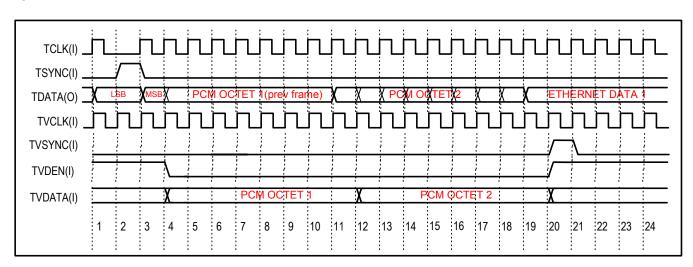

| Figure 11-16. Transmit Voice Port Interface with PCM Octets                         |     |

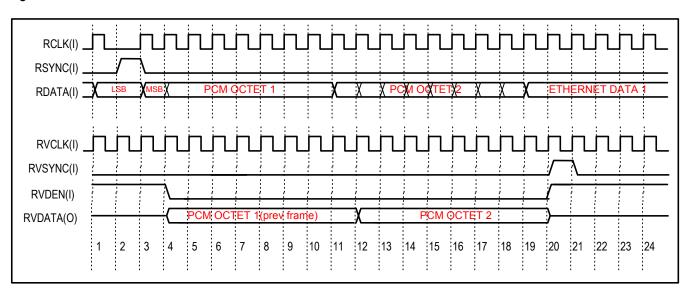

| Figure 11-17. Receive Voice Port Interface with PCM Octets                          |     |

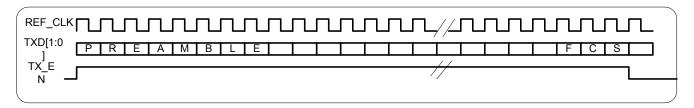

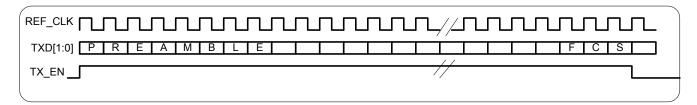

| Figure 11-18. GMII Transmit Interface Functional Timing                             |     |

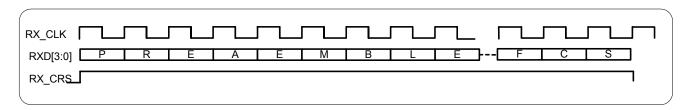

| g                                                                                   |     |

| Figure 11-19. GMII Receive Interface Functional Timing                    | 336 |

|---------------------------------------------------------------------------|-----|

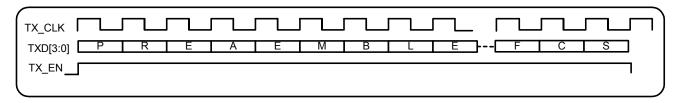

| Figure 11-20. MII Transmit Functional Timing                              | 337 |

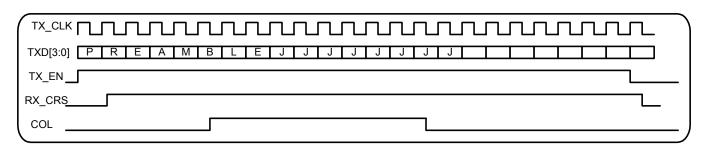

| Figure 11-21. MII Transmit Half Duplex with a Collision Functional Timing | 337 |

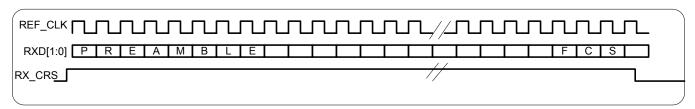

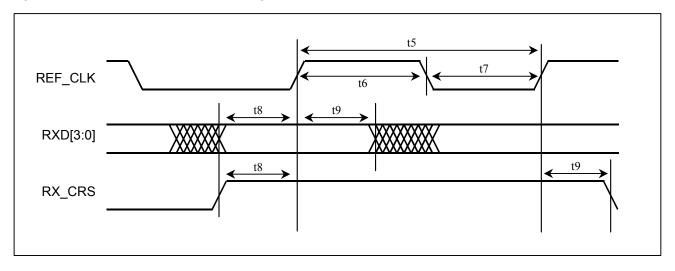

| Figure 11-22. MII Receive Functional Timing                               | 337 |

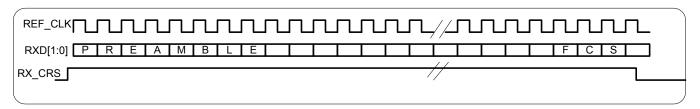

| Figure 11-23. RMII Transmit Interface Functional Timing                   | 338 |

| Figure 11-24. RMII Receive Interface Functional Timing                    | 338 |

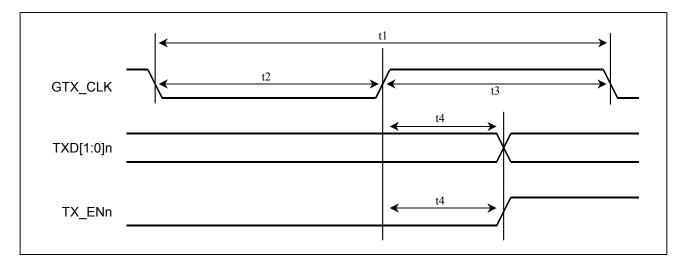

| Figure 12-1. Transmit GMII Interface Timing                               | 342 |

| Figure 12-2. Receive GMII Interface Timing                                | 343 |

| Figure 12-3. Transmit MII Interface Timing                                | 344 |

| Figure 12-4. Receive MII Interface Timing                                 | 345 |

| Figure 12-5. Transmit RMII Interface Timing                               | 346 |

| Figure 12-6. Receive RMII Interface Timing                                | 347 |

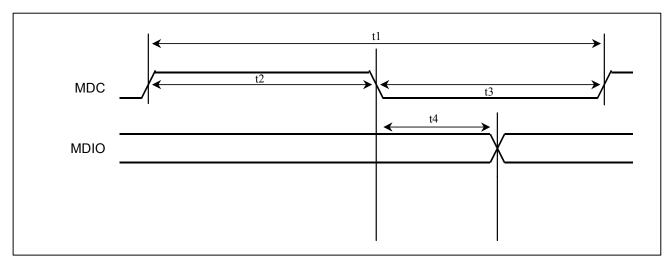

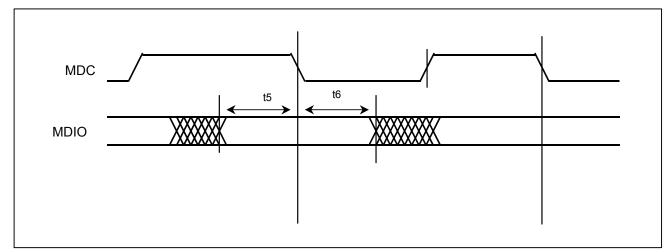

| Figure 12-7. MDIO Interface Timing                                        |     |

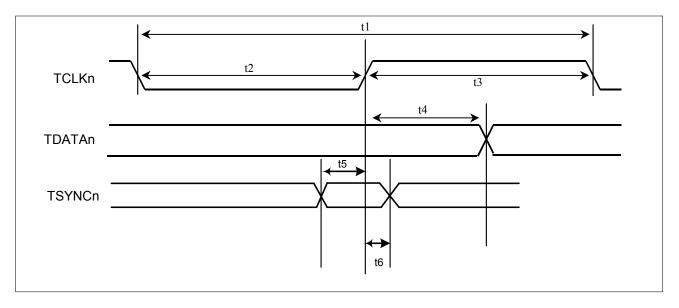

| Figure 12-8. Transmit WAN Timing (Noninverted TCLK)                       | 349 |

| Figure 12-9. Receive WAN Timing (Noninverted RCLK)                        | 350 |

| Figure 12-10. Transmit Voice Port Interface Timing                        | 351 |

| Figure 12-11. Receive Voice Port Interface Timing                         | 352 |

| Figure 12-12. DDR SDRAM Interface Timing                                  | 354 |

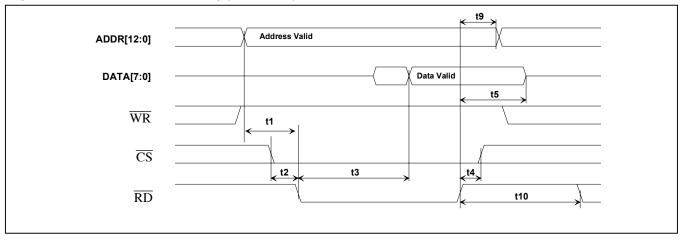

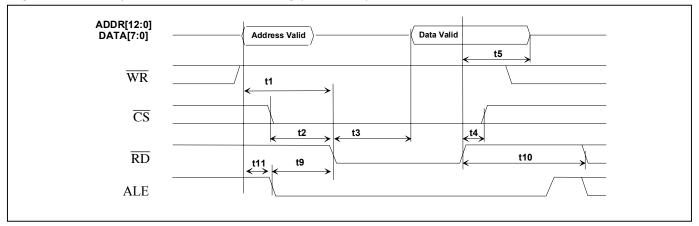

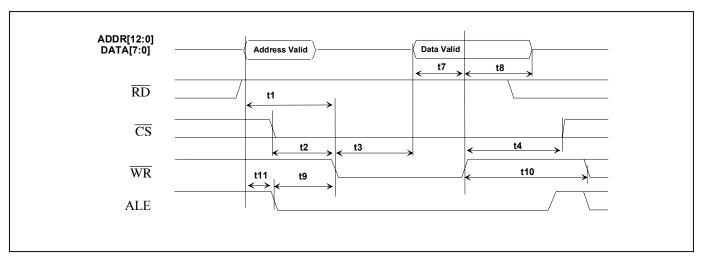

| Figure 12-13. Intel Bus Read Timing (MODE = 0)                            |     |

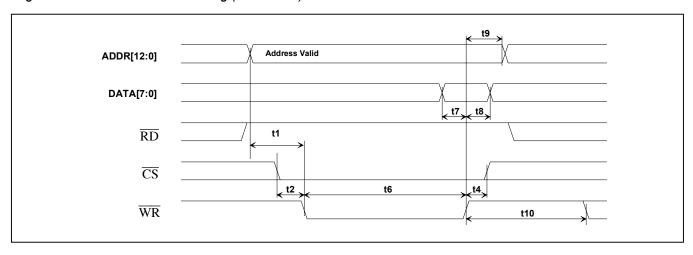

| Figure 12-14. Intel Bus Write Timing (MODE = 0)                           |     |

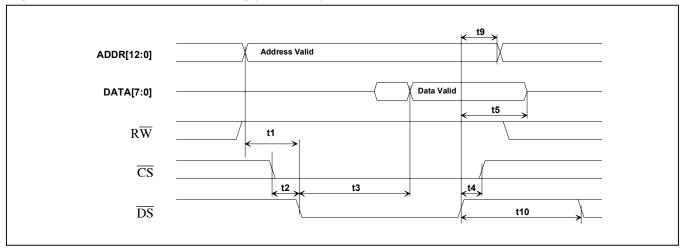

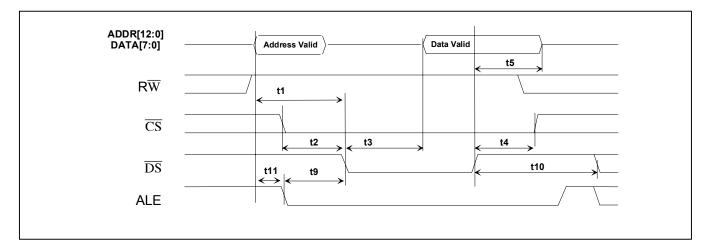

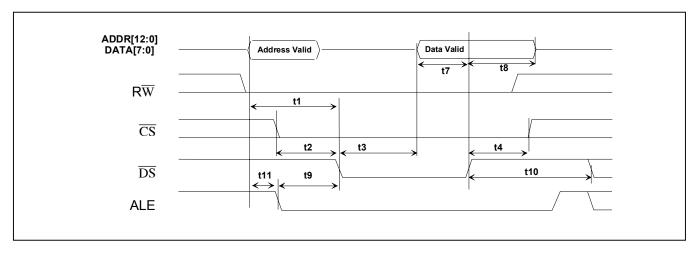

| Figure 12-15. Motorola Bus Read Timing (MODE = 1)                         |     |

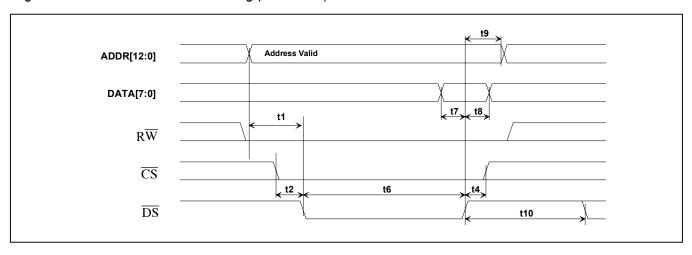

| Figure 12-16. Motorola Bus Write Timing (MODE = 1)                        | 357 |

| Figure 12-17. Multiplexed Intel Bus Read Timing (MODE = 0)                |     |

| Figure 12-18. Multiplexed Intel Bus Write Timing (MODE = 0)               |     |

| Figure 12-19. Multiplexed Motorola Bus Read Timing (MODE = 1)             |     |

| Figure 12-20. Multiplexed Motorola Bus Write Timing (MODE = 1)            |     |

| Figure 12-21. SPI Interface Timing Diagram                                |     |

| Figure 12-22. JTAG Interface Timing                                       | 362 |

| Figure 13-1. JTAG Functional Block Diagram                                |     |

| Figure 13-2. TAP Controller State Diagram                                 |     |

| Figure 13-3. JTAG Functional Timing                                       | 369 |

# List of Tables

| Table 1-1. Product Selection Matrix                                                   | 9   |

|---------------------------------------------------------------------------------------|-----|

| Table 7-1. Detailed Pin Descriptions                                                  | 21  |

| Table 8-1. Clocking Options for the Ethernet Interface                                | 37  |

| Table 8-2. Software Reset Functions                                                   | 39  |

| Table 8-3. Block Enable Functions                                                     | 40  |

| Table 8-4. Forwarding Modes Supported by Device                                       | 49  |

| Table 8-5. Maximum Number of T3/E3 Lines Per Encapsulator (DS33X162 and DS33X82 Only) | 51  |

| Table 8-6. VCAT/LCAS Control Frame for T1/E1                                          | 53  |

| Table 8-7. VCAT/LCAS Control Frame for T3/E3                                          |     |

| Table 8-8. Configuration Recommendations for Maximum Frame Length                     |     |

| Table 8-9. Selection of MAC Interface Modes for Port 1                                |     |

| Table 8-10. Selection of MAC Interface Modes for Port 2                               |     |

| Table 8-11. MII Mode Options                                                          | 64  |

| Table 8-12. Example Priority Table Configuration for DSCP                             |     |

| Table 8-13. Example Priority Table Configuration for PCP                              |     |

| Table 8-14. MAC Control Registers                                                     |     |

| Table 8-15. MAC Status Registers                                                      |     |

| Table 8-16. MAC Counter Registers                                                     |     |

| Table 8-17. GFP Type/tHEC Field (Payload Header) Definition                           |     |

| Table 8-18. GFP UPI Definitions                                                       |     |

| Table 8-19. Example GFP Type + tHEC Values                                            |     |

| Table 8-20. GFP CID/Spare/eHEC (Extension Header) Field Definition                    |     |

| Table 8-21. Example CID + Spare + eHEC Values                                         |     |

| Table 8-22. Credit Threshold Settings with Resulting Bandwidths                       |     |

| Table 10-1. Register Address Map                                                      |     |

| Table 10-2. Global Register Bit Map.                                                  |     |

| Table 10-3. MAC Indirect Register Bit Map                                             |     |

| Table 10-4. Default GL.IDR Values                                                     |     |

| Table 10-5. Valid Conditions for MPL > 2048                                           |     |

| Table 12-1. Recommended DC Operating Conditions                                       | 240 |

| Table 12-3. Thermal Characteristics                                                   |     |

| Table 12-4. Transmit GMII Interface                                                   |     |

| Table 12-5. Receive GMII Interface                                                    |     |

| Table 12-6. Transmit MII Interface                                                    |     |

| Table 12-7. Receive MII Interface                                                     |     |

| Table 12-8. Transmit RMII Interface                                                   |     |

| Table 12-9. Receive RMII Interface                                                    |     |

| Table 12-10. MDIO Interface                                                           |     |

| Table 12-11. Transmit WAN Interface                                                   |     |

| Table 12-12. Receive WAN Interface                                                    |     |

| Table 12-13. Transmit Voice Port Interface                                            |     |

| Table 12-14. Receive Voice Port Interface                                             |     |

| Table 12-15. DDR SDRAM Interface                                                      |     |

| Table 12-16. Parallel Microprocessor Bus.                                             |     |

| Table 12-17. Multiplexed Microprocessor Bus                                           |     |

| Table 12-18. SPI Microprocessor Bus Mode                                              |     |

| Table 12-19. JTAG Interface                                                           | 362 |

| Table 13-1. Instruction Codes for IEEE 1149.1 Architecture                            | 367 |

| Table 13-2 ID Code Structure                                                          | 368 |

# 1. Detailed Description

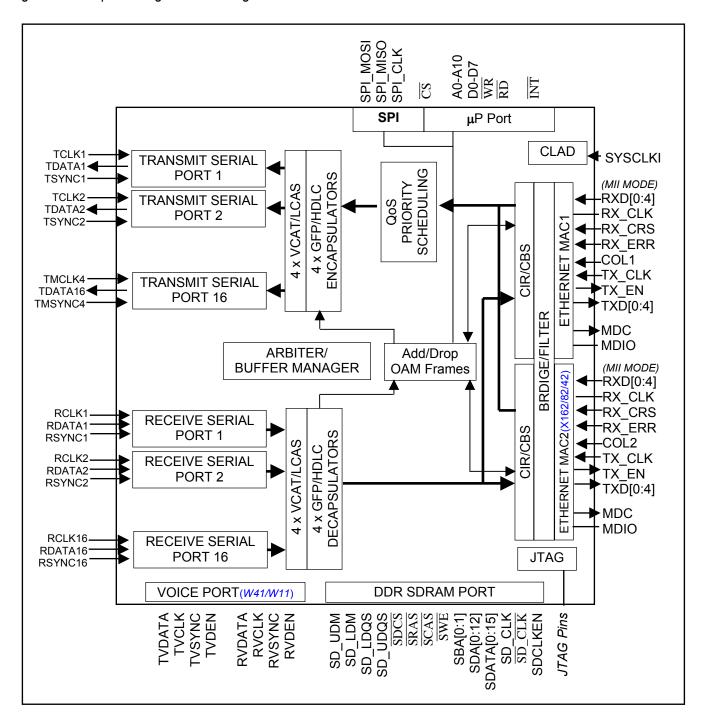

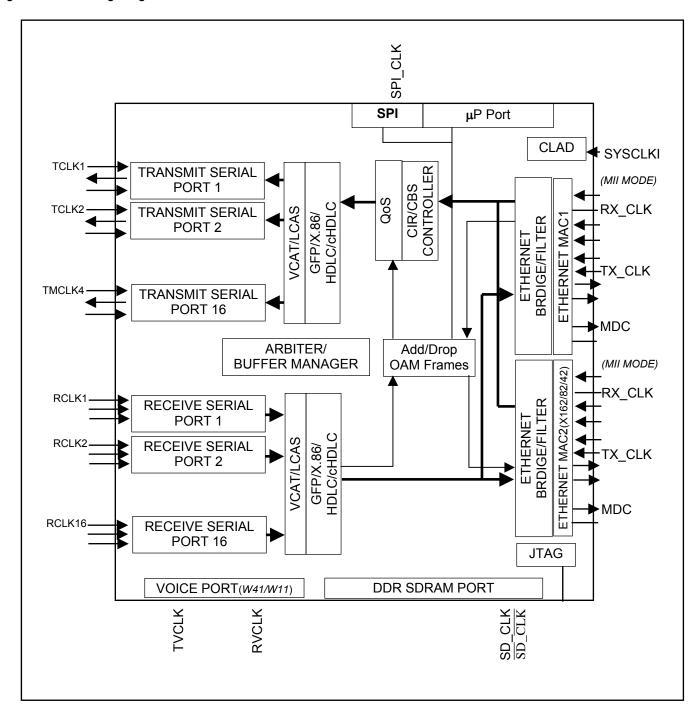

The DS33X162 family of devices provide interconnection and mapping functionality between Ethernet Systems and WAN Time-Division Multiplexed (TDM) systems such as T1/E1/J1, HDSL, T3/E3, and SONET/SDH. The device is composed of up to two 10/100/1000 Ethernet MACs, up to 16 Serial Ports, a Arbiter, GFP-F /HDLC/cHDLC/X.86 (LAPS) Mappers, a DDR SDRAM interface, and control ports. Ethernet traffic is encapsulated with GFP-F, HDLC, cHDLC, or X.86 (LAPS) to be transmitted over the WAN Serial Interfaces. The WAN Serial Interfaces also receive encapsulated Ethernet frames and transmit the extracted frames over the Ethernet ports. The LAN frame interface consists of Ethernet interfaces using one of two physical layer protocols. It can be configured with up to two 10/100Mbps MII/RMII ports or a single GbE GMII port. The WAN Serial Interface can be configured for up to eight serial data streams at up to 52Mbps each, or 16 serial data streams at up to 2.5Mbps each. The Serial Interfaces can be seamlessly connected to the Maxim T1/E1/J1 Framers, Line Interface Units (LIUs), and Single-Chip Transceivers (SCTs). The WAN interfaces can also be seamlessly connected to the Maxim T3/E3/STS-1 Framers, LIUs, and SCTs to provide T3, E3, or STS1 connectivity.

Microprocessor control can be accomplished through a 8-bit Micro controller port or SPI Bus. The device has a 125MHz DDR SDRAM controller and interfaces to a 32-bit wide 256Mb DDR SDRAM via a 16-bit data bus. The DDR SDRAM is used to buffer data from the Ethernet and WAN ports for transport.

The power supplies consist of a 1.8V core supply, a 2.5V DDR SDRAM supply, and 3.3V I/O supply. The DDR interface also requires a 1.25V reference voltage that can be obtained through a resistor-divider network.

**Table 1-1. Product Selection Matrix**

| Ordering<br>Number | Ethernet<br>Ports    | TDM<br>Ports | Voice<br>Ports | VLAN<br>Forwarding<br>Support | Supported<br>Forwarding<br>Modes | WAN<br>Groups<br>(VCGs) | μP<br>Control      | Package           |

|--------------------|----------------------|--------------|----------------|-------------------------------|----------------------------------|-------------------------|--------------------|-------------------|

| DS33X11+           | 1<br>10/100/GbE      | 1            | 0              | No                            | 2                                | 1                       | SPI                | 10mm 144<br>CSBGA |

| DS33W11+           | 1<br>10/100/GbE      | 1            | 1              | No                            | 2                                | 1                       | SPI or<br>Parallel | 17mm 256<br>CSBGA |

| DS33X41+           | 1<br>10/100/GbE      | 4            | 0              | No                            | 2                                | 1                       | SPI or<br>Parallel | 17mm 256<br>CSBGA |

| DS33W41+           | 1<br>10/100/GbE      | 4            | 1              | No                            | 1, 2, 3                          | 1 & 3                   | SPI or<br>Parallel | 17mm 256<br>CSBGA |

| DS33X42+           | 2 10/100<br>or 1 GbE | 4            | 0              | Yes                           | 1, 2, 3, 5                       | 1 & 3                   | SPI or<br>Parallel | 17mm 256<br>CSBGA |

| DS33X81+           | 1<br>10/100/GbE      | 8            | 0              | No                            | 2                                | 1                       | SPI or<br>Parallel | 17mm 256<br>CSBGA |

| DS33X82+           | 2 10/100<br>or 1 GbE | 8            | 0              | Yes                           | 1, 2, 3, 4, 5                    | 1, 2, 3, 4              | SPI or<br>Parallel | 17mm 256<br>CSBGA |

| DS33X161+          | 1<br>10/100/GbE      | 16           | 0              | No                            | 2                                | 1                       | SPI or<br>Parallel | 17mm 256<br>CSBGA |

| DS33X162+          | 2 10/100<br>or 1 GbE | 16           | 0              | Yes                           | 1, 2, 3, 4, 5                    | 1, 2, 3, 4              | SPI or<br>Parallel | 17mm 256<br>CSBGA |

Rev: 063008 9 of 375

# 2. Feature Highlights

#### 2.1 General

- 17mm 256 pin CSBGA Package (DS33X162/X161/X82/X81/X41/W41/W11)

- 10mm 144 pin CSBGA Package (DS33X11)

- 1.8V, 2.5V, 3.3V supplies

- IEEE 1149.1 JTAG boundary scan

- Software access to device ID and silicon revision

- Development support includes evaluation kit, driver source code, and reference designs

## 2.2 VCAT/LCAS Link Aggregation (Inverse Multiplexing)

- Link aggregation for up to 16 links per ITU-T G.7043/G.7042

- Up to 16 members per VCG

- 4 VCGs for the DS33X162/X82, 2 VCGs for the DS33X42, 1 VCG for the DS33X161/X81/X41/W41

- Differential delay compensation for up to 200 ms among members of a VCG

- Receive and Transmit are independent (asymmetry support)

- User programmable configuration of WAN ports used for VCG

- Supports Virtual Concatenation of up to 8 T3/E3 or 16 T1/E1

- VCAT/LCAS link aggregation not available in the DS33X11 and DS33W11

#### 2.3 HDLC

- Up to 4 HDLC Controller Engines

- Compatible with polled or interrupt driven environments

- Supports Bit stuffing/destuffing without Address/Control/PID fields

- Programmable FCS insertion and extraction, with removal of payload FCS

- 16-bit or 32-bit FCS, with support for FCS error insertion

- Programmable frame size limits (Minimum 64 bytes and maximum 2016 bytes)

- Selectable self-synchronizing X<sup>43</sup>+1 frame scrambling/descrambling

- Separate valid and invalid frame counters

- Programmable inter-frame fill for transmit HDLC

- Supports Transparency Processing and Abort Sequence

- Programmable frame filtering for FCS errors, aborts, or frame length errors

#### 2.3.1 cHDLC

- Bit stuffing with Address/Control/PID/FCS fields

- Programmable Interframe fill length.

- Transparency processing

- Counters: Number of received valid frames and erred frames

- Incoming Frame Discard due to FCS error, abort or frame length longer than preset max.

- The default maximum frame length is associated with the maximum PDU length of MAC frame

- Extract SLARP for external processor interpretation

Rev: 063008 10 of 375

### 2.4 GFP-F

- GFP Frame mode per ITU-T G.7041

- GFP idle frame insertion and extraction

- Supports Null and Linear headers

- cHEC based frame delineation

- X<sup>43</sup> +1 payload and Barker Sequence scrambling/descrambling

- CSF frame generation and detection

- Error detection over core header and type headers

- Programmable CRC-32 generation and verification

# 2.5 X.86 Support

- Encapsulation Per ITU-T X.86 (Link Access Procedure for SONET/SDH), with 32 bit FCS

- Transmit Transparency processing 7E is replaced by 7D, 5E

- Transmit Transparency processing 7D replaced by 7D, 5D

- Receive rate adaptation (7D, DD) removal.

- Receive Transparency processing 7D, 5E is replaced by 7D

- Receive Transparency processing 7D, 5D is replaced by 7D

- Receive Abort Sequence frame is dropped if 7D7E is detect

- Selectable self-synchronizing X<sup>43</sup>+1 frame scrambling/descrambling

- Counters: Number of received valid frames and erred frames

- Frame filtering due to bad Address/Control/SAPI, FCS error, abort, or frame length errors

#### 2.6 DDR SDRAM Interface

- 16-bit wide data bus with dual edge transfers and Auto Refresh Timing

- Designed to interface with 256Mbit JEDEC JESD79D compliant DDR SDRAMs with a 16-bit data bus

- Addressable memory range up to 256 Mbits

- JESD79D compliant device sizes other than 256 Mbits may be used, limited to 256 Mbit utilization

- Compatible with DDR266+

- SDRAM Interface Clock output of 125MHz

- Direct connection to external DDR SDRAM (P2P Mode Support)

- Example devices: Micron MT46V16M16, Samsung K4H561638F and Hynix HY5DU561622CF

#### 2.7 MAC Interfaces

- Two E/FE MAC ports with MII/RMII or one GbE port with GMII.

- 10Mbps/100Mbps/1000Mbps Data rates

- Configurable for DTE or DCE mode

- Facilitates auto-negotiation by host microprocessor

- Programmable half and full-duplex modes

- Flow control per 802.3 half-duplex (back-pressure) and full-duplex (pause) modes

- Auto Negotiation for Rates and duplex modes

- Programmable max MAC frame Lengths up to 2016 Bytes for E/FE, 12KB for GbE.

- Minimum MAC frame length: 64 bytes

- Discards frames larger than the max MAC frame size, Runt, non-octet bounded, or bad-FCS frames upon reception

- Programmable threshold for SDRAM queues to initiate flow control, with status indication

- Terminal and Facility Loopbacks at MAC port (without SA/DA swapping)

- Ethernet management interface (MDIO)

- Supports all applicable RMON (RFC2819) 32 bit counters with saturation at max count.

- Configurable for promiscuous mode and broadcast-discard mode.

Rev: 063008 11 of 375

#### 2.7.1 Ethernet Bridging for 10/100

- 4K Address and VLAN ID lookup table for Learning and Filtering

- Programmable Aging between 1 to 300 seconds in 1 second intervals

#### 2.7.2 Ethernet Traffic Classification

- Ingress Classification according to Ethernet COS

- Programmable class map to 4 queues for each Ethernet port

## 2.7.3 Ethernet Bandwidth Policing

- Bandwidth Policing with programmable CIR/CBS on Ethernet Ingress direction.

- Bandwidth Policing based on a per port basis.

- Programmable IEEE 802.3 Pause flow control or discard based on CIR/CBS

- Programmable Non-conforming Ethernet frame discard based on CIR/CBS

- See Section 8.21 for details on the granularity of CIR/CBS.

## 2.7.4 Ethernet Traffic Scheduling

- Programmable scheduler for Ethernet flows toward PDH port(s):

- Strict priority, or

- Weighted Queuing

#### 2.7.5 Connection Endpoints

- Connection between Ethernet port(s) and Serial(s) based on

- Ethernet side:

- o per Ethernet port, or

- o per VLAN ID (sub-interface)

- Priority (VLAN PCP or DSCP)

- WAN side (Serial):

- o per Serial port, or

- o per VCG bundle

#### 2.7.6 Virtual Connection

• Each connection configured for bi-directional flow with selected encapsulation.

## 2.7.7 Connection and Aggregation

- Forwarding between Endpoints based on the following options:

- Per Ethernet port ← → per serial port or per VCG

- o Per VLAN ID ← → per Serial port or port VCG

- VLAN Forwarding supported only in the DS33X42, DS33X82, and DS33X162

#### 2.7.8 Ethernet Control Frame Processing

- Control Frames, except PAUSE and OAM, shall be forwarded without processing.

- PAUSE and OAM frames can be programmed to be intercepted, discarded or forwarded.

#### 2.7.9 Q-in-Q

Programmable Carrier VLAN tag insertion.

Rev: 063008 12 of 375

#### 2.8 Serial Ports

- Four, Eight or Sixteen Serial ports with Synchronous Clock/Data at 128kbps to 52MHz.

- Independently clock inputs for RX and TX operations on the per port bases.

- Input clock supports either continuous or gapped clock

- Seamless interconnect with Maxim LIU/Framer/Transceiver devices for T1/E1/J1, and T3/E3

- Terminal and Facility Loopbacks per port

#### 2.8.1 Voice Ports

- The DS33W41 supports up to four voice ports; DS33W11 supports one voice port

- Each voice port supports up to 16 DS0s of voice to be multiplexed with Ethernet traffic

- Devices supporting voice input are restricted to T1/E1 WAN data rates

## 2.9 Microprocessor Interface

- Selectable 8-bit Parallel or SPI Serial data bus

- Multiplexed/Non-multiplexed Intel and Motorola Timing Modes

- Internal software reset and External Hardware reset input pin

- Global interrupt output pin

## 2.10 Slave Serial Peripheral Interface (SPI) Features

- Four-signal synchronous serial data link operating in full duplex slave mode up to 10Mbps

- Direct connection and fully compliant to popular communication processors such as MPC8260 and microcontrollers such as M68HC11

## 2.11 Test and Diagnostics

- IEEE 1149.1 Support

- Diagnostic Loopbacks

### 2.12 Specifications Compliance

The DS33X162 family of products adhere to the applicable telecommunications standards. The following list provides the specifications and relevant sections.

**IEEE:** 802.3-2002, CSMA/CD access method and physical layer specifications.

802.1D (1998): MAC Bridge 802.1Q (1998): Virtual LANs

802.1v-2001: VLAN Classification by Protocol and Port

802.1ag: Ethernet OAM (extract/insert support)

802.3ah: Ethernet First Mile (OAM extract/insert support)

IETF: RFC1662, PPP in HDLC-like Framing

RFC2615, PPP over SONET/SDH

RFC2918, RMON MIB (Hardware counters, extract/insert support)

ITU-T: X.86 Ethernet over LAPS

G.707 Network node interface for the synchronous digital hierarchy (SDH)

G.7041 Generic Framing Procedure (GFP) (12/2001)

G.7042 LCAS for VCAT signal (02/2004) G.7043 VCAT of PDH signals (07/2004)

G.8040 GFP over PDH Y.1303 Framed GFP Y.1323 Ethernet over LAPS

Y.1731 Ethernet OAM (extract/insert support)

**ANSI:** T1X1/2000-0243R Generic Framing Procedure

Other: RMII: Industry Implementation Agreement for "Reduced MII Interface," Sept 1997

Rev: 063008 13 of 375

# 3. Applicable Equipment Types

- ♦ Bonded Transparent LAN Service

- ♦ LAN Extension

- ♦ Ethernet Delivery over T1/E1/J1, T3/E3, xDSL, V.35/Optical

Figure 3-1. Standardized Ethernet Transport over Multiple T1/E1 Lines

#### **SOLUTION ADVANTAGES:**

- Up to 200ms of Differential Delay Tolerance, with VCAT/LCAS (ITU-T G.7042/G.7043) Link Aggregation

- Ethernet Transport Over Up to 16 T1/E1s or 8 DS3s with QoS and Ethernet OAM Capability!

- No Data Path Code Development Required!

- Committed Information Rate (CIR) Controller Can Be Used to Throttle Subscriber Bandwidth Usage!

- GFP, HDLC, LAPS, or cHDLC Encapsulation

- Advanced Forwarding Modes Allow Use of VLAN or Priority for Physical Port Assignment of Frames

Rev: 063008 14 of 375

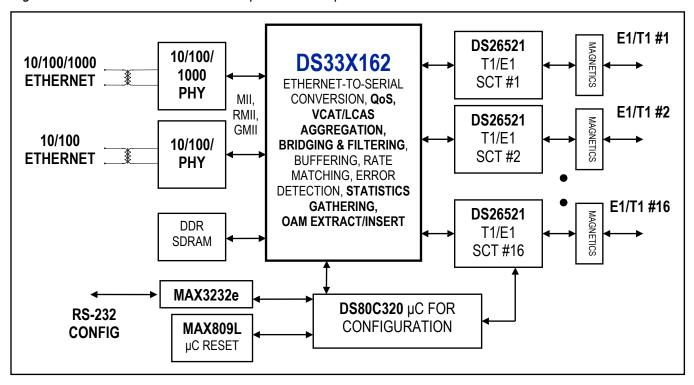

E1/T1 **DS33X11** 10/100/1000 MII, **DS26521** ETHERNET-TO-SERIAL **ETHERNET** RMII, CONVERSION, QoS. T1/E1 10/100/ **GMII BRIDGING & FILTERING,** SCT #1 1000 BUFFERING, RATE MATCHING, ERROR PHY DETECTION, STATISTICS **GATHERING, OAM** PROGRAMMABLE GAPPED CLOCK, DATA, AND **EXTRACT/INSERT** DDR **SDRAM** FRAME SYNC **MAX3232 DS80C320** μC **RS-232** FOR CONFIGURATION MAX809L **CONFIG** μC RESET

Figure 3-2. Standardized Ethernet Transport over a Single T1/E1 Line

#### **SOLUTION ADVANTAGES:**

- Ethernet Transport Over Single or Fractional E1/T1 with QoS and Ethernet OAM Capability!

- Flexible Fractional E1/T1 (Nx64kbps in Any DS0s) Support, Using DS26521 Channel Blocking

- No Data Path Code Development Required!

- GFP, HDLC, LAPS, or cHDLC Encapsulation

- Solution Extends Easily to DS3/E3

Rev: 063008 15 of 375

**8 AGGREGATED** T1/E1/J1s **xDSL LINE CARD DS33X81** MII/ RMII/ ETHERNET-TO-GMII **xDSL LINE CARD** SERIAL LINK **DS26528** ETHERNET SWITCH / ROUTER **AGGREGATION** OCTAL T1/E1/J1 GFP/VCAT/LCAS SINGLE-CHIP **xDSL LINE CARD** VLAN, Q-IN-Q, TRANSCEIVER BACKPLANE 10/100/GbE TO **SUBSCRIBERS** DS80C320 μC **SDRAM** 1000BASE-LX **GbE TRANSCEIVER xDSL LINE CARD**

Figure 3-3. Remote IP DSLAM T1/E1 Trunk Card

## **SOLUTION ADVANTAGES:**

- Standards Compliant Ethernet Transport Over Multiple E1/T1 Links

- QoS and Ethernet OAM Capability!

- No Data Path Code Development Required!

- GFP, HDLC, LAPS, or cHDLC Encapsulation

- Cost-Optimized Ethernet Transport

- Solution Extends Easily to DS3/E3

Rev: 063008 16 of 375

# 4. Acronyms & Glossary

- CLE Customer Located Equipment.

- CoS Class of Service, 802.1Q defined three User priority bits in Tag control Info Field.

- DCE Data Communication Interface.

- DSCP Diff Serve Code Point, IETF defined six bits in the IP ToS field.

- DTE Data Terminating Interface.

- EoPDH Ethernet over PDH. Ethernet encapsulated in HDLC or GFP, transported via one or more PDH lines.

- EoPoS Ethernet transport over PDH over SONET/SDH. Maintaining a PDH framing layer enables re-use of existing Ethernet-over-SSONET/SDH and PDH-over-SONET/SDH equipment for delivering Ethernet services.

- EoS Ethernet over SONET/SDH.

- FCS Frame Check Sequence.

- Frame A Layer-2 Protocol Data unit. (In general, Layer 2 frames carry Layer 3 packets).

- Gapped Clock Non-continuous clock used to strobe the associated synchronous Data at certain times.

- HDLC High Level Data Link Control.

- LAN Local Area Network. Usually used to refer to a local Ethernet segment.

- MAC Media Access Control. Lowest Digital Layer of Protocol Stack. Performs Framing, Sequencing, and Addressing.

- MII Media Independent Interface. One type of data bus between the physical layer (PHY) and the MAC.

- Packet A Layer 3 Protocol Data unit.

- PDH Plesiochronous Digital Hierarchy. The existing telephone network's "last mile." Primarily T1/E1 lines.

- PHY A device that interfaces an OSI logical layer to a physical media (Cat-5, twisted-pair, etc.). In this document, interfaces an Ethernet MAC to copper or fiber.

- RMII Reduced Media Independent Interface.

- VID- Virtual LAN Identifier.

- VCAT Virtual Concatenation. Used in conjunction with the Link Capacity Adjustment Scheme for transporting Ethernet over bonded PDH or SDH/SONET tributaries.

- WAN Wide Area Network. Typically T1(DS1), E1, T3(DS3), E3, or xDSL.

Rev: 063008 17 of 375

# 5. Designing with the DS33X162 Family of Devices

The DS33X162 family of products provide the required flexibility and complexity to meet the needs of a very broad range of applications. Although typical applications using these devices are very complex and each application has a unique set of needs, most application developments follow a predictable set of steps:

- 1. Identification of Application Requirements

- 2. Device Selection

- 3. Ancillary Device Identification

- 4. Circuit Design

- 5. Board Layout

- 6. Software Development

- 7. Production

## 5.1 Identification of Application Requirements

The designer of an application using one of the devices in the DS33X162 product line should begin by answering several high-level questions.

The solutions to these questions, in conjunction with referencing Table 1-1, will lead to a proper device selection:

How many and what type of TDM links are needed?

How does data need to move between the various interfaces of the mapping device?

What traffic prioritization methodologies will be needed?

How many Ethernet ports are needed?

Is direct multiplexing of PCM encoded voice traffic a requirement.

#### 5.2 Device Selection

The answer to "How many and what type of TDM links are needed?" will normally narrow the selection to devices that contain at least that many ports. For example, if 16 E1 links are required, the applicable solutions are the DS33X161 and DS33X162. If 4 DS-3 links are required, the applicable solutions are the DS33X41, DS33X42, DS33X81, DS33X82, DS33X161, and DS33X162.

The answer to "How does data need to move between the various interfaces of the mapping device?" will usually further narrow the selection. The path any given frame takes through the device can be determined by the contents of the frame, the port of entry, the user configured WAN Connections, and the user configured Forwarding Mode. Note that all devices in the product family allow insertion and extraction of frames for inspection, (including ITU-T Y.1731 OAM frames) by the host microprocessor, based on a number of conditions outlined in Section 8.17

If traffic flow is to be governed by VLAN tag information, the choices are narrowed to only those devices that support VLAN forwarding: DS33X42, DS33X82, and DS33X162. If ingress traffic is to be segregated by VLAN ID or DSCP Priority into separate WAN flows, the available number of WAN Groups in Table 1-1 should be considered. Several *Forwarding Modes* govern the flow of frames through the device. See Table 8-4 in Section 8.9 for more information.

Rev: 063008 18 of 375

# 5.3 Ancillary Device Selection

All devices in the product family require an external DDR SDRAM for operation. The user must select a JEDEC JESD79D compliant DDR SDRAM. DDR 266 or faster may be used. The recommended size is 256 Mbit (4 Meg x 16 x 4 banks), although it is possible to use other sizes (see Section 5.4). P2P operation is supported, and 0-ohm series termination is possible with proper PCB layout.

All devices in the product family require an external microprocessor for configuration and status monitoring. Because the DS33X162 family of devices are designed to require only a minimal amount of processor support, an inexpensive microcontroller can normally be used. In applications which make extensive use of the support for higher-layer protocols may require additional protocol processing capability, microprocessor selection can normally be determined by evaluating the management frame processing requirements of the particular application. All devices in the product family are designed to support both polled and interrupt-driven environments. Microprocessor control is possible through the 8-bit parallel control port or SPI Slave port. More information on microprocessor control is available in Section 8.1. Note that the parallel bus is not available in the 144 pin DS33X11, and the SPI Slave port must be used for processor control.

Depending on the application, external PDH framers and LIUs may be required. Maxim offers a broad range of framers, LIUs, and single-chip transceivers compatible with the DS33X162 family of products.

The Ethernet interface will normally be connected to an external Ethernet PHY or Ethernet switch device. Many commercially-available products are available and will seamlessly interface with the device's MII, RMII, or GMII options.

Several external clock sources are required for proper operation. See Section 8.3 for more information.

## 5.4 Circuit Design

Note that all devices except the DS33X11, DS33W11, and DS33W41 share a common footprint. This is intended to make it very easy to design a circuit that easily scales from 4 to 16 WAN ports with alternate assembly BOMs. When designing a PCB for 4 or 8 ports, care should be taken to tie the unused input pins for serial ports 5-16 or 9-16 to ground. This will allow for use of the higher density device for prototype purposes. Care should be taken that outputs from the DS33X162 family device that are present in the high-port count option but not in the low port-count option may potentially leave inputs on other devices floating, and should be pulled appropriately to a known voltage.

The device's DDR SDRAM interface is designed to use a JESD79D 256 Mbit (4 Meg x 16 x 4 bank) DDR SDRAM with a 16 bit data bus. If a larger DDR SDRAM must be used, the lowest 13 address lines (A0-A12) should be used, and care should be taken to ground any unused address inputs on the DDR SDRAM. Note that in such a case, only 256 Mbits are addressable by the device. If a smaller JESD79D DDR SDRAM is to be used (such as the 128 Mbit MT46V8M16), the unused address outputs should be left unconnected, and care should be taken in software to keep the starting and ending addresses of each queue within the same memory bank. In all cases, P2P operation is supported, and  $0\Omega$  series termination is possible with proper PCB layout.

### 5.5 Board Layout

The DDR SDRAM interface has particularly stringent layout requirements. Traces should have matched impedances, be of equal length, and should not have stubs. Refer to the DDR SDRAM's data sheet for more information. Supply decoupling should be placed as close to the device as possible.

### 5.6 Software Development

All devices in the product family have a common register set. An example initialization sequence is shown in Section 8.5. Software drivers and demonstration kit software are both available from Maxim. Go to <a href="https://www.maxim-ic.com/support">www.maxim-ic.com/support</a> for the latest information.

Rev: 063008 19 of 375

# 6. Block Diagrams

Figure 6-1. Simplified Logical Block Diagram

Rev: 063008 20 of 375

# 7. Pin Descriptions

# 7.1 Pin Functional Description

Note that all digital pins are inout pins in JTAG mode. This feature increases the effectiveness of board level ATPG patterns.

**Table 7-1. Detailed Pin Descriptions**

| NAME            | PACKAGE PINS |     | TVDE | FUNCTION                                                                                                                                                                                                                                                 |  |

|-----------------|--------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | 256          | 144 | TYPE | FUNCTION                                                                                                                                                                                                                                                 |  |

|                 |              |     | N    | MICROPROCESSOR PORT                                                                                                                                                                                                                                      |  |

| A0              | K10          | _   | I    | Address Bit 0. Address bit 0 of the microprocessor interface. Least Significant Bit. Note that the parallel bus is not available in the 144 pin DS33X11, and the SPI Slave port must be used for processor control.                                      |  |

| A1              | L9           | _   | I    | Address Bit 1. Address bit 1 of the microprocessor interface.                                                                                                                                                                                            |  |

| A2              | K11          | _   | Ι    | Address Bit 2. Address bit 2 of the microprocessor interface.                                                                                                                                                                                            |  |

| A3              | L10          | _   | I    | Address Bit 3. Address bit 3 of the microprocessor interface.                                                                                                                                                                                            |  |

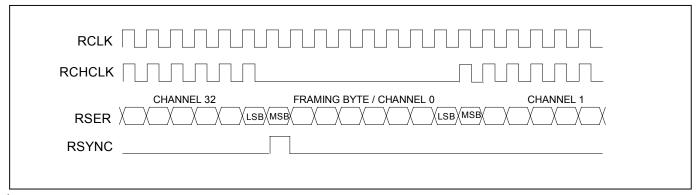

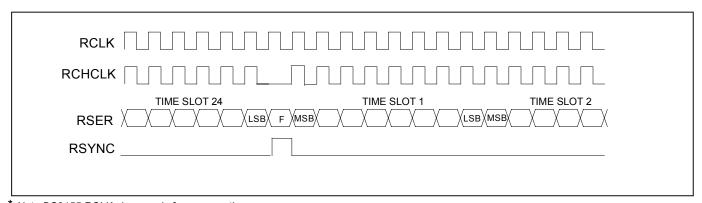

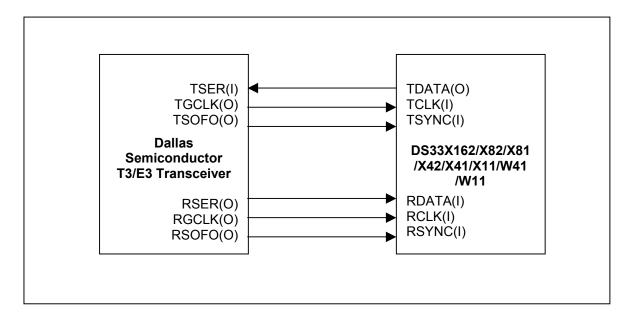

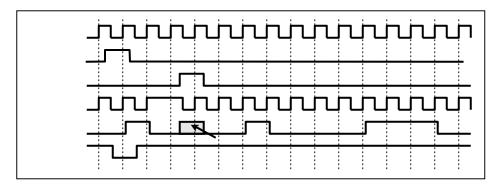

| A4              | K13          |     | _    | Address Bit 4. Address bit 4 of the microprocessor interface.                                                                                                                                                                                            |  |