### Triple 150mA Linear LED Controller

E522.80/81/82/83

Preliminary Information - Jun 23, 2015

#### **Features**

- Three independent Linear Current Drivers (3\*150mA)

- Parallel Output Operation for up to 450mA

- Low Power Standby / Sleep Mode

- Thermal Management Option per Channel

- Operating Input Voltage Range 5V to 25V, max. 40V

- External Reference Voltage / Derating Supported

- PWM Dimming (All channels or separate Channels)

- Diagnostic Functionalities (LED Driver Open/Short, IR Config Open/Short, Junction Temperature, Supply Voltage)

- Diagnostic Bus to link ICs

- Selectable "Failure Feedback Mode" or "Single Lamp Behaviour"

- AEC-Q100 Qualification

### **Applications**

- Automotive LED Lighting, Rear Lighting

- Turn Indicator Driver

- Medium Current Interior Lighting

- Industrial LED Applications or RGB Drivers

## Ordering Information

| Ordering-No.: | Temp <sub>Junc</sub> Range | Package    |

|---------------|----------------------------|------------|

| E52280A97D    | -40°C to +150°C            | SOIC16N-EP |

| E52281A97D    | -40°C to +150°C            | SOIC16N-EP |

| E52282A97D    | -40°C to +150°C            | SOIC16N-EP |

| E52283A97D    | -40°C to +150°C            | SOIC16N-EP |

### General Description

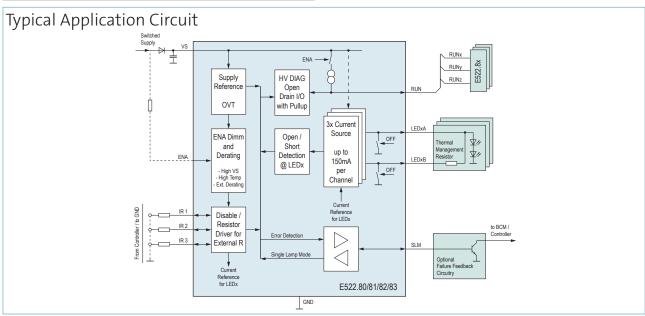

E522.80/81/82/83 family devices provide independent triple linear current controller for LED driving (standalone driver or LED cluster). Diagnostic features are provided to meet automotive requirements, together with a communication interface "RUN" to link ICs to generate more than three channels, supporting individual current configuration and independent digital PWM dimming per channel (e.g. for RGB).

Two external configurable modes of operation allow

- either "Failure Feedback Mode" FFM (operating channels in case of errors, with error signalization)

- or in "Single Lamp Mode" (turning all linked E522.8x's channels "off" in case of errors)

An intelligent power management system is provided using an external shunt resistor to share power distribution between IC package and external heat sink. Hotspot generation can be avoided by flexible heat spreading on the printed board. Internal derating for reference voltage and over-temperature shutdown for extreme temperatures >180°C protect E522.8x in case of abnormal operation conditions.

A high voltage capable input ENA can be used to either digitally enable or disable E522.8x. In addition, this input may be used as analog reference voltage input to realize e.g. thermal derating.

| Version | 'OPEN' Diagnostic                          | Package & Current                          |

|---------|--------------------------------------------|--------------------------------------------|

| E522.80 | Open Diagnostic at V <sub>vs</sub> > 7.5V  | SOIC16N-EP<br>I <sub>LED</sub> = 48mA151mA |

| E522.81 | Open Diagnostic at V <sub>vs</sub> > 9.0V  | SOIC16N-EP<br>I <sub>LED</sub> = 48mA151mA |

| E522.82 | Open Diagnostic at V <sub>vs</sub> > 10.0V | SOIC16N-EP<br>I <sub>LED</sub> = 48mA151mA |

| E522.83 | Open Diagnostic at V <sub>vs</sub> > 15.0V | SOIC16N-EP<br>I <sub>LED</sub> = 48mA151mA |

# Functional Diagram

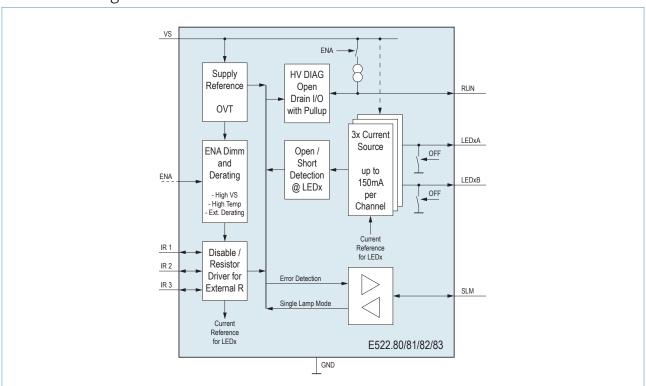

# Pin Configuration

# Pin Description

| Pin | Name           | Type 1) | Description                                                                       |

|-----|----------------|---------|-----------------------------------------------------------------------------------|

| 1   | NC             | A_I     | Not connected internally                                                          |

| 2   | RUN            | HV_A_IO | RUN Diagnostic Bus Interface to link 522.8x Products                              |

| 3   | VS             | HV_S    | High-Voltage Supply Input                                                         |

| 4   | GND            | S       | Ground Connection                                                                 |

| 5   | ENA            | HV_A_I  | High-Voltage Enable and optional analog Referencevoltage Input                    |

| 6   | IR1            | A_IO    | Current Configuration Channel 1, digital Input for Channel 1 dimming              |

| 7   | IR2            | A_IO    | Current Configuration Channel 2, digital Input for Channel 2 dimming              |

| 8   | IR3            | A_IO    | Current Configuration Channel 3, digital Input for Channel 3 dimming              |

| 9   | SLM            | A_IO    | Operating Mode Configuration ("Single Lamp Mode" or "Failure Feedback" Operation) |

| 10  | LED3A          | HV_A_O  | Bypass Output Channel 3, connect to LED directly                                  |

| 11  | LED3B          | HV_A_O  | Priority Output Channel 3, connect to LED via thermal Shunt                       |

| 12  | LED2A          | HV_A_O  | Bypass Output Channel 2, connect to LED directly                                  |

| 13  | LED2B          | HV_A_O  | Priority Output Channel 2, connect to LED via thermal Shunt                       |

| 14  | LED1A          | HV_A_O  | Bypass Output Channel 1, connect to LED directly                                  |

| 15  | LED1B          | HV_A_O  | Priority Output Channel 1, connect to LED via thermal Shunt                       |

| 16  | NC             | A_I     | Not connected internally                                                          |

| -   | Exposed<br>Pad |         | Exposed Pad, Connect to GND for thermal connection                                |

<sup>1)</sup> A = Analog, D = Digital, S = Supply, I = Input, O = Output, B = Bidirectional, HV = High Voltage

### 1 Absolute Maximum Ratings

Stresses beyond these absolute maximum ratings listed below may cause permanent damage to the device. These are stress ratings only; operation of the device at these or any other conditions beyond those listed in the operational sections of this document is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltages referred to VGND. Currents flowing into terminals are positive, those drawn out of a terminal are negative.

| No. | Description                                    | Condition                  | Symbol              | Min  | Max             | Unit |

|-----|------------------------------------------------|----------------------------|---------------------|------|-----------------|------|

| 1   | VS Pin Voltage                                 |                            | V <sub>VS</sub>     | -0.3 | 40              | V    |

| 2   | ENA Pin Voltage                                |                            | V <sub>ENA</sub>    | -0.3 | 40              | V    |

| 3   | IR1,2,3 Pin Voltage                            | 1)                         | $V_{IR,x}$          | -0.3 | 5.5             | V    |

| 4   | IR1,2,3 Pin Current                            |                            | I <sub>IR,x</sub>   | -1   | 1               | mA   |

| 5   | LEDx Current                                   |                            | I <sub>LED.x</sub>  | -170 | 100             | mA   |

| 6   | LEDxA/B Pin Voltage                            |                            | $V_{\text{LED,x}}$  | -1   | V <sub>VS</sub> | V    |

| 7   | RUN Pin Voltage                                |                            | V <sub>RUN</sub>    | -0.3 | V <sub>VS</sub> | V    |

| 8   | RUN Pin Current                                |                            | I <sub>RUN</sub>    | -5   | 5               | mA   |

| 9   | SLM Pin Voltage                                |                            | V <sub>SLM</sub>    | -0.3 | 6.5             | V    |

| 10  | Junction Temperature                           | Continuous                 | Tı                  | -40  | 150             | °C   |

| 11  | Ambient Temperature                            | Info Parameter 2)          | T <sub>A</sub>      | -40  | 125             | °C   |

| 12  | Storage Temperature                            | Unsoldered Device          | T <sub>ST</sub>     | -40  | 125             | °C   |

| 13  | Power Dissipation                              | t <sub>LIFETIME</sub> < 1h | P <sub>V,MAX</sub>  |      | 2.5             | W    |

| 14  | Thermal Resistance Junction to Exposed Die Pad | 3)                         | R <sub>TH,J-C</sub> |      | 6               | K/W  |

<sup>1)</sup> see parameter  $V_{IR, CLMP}$  for clamping behaviour

#### 2 ESD

| No. | Description                          | Condition | Symbol                 | Min  | Max | Unit |

|-----|--------------------------------------|-----------|------------------------|------|-----|------|

| 1   | ESD HBM Protection at all Pins       | 1)        | V <sub>ESD,HBM</sub>   | -2   | 2   | kV   |

| 2   | ESD CDM Protection at Corner Pins    | 2)        | V <sub>ESD,CDM,1</sub> | -750 | 750 | V    |

| 3   | ESD CDM Protection at all other Pins | 2)        | V <sub>ESD,CDM,2</sub> | -500 | 500 | V    |

<sup>1)</sup> According to AEC-Q 100-002, Human Body Model, 1.5k $\Omega$  resistance, 100pF capacitance.

<sup>2)</sup> consider maximum junction temperature and cooling measures to define ambient operating range

<sup>3)</sup> Typical thermal resistance to EP is  $R_{TH,J-C} = 3K/W$  (not production tested)

<sup>2)</sup> According to AEC-Q 100-011, Charged Device Model, pulse rise time (10% to 90%) <400ps,  $1\Omega$  resistance.

# 3 Recommended Operating Conditions

| No. | Description                                                      | Condition                 | Symbol                 | Min  | Тур | Max  | Unit |

|-----|------------------------------------------------------------------|---------------------------|------------------------|------|-----|------|------|

| 1   | Recommended Operating Voltage Range                              |                           | V <sub>VS,OP</sub>     | 5    | 14  | 25   | V    |

| 2   | Continous Power Dissipation in Package                           |                           | P <sub>V,OP</sub>      |      |     | 2.2  | W    |

| 3   | VS Capacitance per E522.8x                                       |                           | C <sub>VS,OP</sub>     | 220  | 330 |      | nF   |

| 4   | Nominal Value of Current-Selection<br>Resistor at IR1,2,3 to GND | LED Channel operating 1)  | R <sub>IR,x</sub>      | 9.53 |     | 30   | kΩ   |

| 5   | Capacitance at IRx Pin to drive R <sub>IR,x</sub>                |                           | C <sub>IR,x</sub>      |      |     | 100  | pF   |

| 6   | Typical Configured Operating Current per<br>Channel              | Sum of LEDxA and LEDxB 1) | I <sub>LED,x</sub>     | 48   | 120 | 151  | mA   |

| 7   | Dimming Frequency at either ENA or IRx                           | 2)                        | f <sub>PWM</sub>       | 50   | 200 | 1000 | Hz   |

| 8   | Minimum High / Low pulse- width in case of PWM Dimming           |                           | T <sub>PULSE,PWM</sub> | 90   |     |      | μs   |

| 9   | Total Capacitance for RUN Bus                                    | 3)                        | C <sub>RUN</sub>       |      |     | 1    | nF   |

| 10  | Capacitance at LEDx Driver Outputs                               | LEDxA and LEDxB           | C <sub>LED,x</sub>     |      | 6.8 | 22   | nF   |

| 11  | Inductance at either LEDxA oder LEDxB                            |                           | L <sub>LED,x</sub>     |      |     | 1    | μН   |

<sup>1)</sup> If selection interface IR is used with higher resistive values take a reduced accuracy into account. Pay attention to the 'open' state detection limit "IIR,OPEN" for IRx configuration

<sup>2)</sup> high PWM frequencies need to take into account, that there is an inherent startup delay between rising edge at IRx and current flow, which may influence PWM linearity

<sup>3)</sup> high capacitance values are possible but lead to additional delay between rising edge at ENA and startup of LEDx Drivers

### 4 Electrical Characteristics

$(V_{VS} = 5V \text{ to } 25V, T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C} \text{ and recommended operating range, unless otherwise noted.}$  Typical values are at  $V_{VS} = 14V \text{ and } T_{J} = 25^{\circ}\text{C}$ . Positive currents flow into the device pins.)

| Description                                                                   | Condition                                                                                                                   | Symbol                    | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| Supply and Bias                                                               |                                                                                                                             |                           |      |      |      |      |

| Enable threshold at ENA                                                       | V <sub>ENA</sub> rising                                                                                                     | V <sub>ENA,ON</sub>       | 1.14 | 1.2  | 1.26 | V    |

| Disable threshold at ENA                                                      | V <sub>ENA</sub> falling                                                                                                    | V <sub>ENA,OFF</sub>      | 1.0  | 1.06 | 1.13 | V    |

| ENA internal Pulldown Resistor                                                |                                                                                                                             | R <sub>ENA,PD</sub>       |      | 500  |      | kΩ   |

| VS undervoltage Release Threshold                                             | VS rising edge                                                                                                              | $V_{VS,ERR}$              | 3.8  | 4.1  | 4.4  | V    |

| VS undervoltage Hysteresis                                                    | VS falling edge                                                                                                             | V <sub>VS,ERR,HYST</sub>  |      | 440  |      | mV   |

| VS sleep mode Current                                                         | $V_{VS} = 14V$ $V_{ENA} = 0V$ $T_J \le 125$ °C                                                                              | I <sub>VS,SLEEP</sub>     |      | 12.5 | 28   | μΑ   |

| VS current in "Standby Mode"                                                  | V <sub>ENA</sub> > 3V<br>V <sub>RUN</sub> < 2V<br>No error detected<br>in device <sup>1)</sup>                              | I <sub>vs,stby,nom</sub>  |      | 90   | 140  | μΑ   |

| Average VS Current in "Single Lamp Mode,<br>Counting"                         | V <sub>ENA</sub> > 3V<br>"IR Open" error detected by device,<br>SLM open <sup>2)</sup>                                      | I <sub>VS,STBY,ERR</sub>  |      | 100  | 150  | μΑ   |

| Device current consumption<br>(GND pin current)                               | all channels regulating in saturation, no error detected $I_{\text{LED,x}} = 120 \text{mA}$                                 | $I_{GND,OP}$              |      | 1.4  | 2.1  | mA   |

| Overtemperature Shutdown                                                      | T, rising                                                                                                                   | T <sub>J,OT</sub>         | 165  | 185  |      | °C   |

| Overtemperature Recovery Hysteresis*)                                         | T, falling                                                                                                                  | T <sub>J,OT,HYST</sub>    |      | 20   |      | °C   |

| Initial Startup Delay of E552.8x after first<br>Power-Up*)                    | Initial delay after<br>V <sub>VS</sub> > V <sub>VS,ERR</sub><br>V <sub>ENA</sub> > V <sub>ENA,ON</sub>                      | t <sub>START</sub>        |      | 30   | 80   | μs   |

| LED Driver                                                                    |                                                                                                                             |                           |      |      |      |      |

| Current Amplification factor between IRx Input and LEDx Outputs               |                                                                                                                             | A <sub>I,LEDx/I,IRx</sub> |      | 960  |      |      |

| Ratio of Current in LEDxB to total configured Current $I_{\text{\tiny LEDx}}$ | $I_{LEDxB}/(I_{LEDxA}+I_{LEDxB})$<br>$V_{VS,LEDxB} > 1V$                                                                    | Q <sub>B/(A+B)</sub>      | 97   | 99.8 |      | %    |

| LED Current Tolerance (maximum)                                               | $ \begin{vmatrix} R_{IRx} = 9.53 \text{kOhm} \\ V_{VS} = V_{ENA} = 14 \text{V} \\ V_{VS, LEDx} > 1 \text{V} \end{vmatrix} $ | I <sub>LED,MAX</sub>      | -160 | -151 | -142 | mA   |

| LED Current Tolerance (high)                                                  | $ \begin{vmatrix} R_{IRx} = 12 kOhm \\ V_{VS} = V_{ENA} = 14 V \\ V_{VS,LEDx} > 1 V \end{vmatrix} $                         | I <sub>LED,HIGH</sub>     | -127 | -120 | -113 | mA   |

| LED Current Tolerance (low)                                                   | $R_{IRx} = 30kOhm$ $V_{VS} = V_{ENA} = 14V$ $V_{VS,LEDx} > 1V$                                                              | I <sub>LED,LOW</sub>      | -54  | -48  | -42  | mA   |

| Drop-Voltage of Bypass Outputs LEDxA for 120mA                                | I <sub>LEDxA</sub> = 120mA<br>LEDxB open <sup>1)</sup>                                                                      | $V_{\text{LEDxA,DROP}}$   |      | 250  | 450  | mV   |

| Drop-Voltage of Priority Outputs LEDxB for 120mA                              | I <sub>LEDxB</sub> = 120mA<br>LEDxA open <sup>1)</sup>                                                                      | V <sub>LEDxB,DROP</sub>   |      | 420  |      | mV   |

| Total pull down Resistance in case of LEDx being turned 'off'                 | $V_{VS} = 14V$<br>$V_{ENA} = 0V$<br>(LEDxA parallel<br>LEDxB)                                                               | R <sub>LED,PD,OFF</sub>   |      | 10   |      | kΩ   |

<sup>\*)</sup> Not tested in production

#### Notes on table section Supply and Bias

#### Notes on table section LED Driver

<sup>1)</sup> See state diagram in chapter "5.4 State Diagram" for details

<sup>2)</sup> Please note, that in case of LED or IR shortcircuit the average input current also depends on the configured current and the re-diagnostic dutycycle. Example: In case of a single LED short to GND the current at VS in SLM is typ. approx.  $100\mu$ A plus  $64/5900^*$ I<sub>LEDx</sub>

<sup>1)</sup> Parallel operation of LEDxA/B is possible to reduce Drop-Voltage

### Electrical Characteristics (continued)

$(V_{VS} = 5V \text{ to } 25V, T_J = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C} \text{ and recommended operating range, unless otherwise noted.}$  Typical values are at  $V_{VS} = 5V \text{ to } 25V, T_J = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C} \text{ and recommended operating range, unless otherwise noted.}$ 14V and  $T_J = 25$ °C. Positive currents flow into the device pins.)

| Description                                                                     | Condition                                                            | Symbol                      | Min  | Тур   | Max                  | Unit |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------|------|-------|----------------------|------|

| IR Driver                                                                       |                                                                      |                             |      |       |                      |      |

| Internal Nominal Reference to drive R <sub>IRX</sub>                            | $V_{ENA} > 3.3V$<br>$T_J < T_{J,DERATE}$                             | V <sub>REF,NOM</sub>        | 1.44 | 1.5   | 1.56                 | V    |

| Internal Reference Derating in case of high $V_{\text{VS}}$                     | V <sub>VS</sub> > 29V                                                | $V_{REF,HV}$                |      | 0.9   |                      | V    |

| Recommended Operating Range for External Reference at ENA $^{\mbox{\tiny 1}}$   | Condition                                                            | V <sub>REF,EXT</sub>        | 0.6  |       | $V_{\text{REF,NOM}}$ | V    |

| Internal Divider Ratio between ENA and IR in case of external Reference Voltage | 1.2V < V <sub>ENA</sub> < 3V                                         | N <sub>ENA,DIV</sub>        |      | 2     |                      |      |

| Internal Reference Derating Threshold for high $V_{\text{vs}}$                  | V <sub>vs</sub> rising                                               | $V_{VS,DERATE}$             | 25   | 27    | 29                   | V    |

| Hysteresis for Voltage Derating Threshold                                       | V <sub>vs</sub> falling                                              | V <sub>VS,DERATE,HYST</sub> |      | 1     |                      | V    |

| Starting Junction Temperature for internal Reference Voltage Derating*)         | V <sub>ENA</sub> > 3.3V                                              | $T_{J,DERATE}$              | 130  | 139   | 148                  | °C   |

| Internal Reference Voltage Derating Slope*)                                     | $V_{ENA} > 3.3V$<br>$T_J > T_{J,DERATE}$                             | dV <sub>J,DERATE</sub>      |      | -26.7 |                      | mV/K |

| Disable Threshold at IRx to disable according LED Channel                       | V <sub>IR</sub> rising <sup>2)</sup>                                 | $V_{IR,DIS}$                | 1.8  | 2.4   | 2.9                  | V    |

| Hysteresis for IR Disable*)                                                     | V <sub>IR</sub> falling                                              | $V_{IR,DIS,HYST}$           |      | 36    |                      | mV   |

| Zener Clamping at IRx <sup>3)</sup>                                             | $I_{IR} = 100 \mu A$                                                 | V <sub>IR,CLMP</sub>        | 5.25 | 6.1   | 7                    | V    |

| Pull down Current in IRx Driver for high $V_{\text{IR}}$                        | V <sub>IR</sub> = 4V                                                 | I <sub>IR,PD</sub>          |      | 6     |                      | μΑ   |

| Propagation Delay between Dimming Signal at IR and LED Driver Current Flow*)    | V <sub>ENA</sub> > 3V<br>V <sub>IR</sub> falling edge <sup>4)</sup>  | t <sub>IR,DEL</sub>         |      | 5     |                      | μs   |

| SLM Interface                                                                   |                                                                      |                             |      |       |                      |      |

| Pull down Current in SLM to drive 'low'                                         | Device nominal operation V <sub>SLM</sub> = 0.7V                     | I <sub>SLM,PD</sub>         |      | 15    |                      | μΑ   |

| Pull up Current in SLM to drive SLM 'high'                                      | Error detected in<br>Device<br>V <sub>SLM</sub> = 0.7V               | I <sub>SLM,PU</sub>         |      | - 250 |                      | μΑ   |

| Threshold to detect Mode of Operation                                           | 1)                                                                   | V <sub>SLM,HIGH</sub>       | 1.4  | 1.5   | 1.6                  | V    |

| PWM Frequency at SLM for Failure Signalization in FFM                           | V <sub>SLM</sub> < S <sub>SLM,HIGH</sub><br>Failure Feedback<br>Mode | f <sub>FFM,PWM</sub>        |      | 3.9   |                      | kHz  |

<sup>\*)</sup> Not tested in production

#### Notes on table section IR Driver

- 1) Take 2:1 divider at ENA into account

- 2) Intended for digital Control with switched GND Potential of RIR,x

- 3) An unused channel may be disabled by connecting to VS via a suitable Resistor

- 4) Disable propagation delay of a channel is typ. < 1 $\mu$ s ( $V_{IR}$  rising to >  $V_{IR,DIS}$ )

#### Notes on table section SLM Interface

1) For "Failure Feedback Mode" connect e.g. bipolar transistor to SLM, otherwise leave open for "Single Lamp Mode"

### Electrical Characteristics (continued)

$(V_{VS} = 5V \text{ to } 25V, T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$  and recommended operating range, unless otherwise noted. Typical values are at  $V_{VS} = 5V \text{ to } 25V, T_{J} = -40^{\circ}\text{C}$  to  $150^{\circ}\text{C}$  and recommended operating range, unless otherwise noted. Typical values are at  $V_{VS} = 5V \text{ to } 25V, T_{J} = -40^{\circ}\text{C}$  to  $150^{\circ}\text{C}$  and recommended operating range, unless otherwise noted. 14V and  $T_J = 25$ °C. Positive currents flow into the device pins.)

| Description                                                              | Condition                                                  | Symbol                       | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------------|------------------------------------------------------------|------------------------------|------|------|------|------|

| RUN Interface and Diagnostics                                            |                                                            |                              |      |      |      |      |

| RUN Pin Pull up Current to VS                                            | $V_{VS} = 14V$<br>$V_{RUN} = 0V$                           | I <sub>RUN,PU</sub>          |      | - 40 |      | μΑ   |

| RUN Bus Comparator,<br>High Threshold                                    |                                                            | V <sub>RUN,ENA</sub>         | 2.7  | 3    | 3.3  | V    |

| RUN Bus Comparator,<br>Low Threshold                                     |                                                            | $V_{RUN,STBY}$               | 2.25 | 2.55 | 2.85 | V    |

| Hysteresis for RUN Thresholds                                            | V <sub>RUN,ENA</sub> - V <sub>RUN,STBY</sub>               | $V_{\text{RUN},\text{HYST}}$ | 250  | 450  |      | mV   |

| RUN State Change Debouncing*)                                            | Rising and falling edge                                    | t <sub>RUN,DEL</sub>         |      | 4    |      | μs   |

| RUN Low Level, Nominal                                                   | $V_{VS} = 14V$<br>$I_{RUN} = 2mA$                          | V <sub>RUN,DRV1</sub>        |      | 0.2  | 0.8  | V    |

| RUN Low Level, low VS or VS Open                                         | VS Pin 'open' $I_{RUN} = 2mA$ $T_J < 125^{\circ}C$         | V <sub>RUN,DRV2</sub>        |      | 1.4  | 2    | V    |

| Current Limitation for RUN driving 'low'                                 | $V_{RUN} = 5V$                                             | I <sub>RUN,LIM</sub>         | 10   | 22   |      | mA   |

| LEDx Short Circuit Detection Threshold                                   | Relative to V <sub>GND</sub>                               | V <sub>LEDx,SHORT</sub>      | 0.9  | 1    | 1.1  | V    |

| Open Detection Threshold at LEDx, relative to nominal configured current | $R_{IRx} = 12k\Omega$ $V_{ENA} > 3V^{1}$                   | I <sub>LEDx,OPEN</sub>       | 27.5 | 37.5 | 47.5 | %    |

| Open Diagnostic Enable Threshold at VS for E522.80                       | E522.80 <sup>1)</sup><br>V <sub>vs</sub> rising            | V <sub>VS,DIAG1</sub>        | 7.1  | 7.5  | 7.9  | V    |

| Open Diagnostic Enable Threshold at VS for E522.81                       | E522.81 <sup>1)</sup><br>V <sub>vs</sub> rising            | V <sub>VS,DIAG2</sub>        | 8.55 | 9    | 9.45 | V    |

| Open Diagnostic Enable Threshold at VS for E522.82                       | E522.82 <sup>1)</sup><br>V <sub>vs</sub> rising            | V <sub>VS,DIAG3</sub>        | 9.5  | 10   | 10.5 | V    |

| Open Diagnostic Enable Threshold at VS for E522.83                       | E522.83 <sup>1)</sup><br>V <sub>vs</sub> rising            | V <sub>VS,DIAG4</sub>        | 14.2 | 15   | 15.8 | V    |

| Open Diagnostic Enable Threshold at VS,<br>Hysteresis                    | V <sub>vs</sub> falling                                    | $V_{VS,DIAG,HYST}$           |      | 0.5  |      | V    |

| IRx Pin Open Diagnostic Threshold                                        | absolute value                                             | I <sub>IR,OPEN</sub>         |      | 9    | 18   | μΑ   |

| IRx pin short circuit Diagnostic Threshold                               | absolute value                                             | I <sub>IR,SHORT</sub>        | 280  | 380  |      | μΑ   |

| Error Tolerance after Enabling a Channel                                 | $V_{ENA} > V_{ENA,ON}$<br>$V_{IR} < V_{IR,DIS}^{2}$        | t <sub>ERR,DEB1</sub>        |      | 64   |      | μs   |

| Additional Debouncing Time in case of Error Detection during Operation*) | New Error de-<br>tected                                    | t <sub>ERR,DEB2</sub>        |      | 4    |      | μs   |

| Re-Diagnosis time out in case of Error<br>Detection                      | ERR present,<br>E522.8x operated<br>undimmed <sup>3)</sup> | t <sub>err,rediag</sub>      | 4.1  | 5.9  | 9.1  | ms   |

<sup>\*)</sup> Not tested in production

### Notes on table section RUN Interface and Diagnostics

- 1) threshold is related to nominal current generated at IRx input. This diagnosis is active for VVS voltages higher than VVS, DIAGX

- 2) start up of a channel is performed within this tolerance time window

- 3) dimming the erroneous channel resets the according channels re-diagnostic cycle, thus a re-diagnostic is performed with the next enabling of the channel

### 5 Functional Description

#### 5.1 Overview

E522.80/81/82/83 family devices provide independent triple linear current controller for LED driving, which can optionally be operated in parallel for higher current requirements. These family members support individual current configuration and independent digital PWM dimming per channel (see IR interface).

Various diagnostic features are provided to meet automotive requirements, together with a communication interface named "RUN" to link ICs to generate more than three channels. ICs linked in this way can be operated as a combined cluster of drivers, turning 'on' and 'off' in parallel (e.g. turning all drivers 'off' in case of hardware failures).

Two external configurable modes of operation allow

- either "Failure Feedback Mode" FFM (operating channels in case of errors, with error signalization)

- or in "Single Lamp Mode" (turning all linked E522.8x's channels "off" in case of errors)

Typical exemplary application topologies are presented in "5.8 Exemplary Application Topologies".

More information on the LEDx drivers and power management can be found in "5.2 LED Driver".

For more details on the configuration and dimming via IRx interface see "5.3 IR Driver".

A detailed overview of functional states is given in "5.4 State Diagram".

Configuration of FFM or Single Lamp Mode is described in "5.5 SLM Interface".

Diagnostic features are located in "5.6 RUN Interface and Diagnostics".

Family members for lower current applications are provided as products E522.84/85/86/87, providing a high degree of functional compatibility to E522.80/81/82/83 at e.g. "RUN" pin. See the according data sheet for more details on these products.

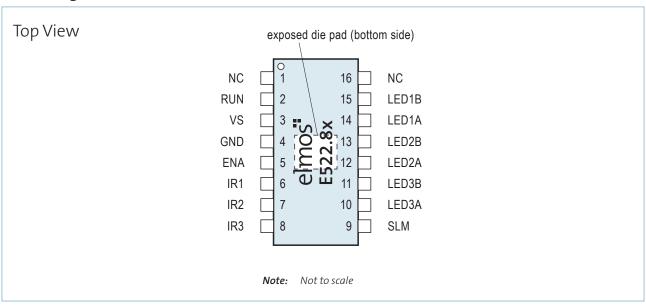

#### 5.2 LED Driver

High side drivers for LEDx provide the current configured by the according IRx pin, reproducing the IIRx with a typical amplification factor of 960:1. In E522.8x there are redundant outputs LEDxA and LEDxB to provide this current. These pins are intended for advanced thermal management (see Typical Application Diagram), sharing IC power with an external power sink as follows:

Figure 1. Power Management Example using a Channel of E522.8x at 120mA

To handle the high power that is typically generated in linear LED drivers, the 522.80/81/82/83 device family offers an advanced power distribution feature. The channels current is regulated as a sum of currents in LEDxA and LEDxB. The priority output LEDxB drives the current as long as the voltage headroom allows to. Afterwards the bypass output LEDxA is activated to deliver the remaining current flow.

This distribution of current allows to share some of the linear regulator power with the external Power-Shunt. "Figure 1. Power Management Example using a Channel of E522.8x at  $120\text{mA}^{\circ}$  shows the basic power generation per channel in (as a function of  $V_{Vs}$ )

- the LED load driven

- the external power shunt, given for exemplary values R1=33 $\Omega$ , R2=56 $\Omega$ , R3=82 $\Omega$

- the remaining power for this channel in E522.8x

For calculation, this principle offers two points of "zero" power in E522.8x, one for the  $V_{VS,Z1} = V_{LED}$  and a second "zero" power point at  $V_{VS,Z2} = V_{LED} + I_{LED} * R_{POWERSHUNT}$ . Beyond  $V_{VS,Z2}$  the power in E522.8x starts to increase linearly as for common linear LED drivers.

At the voltage derating threshold  $V_{VS,DERATE}$  the internal reference is reduced to 60% of nominal, thus the overall system power is reduced as shown to avoid excessive heat generation in case of e.g. load dump pulses.

#### 5.3 IR Driver

The interface IRx is used to configure the current in the according LEDxA/B channel. By connecting the IRx input to GND potential, the current flow in IRx is multiplied to LEDxA/B by a factor of typical 960:1.

Digital dimming can be applied to IRx by setting  $V_{IRx} > V_{IR,DIS}$ . A simple option to control the current is to switch the GND connection of  $R_{IRx}$  by a micro controller port, thus 'low' level drives the current into IRx, the high level disables the according channel.

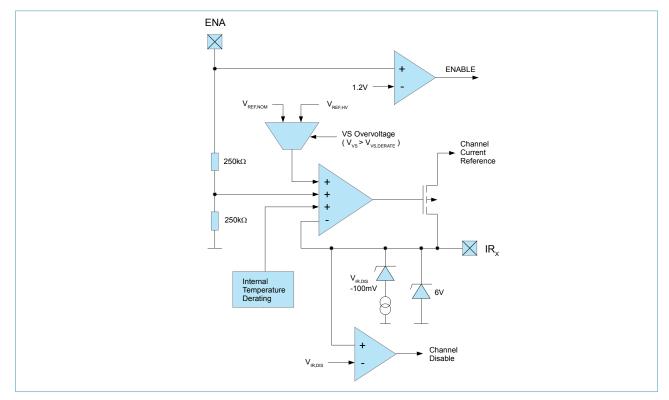

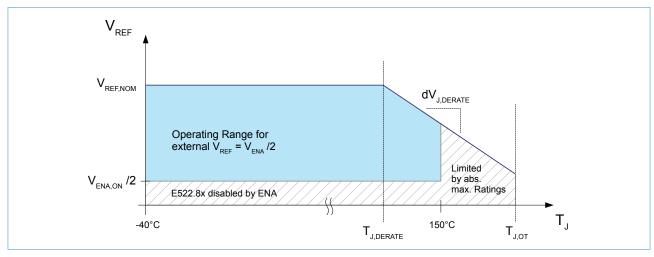

Various factors influence the reference voltage driven to IR as an output. Details are illustrated in Figure 2. In nominal case (typical junction temperature,  $V_{ENA} > 3V$ ) the internal reference is used. The lowest reference applied to the amplifier shown in Figure 2 is used to regulate  $V_{IR}$ .

Figure 2. IR Reference Generation

In case that less than three current drivers are needed, the internal clamping as shown in "Figure 2. IR Reference Generation" allows to connect this input to e.g. VS directly by a resistor of typ.  $100k\Omega$ .

Note that this resistor will contribute to the overall sleep mode or standby current of the application.

Connecting the IRx inputs statically to other supply voltages  $V_{SUPPLY} > V_{IR,DIS}$  is also possible to effectively disable the according channel. Please note, that the maximum supply voltage to turn IRx 'off' may be restricted by the clamping voltage at this pin, see parameter "VIR,CLMP".

Figure 3. Principle of Internal Temperature Derating

The internal reference derating function implemented is rather tolerant to allow external configuration of derating by the user. It typically starts to derate the internal reference at  $T_1 = 138^{\circ}$ C, falling with typ. -26.7mV/K beyond this temperature. The range of operating E522.8x with external reference or external derating is shown in "Figure 3. Principle of Internal Temperature Derating".

To realize an external derating function and shut down, it is possible to use e.g. a temperature dependent resistor divider at ENA. In the range of typically 3V down to  $V_{ENA,OFF}$  the voltage VENA/2 is used to drive  $V_{IR}$ . Falling below  $V_{ENA,OFF}$  disables E522.8x, restarting with  $V_{ENA,ON}$ .

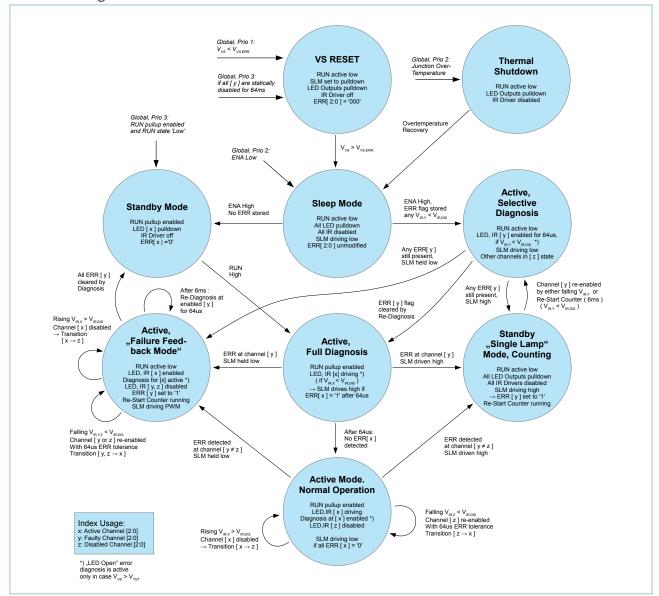

#### 5.4 State Diagram

Figure 4. State Diagram E522.80/81/82/83

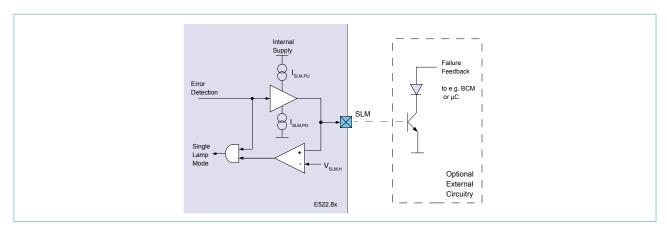

#### 5.5 SLM Interface

The pin SLM ("Single Lamp Mode") can be used to distinguish between single lamp behaviour or failure feedback mode (FFM). The basic setup of this pin is shown in "Figure 5. SLM Configuration".

**Single Lamp Mode** is characterized by switching all channels 'off' in case of a single failure on any channel. This behavior allows a network of LEDs to behave in a comparable manner to single bulb lamp. Other E522.8x devices should be connected by RUN to each other to allow switching other ICs to standby mode as well.

To operate E522.8x in this way, the pin SLM has to be left open, thus the voltage level  $V_{SLM}$  exceeds  $V_{SLM,HIGH}$ .

**Failure Feedback Mode** (FFM) is used to provide status feedback to some external circuitry, e.g. a microcontroller or a body control module. In this mode of operation a failing channel can be indicated, thus the other channels are not affected by the error detection and remain operated. This mode can as well be used in case of applications for which the diagnostics of channels must not affect other channels.

To use E522.8x in this way, it is recommended to use a bipolar external device and connect its base to SLM (a direct connection of SLM pin to GND is possible as well if channels shall be made independent of eachother). The threshold VSLM,HIGH is high enough to detect SLM as being held low by the base-emitter voltage of the external bipolar device. Other E522.8x in the application can share the same bipolar base to reduce device count (wired-OR).

Note, that RUN is switched to low in this case as well, thus a direct connection to other E522.8x is not recommended in FFM. (Remark: FFM can also be achieved by connecting SLM directly to GND).

More detailed information on the behavior of E522.80/81/82/83 can be found in the statediagram in "Figure 4. State Diagram E522.80/81/82/83".

Figure 5. SLM Configuration

During "Failure Feedback Mode" a 4 bit pulse-width modulated (PWM) signal is provided at the SLM output to determine which channels are failing. This protocol is repeated typically every  $256\mu s$  (typ.  $16\mu s$  bit-time), representing the actual ERR[2:0] state at the start of the PWM cycle.

The falling edge at SLM between typ. 56.3% and 93.8% represents the ERR[2:0] register status (only for enabled channels - disabled channels or channels without failure are treated as '0' in this PWM, see table below. Remark, a potential failure flag remains stored internally for re-diagnosis)

Note, that if all channels are disabled by IR dimming, SLM provides a static 'high' level (all ERR[2:0] entries are blanked by dimming). If the 'off' condition at IR is applied to a channel for typical >64ms, the according entry in ERR[2:0] register is resetted, see also chapter "5.6 RUN Interface and Diagnostics".

For physical layer implementation, make sure the output level is limited to avoid detection of SLM operating mode, e.g. by using an external NPN bipolar transistor per E522.8x ("Figure 5. SLM Configuration").

Table 1. PWM Dutycycle Reference Table

| PWM Dutycycle | ERR[2], channel LEDx3 | ERR[1], channel LEDx2 | ERR[0], channel LEDx1 |

|---------------|-----------------------|-----------------------|-----------------------|

| 100%          | '0'                   | '0'                   | '0'                   |

| 93.8%         | '0'                   | '0'                   | '1'                   |

| 87.5%         | '0'                   | '1'                   | '0'                   |

| 81.3%         | '0'                   | '1'                   | '1'                   |

| 75.0%         | '1'                   | '0'                   | '0'                   |

| 68.8%         | '1'                   | '0'                   | '1'                   |

| 62.5%         | '1'                   | '1'                   | '0'                   |

| 56.3%         | '1'                   | '1'                   | '1'                   |

Digital '0' represents either correct operation at LEDx or disabled channels ( $V_{IR,x} > V_{IR,DIS}$ )

**Example A**: PWM in case of channel LEDx2 failure detection (all channels enabled):

ERR[2:0] = '010' (no failures blanked by dimming at IRx)

=> PWM Dutycycle of 87.5%

**Example B**: PWM in case of channel LEDx2 & LEDx3 failure detection (channel LEDx2 disabled): ERR[2:0] = '110' (failure at channel 2 is blanked by dimming, thus the relevant register value becomes '100') => PWM Dutycycle of 75.0%

#### 5.6 RUN Interface and Diagnostics

Diagnostic features provided in E522.8x include the monitoring of

- High resistive IRx drivers for each channel (e.g. in case of 'open' connection for any of the connected devices)

- Short-circuit at IRx drivers to GND for each channel

- Short circuit of LEDxA/B to GND for each channel (checking for a static threshold of V<sub>LEDx,SHORT</sub>)

- Open LEDxA connections for each channel (E522.8x family members provide different thresholds of VVS to enable this

monitor, thus avoiding wrong 'OPEN' error detection in case V<sub>VS</sub> is smaller than the forward voltage of the LEDs (V<sub>LED</sub>)

- Internal junction overtemperature (disabling all channels)

- V<sub>vs</sub> voltage monitoring for undervoltage (providing defined behavior for slow supply ramping)

The driver "OPEN" detection is relative to the actual current configured at IRx. This detection is active if the supply  $V_{VS}$  is higher than  $V_{VS,DIAGx}$ , which is a family member specific threshold.

If a defect at any of the channels is detected, it is stored for selective re-diagnosis. Dimming at either ENA or  $V_{IR}$  does not delete this information. A diagnosis cycle showing removal of the erroneous conditions, VS under-voltage or permanent disable of all failing channels via IR input (see below) resets the stored flag(s) to '0'.

Erroneous channels can be deactivated and removed from state consideration by setting the according  $V_{IR,y} > V_{IR,DIS}$ . Once the disable request exceeds a length of typ. 64ms (in any mode other than 'Sleep Mode' or 'VS Reset'), the channel will no longer be considered for SLM or FFM state. In this way, e.g. a SLM application may be re-enabled (without the erroneous channel). For details see statediagram, global transitions into VS\_RESET state.

Re-diagnosis in case of continuous operation is performed on a regular time-basis of  $t_{ERR,REDIAG}$  to allow replacement of defect loads / LEDs for such applications.

A loss of VS connection for a single E522.8x is propagated via RUN being set to low, as well as for ENA being 'low' (e.g. in case of 'OPEN' failure at ENA).

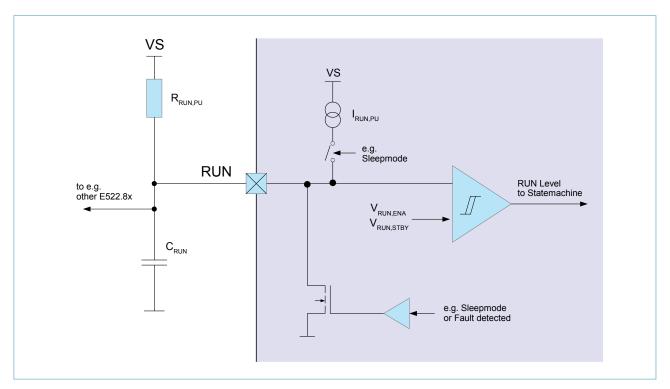

Figure 6. RUN Interface

The basic structure of the RUN interface is shown in Figure 6. Please note, that the purpose of the RUN bus is to form a direct connection to other family members E522.8x or local circuitry, preferably on the same PCB. In that case or if RUN is unused, the components  $C_{RUN}$  and  $R_{RUN,PU}$  may be omitted. They are recommended to protect the bus for additional requirements (e.g. EMC). The interface itself is not suitable for usage in a wiring harness without adequate protective measures.

The limits for usable values for  $C_{RUN}$  and  $R_{RUN,PU}$  are given by the tolerable delay at startup or from standby together with the current limitation for the RUN interface (see <u>"RUN Interface and Diagnostics"</u>). Furthermore,  $R_{RUN,PU}$  can contribute to sleepmode current consumption due to RUN being driven active low in this case.

### 5.7 Typical Performance Figures

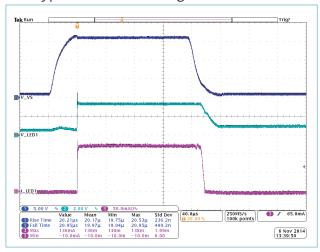

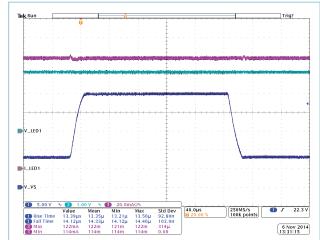

Figure 7. Fast Supply Step (Startup)

Typical Startup from unsupplied to 16V, Delay to deliver current is  $\!\!\!<\!\!40\mu s.$

Dark-Blue: VS-Supply, Bright-Blue: LED voltage, Purple: Current Probe for LED current

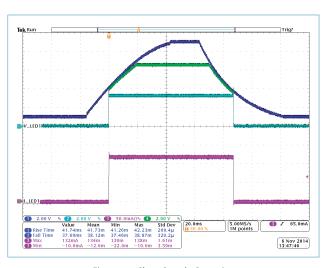

Figure 9. Fast Channel Switch-Over LEDA & LEDB

Switch-over between primary and bypass channel.

Dark-Blue: Supply at VS, Green: LED primary driver, BrightBlue: Bypass Driver (LED Voltage), Purple: LED Current

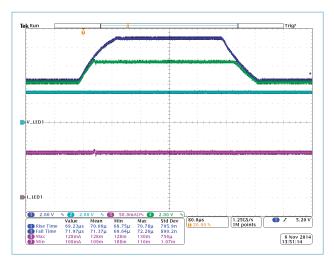

Figure 8. Slow Supply Ramping

Ramping of Supply in >20ms. Green and bright-blue channels show the primary and secondary LED driver outputs, darkblue is the supply voltage at VS. Purple Curve is the according current probed.

Figure 10. Very fast VS Stepresponse (8V to 25V)

Very steep rising and falling VS Supply, 8V to 25V at VS, Risetime approx. 14µs. Purple Channel: LED Current Bright-Blue Channel: LED Voltage Dark-Blue Channel: VS Supply Voltage (Step)

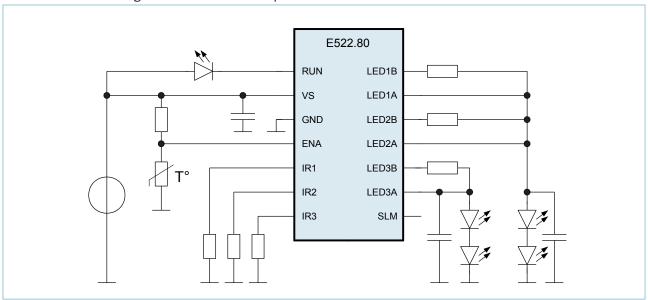

#### 5.8 Exemplary Application Topologies

This chapter provides various exemplary Application topologies and use-cases for E522.80/81/82/83. From basic setup to full automotive setup there are typical options given, which of course can be combined to more complex systems. Please make sure, that examples taken from this chapter fulfil your application requirements.

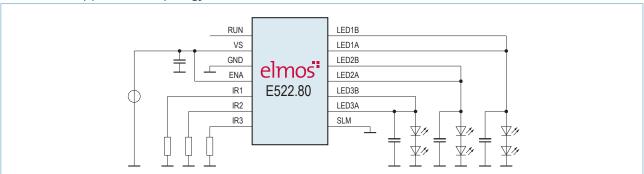

### 5.8.1 Basic Application Topology

Figure 11. Basic Topology

This is an exemplary basic implementation using E522.80/81/82/83 Family members. The basic features are

- Permanent operation of all LED strings

- Individual current configuration for each LED String

- Channels diagnostic does not interfere between channels (FFM mode used see SLM pin and RUN pin open)

- Capacitors at the LED loads are used to improve PSRR of the circuit

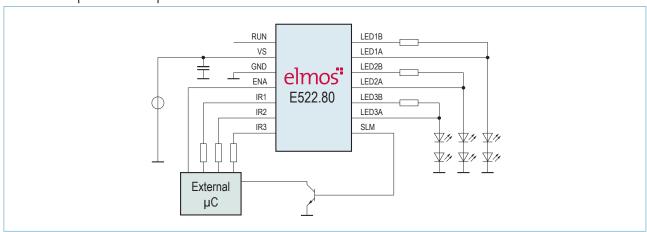

#### 5.8.2 Basic μC RGB Setup

Figure 12. RGB μC Topology

RGB driving is possible using the individual current configuration per channel of the LEDs via IR. An additional  $\mu$ Controller drives the resistors to GND (enable of channel) or to its supply (disable of channel).

- External controller provides colour mixtures by dimming at either IR1,2,3 or ENA

- Optionally, instead of digital signals, an analog reference can be generated by the controllers DAC to the ENA pin (with respect to the input impedance of ENA)

- Diagnostic feedback is provided from SLM by failure-feedback mode, indicating potential issues for a channel via PWM signal. In this way e.g. redundancy can be build for the colours, compensating a single channel fail with another LED string

Hint: Make sure, that the voltage drop across the controller ports is low to make sure, that reference current remains accurate.

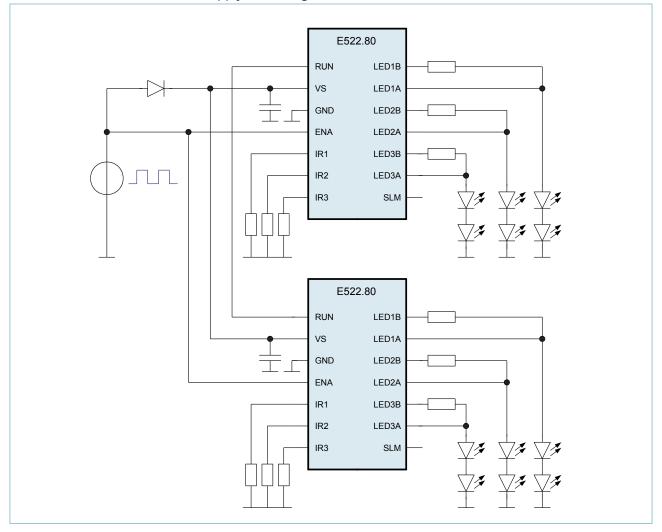

### 5.8.3 Six Channel Cluster and Supply-Dimming

Figure 13. Six Channel Cluster in SLM

This Application is a six-channel cluster, that makes use of the following product features:

- Digital Dimming via supply line is possible. ICs remain powered by reverse polarity protection and input capacitors, consuming only very low sleep mode currents.

- Single-Lamp Mode (SLM) is configured, deactivating all LEDs in case of a single channel failure on any LED Output. RUN connection is used to propagate the information between ICs, immitating the failing behaviour of a bulb if necessary.

- Thermal management resistors are applied to distribute the power on the PCB

### 5.8.4 Thermal Management and Parallel Operation

Figure 14. Thermal Application Topology

In this setup more thermal handling options are presented:

- Thermal shunts at LEDxB are used for power-distribution on the PCB

- Temperature depending divider at ENA provides derating, if the divided voltage falls below the internal reference of E522.8x

- Parallel operation of two channels to increase output current

- A fail-indicator LED is connected to RUN, which may be useful e.g. to identify defect PCBs

- Capacitors parallel to loads improve PSRR and thus the lifetime of the LEDs in case of e.g. ESD events

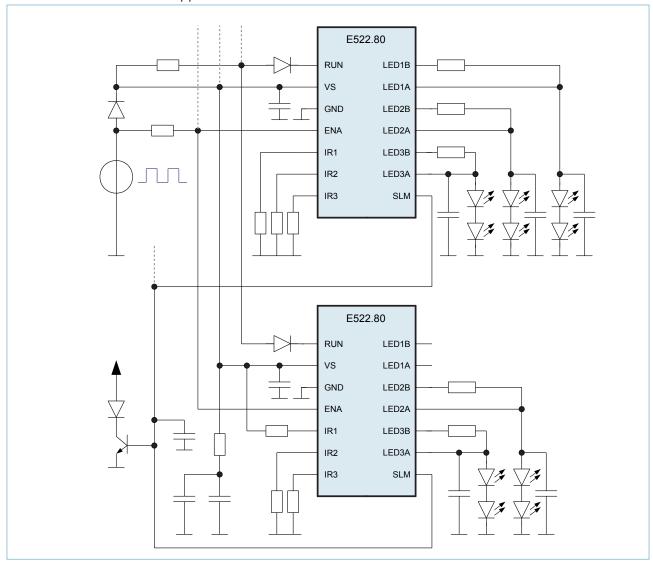

### 5.8.5 Automotive Cluster Application

Figure 15. Automotive Cluster Application

The application shows additional elements, that are typically useful for an automotive environment. Further elements may be necessary (e.g. input protection or suppressor diodes as required).

#### Features of this setup are:

- Digital dimming via battery line, e.g. from control modules highside driver

- RUN diode-Or bus for failure indication, making use of central bus pull-up resistor to VS. Hint: Take the resistor into account for sleep mode current consumption (ENA 'low' leads to active-low RUN state for all disabled ICs)

- If the RUN diagnostic bus drawn is not used by means of e.g. a local controller, it can be omitted for FFM (leave RUN pins just open)

- FFM (Failure-Feedback Mode): SLM is shared by more than one IC, driving a potential feedback path to the control module. In this mode a failure is reported, the cluster remains active

- Exemplary single-channel deactivation via IR Resistor to VS at lower IC

- Various protective devices added for automotive environment, like e.g. damping R-C network for inductive supply line

- Topology can be extended by further devices of the E522.8x family to build larger clusters

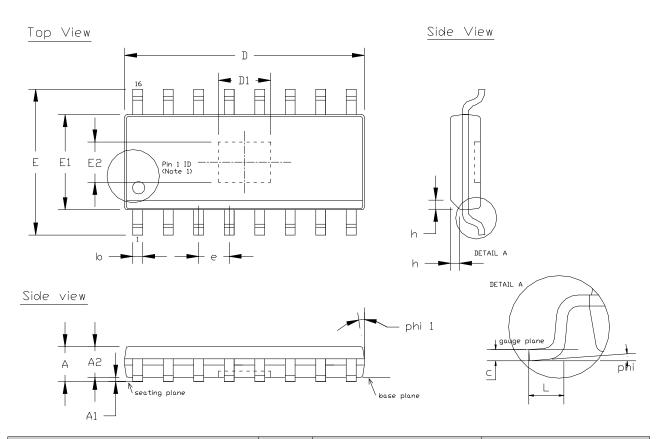

# 6 Package Reference

All devices are available in a Pb free, RoHs compliant SOIC16N-EP plastic package according to JEDEC MS-012-F, variant BC. The package is classified to Moisture Sensitivity Level 3 (MSL 3) according to JEDEC J-STD-020 with a soldering peak temperature of (260+5)°C.

| Description                                        | Symbol  |       | mm       |       |       | inch      |       |

|----------------------------------------------------|---------|-------|----------|-------|-------|-----------|-------|

| Description                                        | Symbol  | min   | typ      | max   | min   | typ       | max   |

| Package height                                     | Α       |       |          | 1.75  |       |           | 0.067 |

| Stand off                                          | A1      | 0.00  |          | 0.15  | 0.000 |           | 0.006 |

| Package body thickness                             | A2      | 1.25  |          |       | 0.049 |           |       |

| Width of terminal leads, inclusive lead finish     | b       | 0.31  |          | 0.51  | 0.012 |           | 0.020 |

| Thickness of terminal leads, inclusive lead finish | С       | 0.10  |          | 0.25  | 0.004 |           | 0.010 |

| Package length                                     | D       |       | 9.90 BSC |       |       | 0.390 BSC |       |

| Exposed pad length                                 | D1      | 2.290 | 2.540    | 2.800 | 0.090 | 0.100     | 0.110 |

| Package width                                      | Е       |       | 6.00 BSC |       |       | 0.236 BSC |       |

| Package body width                                 | E1      |       | 3.90 BSC |       |       | 0.154 BSC |       |

| Exposed pad width                                  | E2      | 1.780 | 2.030    | 2.290 | 0.070 | 0.080     | 0.090 |

| Lead pitch                                         | е       |       | 1.27 BSC |       |       | 0.050 BSC |       |

| Length of terminal for soldering to substrate      | L       | 0.4   |          | 1.27  | 0.016 |           | 0.050 |

| body chamfer (45°)                                 | h       | 0.25  |          | 0.50  | 0.010 |           | 0.020 |

| Angle of lead mounting area                        | phi [°] | 0     |          | 8     | 0     |           | 8     |

| nold release angle phi1 [ g 5 15                   |         | 5     |          | 15    |       |           |       |

| Number of terminal positions                       | N       |       | 16       |       |       | 16        | •     |

Note: the mm values are valid, the inch values contains rounding errors

# 7 Functional Safety

The development of this product is based on a process according to an ISO/TS16949 certified quality management system. Functional safety requirements according to ISO 26262 have not been submitted to Elmos and therefore have not been considered for the development of this product.

# 8 Record of Revision

| Chapter | Revision | Change and Reason for Change                                                                | Date         | Released Elmos |

|---------|----------|---------------------------------------------------------------------------------------------|--------------|----------------|

| -       | .00      | Initial revision                                                                            | Nov 26, 2014 | DHOE/ZOE       |

| 6       | .01      | Drawing and dimensions revised                                                              | Jun 23, 2015 | DHOE/ZOE       |

| -       | .01      | Product classification changed from advanced product information to preliminary information | Jun 23, 2015 | DHOE/ZOE       |

| -       | .01      | Adapted to the specification                                                                | Jun 23, 2015 | ASU/ZOE        |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

|         |          |                                                                                             |              |                |

#### WARNING - Life Support Applications Policy

Elmos Semiconductor AG is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing Elmos Semiconductor AG products, to observe standards of safety, and to avoid situations in which malfunction or failure of an Elmos Semiconductor AG Product could cause loss of human life, body injury or damage to property. In the development of your design, please ensure that Elmos Semiconductor AG products are used within specified operating ranges as set forth in the most recent product specifications.

#### **General Disclaimer**

Information furnished by Elmos Semiconductor AG is believed to be accurate and reliable. However, no responsibility is assumed by Elmos Semiconductor AG for its use, nor for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Elmos Semiconductor AG. Elmos Semiconductor AG reserves the right to make changes to this document or the products contained therein without prior notice, to improve performance, reliability, or manufacturability.

#### **Application Disclaimer**

Circuit diagrams may contain components not manufactured by Elmos Semiconductor AG, which are included as means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. The information in the application examples has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Elmos Semiconductor AG or others.

#### Contact Information

| <b>Headquarters</b> Elmos Semiconductor AG Heinrich-Hertz-Str. 1 • D-44227 Dortmund (Germany)                                                                                                                                   | <b>≘</b> :+492317549100   | ⊠: sales-germany@elmos.com   | ③: www.elmos.com |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------|------------------|

| Sales and Application Support Office North America<br>Elmos NA. Inc.<br>32255 Northwestern Highway • Suite 220 Farmington Hills<br>MI 48334 (USA)                                                                               | <b>≘</b> : +12488653200   | ⊠: sales-usa@elmos.com       |                  |

| Sales and Application Support Office China<br>Elmos Semiconductor Technology (Shanghai) Co., Ltd.<br>Unit 16B, 16F Zhao Feng World Trade Building,<br>No. 369 Jiang Su Road, Chang Ning District,<br>Shanghai, PR China, 200050 | <b>≘</b> : +86216210 0908 | ⊠: sales-china@elmos.com     |                  |

| Sales and Application Support Office Korea<br>Elmos Korea<br>B-1007, U-Space 2, #670 Daewangpangyo-ro,<br>Sampyoung-dong, Bunddang-gu, Sungnam-si<br>Kyounggi-do 463-400 Korea                                                  | 營: +82317141131           | ⊠: sales-korea@elmos.com     |                  |

| Sales and Application Support Office Japan<br>Elmos Japan K.K.<br>BR Shibaura N Bldg. 7F<br>3-20-9 Shibaura, Minato-ku,<br>Tokyo 108-0023 Japan                                                                                 | <b>≘</b> : +81334517101   | ⊠: sales-japan@elmos.com     |                  |

| Sales and Application Support Office Singapore Elmos Semiconductor Singapore Pte Ltd. 3A International Business Park #09-13 ICON@IBP • 609935 Singapore                                                                         | 營: +65 6908 1261          | ⊠: sales-singapore@elmos.com |                  |

© Elmos Semiconductor AG, 2015. Reproduction, in part or whole, without the prior written consent of Elmos Semiconductor AG, is prohibited.