### HALIOS® MULTI PURPOSE SENSOR FOR AUTOMOTIVE

E909.06

PRODUCTION DATA - APR 8, 2016

### **Features**

- Sensor IC based on HALIOS® technology

- Up to 4 sending channels, 1 compensation channel an 1 differential receiver input for various HALIOS® applications

- ▶ 16 bit micro controller 'EL16' with debug interface

- ► Up to 1.5K x 18 (3KByte) SRAM including 2 bit parity per 16 bit word and byte write support

- Up to 30K x 22 (60KByte) FLASH including 6 bit CRC checksum per 16 bit word

- ► SPI and I<sup>2</sup>C communication interface

- SCI interface incl. LIN support

- ► Watchdog, 32 bit timer, up to 8 GPIOs

- Multiply unit

- AEC-Q100 automotive qualification

- Supply voltage range 2.25V to 2.75V

# **Ordering Information**

| Ordering No.: | Temp. Range <sub>Amb</sub> | Package |

|---------------|----------------------------|---------|

| E90906A61C    | -40°C to +85°C             | QFN32L5 |

# **Applications**

- Optical or capacitive input devices

- Proximity and gesture detection

- Compact HMI interfaces for one-dimensional up to three-dimensional input

## **General Description**

The IC is based on an optical bridge technology which provides a non-mechanical detection of movements.

The system detects the optical reflections of an object in front of the sensor by using a function principle called HALIOS® (High Ambient Light Independent Optical System) which is very effective in the suppression of ambient light and also has self calibration capability to eliminate disturbances caused by housing reflections and scratches.

In the same manner capacitive systems can be addressed by using the integrated charge amplifier.

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

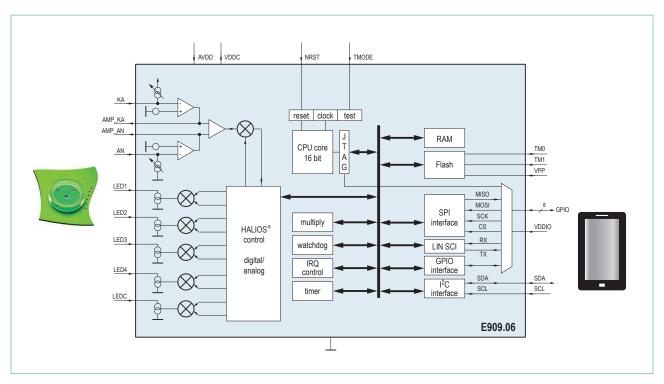

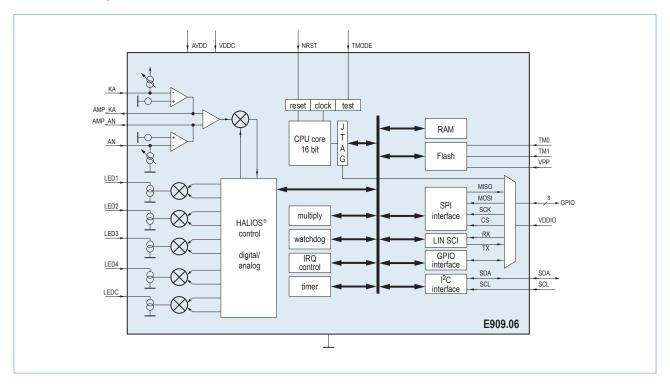

# 1 Block Diagram

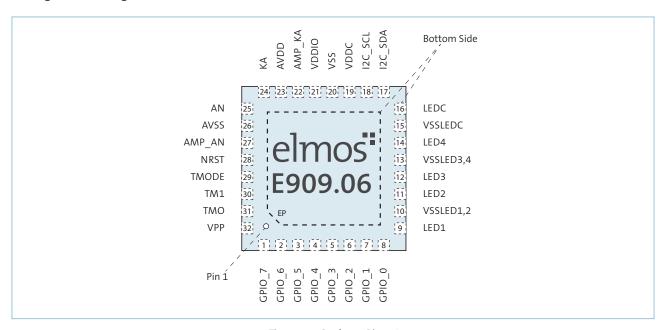

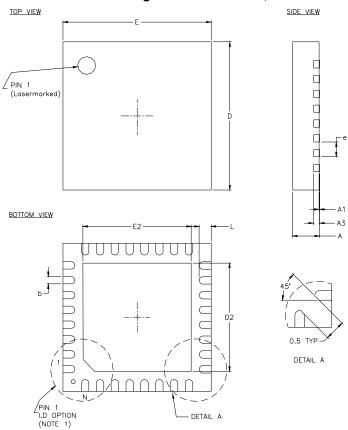

### 2 Pinout

## 2.1 Package Pinout

Package: QFN32L5

Package is according JEDEC MO-220-K, version VHHD-4.

Figure 1. Package Pinout

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# 2.2 Pin Description

| No | Name      | Type 1) | Description                                                                           |

|----|-----------|---------|---------------------------------------------------------------------------------------|

| 1  | GPIO_7    | D_IO    | General Purpose IO 7 (Sr)                                                             |

| 2  | GPIO_6    | D_IO    | General Purpose IO 6 (Sr)                                                             |

| 3  | GPIO_5    | D_IO    | General Purpose IO 5 (Sr)                                                             |

| 4  | GPIO_4    | D_IO    | General Purpose IO 4 (Sr)                                                             |

| 5  | GPIO_3    | D_IO    | General Purpose IO 3 (Sr)                                                             |

| 6  | GPIO_2    | D_IO    | General Purpose IO 2 (Sr)                                                             |

| 7  | GPIO_1    | D_IO    | General Purpose IO 1 (Sr)                                                             |

| 8  | GPIO_0    | D_IO    | General Purpose IO 0 (Sr)                                                             |

| 9  | LED1      | A_O     | LED Driver output                                                                     |

| 10 | VSSLED1,2 | S       | Ground LED1,2                                                                         |

| 11 | LED2      | A_O     | LED Driver output                                                                     |

| 12 | LED3      | A_O     | LED Driver output                                                                     |

| 13 | VSSLED3,4 | S       | Ground LED3,4                                                                         |

| 14 | LED4      | A_O     | LED Driver output                                                                     |

| 15 | VSSLEDC   | S       | Ground LEDC                                                                           |

| 16 | LEDC      | A_O     | LED Driver output                                                                     |

| 17 | I2C_SDA   | D_IO    | I2C SDA (Data)                                                                        |

| 18 | I2C_SCL   | D_IO    | I2C SCL (CLK)                                                                         |

| 19 | VDDC      | S       | Core Supply 2.5V                                                                      |

| 20 | VSS       | S       | Ground                                                                                |

| 21 | VDDIO     | S       | IO Supply 3.3V                                                                        |

| 22 | AMP_KA    | A_O     | Output 1. stage amplifier at KA                                                       |

| 23 | AVDD      | S       | Analog Supply 2.5V                                                                    |

| 24 | KA        | A_I     | Cathode                                                                               |

| 25 | AN        | A_I     | Anode                                                                                 |

| 26 | AVSS      | S       | Analog Ground                                                                         |

| 27 | AMP_AN    | A_O     | Output 1. stage amplifier at AN                                                       |

| 28 | NRST      | D_I     | Reset                                                                                 |

| 29 | TMODE     | D_I     | Testmode                                                                              |

| 30 | TM1       | A_IO    | Analog Testbus, only used for production test. This Pin must be left open.            |

| 31 | TM0       | A_IO    | Analog Testbus, only used for production test. This Pin must be left open.            |

| 32 | VPP       | HV_S    | FLASH Testmode pin, only used for production test. This Pin must be connected to GND. |

| -  | EP        | S       | Exposed Die Pad                                                                       |

<sup>1)</sup> D = Digital, A = Analog, S = Supply, I = Input, O = Output, HV = High Voltage

# **3 Operating Conditions**

## 3.1 Absolute Maximum Ratings

Continuous operation of the device above these ratings is not allowed and may destroy the device. All potentials refer to GROUND (GND) unless otherwise specified. Currents flowing into the circuit pins have positive values.

| No. | Description                                          | Condition                                           | Symbol                              | Min. | Max.                    | Unit |

|-----|------------------------------------------------------|-----------------------------------------------------|-------------------------------------|------|-------------------------|------|

| 1   | Supply voltage: digital core, analog part            | Referenced<br>to V <sub>ss</sub> / A <sub>vss</sub> | V <sub>DDC</sub> / A <sub>VDD</sub> | -0.3 | 2.8                     | V    |

| 2   | IO supply voltage/digital pins (see "type"/chapter)  | Referenced<br>to V <sub>ss</sub>                    | V <sub>DDIO</sub>                   | -0.3 | 3.7                     | V    |

| 3   | Input voltage analog pins (see "type"/chapter)       | Referenced<br>to A <sub>vss</sub>                   | V <sub>INA</sub>                    | -0.3 | A <sub>VDD</sub> + 0.3  | V    |

| 4   | Input voltage digital pins/GPIO (see "type"/chapter) | Referenced<br>to V <sub>ss</sub>                    | V <sub>IND</sub>                    | -0.3 | V <sub>DDIO</sub> + 0.3 | V    |

| 5   | Ground offset                                        | $V_{SS}$ to $A_{VSS}$ to $V_{SSLED}$                | Ground<br>offset                    | -0.3 | 0.3                     | V    |

| 6   | Junction Temperature                                 |                                                     | T <sub>j</sub>                      | -40  | +125                    | °C   |

| 7   | Storage Temperature                                  |                                                     | T <sub>STG</sub>                    | -50  | 150                     | °C   |

## 3.2 Recommended Operating Conditions

The following conditions apply unless otherwise stated. All potentials refer to GROUND (GND) unless otherwise specified. Currents flowing into the circuit pins have positive values.

| No. | Description                                         | Condition                          | Symbol                              | Min. | Тур. | Max. | Unit |

|-----|-----------------------------------------------------|------------------------------------|-------------------------------------|------|------|------|------|

| 1   | Supply voltage: analog part, digital core           | Referenced to $V_{ss}$ / $A_{vss}$ | V <sub>DDC</sub> / A <sub>VDD</sub> | 2.25 | 2.5  | 2.75 | V    |

| 2   | IO supply voltage/digital pins (see "type"/chapter) | Referenced<br>to V <sub>ss</sub>   | V <sub>DDIO</sub>                   | 3.0  | 3.3  | 3.6  | V    |

| 3   | Filter capacitor analog part                        | Connected to $A_{VDD}$             | C <sub>AVDD</sub>                   |      | 10   |      | μF   |

| 4   | Filter capacitor digital part                       | Connected to V <sub>DDC</sub>      | C <sub>VDDC</sub>                   |      | 100  |      | nF   |

| 5   | Ambient operating temperature range                 |                                    | T <sub>OPT</sub>                    | -40  | 25   | 85   | °C   |

| 6   | Thermal resistance, junction to ambient             | QFN32L5                            | R <sub>T,J-A</sub>                  |      | 35   |      | °C/W |

All voltages are referred to  $V_{ss}$ , and currents are positive when flowing into the node unless otherwise specified.

# **4 Detailed Electrical Specification**

The following conditions apply unless otherwise stated. All potentials refer to GROUND (GND) unless otherwise specified. Currents flowing into the circuit pins have positive values.

# 4.1 Supply Voltages

| No. | Description                                      | Condition                                                         | Symbol                | Min. | Тур.             | Max. | Unit       |

|-----|--------------------------------------------------|-------------------------------------------------------------------|-----------------------|------|------------------|------|------------|

| 1   | Digital operating current, run mode              | FSYS = 8 MHz,<br>system state:<br>run                             | l <sub>VDDC</sub>     |      | 5.8              | 12   | mA         |

| 2   | Digital operating current, standby mode          | System state:<br>standby                                          | I <sub>STANDBY</sub>  |      | 1.8              | 5    | mA         |

| 3   | Digital operating current, off mode              | System state:<br>off                                              | I <sub>OFF</sub>      |      |                  | 35   | μΑ         |

| 4   | Analog operating current                         | MCR[13:12]<br>="11"<br>PCR[14:13]<br>="11"                        | I <sub>AVDD</sub>     |      | 3.5              | 5    | mA         |

| 5   | Analog operating current                         | Analog on = 0                                                     | AVDD OFF              |      |                  | 15   | μΑ         |

| 6   | Over all current consumption in application mode | Active mode 1)                                                    | I <sub>ACTIVE</sub>   |      | 2.0              | 2.25 | mA         |

| 7   | Over all current consumption in application mode | Idle mode<br>(I <sub>IDLE</sub> = I <sub>OFF</sub> +<br>AVDD OFF) | I <sub>IDLE</sub>     |      | 19 <sup>2)</sup> | 88   | μΑ         |

| 8   | State change from STANDBY to RUN mode            | _                                                                 | T <sub>STANDB</sub> - |      |                  | 3    | 1/<br>FSYS |

| 9   | State change from OFF to<br>RUN mode             |                                                                   | T <sub>OFF2RUN</sub>  |      |                  | 5    | 1/<br>FSYS |

<sup>1)</sup> In application mode the current consumption is calculated from the duty cycle of the digital operating current and the analog operating current.

MCR - Measurement Configuration Register

PCR - Preamplifier Configuration Register

<sup>2)</sup> at 25℃

### 4.2 Reset Generation

| No. | Description                                                        | Condition                     | Symbol               | Min. | Тур.           | Max. | Unit              |

|-----|--------------------------------------------------------------------|-------------------------------|----------------------|------|----------------|------|-------------------|

| 1   | Power on reset level                                               | Reference is V <sub>DDC</sub> | V <sub>POR</sub>     |      |                | 2.25 | V                 |

| 2   | Brown out high-to-low threshold level                              | Reference is V <sub>DDC</sub> | V <sub>BOHL</sub>    | 1.7  |                |      | V                 |

| 3   | Brown out reset hysteresis                                         |                               | V <sub>BOHYST</sub>  | 100  | 200            | 300  | mV                |

| 4   | Minimum supply voltage for power on reset and brown out circuit 1) |                               | VDDmin               |      | 0.9            |      | V                 |

| 5   | NRST-pin threshold level                                           |                               | NRST <sub>LH</sub>   | 0.35 | 0.5            | 0.65 | V <sub>DDIO</sub> |

| 6   | Pull up current NRST-pin                                           | $V_{NRST} = V_{DDIO}$         | I <sub>NRSTPU</sub>  | 15   | 35             | 60   | μΑ                |

| 7   | Min. pulse width for a valid reset at pin NRST (debouncing)        | $V_{DDC} > V_{DDC min}$       | T <sub>DEBNRST</sub> | 1.0  |                | -    | μs                |

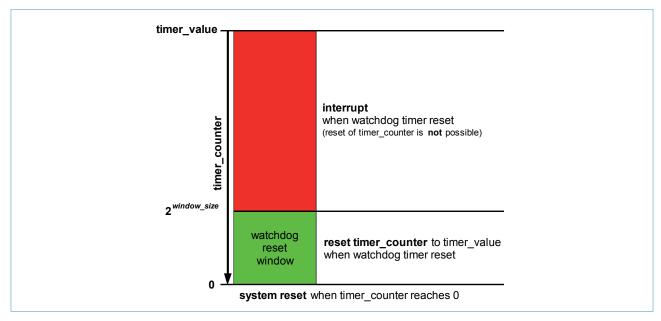

| 8   | Delay Watchdog start => reset 1)                                   |                               | T <sub>wdog</sub>    |      | timer<br>value |      | 1/<br>FSYS        |

<sup>1)</sup> Will not be tested in production test

### 4.3 Internal Clock Generation

### 4.3.1 Reference Clocks

| No. | Description            | Condition                                          | Symbol | Min.  | Тур.  | Max.  | Unit |

|-----|------------------------|----------------------------------------------------|--------|-------|-------|-------|------|

| 1   | Wakeup clock frequency | Within rec-<br>ommended<br>operating<br>conditions | FWK    | 108.2 | 128.0 | 147.2 | kHz  |

| 2   | Master clock           | Within rec-<br>ommended<br>operating<br>conditions | FSYS   | 7.2   | 8.0   | 8.8   | MHz  |

# 4.4 Module Description

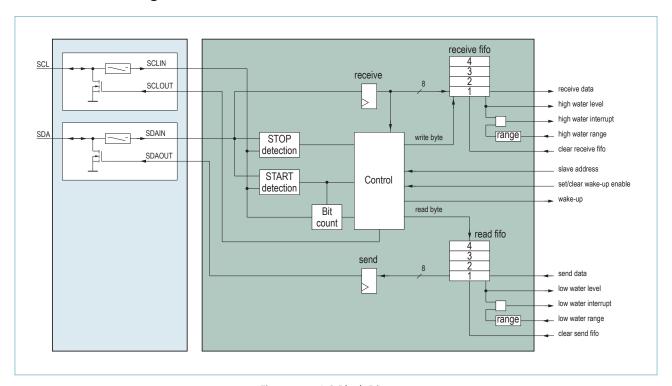

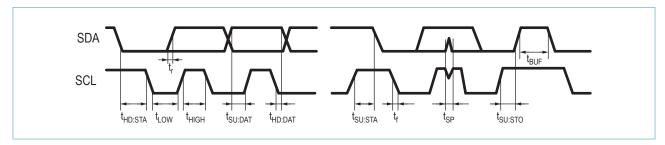

### 4.4.1 I<sup>2</sup>C Interface

| No. | Description                                                                                                           | Condition                               | Symbol                           | Min.                      | Тур. | Max.                    | Unit |

|-----|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------|---------------------------|------|-------------------------|------|

| 1   | SDA/SCL: Input voltage low                                                                                            |                                         | V <sub>IL</sub>                  | -0.3                      |      | 0.3 x V <sub>DDIO</sub> | V    |

| 2   | SDA/SCL: Input voltage high                                                                                           |                                         | V <sub>IH</sub>                  | 0.7 x V <sub>DDIO</sub>   |      | V <sub>DDIO</sub> + 0.3 | V    |

| 3   | SDA/SCL: Hysteresis of Schmitt trigger inputs 1)                                                                      | V <sub>DDIO</sub> > 2.0 V               | $V_{hys}$                        | 0.05 x V <sub>DDIO</sub>  |      | -                       | V    |

| 4   | SDA/SCL: Output voltage low (open drain)                                                                              | I = 3 mA, V <sub>DDIO</sub> > 2.0 V     | $V_{OL}$                         |                           |      | 0.4                     | V    |

| 5   | SDA/SCL: Input current                                                                                                | 0 < V <sub>IN</sub> < V <sub>DDIO</sub> | <b>I</b> <sub>i</sub>            | -10                       |      | 10                      | μΑ   |

| 6   | SDA/SCL: capacitance 1)                                                                                               |                                         | C <sub>i</sub>                   | -                         |      | 10                      | pF   |

| 7   | SCL clock frequency                                                                                                   |                                         | $f_{_{SCL}}$                     | 0                         |      | 400                     | kHz  |

| 8   | Hold time (repeated) START condition <sup>1)</sup>                                                                    |                                         | t <sub>HD.:STA</sub>             | 600                       |      | -                       | ns   |

| 9   | LOW period of SCL clock                                                                                               |                                         | $t_{low}$                        | 1300                      |      | -                       | ns   |

| 10  | HIGH period of SCL clock                                                                                              |                                         | $t_{_{HIGH}}$                    | 600                       |      | -                       | ns   |

| 11  | Set-up time for repeated start condition 1)                                                                           |                                         | t <sub>su.:STA</sub>             | 600                       |      | -                       | ns   |

| 12  | Data hold time 1)                                                                                                     |                                         | $t_{\scriptscriptstyle{HD.DAT}}$ | 0                         |      | 900                     | ns   |

| 13  | Data set-up time 1)                                                                                                   |                                         | $t_{\scriptscriptstyle{SU:DAT}}$ | 100                       |      | -                       | ns   |

| 14  | Rise time of SDA and SCL signals with a bus capacitance (C <sub>p</sub> ) from 10 pF to 400 pF <sup>1)</sup>          |                                         | $t_r$                            | 20 + 0.1 x C <sub>b</sub> |      | 300                     | ns   |

| 15  | Fall time of SDA and SCL signals with a bus capacitance (C <sub>p</sub> ) from 10 pF to 400 pF <sup>1)</sup>          |                                         | t <sub>f</sub>                   | 20 + 0.1 x C <sub>b</sub> |      | 300                     | ns   |

| 16  | SDA/SCL: Output fall time from VIH to VIL with a bus capacitance (C <sub>b</sub> ) from 10 pF to 400 pF <sup>1)</sup> |                                         | t <sub>of</sub>                  | 20 + 0.1 x C <sub>b</sub> |      | 250                     | ns   |

| 17  | Set-up time for STOP condition 1)                                                                                     |                                         | t <sub>su:sto</sub>              | 600                       |      | -                       | ns   |

| 18  | Bus free time between STOP and START 1)                                                                               |                                         | t <sub>BUF</sub>                 | 1300                      |      | -                       | ns   |

| 19  | Pulse width of spikes which<br>must be suppressed by the<br>IC-internal input filter                                  |                                         | t <sub>sp</sub>                  | 0                         |      | 30                      | ns   |

<sup>1)</sup> Will not be tested in production test

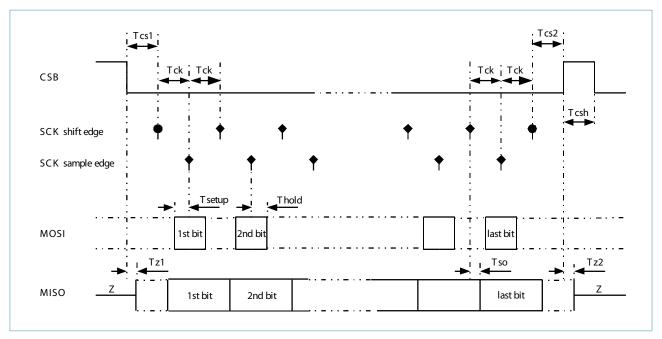

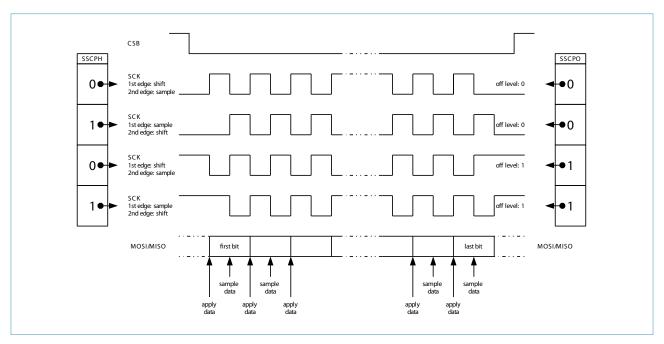

### 4.4.2 SPI Module

| No. | Description                            | Condition            | Symbol | Min. | Тур. | Max. | Unit       |

|-----|----------------------------------------|----------------------|--------|------|------|------|------------|

| 1   | SCK pulse low width / pulse high width | transfer             | Tck    | 4    |      |      | 1/<br>FSYS |

| 2   | First SCK after falling CSB            | start of<br>transfer | Tcs1   | 2    |      |      | 1/<br>FSYS |

| 3   | Last SCK before rising CSB             | end of<br>transfer   | Tcs2   | 2    |      |      | 1/<br>FSYS |

| 4   | Setup time                             |                      | Tsetup | 1    |      |      | 1/<br>FSYS |

| 5   | Hold time                              |                      | Thold  | 1    |      |      | 1/<br>FSYS |

| 6   | Data out after shift                   |                      | Tso    |      |      | 3    | 1/<br>FSYS |

| 7   | CSB high time                          |                      | Tcsh   | 2    |      |      | 1/<br>FSYS |

| 8   | Data out change from Z to driven data  | start of<br>transfer | Tz1    |      |      | 1    | 1/<br>FSYS |

| 9   | Data out change from driven data to Z  | end of<br>transfer   | Tz2    |      |      | 1    | 1/<br>FSYS |

### 4.4.3 GPIO Module

| No. | Description                               | Condition                                  | Symbol              | Min.  | Тур. | Max. | Unit |

|-----|-------------------------------------------|--------------------------------------------|---------------------|-------|------|------|------|

| 1   | Threshold point                           |                                            | GPIO <sub>TH</sub>  | 1.2   | 1.32 | 1.46 | V    |

| 2   | Pull down resistor                        | $V_{IN} > 0.75 \cdot V_{DDIO}$             | R <sub>GPIOPD</sub> | 45    |      | 155  | kΩ   |

| 3   | Output Voltage Low                        | GPIOIOL=4 mA;<br>V <sub>DDIO</sub> =3.3 V  | GPIOVOL             |       |      | 0.5  | V    |

| 4   | Output Voltage High                       | GPIOIOH=-4 mA;<br>V <sub>DDIO</sub> =3.3 V | GPIOVOH             | 2.4   |      |      | V    |

| 5   | Low Level Output Current                  | GPIOVOL=0.4V                               | GPIOIOL             | 4     |      | 17   | mA   |

| 6   | High Level Output Current                 | GPIOVOH=2.4V                               | GPIOIOH             | -25.6 |      | -6   | mA   |

| 7   | Tri-State Input/Output<br>Leakage Current | Vout=V <sub>DDIO</sub> or 0 V              | GPIOILC             | -5    |      | 5    | μΑ   |

## 4.4.4 HALIOS® Interface

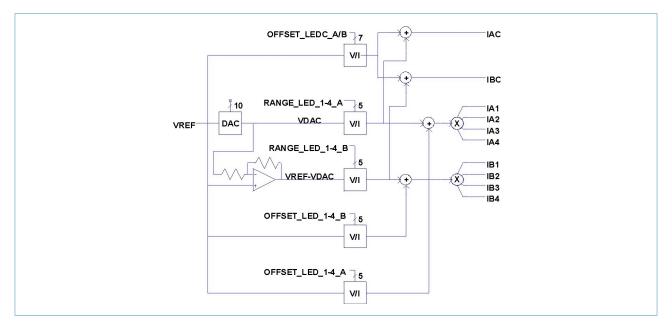

### 4.4.4.1 Current Generation for LED Modulators

| No. | Description                      | Condition | Symbol           | Min. | Тур. | Max. | Unit |

|-----|----------------------------------|-----------|------------------|------|------|------|------|

| 1   | DAC resolution                   |           | N                |      | 10   |      | bit  |

| 2   | Integral non linearity (INL)     |           | E <sub>i</sub>   |      | 2    |      | LSB  |

| 3   | Differential non linearity (DNL) |           | E <sub>d</sub>   |      | 2    |      | LSB  |

| 4   | DAC output voltage at full scale |           | V <sub>MAX</sub> | 1    | 1.22 | 1.5  | V    |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

## 4.4.4.2 LED Driver 1 - 4

| No. | Description                                             | Condition                 | Symbol               | Min. | Тур. | Max.                          | Unit |

|-----|---------------------------------------------------------|---------------------------|----------------------|------|------|-------------------------------|------|

| 1   | Regulated proportion of LED current @ DAC = 0           | DAC = 0                   | I <sub>R_MINS</sub>  |      |      | 5 % if I <sub>R_MAXS</sub> 1) | mA   |

| 2   | Max. regulated proportion of LED current (RANGE)        | RANGE = 31,<br>DAC = 1023 | I <sub>R_MAXS</sub>  | 6    | 10   | 14                            | mA   |

| 3   | Stepsize for regulated cur-<br>rent-range configuration |                           | I <sub>R_STEPS</sub> | 90   | 290  | 440                           | μΑ   |

| 4   | Resolution current-range configuration                  |                           | N <sub>RS</sub>      |      | 5    |                               | bit  |

| 5   | Max. fixed proportion of LED current (OFFSET)           | OFFSET = 31               | I <sub>O_MAXS</sub>  | 6.5  | 10   | 13.5                          | mA   |

| 6   | Stepsize for fixed offset-cur-<br>rent configuration    |                           | I_STEPS              | 90   | 290  | 440                           | μΑ   |

| 7   | Resolution offset-current configuration                 |                           | N <sub>os</sub>      |      | 5    |                               | bit  |

| 8   | DC-bias current                                         |                           | I <sub>BIAS S</sub>  | 60   | 225  | 400                           | μΑ   |

<sup>1)</sup>  $I_{R\_MAXS}$  is the maximum current selected with parameter RANGE

### 4.4.4.3 LED Driver C

| No. | Description                                             | Condition                 | Symbol                | Min. | Тур. | Max.                          | Unit |

|-----|---------------------------------------------------------|---------------------------|-----------------------|------|------|-------------------------------|------|

| 1   | Regulated proportion of LED current @ DAC = 0           | DAC = 0                   | I <sub>R_MINC</sub>   |      |      | 5 % of I <sub>R_MAXS</sub> 1) | mA   |

| 2   | Max. regulated proportion of LED current (RANGE)        | RANGE = 31,<br>DAC = 1023 | I <sub>R_MAXC</sub>   | 2    | 4    | 6                             | mA   |

| 3   | Stepsize for regulated cur-<br>rent-range configuration |                           | I <sub>R_STEPC</sub>  | 30   | 125  | 200                           | μΑ   |

| 4   | Resolution current-range configuration                  |                           | N <sub>RC</sub>       |      | 5    |                               | bit  |

| 5   | Max. fixed proportion of LED current (OFFSET)           | OFFSET = 127              | I <sub>O_MAXC</sub>   | 3    | 5    | 7                             | mA   |

| 6   | Stepsize for fixed offset-cur-<br>rent configuration    |                           | I <sub>O_STEPC</sub>  | 7    | 40   | 70                            | μΑ   |

| 7   | Resolution offset-current configuration                 |                           | N <sub>oc</sub>       |      | 7    |                               | bit  |

| 8   | Minimal value for DC-bias current                       |                           | I <sub>BIA_CO</sub>   | 30   | 100  | 200                           | μΑ   |

| 9   | Stepsize for DC-bias current                            |                           | DCO STEPC             | 0.5  | 2.5  | 3.6                           | mA   |

| 10  | Max. DC-bias current (DC_OFFSET)                        | DC_OFFSET<br>= 15         | I <sub>DCO_MAXC</sub> | 20   | 37.6 | 50                            | mA   |

<sup>1)</sup>  $I_{R\ MAXS}$  is the maximum current selected with parameter RANGE

### 4.4.4.4 Receiver

| No. | Description                                                                         | Condition                | Symbol                      | Min. | Тур. | Max. | Unit |

|-----|-------------------------------------------------------------------------------------|--------------------------|-----------------------------|------|------|------|------|

| 1   | Feedback resistor of 1. stage<br>amplifier at input KA and AN;<br>bit 0, bit 1 = 1  |                          | $R_f$                       |      | 50   |      | kΩ   |

| 2   | Feedback capacitor of 1.<br>stage amplifier at input KA<br>and AN; bit 2, bit 3 = 1 |                          | $C_f$                       |      | 3.6  |      | pF   |

| 3   | DC photo-current Gyrator<br>mode; bit 9, bit 10 = 1                                 |                          | l <sub>DC_photo</sub>       |      |      | 1000 | μΑ   |

| 4   | Voltage at amplifier input KA                                                       |                          | $V_{KA}$                    |      | 1.9  |      | V    |

| 5   | Voltage at amplifier input AN                                                       |                          | V <sub>AN</sub>             |      | 1.3  |      | V    |

| 6   | Corner frequency highpass filter                                                    |                          | $f_{_{G}}$                  |      | 10   |      | kHz  |

| 7   | Gain amplifier 2. stage                                                             |                          | $G_{0}$                     | 4    | 6    | 8    | dB   |

| 8   | Gain amplifier 3. stage                                                             | PCR[8:7]="01"            | $G_3$                       | 10   | 12   | 14   | dB   |

| 9   | Gain amplifier 3. stage                                                             | PCR[8:7]="00"<br>or "11" | $G_3$                       | 22   | 24   | 26   | dB   |

| 10  | Gain amplifier 3. stage                                                             | PCR[8:7]="10"            | $G_3$                       | 31   | 36   | 38   | dB   |

| 11  | Total gain sym. input                                                               | PCR[8:7]="01"            | G <sub>TOT</sub>            | 114  | 118  | 122  | dBΩ  |

| 12  | Total gain sym. input                                                               | PCR[8:7]="00"<br>or "11" | G <sub>TOT</sub>            | 126  | 130  | 134  | dBΩ  |

| 13  | Total gain sym. input                                                               | PCR[8:7]="10"            | $G_{\scriptscriptstyleTOT}$ | 138  | 142  | 146  | dBΩ  |

| 14  | Total gain nonsym. input                                                            | PCR[8:7]="01"            | G <sub>TOT</sub>            | 108  | 112  | 116  | dBΩ  |

| 15  | Total gain nonsym. input                                                            | PCR[8:7]="00"<br>or "11" | G <sub>тот</sub>            | 120  | 124  | 128  | dBΩ  |

| 16  | Total gain nonsym. input                                                            | PCR[8:7]="10"            | $G_{TOT}$                   | 132  | 136  | 140  | dBΩ  |

| 17  | Center frequency                                                                    | 1)                       | f <sub>c</sub>              |      | 125  |      | kHz  |

| 18  | Resolution demodulator output                                                       |                          | N <sub>DEMOD</sub>          |      | 1    |      | bit  |

| 19  | Capacitance of photo diode at input KA                                              | 1)                       | C <sub>DIODE</sub>          |      |      | 70   | pF   |

| 20  | Internal reference current                                                          |                          | I <sub>BIAS</sub>           | 5    | 10   | 16   | μΑ   |

PCR - Preamplifier Configuration Register

<sup>1)</sup> Will not be tested in production test

## **5 Functional Description**

#### 5.1 Introduction

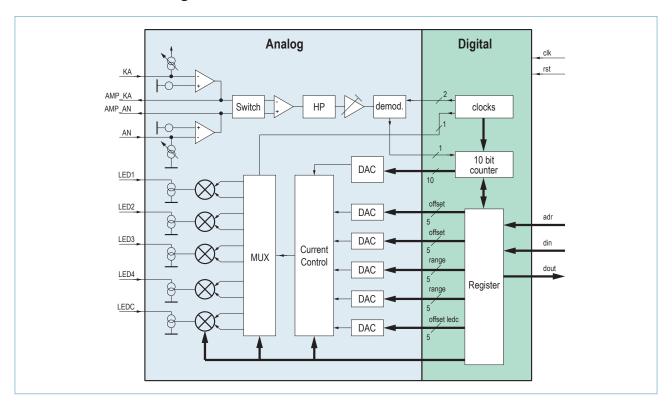

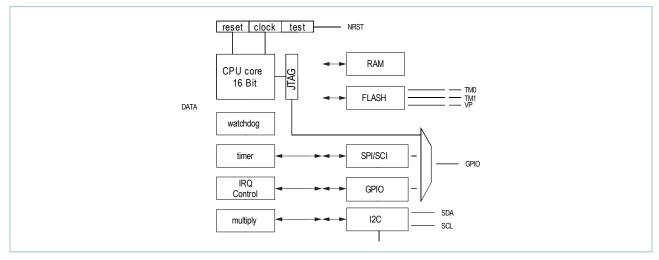

The general architecture of the 3D-optical input device is shown in the system block diagram.

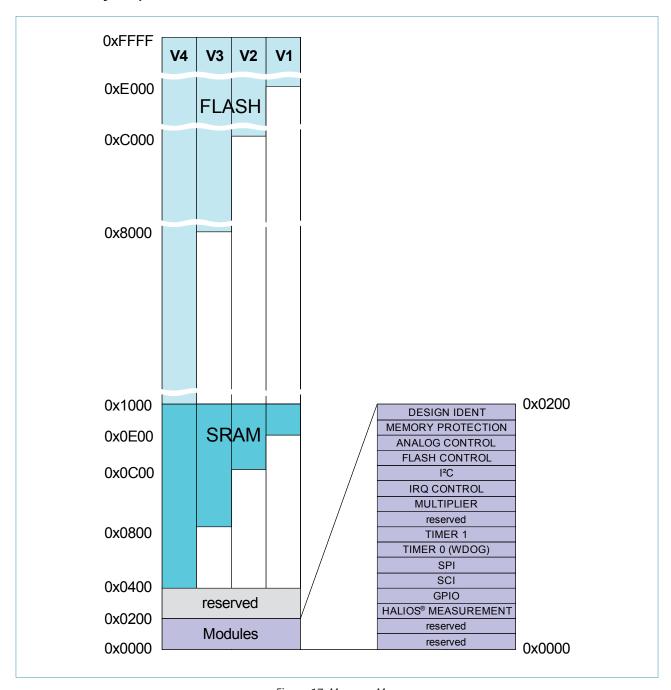

The CPU is connected to the memory (FLASH and SRAM) and the peripheral modules via the internal system bus. The system bus provides a 16 bit address space and allows 8 and 16 bit data transfers.

The memory contains the program code and the data. Memory and registers are mapped to the global memory map and can be accessed through all memory related operation provided by the CPUs instruction set. The memory of the ASIC consists a FLASH cell up to 30Kx22 (60KByte) including 6 additional bits per word used as CRC for error detection and error correction and a SRAM cell up to 1.5Kx18 (3KByte) including 2 bit parity per word.

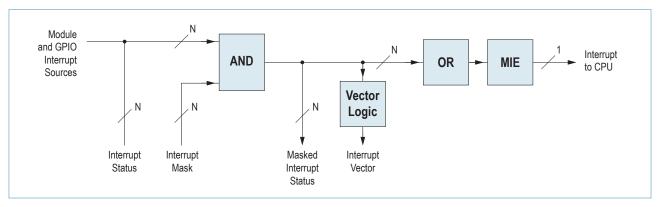

The Interrupt Controller collects requests from all interrupt sources and provides an interrupt signal to the CPU. Interrupt sources can be masked within the interrupt controller. Interrupts are generated by the modules and hold until they are cleared within the module. See module description for clearing procedures.

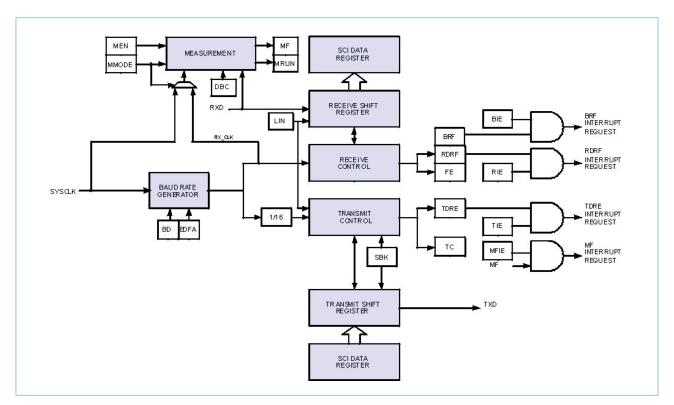

The SPI can be configured either as a master or a slave. Transfer length is eight bit and can be extended by a multiple of eight bit. Data FIFOs are provided for transmit and receive tasks.

The SCI provides the standard NRZ (Non Return to Zero) mark/space data format where each frame contains one start bit, eight data bits and one stop bit. Several features are implemented for special LIN support.

The timer module contains a 32 bit timer module as well as a watchdog timer. Additionally a second timer module operating on wakeup clock is implemented that remains active even in off mode, so it can be used for a periodical wake up from off mode for applications that require a low current consumption.

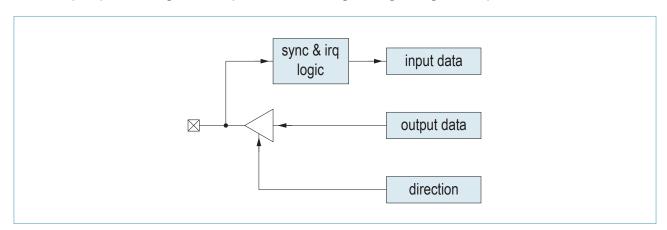

8 IO port pins can either be configured as general purpose IO's or can be configured as ports for the SPI or SCI module. Additionally two ports are reserved for the I<sup>2</sup>C slave interface.

The clock and reset generator module provides the system clock and the global reset signal. A power-on-reset, brown out detect and a power watch are implemented. As external reset source a reset input will be considered. The system clock is generated by an on-chip oscillators. A more detailed diagram of the clock/reset generation block (CRG) is shown in the following sections.

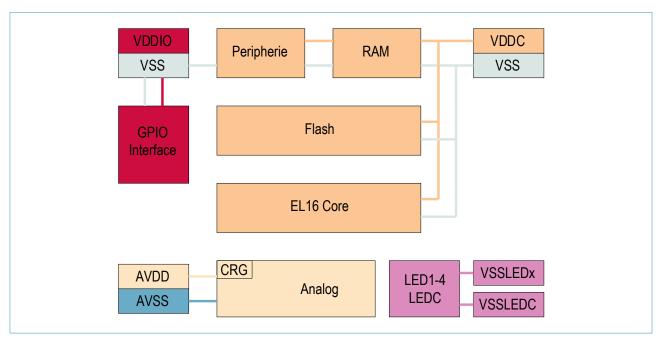

## 5.2 Supply Voltages

### 5.2.1 Block Diagram

Figure 2. Block Diagram Supply Voltages

## **5.2.2 Functional Description**

Three separate power supplies are needed to operate the IC. The core voltage supplying all digital blocks, the analog parts needed for the oscillator and supply observation as well as the preamplifiers of the output pads and the IO supply which powers the post drivers of the GPIO pads. The third supply is used for the HALIOS® measurement analog part. In the figure above the different power supply regions are depicted.

### **5.2.3 Power Up Sequence Considerations**

During power-up the power-on-reset configures all pads as inputs consequently disabling the output drivers. The IO supply is watched after power up if the core supply is in the specified range and causes a reset if it leaves the allowed region. The core supply is watched via a brown out circuit.

The pads will remain input pads as long as the software does not reconfigure them.

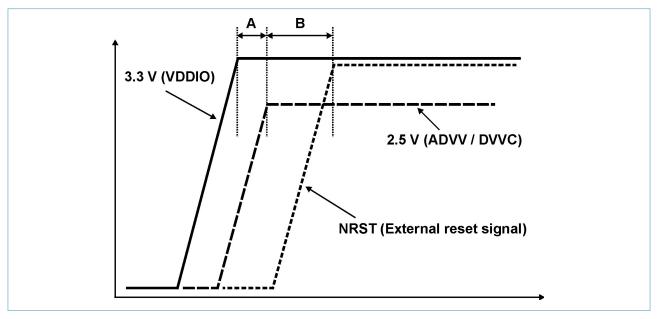

According the following diagram it must be guaranteed that ADVV / DVVC is not switched on before VDDIO. NRST can be switched on if the VDDIO and AVDD/DVVC are stabilized on its potential.

A >= 0ms

B > 5ms (recommended)

To avoid floating gates, A < 100 $\mu$ s is recommended.

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Figure 3. Power Up Sequence: A >= 0 ms; B > 5 ms

## **5.2.4 Power Down Sequence Considerations**

During power down the chip will enter the reset state as soon as the core or IO supply leaves the specified region bringing all pads into input configuration again.

Note: It has to be assured that VDDIO – VDDC > -0.3V at any time during power up and power down.

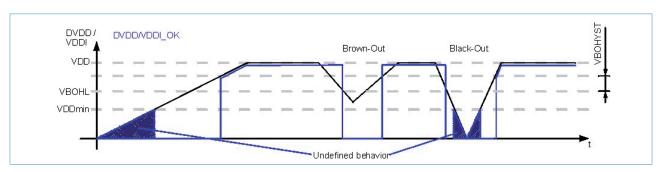

#### 5.3 Brown Out Detection

## 5.3.1 Timing Diagram

Figure 4. Brown-Out timing diagram

## 5.3.2 Functional Description

The brown out detection of the chip will cause a reset whenever the core or IO power supply falls below the specified region. An over-voltage protection is not implemented. The circuit will not be operational when the core supply is below VDDmin. In these cases the power-on-reset will take care of proper reset generation.

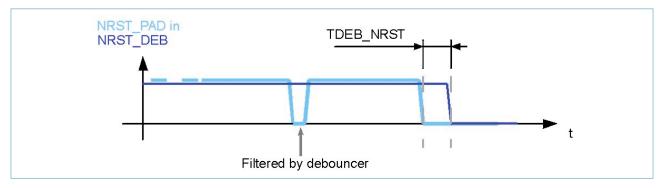

#### 5.4 Reset Generation

## 5.4.1 Reset Generation (RESGEN)

The IC is equipped with a reset input pin which can be used to reset the chip. Any low pulse longer than T<sub>DEBNRST</sub> on the external reset line will be sensed and causes an IC reset.

The IC contains different dynamic and static reset sources. The static sources trigger the master reset as long as the cause for the reset persists. The dynamic sources trigger the reset for a defined minimum reset time. After that time has expired the system reset is released. In case the dynamic source is still signaling a reset the reset is re-triggered.

#### Static reset sources:

- A power up sequence of the core voltage (power on reset)

- Brown out of the core voltage

#### **Dynamic reset sources:**

- Uncorrectable FLASH CRC error

- SRAM parity error

- CPU register parity error

- Watchdog timeout

- Uncorrectable trim register ECC error

Figure 5. Timing of the external reset signal

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

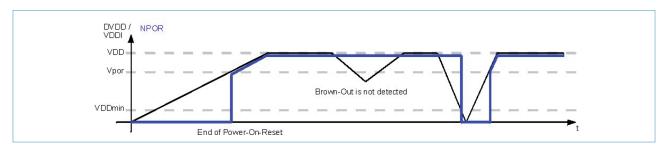

#### 5.4.2 Power-On-Reset

### 5.4.2.1 Timing Diagram

Figure 6. Power-On-Reset timing digram

## 5.4.2.2 Functional Description

The power on reset is designed to cause a reset during the power on cycle of the chip. The reset will be deactivated when the supply crosses  $V_{POR}$ .

After the power up sequence the power on reset block will only cause a new reset if the power supply voltage drops below VDDmin and the rise and fall times of the supply are below the specified values.

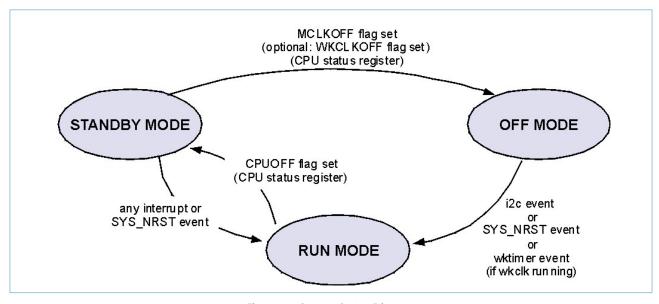

### 5.5 System States

| system state | EL16   | SPI, watchdog,<br>timer1, GPIO | wakeup timer |    | current consup-<br>tion |

|--------------|--------|--------------------------------|--------------|----|-------------------------|

| RUN          | ON     | ON                             | ON           | ON | IRUN                    |

| STANDBY      | halted | ON                             | ON           | ON | ISTANDBY                |

| OFF          | halted | halted                         | halted       | ON | IOFF                    |

Figure 7. System States Diagram

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

#### 1. RUN state:

- master clock = FSYS

- wakeup clock = FWK

- standby state by setting CPUOFF flag (CPU status register) -> entering STANDBY state

- off state by setting CPUOFF flag and MCLKOFF flag (CPU status register) -> entering OFF state

- note: after setting the MCLKOFF and/or CPUOFF bit in the CPU status register the following instruction will be

executed, the next will be fetched, then standby or off mode will be entered. Therefore it is recommended to

execute two NOP instructions after setting the corresponding bits in the status register. The STANDBY or OFF

state has to be entered in a save state without enabled interrupts.

#### 2. STANDBY state:

- CPU halted (no system bus requests -> standby of FLASH and SRAM)

- master clock = FSYS

- wakeup clock = FWK

- wakeup by any interrupt -> returns to RUN state

- wakeup by SYS NRST event (see Reset Generation Diagram) -> returns to RUN state

#### 3. OFF state:

- master clock = off

- wakeup clock = on / off (defined by application software, CPU status register)

- wakeup by specific (external) signal event (I2C or wakeup timer) -> returns to RUN state

- wakeup by SYS\_NRST event (see Reset Generation Diagram) -> returns to RUN state

## 5.6 System Failsafe Features

| failsafe feature                               | asserts interrupt | asserts reset |

|------------------------------------------------|-------------------|---------------|

| FLASH CRC (bit error corrected)                | X                 |               |

| FLASH CRC (uncorrectable bit error)            |                   | Х             |

| empty (erased) FLASH word read detection       |                   | Χ             |

| FLASH write detection                          | X                 |               |

| RAM byte parity                                |                   | Х             |

| uninitialized RAM word / byte read detection   |                   | Х             |

| CPU register parity                            |                   | Х             |

| CPU undefined opcode detection                 | X                 |               |

| CPU misaligned word access detection           | X                 |               |

| opcode execution memory protection             | X                 |               |

| stack overflow detection                       | X                 |               |

| invalid module register access detection       | X                 |               |

| watchdog time-out                              |                   | Х             |

| watchdog window protection                     | Х                 |               |

| brownout detection (supply voltage monitoring) |                   | Х             |

| system clock monitoring                        |                   | Х             |

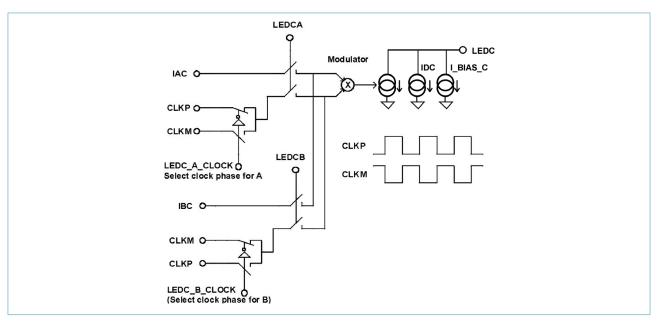

#### 5.7 HALIOS® Interface

## 5.7.1 HALIOS® Block Diagram

Figure 8. HALIOS® Block Diagram

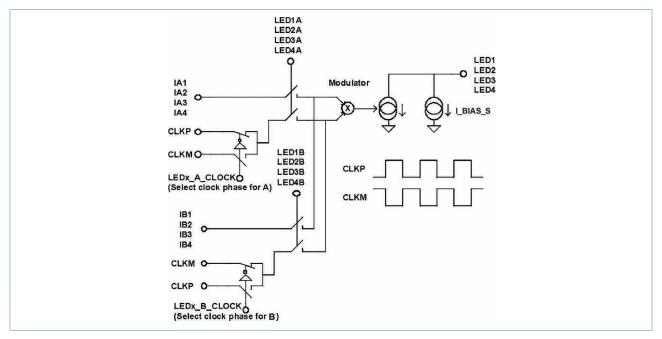

#### 5.7.2 HALIOS® Features

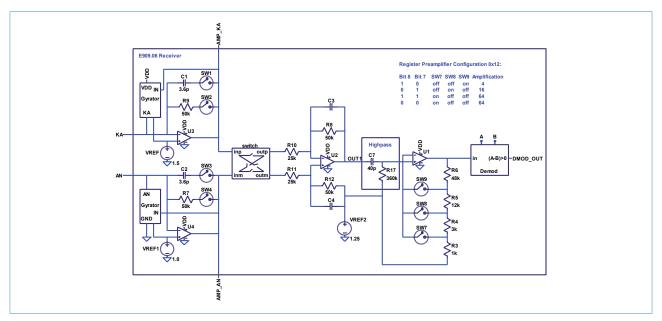

In order to be able to realize optical as well as capacitive sensors the input amplifier can be changed in its characteristic between transimpedance amplifier and charge amplifier. This is achieved by changing the feedback impedance. To have a good immunity to noise the receiving path consists of a symmetrical differential input.

The HALIOS® ASIC contains a configurable current driver interface. In the case of an optical sensor it is possible to drive up to four sending LEDs and one compensation LED. If a capacitive sensor should be realized, the current is converted into a voltage by connecting pullup resistances at the outputs LEDx. The HALIOS® measurement loop is closed by a 10 bit DAC which regulates the output current for the sending/compensation LED. The DAC is controlled by a counter that sets the DAC dependent on the received signal amplitudes up or down.

To follow fast signal changes the counter can be increased or decreased by 1, 2, 4 or 8 steps, this is called the step size that is set due to the number of up/down-counts in the same direction. To start a new measurement the interface is configured with the counter-value and the step size (generally the values from the last measurement), the LED configuration and the current configuration for the LED driver. The measurement regulates the DAC and performs 25 counter steps to follow the actual reflection conditions of the sensor. After one measurement the interface returns the counter-value, the mean-value (it is calculated from the last 16 counter-steps during one measurement) and the stepsize from the last integrator cycle.

After the automated measurement cycle is finished an interrupt appears if the interrupt is enabled. The interrupt is used to wake the system from standby mode.

The HALIOS® clock is adjustable in 5 frequencies (FSYS=8 MHz):

- 167 kHz

- 125 kHz (default)

- 100 kHz

- 83 kHz

- 71 kHz

# 5.7.3 HALIOS® Module Registers

| Register Name                            | Address | Description |

|------------------------------------------|---------|-------------|

| Start Value Counter                      | 0x00    |             |

| Measurement Configuration                | 0x02    |             |

| Measurement Configuration HALIOS® Clock  | 0x04    |             |

| Current Configuration Phase A            | 0x06    |             |

| Current Configuration Phase B            | 0x08    |             |

| Current Configuration Compensator Offset | 0x0A    |             |

| Measurement Result: Counter Value        | 0x0C    |             |

| Measurement Result: Mean Value           | 0x0E    |             |

| Interrupt                                | 0x10    |             |

| Preamplifier Configuration               | 0x12    |             |

| Send Frequency Select                    | 0x14    |             |

### Register Start Value Counter (0x00)

|                 | MSB                                     |     |     |     |   |     |     |     |     |     |     |     |     |     |     | LSB |

|-----------------|-----------------------------------------|-----|-----|-----|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Content         | 15:<br>12                               |     |     |     |   | 10  | 9:0 |     |     |     |     |     |     |     |     |     |

| Reset value     | 0                                       | 0   | 0   | 0   | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Internal access | R/W                                     | R/W | R/W | R/W | R | R/W |

| External access | R/W                                     | R/W | R/W | R/W | R | R/W |

| Bit Description | R/W |     |     |     |   |     |     |     |     |     |     |     |     |     |     |     |

## Register Measurement Configuration (0x02)

|                 | MSB                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                        |                                                                  |                       |                        | LSB  |