SANYO Semiconductors

## DATA SHEET

Monolithic Linear IC

# LA7567BVA — TV and VCR IF Signal Processor (VIF + SIF + SIF converter)

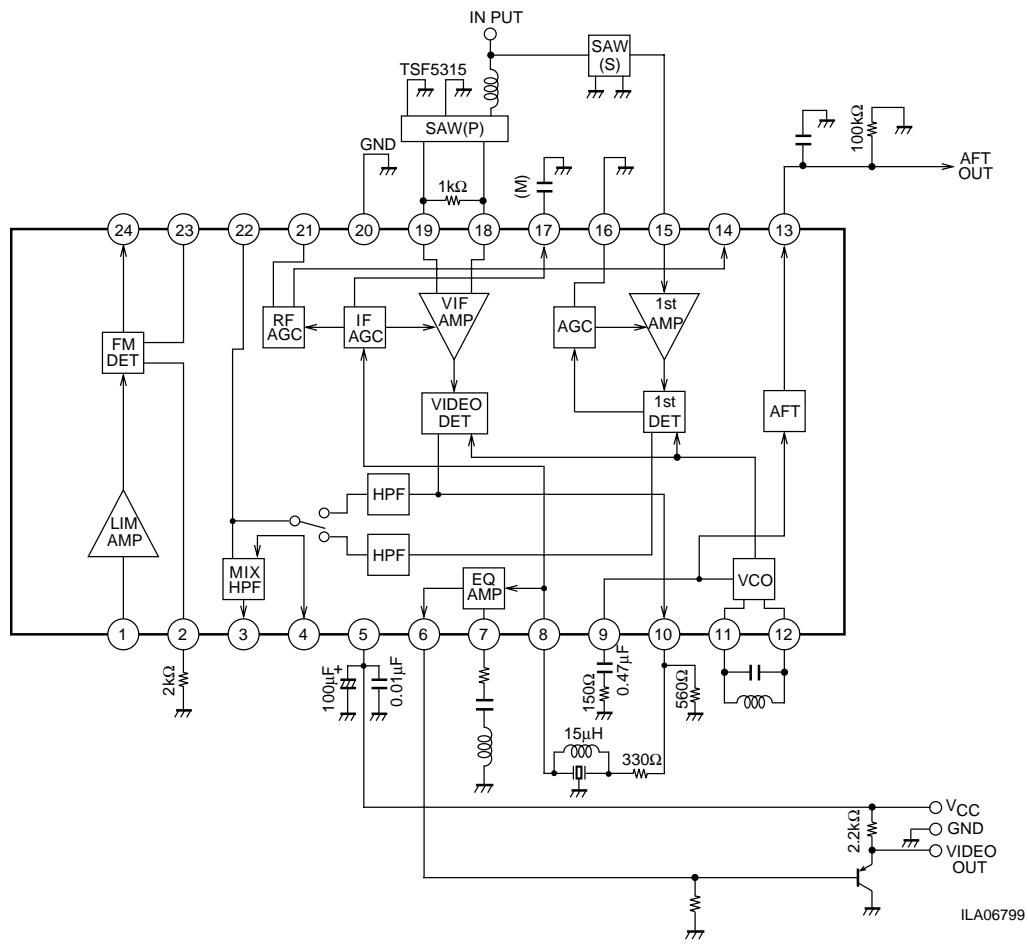

The LA7567BVA is a PAL/NTSC multiformat VIF/SIF IC that adopts a semi-adjustment-free system. The VIF block adopts a system in which VCO adjustment makes AFT adjustment unnecessary to simplify adjustment. The FM detector adopts a PLL detection system that supports multi-detection audio. This IC also integrates an SIF converter, making design of multisystem products easier. The LA7567BVA uses the 5V supply voltage common in multimedia equipment. In addition, the LA7567BVA also includes a buzz canceller that suppresses Nyquist buzzing for superb audio quality.

## Functions

- VIF block: VIF amplifier, buzz canceller, PLL detector, IF AGC, RF AGC, AFT, equalizer amplifier.

- First SIF block: First SIF amplifier, first SIF detector.

- SIF block: Limiter amplifier, PLL FM detector.

## Features

- No AFT or SIF coils are required, making these circuits adjustment free.

- Allows PAL/NTSC multiformat systems to be implemented easily.

- Built-in buzz canceller for excellent audio quality.

- $V_{CC} = 5V$ , low power: 250mW

## Specifications

### Maximum Ratings at $T_a = 25^\circ\text{C}$

| Parameter                   | Symbol           | Conditions                                             | Rated value | Unit |

|-----------------------------|------------------|--------------------------------------------------------|-------------|------|

| Maximum supply voltage      | $V_{CC}$ max     |                                                        | 6           | V    |

| Circuit voltage             | $V_{13}, V_{17}$ |                                                        | $V_{CC}$    | V    |

| Circuit current             | $I_6$            |                                                        | -3          |      |

| Allowable power dissipation | $I_{10}$         |                                                        | -10         | mA   |

|                             | $I_{24}$         |                                                        | -2          |      |

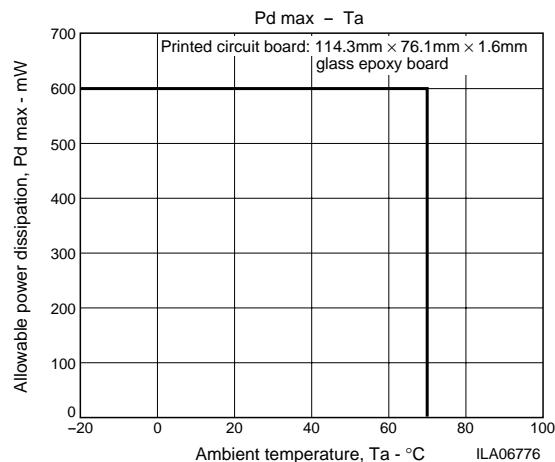

|                             | $P_d$ max        | $T_a = \leq 70^\circ\text{C}$ , when mounted on a PCB* | 600         | mW   |

| Operating temperature       | $T_{opr}$        |                                                        | -20 to +70  | °C   |

| Storage temperature         | $T_{stg}$        |                                                        | -55 to +150 | °C   |

\*: Printed circuit board: 114.3mm × 76.1mm × 1.6mm, glass epoxy board.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

**SANYO Electric Co.,Ltd. Semiconductor Company**

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

# LA7567BVA

## Recommended Operating Conditions at $T_a = 25^\circ\text{C}$

| Parameter                  | Symbol       | Conditions | Rated value | Unit |

|----------------------------|--------------|------------|-------------|------|

| Recommended supply voltage | $V_{CC}$     |            | 5           | V    |

| Operating supply voltage   | $V_{CC\ op}$ |            | 4.5 to 5.5  | V    |

## Electrical Characteristics at $T_a = 25^\circ\text{C}$ , $V_{CC} = 5\text{V}$ , $f_p = 38.9\text{MHz}$

| Parameter                        | Symbol                 | Conditions                | Ratings        |          |      | Unit                   |

|----------------------------------|------------------------|---------------------------|----------------|----------|------|------------------------|

|                                  |                        |                           | min            | typ      | max  |                        |

| <b>[VIF Block]</b>               |                        |                           |                |          |      |                        |

| Circuit current                  | $I_5$                  |                           | 40.8           | 48       | 55.2 | mA                     |

| Maximum RF AGC voltage           | $V_{14H}$              |                           | $V_{CC} - 0.5$ | $V_{CC}$ |      | V                      |

| Minimum RF AGC voltage           | $V_{14L}$              |                           | 0              | 0.5      |      | V                      |

| Input sensitivity                | $V_I$                  | $S_1 = \text{OFF}$        | 27             | 33       | 39   | $\text{dB}\mu\text{V}$ |

| AGC range                        | $G_R$                  |                           | 58             | 63       |      | dB                     |

| Maximum allowable input          | $V_I\ \text{max}$      |                           | 95             | 100      |      | $\text{dB}\mu\text{V}$ |

| No signal voltage output voltage | $V_6$                  |                           | 2.7            | 3.0      | 3.3  | V                      |

| Sync. signal tip voltage         | $V_{6\text{tip}}$      |                           | 0.4            | 0.7      | 1.0  | V                      |

| Video output level               | $V_O$                  |                           | 1.7            | 2        | 2.3  | $\text{Vp-p}$          |

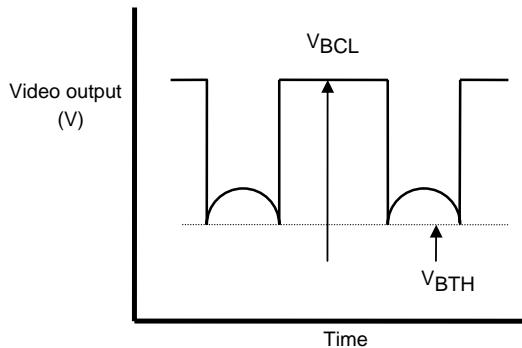

| Black noise threshold voltage    | $V_{BTH}$              |                           | 0.5            | 0.8      | 1.1  | V                      |

| Black noise clamp voltage        | $V_{BCL}$              |                           | 1.6            | 1.9      | 2.2  | V                      |

| Video SNR                        | S/N                    |                           | 48             | 52       |      | dB                     |

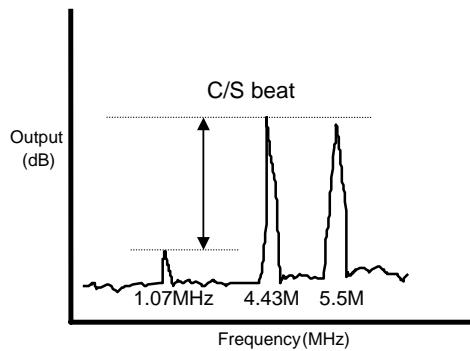

| C-S beating                      | $I_{C-S}$              |                           | 38             | 43       |      | dB                     |

| Frequency characteristics        | $f_c$                  | 6MHz                      | -3             | -1.5     |      | dB                     |

| Differential gain                | $D_G$                  |                           | 3              | 6.5      |      | %                      |

| Differential phase               | $D_P$                  |                           | 3              | 5        |      | $^\circ\text{C}$       |

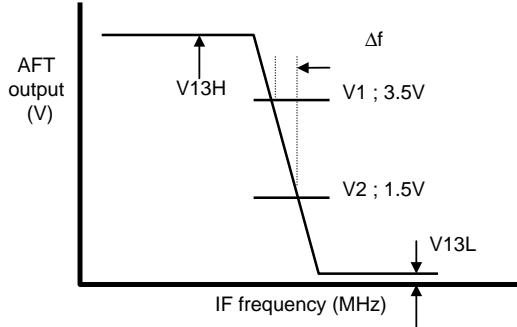

| No signal AFT voltage            | $V_{13}$               |                           | 2.0            | 2.5      | 3.0  | V                      |

| Maximum AFT voltage              | $V_{13H}$              |                           | 4.0            | 4.4      | 5.0  | V                      |

| Minimum AFT voltage              | $V_{13L}$              |                           | 0.18           | 1.0      |      | V                      |

| AFT detection sensitivity        | $S_f$                  |                           | 17             | 25       | 34   | $\text{mV/kHz}$        |

| VIF input resistance             | $R_i$                  | 38.9MHz                   |                | 1.5      |      | $\text{k}\Omega$       |

| VIF input capacitance            | $C_i$                  | 38.9MHz                   |                | 3        |      | pF                     |

| APC pull-in range (U)            | $f_{pu}$               |                           | 0.7            | 1.5      |      | MHz                    |

| APC pull-in range (L)            | $f_{pl}$               |                           |                | -1.5     | -0.9 | MHz                    |

| AFT tolerance frequency          | $f_{fa1}$              |                           | -250           | 0        | +200 | kHz                    |

| VCO 1 maximum variability (U)    | $d_{fu}$               |                           | 1.0            | 1.5      |      | MHz                    |

| VCO 1 maximum variability (L)    | $d_{fl}$               |                           |                | -1.5     | -1   | MHz                    |

| VCO control sensitivity          | B                      |                           | 1.6            | 3.2      | 6.4  | $\text{kHz/mV}$        |

| Synchronization ratio            | $V_S$                  |                           | 25.0           | 28.5     | 31.5 | %                      |

| <b>[First SIF Block]</b>         |                        |                           |                |          |      |                        |

| Conversion gain                  | $V_G$                  |                           | 22             | 28       | 32   | dB                     |

| 5.5MHz output level              | $S_O$                  |                           | 32             | 70       | 110  | $\text{mVrms}$         |

| First SIF maximum input          | $S_i\ \text{max}$      |                           | 50             | 100      |      | $\text{mVrms}$         |

| First SIF input resistance       | $R_i\ (\text{SIF})$    | 33.4MHz                   |                | 2        |      | $\text{k}\Omega$       |

| First SIF input capacitance      | $C_i\ (\text{SIF})$    | 33.4MHz                   |                | 3        |      | pF                     |

| <b>[SIF Block]</b>               |                        |                           |                |          |      |                        |

| Limiting sensitivity             | $V_{lj}\ (\text{lim})$ |                           | 42             | 48       | 54   | $\text{dB}\mu\text{V}$ |

| FM detector output voltage*      | $V_O\ (\text{FM})$     | 5.5MHz $\pm 30\text{kHz}$ | 470            | 600      | 760  | $\text{mVrms}$         |

| AMR                              | AMR                    |                           | 50             | 60       |      | dB                     |

| Total harmonic distortion        | THD                    |                           |                | 0.3      | 0.8  | %                      |

| SIF S/N                          | S/N (FM)               |                           | 57             | 62       |      | dB                     |

| <b>[SIF Converter]</b>           |                        |                           |                |          |      |                        |

| Conversion gain                  | $V_G\ (\text{SIF})$    |                           | 8              | 11       | 14   | dB                     |

| Maximum output level             | $V_{\text{max}}$       |                           | 103            | 109      | 115  | $\text{dB}\mu\text{V}$ |

| Carrier suppression ratio        | $V_{GR}\ (5.5)$        |                           | 15             | 21       |      | dB                     |

| Oscillator level                 | $V_{OSC}$              |                           | 35             | 70       |      | $\text{mVp-p}$         |

| Oscillator leakage               | $OSC_{\text{leak}}$    |                           | 14             | 25       |      | dB                     |

| Oscillator stop current          | $I_4$                  |                           |                |          | 300  | $\mu\text{A}$          |

\*: To acquire the maximum dynamic range from the FM detector, insert a resistor and capacitor in series between pin 23 and ground to adjust the level.

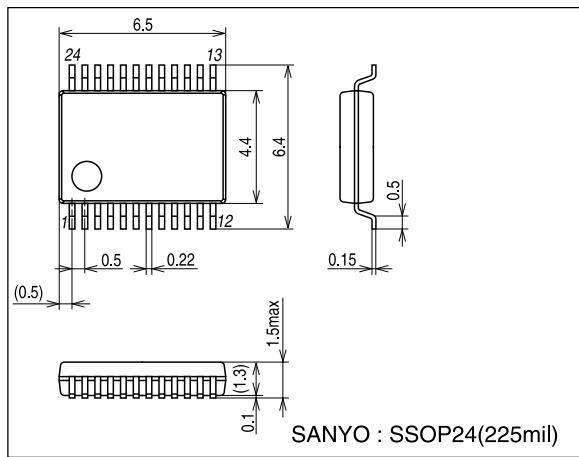

## Package Dimensions

unit : mm

3287

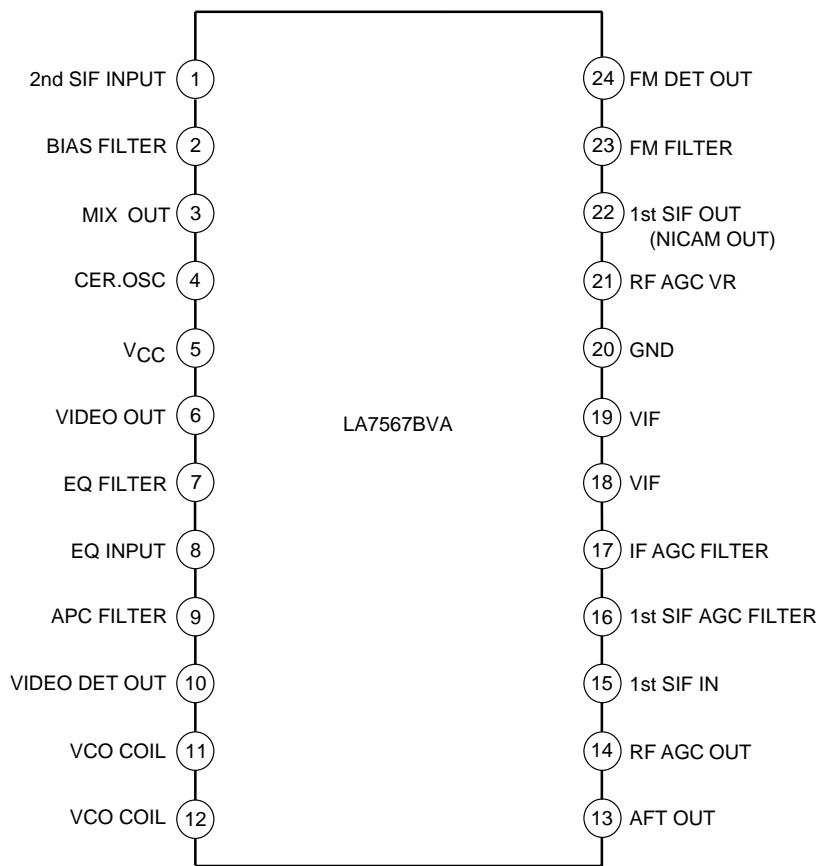

## Pin Assignment

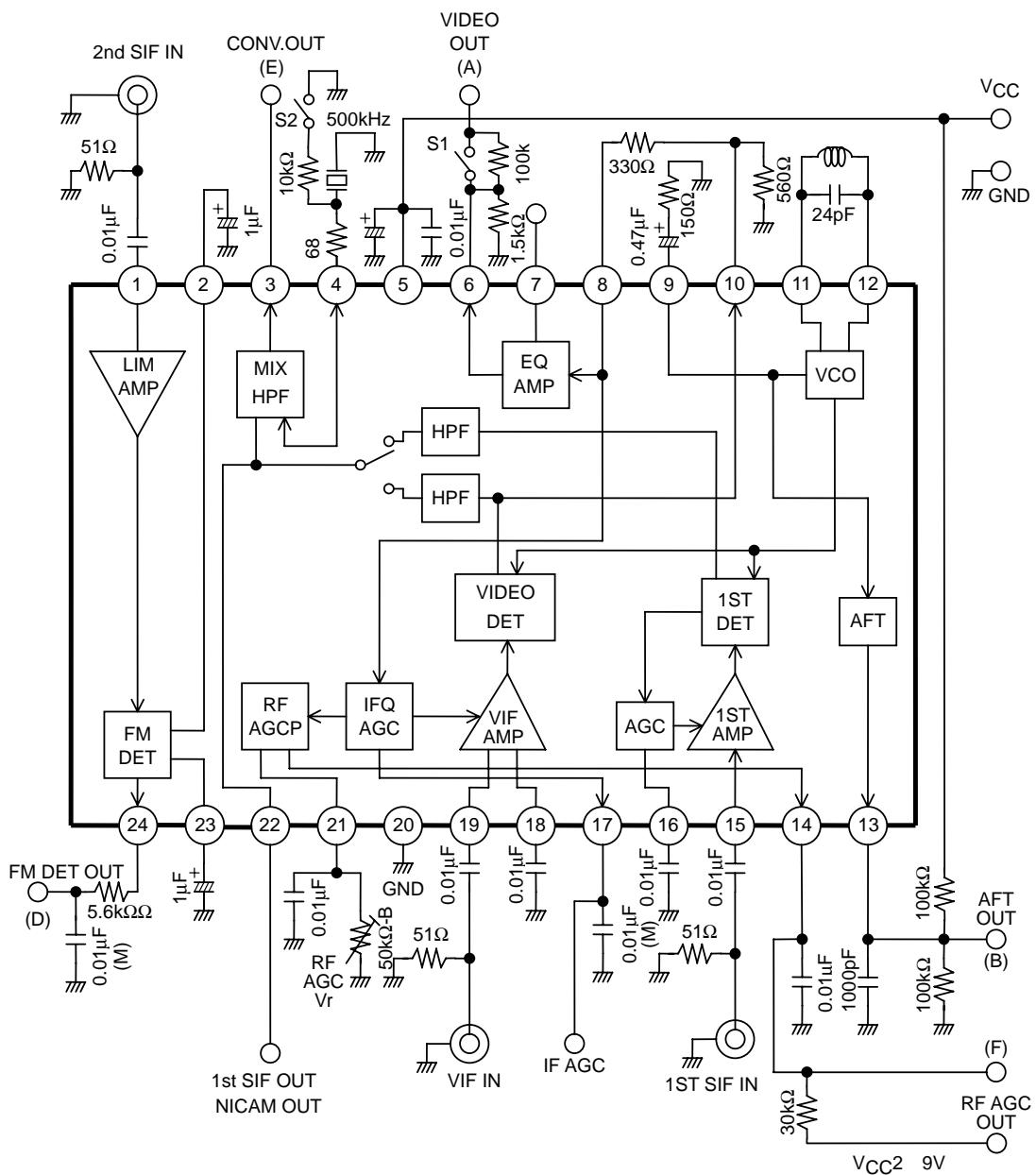

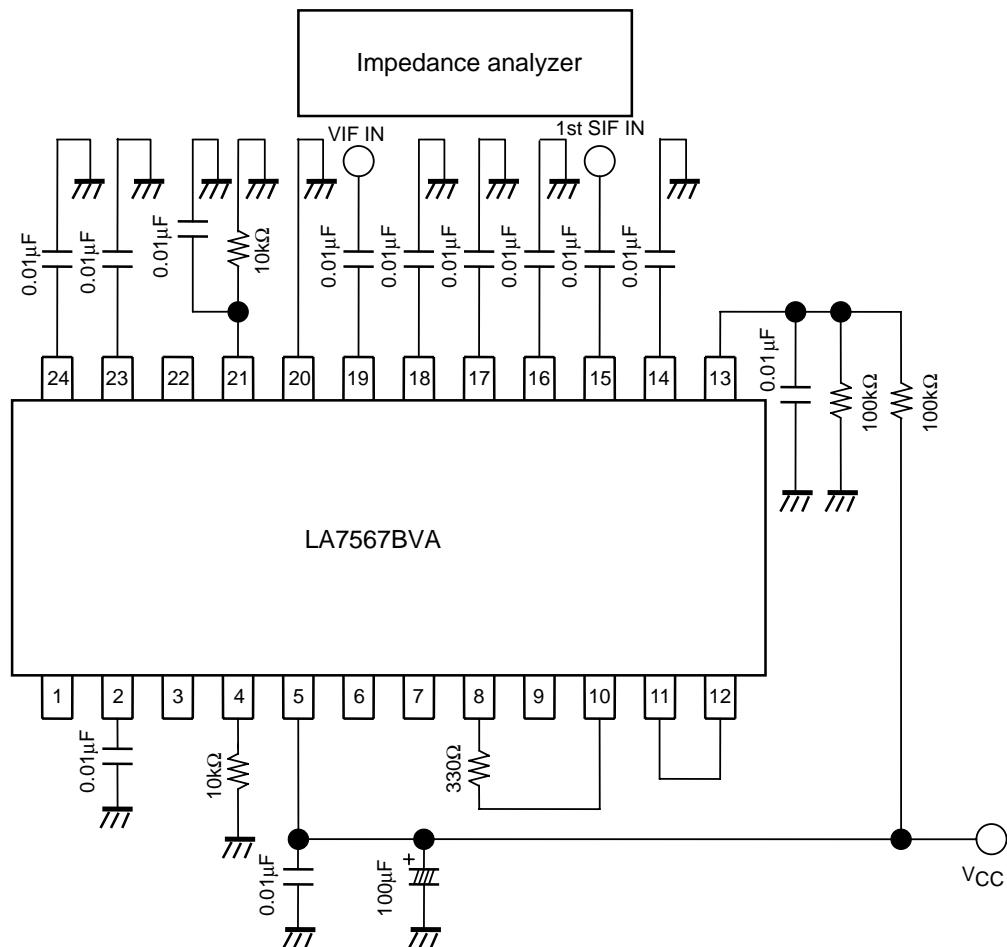

## AC Characteristics Test Circuit

## Test Circuits

Input Impedance Test Circuit (VIF and first SIF input impedance)

**Test Conditions****V1. Circuit current . . . . . [I<sub>5</sub>]**

- (1) Internal AGC

- (2) Input a 38.9MHz 10mVrms continuous wave to the VIF input pin.

- (3) RF AGC V<sub>r</sub> MAX

- (4) Connect an ammeter to the V<sub>CC</sub> and measure the incoming current.

**V2.V3. Maximum RF AGC voltage, Minimum RF AGC voltage . . . . . [V<sub>14H</sub>, V<sub>14L</sub>]**

- (1) Internal AGC

- (2) Input a 38.9MHz 10mVrms continuous wave to the VIF input pin.

- (3) Adjust the RF AGC V<sub>r</sub> (resistor value max.) and measure the maximum RF AGC voltage. (F)

- (4) Adjust the RF AGC V<sub>r</sub> (resistor value min.) and measure the minimum RF AGC voltage. (F)

**V4. Input sensitivity . . . . . [V<sub>I</sub>]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz 400Hz 40% AM (VIF input)

- (3) Turn off the S1 and put 100kΩ through.

- (4) VIF input level at which the 400Hz detection output level at test point A becomes 0.64Vp-p.

**V5. AGC range . . . . . [G<sub>R</sub>]**

- (1) Apply the V<sub>CC</sub> voltage to the external AGC IF AGC (pin 17).

- (2) In the same manner as for the V4 (input sensitivity), measure the VIF input level at which the detection output level becomes 0.64Vp-p . . . . . V<sub>i1</sub>.

- (3)

$$G_R = 20 \log \frac{V_{i1}}{V_i} \text{ dB}$$

**V6. Maximum allowable input . . . . . [V<sub>I</sub> max]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz 15 kHz 78% AM (VIF input)

- (3) VIF input level at which the detection output level at test point A is video output (V<sub>o</sub>) ±1dB

**V7. No-signal video output voltage . . . . . [V<sub>6</sub>]**

- (1) Apply the V<sub>CC</sub> voltage to the external AGC, IF AGC (pin 17).

- (2) Measure the DC voltage of VIDEO output (A).

**V8. Sync. signal tip voltage . . . . . [V<sub>6tip</sub>]**

- (1) Internal AGC

- (2) Input a 38.9MHz 10mVrms continuous wave to the VIF input pin.

- (3) Measure the DC voltage of VIDEO output (A).

**V9. Video output level . . . . . [V<sub>o</sub>]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz 15kHz 78% AM V<sub>i</sub> = 10mVrms (VIF input)

- (3) Measure the peak value of the detection output level at test point A. . . . . V<sub>p-p</sub>

**V10.V11. Black noise threshold level and clamp voltage . . . . . [V<sub>BTH</sub>, V<sub>BCL</sub>]**

- (1) Apply DC voltage to the external AGC, IF AGC (pin 17) and adjust the voltage.

- (2)  $f_p = 38.9\text{MHz}$  400Hz 40% AM10mVrms (VIF input)

- (3) Adjust the IF AGC (pin 17) voltage to operate the noise canceller.

Measure the  $V_{BTH}$ ,  $V_{BCL}$  at test point A.

**V12. Video S/N . . . . . [S/N]**

- (1) Internal AGC

- (2)  $f_p = 38.9\text{MHz}$  CW = 10mVrms (VIF input)

- (3) Measure the noise voltage at test point A in RMS volts through a 10kHz to 4MHz band-pass filter.

.....Noise voltage (N)

$$(4) \text{S/N} = 20 \log \frac{\text{Video portion (Vp-p)}}{\text{Noise voltage (Vrms)}} = 20 \log \frac{1.12\text{Vp-p}}{\text{Noise voltage (Vrms)}} \text{ (dB)}$$

**V13. C/S beat . . . . . [ICS]**

- (1) Apply DC voltage to the external AGC IF AGC (pin 17) and adjust the voltage.

- (2)  $f_p = 38.9\text{MHz}$  CW; 10mVrms

$f_c = 34.47\text{MHz}$  CW; 10mVrms-10dB

$f_s = 33.4\text{MHz}$  CW; 10mVrms-10dB

- (3) Adjust the IF AGC (pin 17) voltage so that the output level at test point A becomes 1.3Vp-p.

- (4) Measure the difference between the levels at 4.43MHz and 1.07MHz.

**V14. Frequency characteristics . . . . . [f<sub>c</sub>]**

- (1) Apply DC voltage to the external AGC IF AGC (pin 17) and adjust the voltage.

- (2) SG1 : 38.9MHz continuous wave 10mVrms

SG2 : 38.8MHz to 32.9MHz continuous wave 2mVrms

Add the SG1 and SG2 signals using a T pat and adjust each SG signal level so that the above-mentioned levels are reached and input the added signals to the VIF IN.

- (3) First set the SG2 frequency to 38.8MHz, and then adjust the IF AGC voltage (V17) so that the output level at test point A becomes 0.5Vp-p..... V1

- (4) Set the SG2 frequency to 32.9MHz and measure the output level.....V2

- (5) Calculate as follows:

$$f_c = 20 \log \frac{V2}{V1} \text{ (dB)}$$

**V15.V16. Differential gain, differential phase . . . [DG, DP]**

- (1) Internal AGC

- (2)  $f_p = 38.9\text{MHz}$  ALP 50% 87.5% modulation video signal  $V_i = 10\text{mVrms}$

- (3) Measure the DG and DP at test point A

**V17. No signal AFT voltage. . . . . [V13]**

- (1) Internal AGC

- (2) Measure the DC voltage at the AFT output (B).

**V18.V19.V20. Maximum minimum AFT output voltage, AFT detection sensitivity . . . [V13H, V13L, S<sub>f</sub>]**

- (1) Internal AGC

- (2)  $f_p = 38.9\text{MHz} \pm 1.5\text{MHz}$  Sweep = 10mVrms (VIF input)

- (3) Maximum voltage: V13H, minimum voltage: V13L

- (4) Measure the frequency deviation at which the voltage at test point B changes from V1 to V2.

..... $\Delta f$

$$S_f = \frac{2000(\text{mV})}{\Delta f(\text{kHz})} \text{ mV/kHz}$$

**V21.V22. VIF input resistance, Input capacitance . . . . . [R<sub>i</sub>, C<sub>i</sub>]**

- (1) Referring to the input impedance Test Circuit, measure  $R_i$  and  $C_i$  with an impedance analyzer.

**V23.V24. APC pull-in range . . . . . [f<sub>pu</sub>, f<sub>pl</sub>]**

- (1) Internal AGC

- (2)  $f_p = 33\text{MHz}$  to 44MHz continuous wave; 10mVrms

- (3) Adjust the SG signal frequency to be higher than  $f_p = 38.9\text{MHz}$  to bring the PLL to unlocked state.

Note: GThe PLL is assumed to be in unlocked state when a beat signal appears at test point A.

- (4) When the SG signal frequency is lowered, the PLL is brought to locked state again. ....(f1)

- (5) Lower the SG signal frequency to bring the PLL to unlocked state.

- (6) When the SG signal frequency is raised, the PLL is brought to locked state again. ....(f2)

- (7) Calculate as follows:

$f_{pu} = f_1 - 38.9\text{MHz}$

$f_{pl} = f_2 - 38.9\text{MHz}$

**V25. AFT tolerance frequency . . . . . [ΔF<sub>a1</sub>]**

- (1) Internal AGC

- (2) SG1 : 37.9MHz to 40.9MHz variable continuous wave 10mVrms

- (3) Adjust the SG1 signal frequency so that the AFT output DC voltage (test point B) becomes 2.5V; that SG1 signal frequency is f1.

- (4) External AGC (Adjust the V17.)

- (5) Apply 5V to the IFAGC (pin 17) and then pick up the VCO oscillation frequency from GND, etc. and measure the frequency (f2)

- (6) Calculate as follows:

$\text{AFT tolerance frequency } \Delta F_{a1} = f_2 - f_1(\text{kHz})$

**V26.V27. VCO Maximum variable range(U, L) . . . [d<sub>f</sub>U, d<sub>f</sub>I]**

- (1) Apply the V<sub>CC</sub> voltage to the external AGC, IF AGC (pin 17).

- (2) Pick up the VCO oscillation frequency from the VIDEO output (A), GND, etc. and adjust the VCO coil so that the frequency becomes 38.9MHz.

- (3) f<sub>U</sub> is taken as the frequency when 1V is applied to the APC pin (pin 9). In the same manner, f<sub>I</sub> is taken as the frequency when 5V is applied to the APC pin (pin 9).

$$d_{fU} = f_U - 38.9\text{MHz}$$

$$d_{fI} = f_I - 38.9\text{MHz}$$

**V28. VCO control sensitivity . . . . . [β]**

- (1) Apply the V<sub>CC</sub> voltage to the external AGC, IF AGC (pin 17).

- (2) Pick up the VCO oscillation frequency from the VIDEO output (A), GND, etc. and adjust the VCO coil so that the frequency becomes 38.9MHz.

- (3) f<sub>1</sub> is taken as the frequency when 3.0V applied to the APC pin (pin 9). In the same manner, f<sub>2</sub> is taken as the frequency when 3.4V is applied to the APC pin (pin 9).

$$\beta = \frac{f_2 - f_1}{400} (\text{kHz}/\text{mV})$$

**V29. Synchronization ratio . . . . . [Vs]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz 87.5% 10STEP B/W

V<sub>i</sub> = 10mVrms

- (3) Measure the output amplitude at the measuring point A . . . . . V<sub>video</sub>

- (4) Measure the pedestal voltage (DC) at the measuring point A . . . . . V<sub>ped</sub>

V<sub>S</sub> = (V<sub>ped</sub>-V<sub>6tip</sub>)/V<sub>video</sub> × 100 (%)

**F1. First SIF conversion gain . . . . . [VG]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz CW; 10mV (VIF input)

f<sub>s</sub> = 33.4MHz CW; 500μV (First SIF input) . . . . . V<sub>1</sub>

- (3) Detection output level at test point C (Vrms) . . . . . V<sub>2</sub> (5.5MHz)

- (4) V<sub>G</sub> = 20log  $\frac{V_2}{V_1}$  dB

**F2. 5.5MHz output level . . . . . [S<sub>O</sub>]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz CW; 10mV (VIF input)

f<sub>s</sub> = 33.4MHz CW; 10mV (First SIF input) . . . . . V<sub>1</sub>

- (3) Detection output level at test point C (5.5MHz) . . . . . S<sub>O</sub> (mVrms)

**F3. First SIF maximum input . . . . . [S<sub>i</sub>max]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz CW; 10mV (VIF input)

f<sub>s</sub> = 33.4MHz CW; variable (First SIF input)

- (3) Input level at which the detection output at test point C (5.5MHz) becomes S<sub>O</sub> ± 2dB.....S<sub>i</sub>max

**F4. F5. First SIF input resistance, input capacitance . . . . . [R<sub>i</sub>(SIF1), C<sub>i</sub>(SIF1)]**

- (1) Using an input analyzer, measure R<sub>i</sub> and C<sub>i</sub> in the input impedance measuring circuit.

**S1. SIF limiting sensitivity . . . . . [V<sub>li</sub>(lim)]**

- (1) Apply the V<sub>CC</sub> voltage to the external AGC, IF AGC (pin 17).

- (2) f<sub>s</sub> = 5.5MHz fm = 400Hz ΔF = ±30kHz (SIF input)

- (3) Set the SIF input level to 100mVrms and then measure the level at test point D.....V1

- (4) Lower the SIF input level until V1-3dB occurs. Measure the input level at that moment.

**S2. S4. FM detection output voltage, distortion factor . . . [V<sub>O</sub>(FM, THD)]**

- (1) Apply the V<sub>CC</sub> voltage to the external AGC, IF AGC (pin 17).

- (2) f<sub>s</sub> = 5.5MHz fm = 400Hz AM = 30%

(SIF input V<sub>i</sub> = 100mVrms)

- (3) Assign the level at test point D to the FM detection output voltage and measure the distortion factor.

**S3. AM rejection ratio . . . . . [AMR]**

- (1) Apply the V<sub>CC</sub> voltage to the external AGC, IF AGC (pin 17).

- (2) f<sub>s</sub> = 5.5MHz fm = 400Hz AM = 30%

(SIF input V<sub>i</sub> = 100mVrms)

- (3) Measure the output level at test point D.....V<sub>AM</sub>

- (4)  $AMR = 20\log \frac{V_O(DET)}{V_{AM}} \text{ dB}$

**S5. SIF S/N . . . . . [S/N]**

- (1) External AGC (V17 = V<sub>CC</sub>)

- (2) f<sub>s</sub> = 5.5MHz NO MOD V<sub>i</sub> = 100mVrms

- (3) Measure the output level at test point D.....V<sub>n</sub>

- (4)  $S/N = 20\log \frac{V_O(DET)}{V_n} \text{ dB}$

**C1. Converter conversion gain. . . . . V<sub>G</sub>(SIF)**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz CW; 10mV (VIF input)

f<sub>s</sub> = 33.4MHz CW; 316μV (First SIF input)

- (3) Measure the 6MHz component at test point E (MIX output). .....V1

- (4) Measure the 5.5MHz component at test point F (NICAM output). .....V2

- (5)  $V_G \text{ mix} = 20\log \frac{V_1}{V_2} \text{ dB}$

**C2. SIF converter maximum output level . . . . . [V<sub>max</sub>]**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz CW; 10mV (VIF input)

f<sub>s</sub> = 33.4MHz CW; 10mV (First SIF input)

- (3) Measure the 6MHz component at test point E (MIX output). .....V<sub>max</sub>(dBμV)

**C3. Carrier suppression ratio (V<sub>GR</sub>(5.5))**

- (1) Internal AGC

- (2) f<sub>p</sub> = 38.9MHz CW; 10 mV (VIF input)

f<sub>s</sub> = 33.4MHz CW; 316 μV (First SIF input)

- (3) Measure the 6MHz component at test point E (MIX output). .....V6 (dBμV)

- (4) Measure the 5.5MHz component at test point E (MIX output). .....V5.5 (dBμV)

- (5) Perform the following calculation.

Carrier suppression ratio V<sub>GR</sub>(5.5)(dB) = V6 - V5.5

## C5. OSC leakage (OSC leak)

- (1) Internal AGC

- (2)  $f_p = 38.9\text{MHz}$  CW; 10mV (VIF input)

$f_s = 33.4\text{MHz}$  CW;  $316\mu\text{V}$  (First SIF input)

- (3) Measure the 6MHz component at test point E (MIX output). .... $V_6(\text{dB}\mu\text{V})$

- (4) Measure the 500kHz component at test point E (MIX output). .... $V_{0.5}(\text{dB}\mu\text{V})$

- (5) Perform the following calculation.

Carrier suppression ratio  $\text{OSCleak}(\text{dB}) = V_6 - V_{0.5}$

Note 1) Unless otherwise specified for VIF test, apply the  $V_{CC}$  voltage to the IF AGC and adjust the VCO coil so that oscillation occurs at 38.9MHz.

Note 2) Unless otherwise specified, the SW1 must be ON.

## Application Circuits

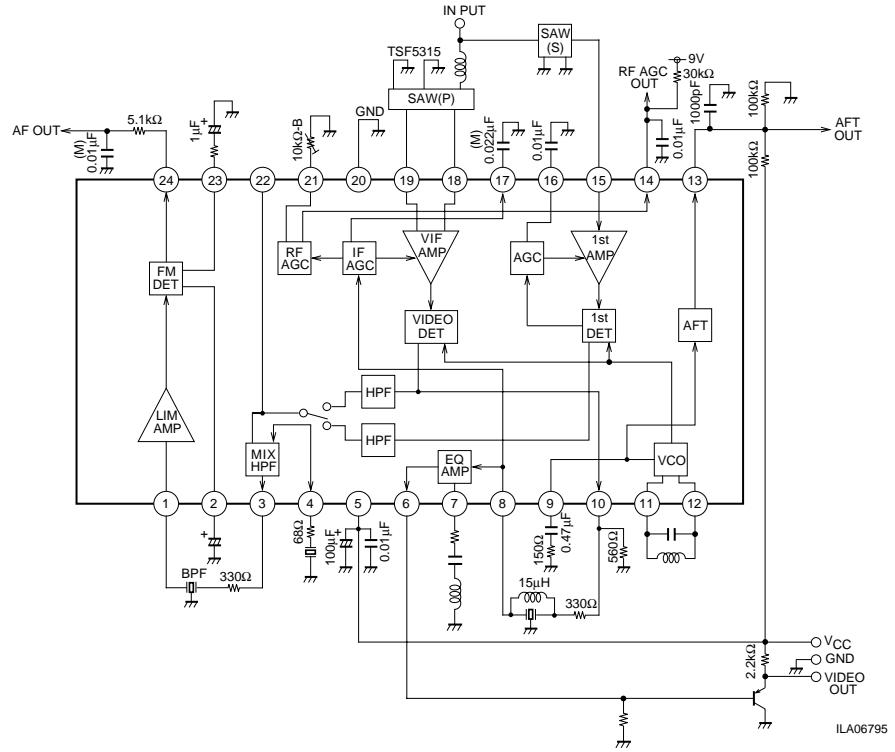

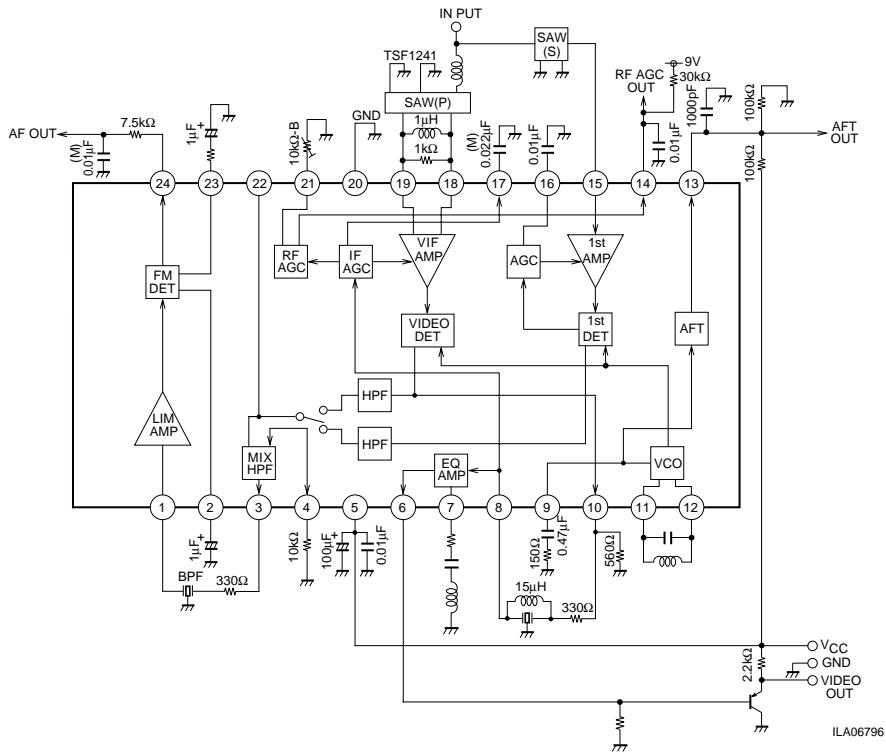

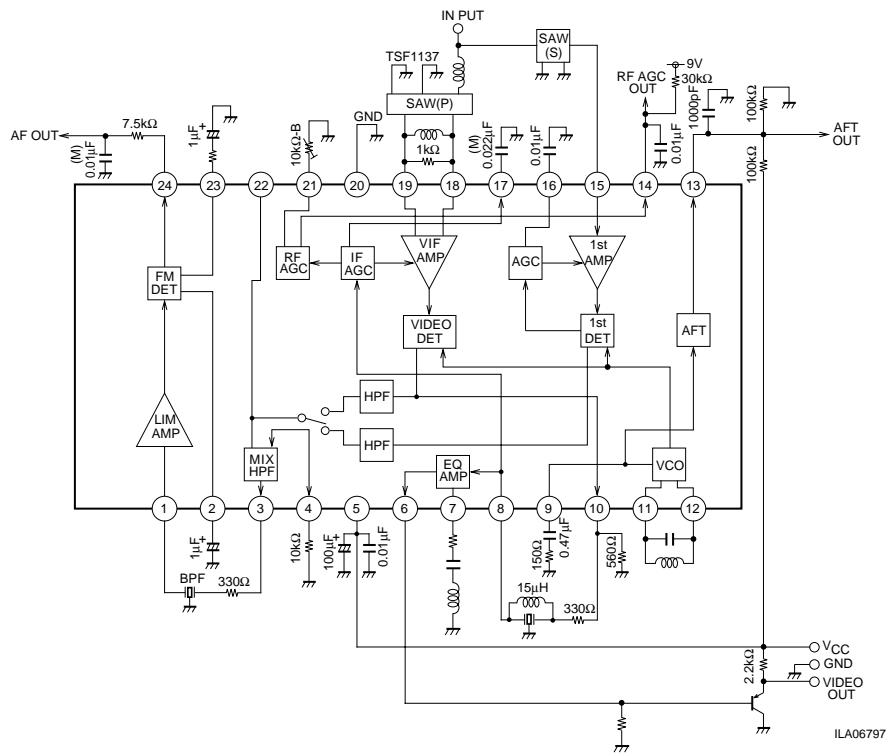

## PAL SPLIT

NT (US) SPLIT

# LA7567BVA

## JAPAN SPLIT

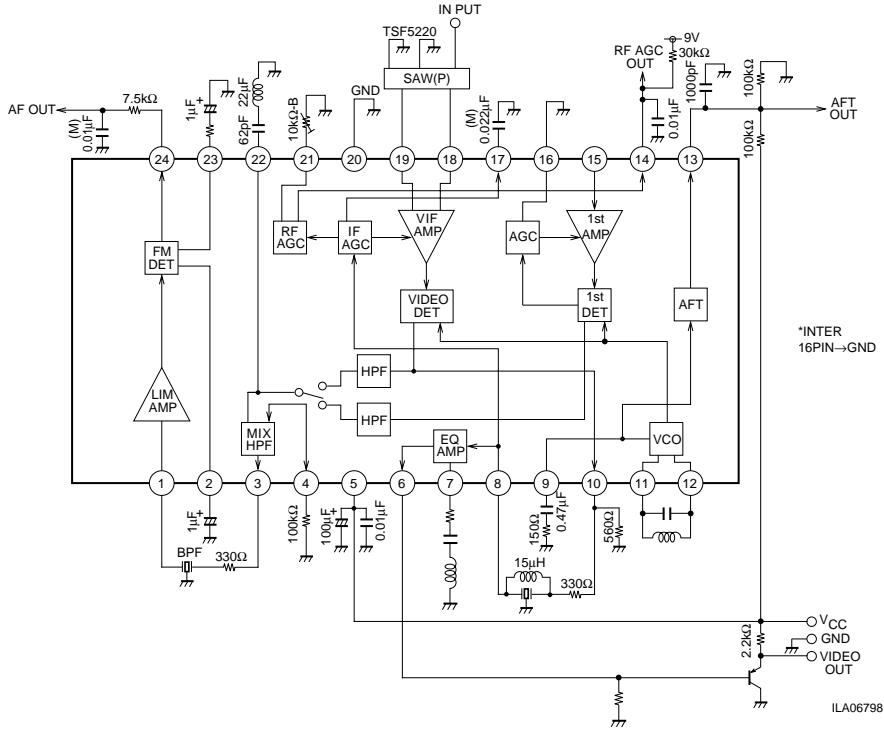

## NT (US) INTER

## Application Circuit Example

When the SIF, first SIF, AFT, and/or RF AGC are not used

(1) When the SIF circuit is not used

Leave pins 1, 23, and 24 open.

Insert a  $2\text{k}\Omega$  resistor between pin 2 and ground.

(2) When the first SIF circuit is not used

Leave pins 3, 4, 22, and 15 open.

Connect pin 16 to ground.

(3) When the AFT circuit is not used

Since there is no way to defeat the AFT circuit, insert a  $100\text{k}\Omega$  resistor and a  $0.01\mu\text{F}$  capacitor in parallel between pin 13 and ground.

(4) When the RF AGC circuit is not used

Leave pins 14 and 21 open.

Insert a  $0.01\mu\text{F}$  capacitor between pin 21 and ground to prevent oscillation.

## Pin Descriptions

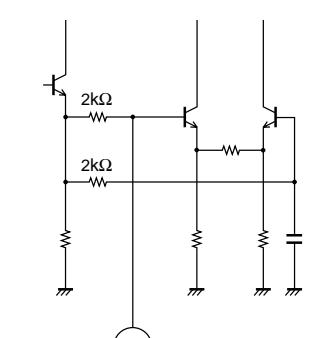

| Pin No. | Pin                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Equivalent circuit                                                                                                                                                                                         |

|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

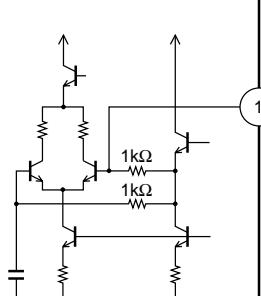

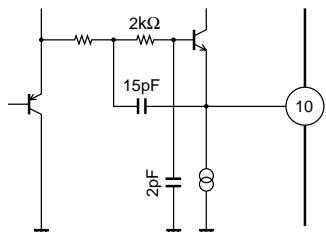

| 1       | SIF INPUT              | <p>The input impedance is about <math>1\text{k}\Omega</math>. If interference* enters at this pin, it can cause buzzing and beating. The PCB pattern layout must be designed to minimize interface at this pin.</p> <p>*: Signals that can cause interface with the audio include video signals and the chroma signal. Signal such as the VIF carrier can also cause interference.</p>                                                                                                                                                                                                                                                            |  <p>ILA06800</p>                                                                                                         |

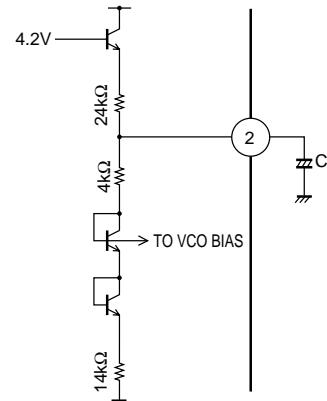

| 2       | FM power supply filter | <p>The FM detector signal-to-noise ratio can be improved by inserting an FM detector bias line filter.</p> <p>If the FM detector with <math>C_1</math> (<math>0.47\mu\text{F}</math> or larger; the recommended value is <math>1\mu\text{F}</math>) is not used, pin 2 must be connected to ground through a <math>2\text{k}\Omega</math> resistor. This stops the FM detector VCO circuit.</p>                                                                                                                                                                                                                                                   |  <p>ILA06801</p>                                                                                                        |

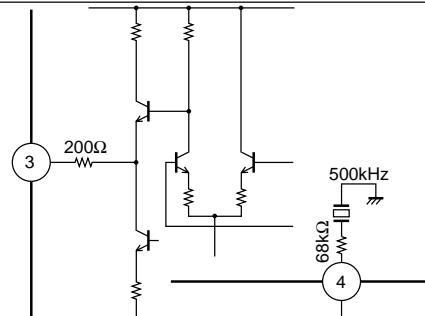

| 3<br>4  | SIF converter          | <p>Pin 3 is the SIF converter output. This signal is passed through a 6MHz bandpass filter and input to the SIF block. This is an emitter-follower output with a <math>200\Omega</math> series resistor inserted in the output.</p> <p>Pin 4 is the SIF converter's 500kHz oscillator connection. Since this oscillator circuit includes an ALC, the oscillator level is low and is controlled to be a fixed level. If this circuit is not used, insert a <math>10\text{k}\Omega</math> resistor between pin 3 and ground. Connecting this external resistor stops the 500kHz oscillator and allows the converter to be used as an amplifier.</p> |  <p>ILA06819</p>  <p>ILA06802</p> |

| 5       | VCC                    | <ul style="list-style-type: none"> <li>The decoupling capacitor between VCC and ground must be connected with the shortest lines possible.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                            |

Continued on next page.

Continued from preceding page.

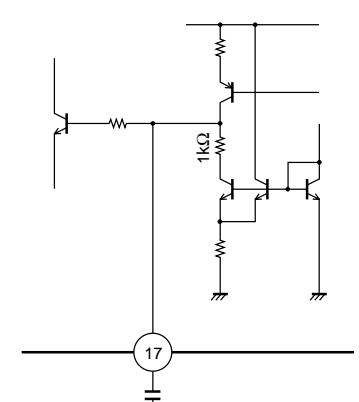

| Pin No.     | Pin        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Equivalent circuit                                                                                                                                                                                     |

|-------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

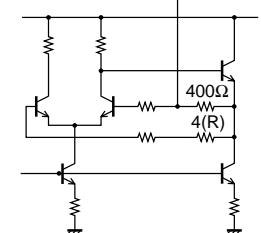

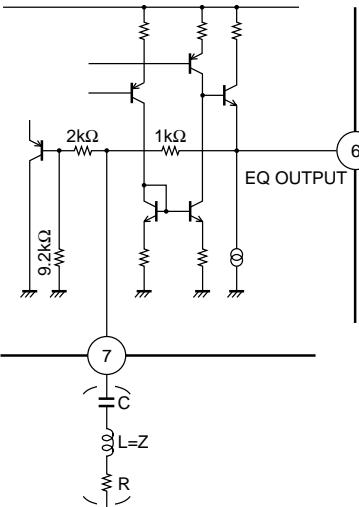

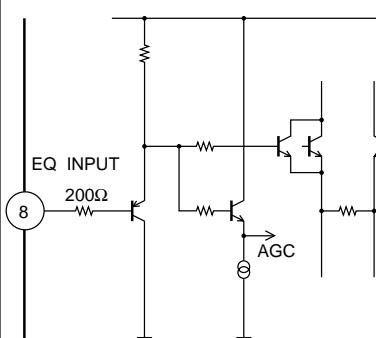

| 6<br>7<br>8 | EQ amp     | <p>Equalizer circuit<br/>This circuit corrects the video signal frequency characteristics.</p> <p>Pin 8 is the equalizer amplifier input.<br/>A 1.5Vp-p signal is input and the equalizer amplifier amplifies it to 2Vp-p.</p> <ul style="list-style-type: none"> <li>• Equalizer amplifier design<br/>The equalizer amplifier is designed as a voltage follower with about 2.3dB of gain. Insert an inductor, a capacitor, and a resistor in series between pin 7 and ground if frequency characteristics correction is required.</li> <li>• Equation amplifier notes<br/>If <math>v_i</math> is the input signal and <math>v_o</math> the output, this amplifier operates as follows.</li> </ul> $\frac{R_1}{Z} + 1 (v_i + v_{in}) = v_o \times G$ <p>G: Voltage follower amplifier gain<br/>vin: Imaginary short<br/>G: About 2.3dB<br/>Assuming <math>v_{in}</math> is close to 0:</p> $AV = \frac{v_o G}{v_i} = \frac{R_1}{Z} + 1$ <p>R1 is an IC internal resistor, and is 1kΩ. Z may be chosen to match the desired characteristics. However, since the equalizer amplifier gain is at its maximum at Z's resonance point, care is required to assure that distortion does not occur.</p> |  <p>ILA06803</p>  <p>ILA06804</p> |

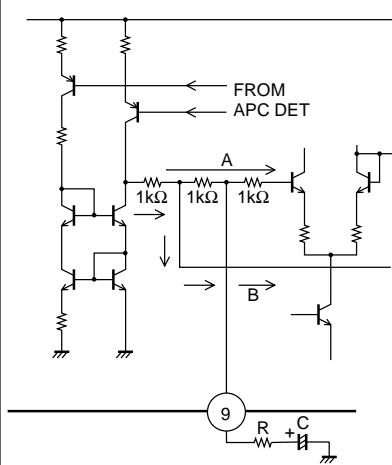

| 9           | APC FILTER | <p>PLL detector APC filter connection<br/>The APC time constant is switched internally in the IC. When locked, the VCO is controlled by the route A and the loop gain is lowered.</p> <p>When unlocked and during weak field reception, the VCO is controlled by the route B and the loop gain is increased.</p> <p><math>R = 150</math> to <math>390\Omega</math><br/><math>0.47\mu F</math> is the recommended value for C.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  <p>ILA06805</p>                                                                                                   |

Continued on next page.

# LA7567BVA

Continued from preceding page.

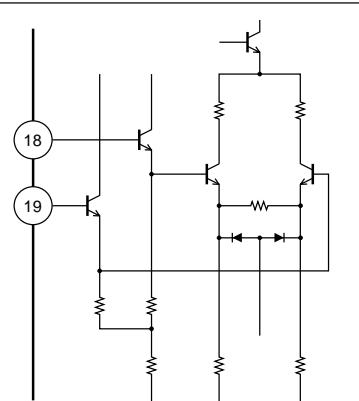

| Pin No.  | Pin                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Equivalent circuit                                                                                   |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 10       | Composite video output | Video output (including the SIF carrier) pin. A resistor must be inserted between pin 10 and ground to acquire the pin circuit's drive capability.<br>$R \geq 300\Omega$                                                                                                                                                                                                                                                                                             |  <p>ILA06806</p>   |

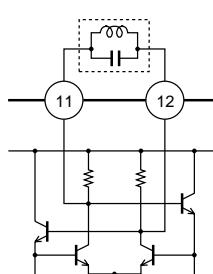

| 11<br>12 | VCO tank               | Video detector VCO tank circuit connection. See the coil specifications provided separately for details on this tank circuit. This is a vector synthesis VCO circuit.                                                                                                                                                                                                                                                                                                |  <p>ILA06807</p>  |

| 13       | AFT OUTPUT             | AFT output<br>The AFT center voltage is created by an external bleeder resistor. The AFT gain is increased by increasing the value of this external bleeder resistor.<br>The resistor value must be limited to be no more than $390\Omega$ .<br>This IC includes a function that controls the AFT voltage to naturally go to the center voltage during weak field reception.                                                                                         |  <p>ILA06808</p>  |

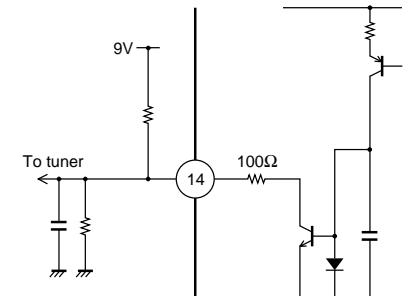

| 14       | RF AGC OUTPUT          | RF AGC output<br>This output controls the tuner RF AGC. A $100\Omega$ protective resistor is inserted in series with this open collector output. Determine the value of the external bleeder resistor by referring to the tuner specifications.                                                                                                                                                                                                                      |  <p>ILA06809</p> |

| 15       | 1st SIF INPUT          | First SIF input<br>A capacitor must be used to cut the DC component of the input to this input circuit. <ul style="list-style-type: none"><li>When a SAW filter is used:<br/>The first SIF sensitivity can also be increased by inserting an inductor between the SAW filter and the IC to neutralize the SAW filter output capacitance and the IC input capacitance.</li><li>If this IC is used with an intercarrier, this pin (pin 15) may be left open.</li></ul> |  <p>ILA06810</p> |

Continued on next page.

# LA7567BVA

Continued from preceding page.

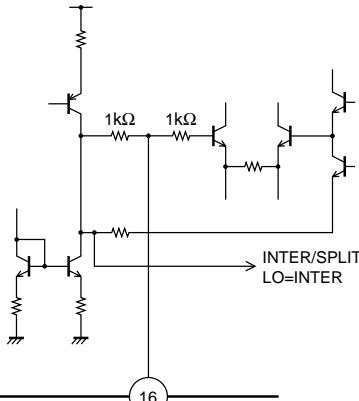

| Pin No.  | Pin                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Equivalent circuit                                                                                   |

|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

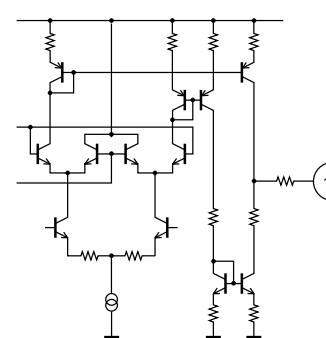

| 16       | 1st SIF AGC FILTER | <p>First SIF AGC filter connection</p> <p>This IC adopts an average value AGC system. The first SIF conversion gain is about 30dB and the AGC range is over 50 dB. Normally, a 0.01<math>\mu</math>F capacitor should be used for the filter at this pin.</p> <ul style="list-style-type: none"> <li>If an intercarrier is used, connect this pin to ground. An IC internal switch will be set so that the intercarrier output becomes the SIF converter input.</li> </ul> |  <p>ILA06811</p>   |

| 17       | IF AGC FILTER      | <p>IF AGC filter connection</p> <p>The signal which is peak detected by the internal AGC detector is converted to the AGC voltage at pin 17. Furthermore, this IC includes a second AGC filter (lag-lead filter) used to create the dual time constants internally in the IC.</p> <p>Use a 0.022<math>\mu</math>F capacitor as this external capacitor. However, this capacitor value must be adjusted according to the sag, AGC peak, and other characteristics.</p>      |  <p>ILA06812</p>  |

| 18<br>19 | VIF input          | <p>VIF amplifier input</p> <p>This input circuit is a balanced input and the input impedance corresponds to the following values.</p> <p><math>R = 1.5k\Omega</math></p> <p><math>C = 3pF</math></p>                                                                                                                                                                                                                                                                       |  <p>ILA06813</p> |

| 20       | GND                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                      |

Continued on next page.

Continued from preceding page.

| Pin No. | Pin                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Equivalent circuit                                                                                   |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

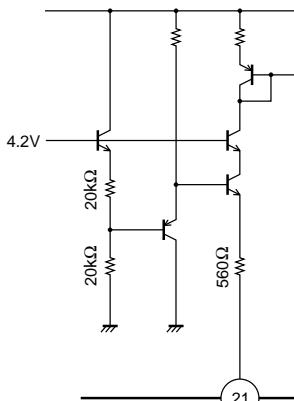

| 21      | RF AGC VR          | <p>RF AGC VR connection<br/>This pin sets the tuner RF AGC operating point. The FM output and the video output can be muted at the same time by connecting this pin to ground.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  <p>ILA06814</p>   |

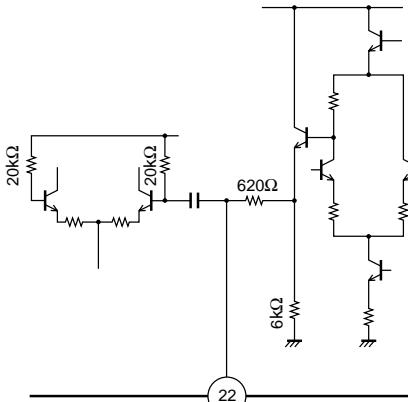

| 22      | NICAM output       | <p>First SIF output<br/>The input circuit includes a <math>600\Omega</math> resistor in the emitter-follower output.<br/>If an intercarrier is used, the buzz characteristics can be improved by forming a chroma carrier trap on this pin.</p> <p>22</p> <p>← This circuit forms a chroma carrier trap.</p>                                                                                                                                                                                                                                                                                                                               |  <p>ILA06815</p>  |

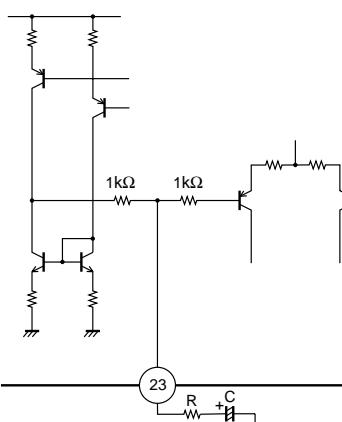

| 23      | FM filter          | <p>Connection for the filter that holds the FM detector output voltage fixed.<br/>Normally, a <math>1\mu\text{F}</math> electrolytic capacitor is used. If there are problems with the low band (around 50Hz) frequency characteristics, this capacitor value should be increased.<br/>The FM detector output level can be reduced and the FM dynamic range increased by inserting a resistor between pin 23 and ground in series with the capacitor 0.</p>                                                                                                                                                                                |  <p>ILA06817</p> |

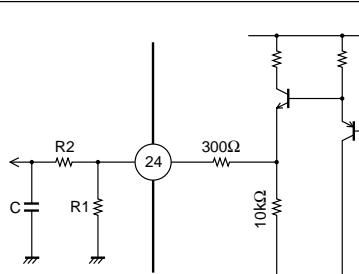

| 24      | FM Detector output | <p>Audio FM detector output<br/>There is an internal <math>300\Omega</math> resistor in series with this emitter-follower output.</p> <ul style="list-style-type: none"> <li><b>Stereo applications</b><br/>Certain stereo decoder input applications have a low input impedance, and this can cause distortion in the left and right signals and degrade the stereo characteristics. If that is the case, add a resistor between pin 24 and ground.<br/><math>R1 \geq 5.1\text{k}\Omega</math></li> <li><b>Mono applications</b><br/>Form an external deemphasis circuit at this pin.<br/><math>T = 2 \times C \times R</math></li> </ul> |  <p>ILA06818</p> |

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 2005. Specifications and information herein are subject to change without notice.