The TLM-2.0 Standard

John Aynsley, Doulos

## The TLM-2.0 Standard

CONTENTS \_

- Review of SystemC and TLM

- Review of TLM-2.0

- Frequently Asked Questions

# What is SystemC?

- System-level modeling language

- Network of communicating processes (c.f. HDL)

- Modeling hardware and software together

- New: SystemC-AMS (mixed signal)

- C++ class library

- Industry standard IEEE 1666™

- Owned and driven by OSCI (Open SystemC Initiative)

- Open source implementation

- Mature, robust, easy-to-integrate and "free"

# **Transaction Level Modeling**

Simulate every event!

100-10,000 X faster simulation!

# Reasons for using TLM

Firmware / software

Accelerates product release schedule

Software development

TLM

Ready before RTL

RTL

Test bench

**Architectural exploration**

Hardware verification

TLM = golden model

Design Verification Conference and Exhibition

# **TLM is Communication-Oriented**

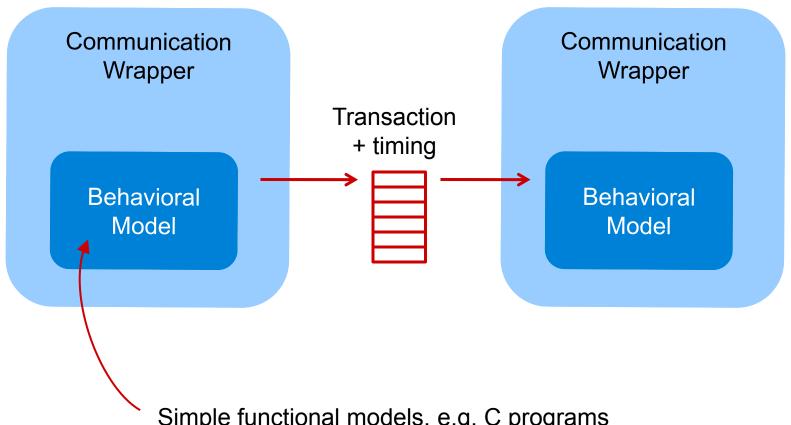

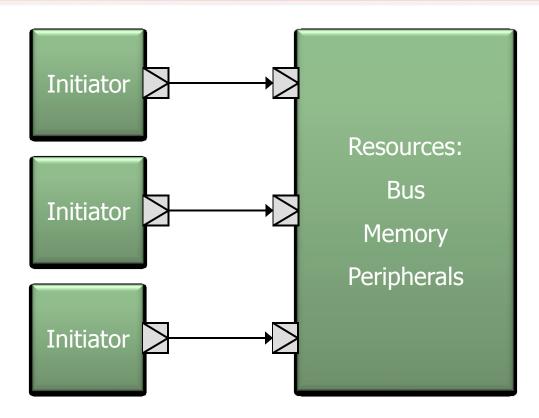

#### Concurrent simulation environment

Simple functional models, e.g. C programs

Could be synthesized by an ESL synthesis tool?

6

Design Verification Conference and Exhibition

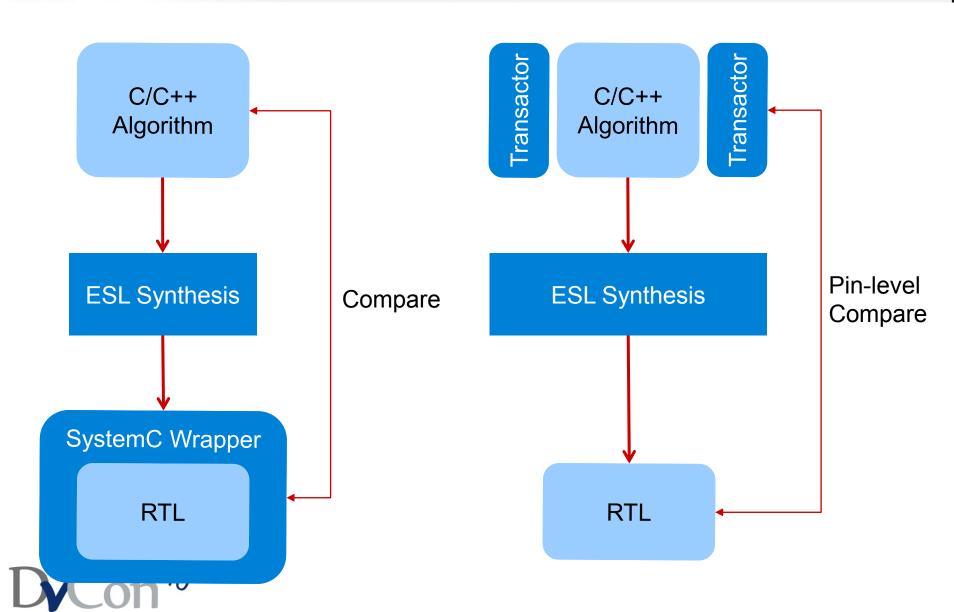

# **TLM and Synthesis**

## The TLM-2.0 Standard

CONTENTS \_

- Review of SystemC and TLM

- Review of TLM-2.0

- Frequently Asked Questions

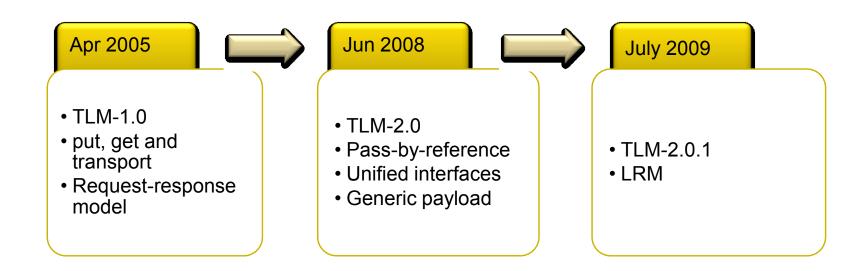

# **OSCITLM Timeline**

TLM-2.0 focusses on memory-mapped bus modeling

Speed!

Interoperability!

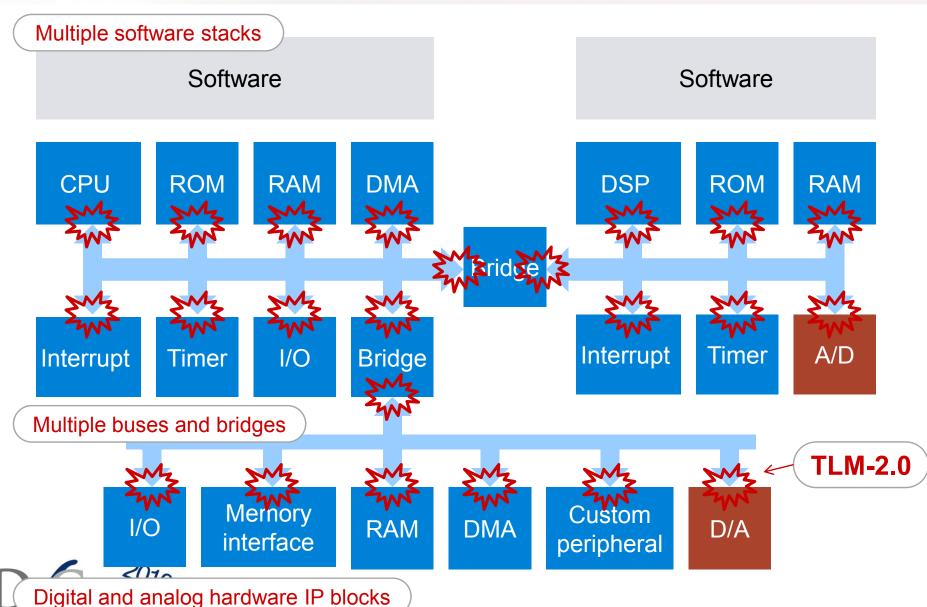

# **Typical Use Case: Virtual Platform**

## **Virtual Platform Characteristics**

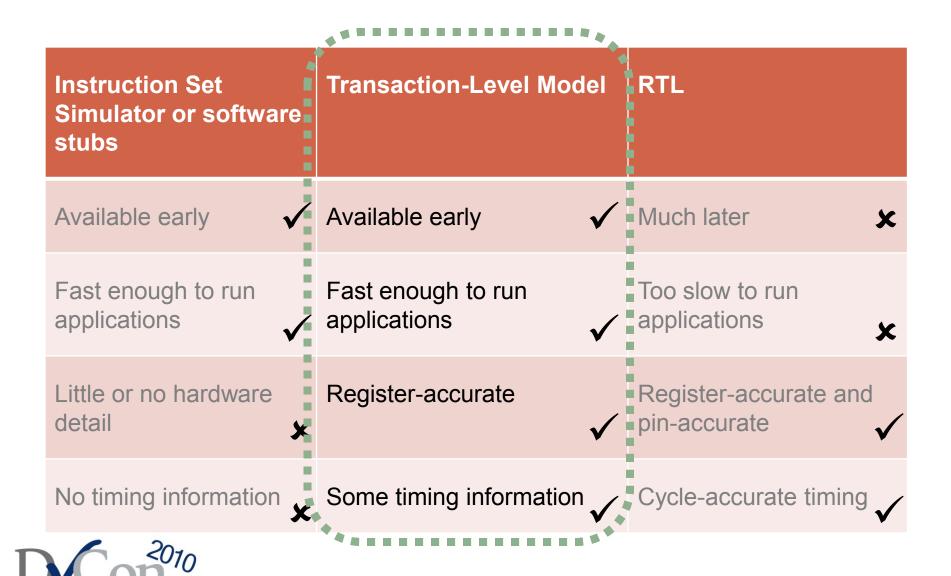

# Coding Styles and Mechanisms

#### Use cases

Software development

Software performance

Architectural analysis

Hardware verification

TLM-2 Coding styles (just guidelines)

Loosely-timed

**Approximately-timed**

Mechanisms (definitive API for TLM-2.0 enabling interoperability)

Blocking transport

DMI

Quantum

Sockets

Generic payload

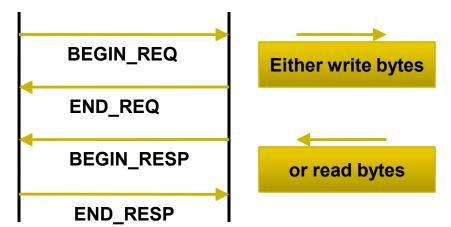

Phases

Non-blocking transport

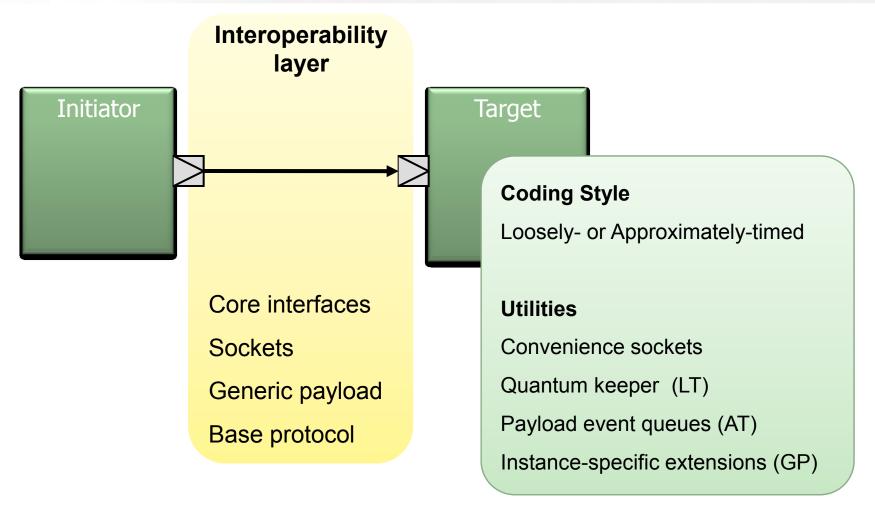

# Interoperability Layer

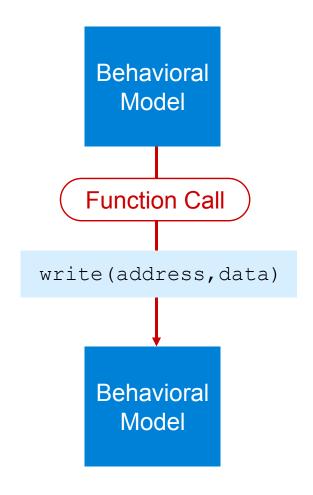

# 1. Core interfaces and sockets The first function call Target

#### 2. Generic payload

Command

Address

Data

Byte enables

Streaming

Response status

Extensions

#### 3. Base protocol

## **Utilities**

- Productivity

- Shortened learning curve

- Consistent coding style

## The TLM-2.0 Standard

CONTENTS \_

- Review of SystemC and TLM

- Review of TLM-2.0

- Frequently Asked Questions

"Do I want LT or AT or CA?"

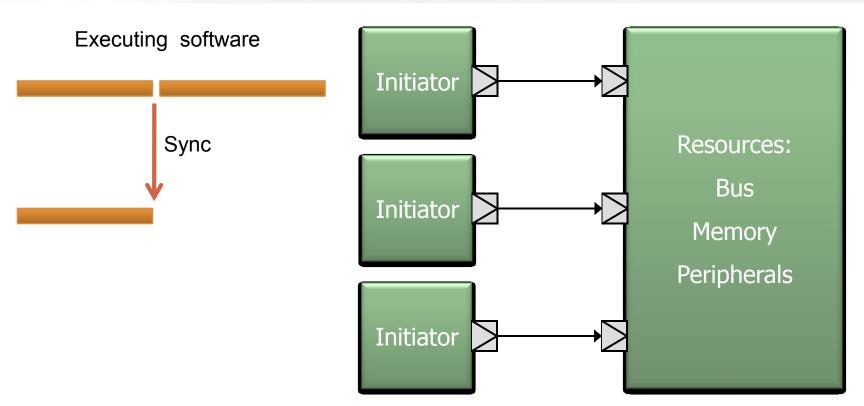

# **Loosely-Timed**

Executing software

The End!

- Goal: execute software at full speed of host processor

- Target models do not consume any time, initiators run ahead

- Need the initiators to take turns

- Either have explicit synchronization points (can be untimed)

- or initiators must use a time quantum

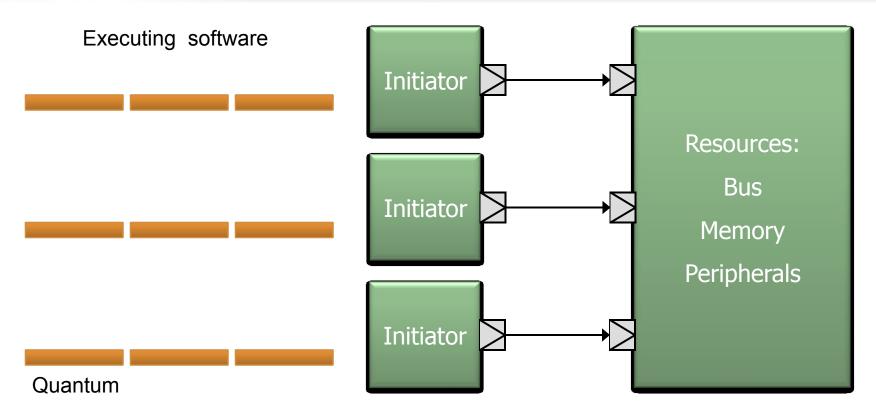

# **Loosely-Timed**

- Goal: execute software at full speed of host processor

- Target models do not consume any time, initiators run ahead

- Need the initiators to take turns

- Either have explicit synchronization points (can be untimed)

- or initiators must use a time quantum

# **Loosely-Timed**

- Goal: execute software at full speed of host processor

- Target models do not consume any time, initiators run ahead

- Need the initiators to take turns

- Either have explicit synchronization points (can be untimed)

- or initiators must use a time quantum

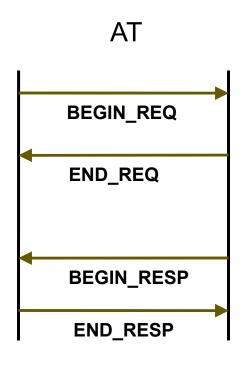

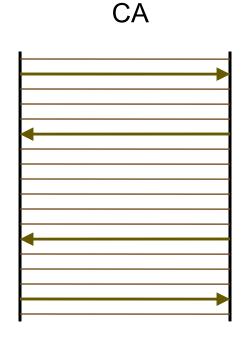

# AT and CA

No running ahead of simulation time; everything stays in sync

Wake up at significant timing points

Wake up every cycle

"How do I model such-and-such a feature using TLM-2?"

"What does it take to make a model TLM-2-compliant?"

"How much of this 194-page LRM do I really need to understand?"

"How can TLM-2 make models of different protocols interoperable?"

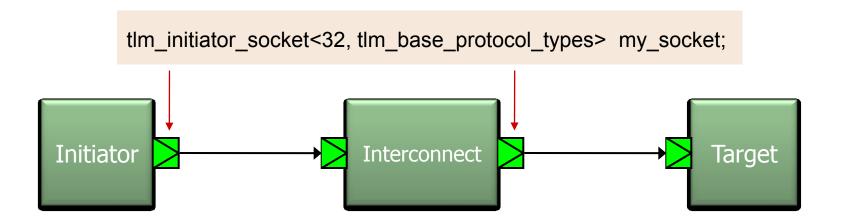

# First Kind of Interoperability

- Use the full interoperability layer

- Use the generic payload + ignorable extensions

- Obey all the rules of the base protocol. The LRM is your rule book

Functional incompatibilities are still possible (e.g. writing to a ROM)

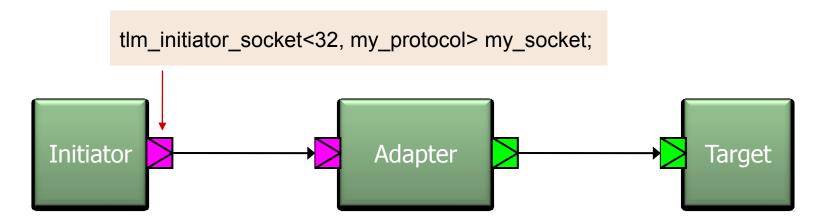

# Second Kind of Interoperability

- Create a new protocol traits class

- Create user-defined generic payload extensions and phases as needed

- Make your own rules!

- One rule enforced: cannot bind sockets of differing protocol types

- Recommendation: keep close to the base protocol. The LRM is your guidebook

- The clever stuff in TLM-2.0 makes the adapter fast

- Q. "How do I model such-and-such a feature using TLM-2?"

- A. Either make do with the generic payload, or create extensions

- Q. "What does it take to make a model TLM-2-compliant?"

- A. Either obey the base protocol or make your own rules

- Q. "How much of this 194-page LRM do I really need to understand?"

- A. For the base protocol, everything except Utilities and TLM-1

- Q. "How can TLM-2 make models of different protocols interoperable?"

- A. Either map onto the base protocol, or write adapters

Q. "How do I model my algorithm using TLM-2.0"

A1. Not applicable. TLM is communication-centric

A2. Use the LT/AT coding styles as guidelines

A3. Use the utilities at least as examples

Q. "How do I use extensions? It's not really explained anywhere."

Design Verification Conference and Exhibition

## **Create an Extension Class**

```

struct my_extension: tlm::tlm_extension<my_extension>

my_extension() { m_attribute1 = ...; }

virtual tlm extension base* clone() const

my extension* ext = new my extension;

ext->m attribute1 = this->m attribute1;

Standard code to clone/copy

ext->m attribute2 = this->m attribute2;

return ext;

virtual void copy from (tlm extension base const& ext)

m attribute1 = static cast<my extension const &>(ext).m attribute1;

m_attribute2 = static_cast<my_extension const &>(ext).m_attribute2;

int

m attribute1;

Any number of attributes

string m attribute2;

```

# **Setting and Getting Extensions**

#### Initiator

```

tlm generic payload* trans;

my extension* ext = new my extension;

ext->m attribute1 = 1;

ext->m attribute2 = "foo";

trans->set auto extension( ext );

socket->b transport( *trans, delay );

```

Have the initiator add the extension

### **Target**

```

virtual void b_transport( ... )

{

my_extension* ext;

trans.get_extension(ext);

if (ext) {

... = ext->m_attribute1;

... = ext->m_attribute2;

...

}

```

Target can test for an extension

Q. "Okay, but you've not shown me how to create ignorable extensions.

How do I do that?"

A. Being ignorable is not an explicit property of an extension, but about how you use it

# **Ignorable Extensions**

#### An ignorable extension is able to be ignored

- Timestamp when the transaction was created

- An initiator ID or transaction ID

#### Extensions that might not be ignorable

- An extended address (initiator might rely on extended address space)

- A priority (initiator might rely on high priority transaction executing first)

- A flag to lock the interconnect (initiator might rely on have exclusive access)

Q. "How do I dispose of the extension object? Can I re-use it?"

A. Use a memory manager

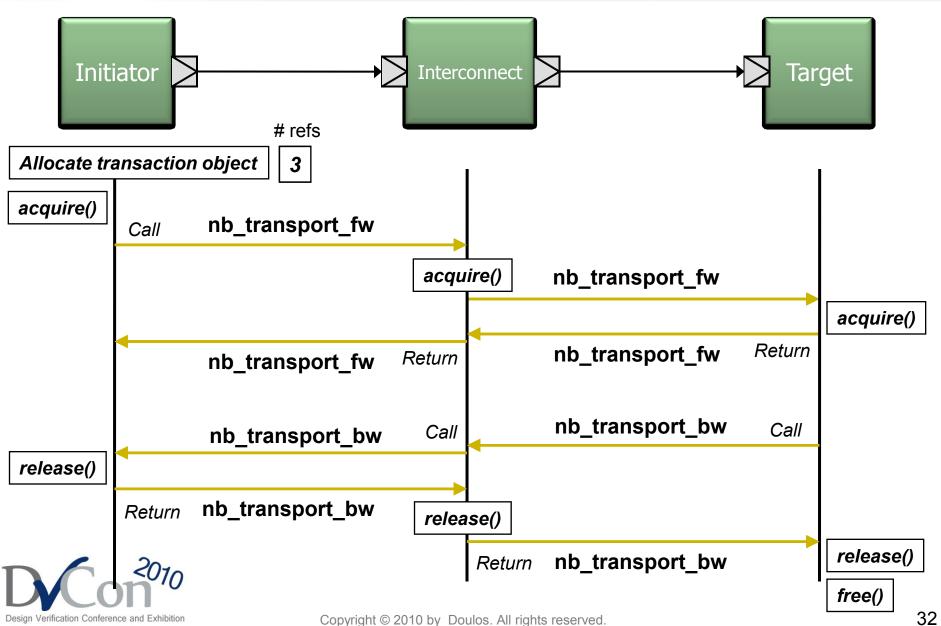

# **Using a Memory Manager**

# **Memory Management Methods**

```

class tlm_generic_payload {

public:

tlm generic payload ();

tlm_generic_payload(tlm mm interface* mm);

virtual ~tlm generic payload ();

void set_mm(tlm mm interface* mm);

bool has mm();

void acquire();

void release();

get ref count();

int

void deep_copy_from( const tlm_generic_payload& );

void update_original_from( const tlm generic payload& );

void free all extensions();

void reset();

Frees all auto-extensions

};

```

# A User-Defined Memory Manager

```

#include "tlm.h"

class gp_mm: public tlm::tlm_mm_interface

typedef tlm::tlm generic payload gp t;

public:

gp_mm();

virtual ~gp_mm();

gp_t* allocate() {

Pass mm as constructor arg

ptr = new gp_t( this );

Called when ref count == 0

void free(gp_t* trans) {

trans->reset();

Free auto-extensions

```

Design Verification Conference and Exhibition

# **Typical Coding Idiom**

```

my_module(sc_module_name _n, gp_mm* mm)

Pass mm as constructor arg

: m mm(mm) {...}

tlm generic payload* trans;

Get transaction object from mm

trans = m mm.allocate();

trans->acquire();

Increment reference count

my extension* ext = new my extension;

Allocate extension on heap

ext->m attribute1 = 1;

ext->m attribute2 = "foo";

Set for auto-deletion

trans->set auto extension( ext );

Not just for nb_transport

socket->b transport( *trans, delay );

Decrement reference count

trans->release();

```

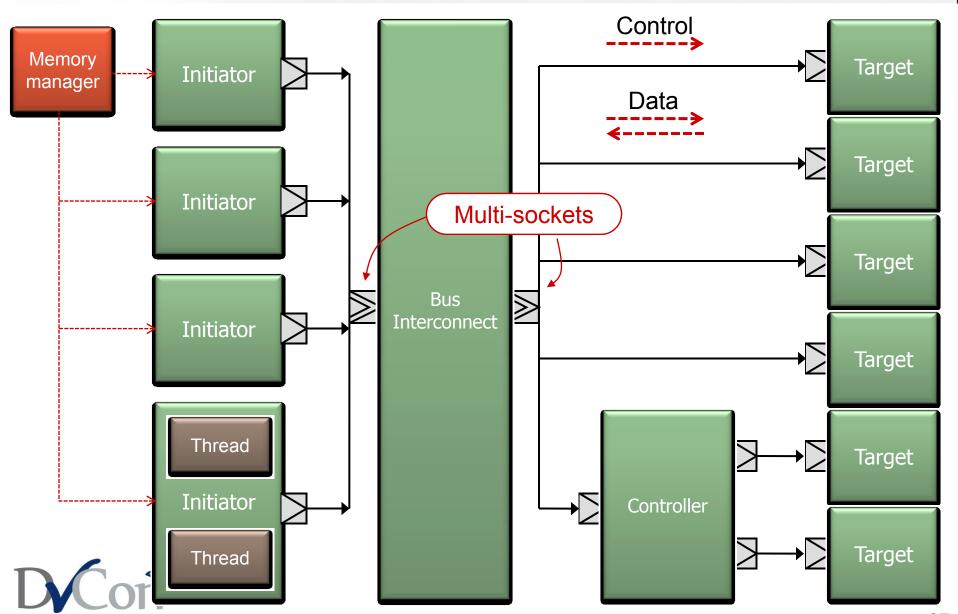

- Q. "How do I connect multiple components together?"

- Q. "How do I model a bus with multiple masters/slaves?"

- Q. "How many sockets do I need for two-way communication?"

- Q. "How many transactions do I use?"

# **Example Topology**

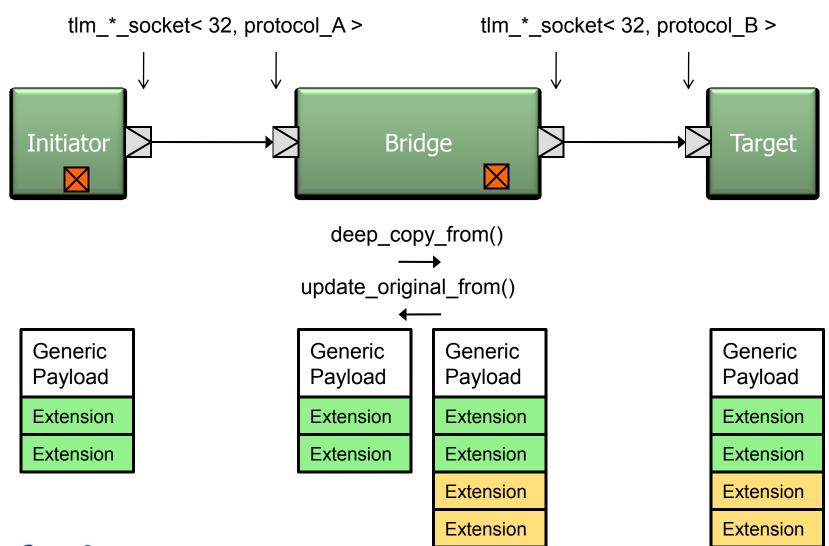

# **Bridges**

# **Copying the Data Array**

Deep-copy the data array in the bridge

```

new_trans->set_data_ptr( &data_buffer );

new_trans->deep_copy_from ( original_trans );

new_trans->b_transport(...);

original_trans->update_original_from( new_trans );

```

Copies back data array on read

Shallow-copy the data array in the bridge

```

new_trans->set_data_ptr( 0 );

new_trans->deep_copy_from ( original_trans );

new_trans->set_data_ptr( original_trans->get_data_ptr() );

new_trans->b_transport(...);

original_trans->update_original_from( new_trans );

```

Does not touch data array

- Q. "How do I connect multiple components together?"

- A. By having one or more components act as a hub

- Q. "How do I model a bus with multiple masters/slaves?"

- A. The "hub" can do arbitration and routing. Use multi-sockets for convenience

- Q. "How many sockets do I need for two-way communication?"

- A. Each initiator needs an initiator socket, each target a target socket

- Q. "How many transactions do I use?"

- A. As few as possible

- Q. "How do I model something like a SPI port?"

- A. If you can abstract the functionality, use the base protocol

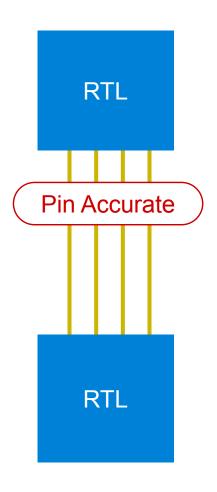

- Q. "How do I model something like a SPI port with accurate timing?"

- A. You can model precise timing with the AT coding style, but why not use RTL?

- Q. "How do I model something like AMBA, PCI, or USB?"

- A. Buy a model (or get one through a university/research program)

## For More FREE Information

IEEE 1666

standards.ieee.org/getieee/1666/index.html

OSCI SystemC 2.2 and TLM-2.0

www.systemc.org

Tutorial introduction to TLM-2.0 and Free TLM-2.0 Protocol Checker

www.doulos.com/knowhow/systemc/tlm2

# System Design

SystemC ARM • C++

Verification Methodology

e • PSL • SCVSystemVerilog

Hardware Design

VHDL • Verilog Altera • Xilinx Perl • Tcl/Tk