# LMV331 Single / LMV393 Dual / LMV339 Quad General Purpose, Low Voltage, Tiny Pack Comparators

# **General Description**

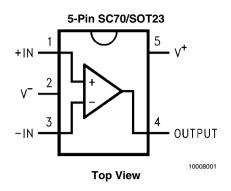

The LMV393 and LMV339 are low voltage (2.7-5V) versions of the dual and quad comparators, LM393/339, which are specified at 5-30V. The LMV331 is the single version, which is available in space saving 5-pin SC70 and 5-pin SOT23 packages. The 5-pin SC70 is approximately half the size of the 5-pin SOT23.

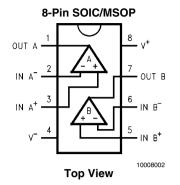

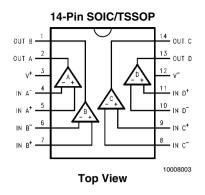

The LMV393 is available in 8-pin SOIC and MSOP. The LMV339 is available in 14-pin SOIC and TSSOP.

The LMV331/393/339 is the most cost-effective solution where space, low voltage, low power and price are the primary specification in circuit design for portable consumer products. They offer specifications that meet or exceed the familiar LM393/339 at a fraction of the supply current.

The chips are built with National's advanced Submicron Silicon-Gate BiCMOS process. The LMV331/393/339 have bipolar input and output stages for improved noise performance.

# **Features**

(For 5V supply, typical unless otherwise noted)

- Guaranteed 2.7V and 5V performance

- Industrial temperature range -40°C to +85°C

- Low supply current 60 µA/Channel

- Input common mode voltage range includes ground

- Low output saturation voltage200 m

- Propagation delay 200 ns

- Space saving 5-pin SC70 and 5-Pin SOT23 packages

# **Applications**

- Mobile communications

- Notebooks and PDA's

- Battery powered electronics

- General purpose portable device

- General purpose low voltage applications

# **Typical Applications**

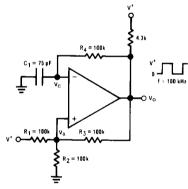

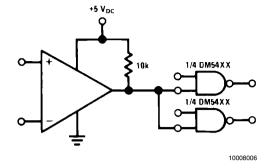

#### **Squarewave Oscillator**

10008008

10008024

Positive Peak Detector

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2) **Human Body Model**

LMV331/393/339 800V Machine Model LMV331/339/393 120V Differential Input Voltage ±Supply Voltage Voltage on any pin

(referred to V- pin) Soldering Information

Infrared or Convection (20 sec) 235°C Storage Temp. Range -65°C to +150°C Junction Temperature (Note 3) 150°C

# **Operating Ratings** (Note 1)

Supply Voltage 2.7V to 5.0V

Temperature Range (Note 3)

LMV393, LMV339, LMV331 -40°C to +85°C

Thermal Resistance  $(\theta_{IA})$

5-Pin SC70 478°C/W 5-Pin SOT23 265°C/W 8-Pin SOIC 190°C/W 8-Pin MSOP 235°C/W 14-Pin SOIC 145°C/W 14-Pin TSSOP 155°C/W

# 2.7V DC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for T<sub>J</sub> = 25°C, V+ = 2.7V, V- = 0V. Boldface limits apply at the temperature extremes.

5.5V

| Symbol            | Parameter                          | Conditions                     | Min<br>(Note 5) | Typ<br>(Note 4) | Max<br>(Note 5)   | Units |  |

|-------------------|------------------------------------|--------------------------------|-----------------|-----------------|-------------------|-------|--|

| V <sub>os</sub>   | Input Offset Voltage               |                                |                 | 1.7             | 7                 | mV    |  |

| TCV <sub>OS</sub> | Input Offset Voltage Average Drift |                                |                 | 5               |                   | μV/°C |  |

| I <sub>B</sub>    | Input Bias Current                 |                                |                 | 10              | 250<br><b>400</b> | nA    |  |

| I <sub>OS</sub>   | Input Offset Current               |                                |                 | 5               | 50<br><b>150</b>  | nA    |  |

| V <sub>CM</sub>   | Input Voltage Range                |                                |                 | -0.1            |                   | V     |  |

|                   |                                    |                                |                 | 2.0             |                   | ٧     |  |

| V <sub>SAT</sub>  | Saturation Voltage                 | I <sub>SINK</sub> ≤ 1 mA       |                 | 120             |                   | mV    |  |

| I <sub>o</sub>    | Output Sink Current                | V <sub>O</sub> ≤ 1.5V          | 5               | 23              |                   | mA    |  |

| I <sub>s</sub>    | Supply Current                     | LMV331                         |                 | 40              | 100               | μA    |  |

|                   |                                    | LMV393<br>Both Comparators     |                 | 70              | 140               | μΑ    |  |

|                   |                                    | LMV339<br>All four Comparators |                 | 140             | 200               | μΑ    |  |

|                   | Output Leakage Current             |                                |                 | .003            | 1                 | μA    |  |

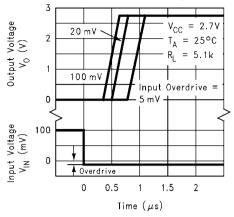

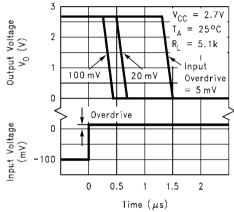

# 2.7V AC Electrical Characteristics

$T_J=25^{\circ}C,~V^{+}=2.7V,~R_L^{}~=5.1~k\Omega,~V^{-}=0V.$

| Symbol           | Parameter                       | Conditions               | Min      | Тур      | Max      | Units |

|------------------|---------------------------------|--------------------------|----------|----------|----------|-------|

|                  |                                 |                          | (Note 5) | (Note 4) | (Note 5) |       |

| t <sub>PHL</sub> | Propagation Delay (High to Low) | Input Overdrive = 10 mV  |          | 1000     |          | ns    |

|                  |                                 | Input Overdrive = 100 mV |          | 350      |          | ns    |

| t <sub>PLH</sub> | Propagation Delay (Low to High) | Input Overdrive = 10 mV  |          | 500      |          | ns    |

|                  |                                 | Input Overdrive = 100 mV |          | 400      |          | ns    |

# **5V DC Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ . **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                          | Conditions               | Min      | Тур      | max      | Units |  |

|------------------|------------------------------------|--------------------------|----------|----------|----------|-------|--|

|                  |                                    |                          | (Note 5) | (Note 4) | (Note 5) |       |  |

| Vos              | Input Offset Voltage               |                          |          | 1.7      | 7        | mV    |  |

|                  |                                    |                          |          |          | 9        | mv    |  |

| $TCV_OS$         | Input Offset Voltage Average Drift |                          |          | 5        |          | μV/°C |  |

| I <sub>B</sub>   | Input Bias Current                 |                          |          | 25       | 250      | ^     |  |

|                  |                                    |                          |          |          | 400      | nA    |  |

| I <sub>os</sub>  | Input Offset Current               |                          |          | 2        | 50       | nA    |  |

|                  |                                    |                          |          |          | 150      | IIA   |  |

| V <sub>CM</sub>  | Input Voltage Range                |                          |          | -0.1     |          | V     |  |

|                  |                                    |                          |          | 4.2      |          | V     |  |

| A <sub>V</sub>   | Voltage Gain                       |                          | 20       | 50       |          | V/mV  |  |

| V <sub>sat</sub> | Saturation Voltage                 | I <sub>SINK</sub> ≤ 4 mA |          | 200      | 400      | mV    |  |

|                  |                                    | Olivic                   |          |          | 700      | IIIV  |  |

| $I_{O}$          | Output Sink Current                | V <sub>O</sub> ≤ 1.5V    |          | 84       | 10       | mA    |  |

| I <sub>s</sub>   | Supply Current                     | LMV331                   |          | 60       | 120      |       |  |

|                  |                                    |                          |          |          | 150      | μA    |  |

|                  |                                    | LMV393                   |          | 100      | 200      |       |  |

|                  |                                    | Both Comparators         |          |          | 250      | μA    |  |

|                  |                                    | LMV339                   |          | 170      | 300      |       |  |

|                  |                                    | All four Comparators     |          |          | 350      | μA    |  |

|                  | Output Leakage Current             |                          |          | .003     | 1        | μΑ    |  |

# **5V AC Electrical Characteristics**

$T_{.1} = 25^{\circ}C, V^{+} = 5V, R_{1}^{-} = 5.1 \text{ k}\Omega, V^{-} = 0V.$

| Symbol           | Parameter                       | Conditions               | Min<br>(Note 5) | Typ<br>(Note 4) | Max<br>(Note 5) | Units |  |

|------------------|---------------------------------|--------------------------|-----------------|-----------------|-----------------|-------|--|

| t <sub>PHL</sub> | Propagation Delay (High to Low) | Input Overdrive = 10 mV  | , ,             | 600             | ,               | ns    |  |

|                  |                                 | Input Overdrive = 100 mV |                 | 200             |                 | ns    |  |

| t <sub>PLH</sub> | Propagation Delay (Low to High) | Input Overdrive = 10 mV  |                 | 450             |                 | ns    |  |

|                  |                                 | Input Overdrive = 100 mV |                 | 300             |                 | ns    |  |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical characteristics.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

Note 3: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)}, T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

**Note 4:** Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 5: All limits are guaranteed by testing or statistical analysis.

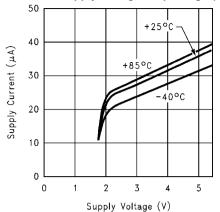

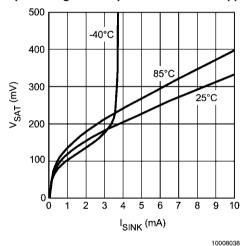

# Typical Performance Characteristics Unless otherwise specified, $V_S = +5V$ , single supply, $T_A = 25^{\circ}C$

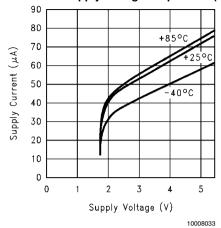

## Supply Current vs. Supply Voltage Output High (LMV331) Supply Current vs. Supply Voltage Output Low (LMV331)

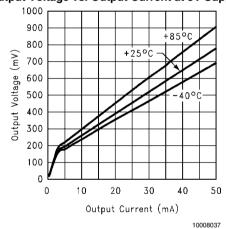

## Output Voltage vs. Output Current at 5V Supply

10008034

## Output Voltage vs. Output Current at 2.7 Supply

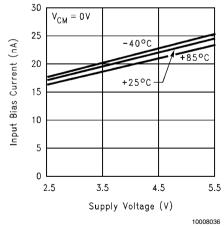

## Input Bias Current vs. Supply Voltage

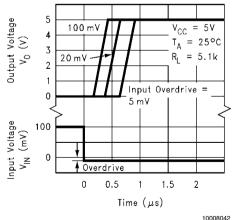

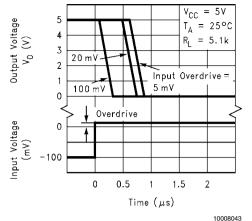

## Response Time vs. Input Overdrives Negative Transition

## **Response Time for Input Overdrive Positive Transition**

#### **Response Time vs. Input Overdrives Negative Transition**

## 10008041

# **Response Time for Input Overdrive Positive Transition**

10008040

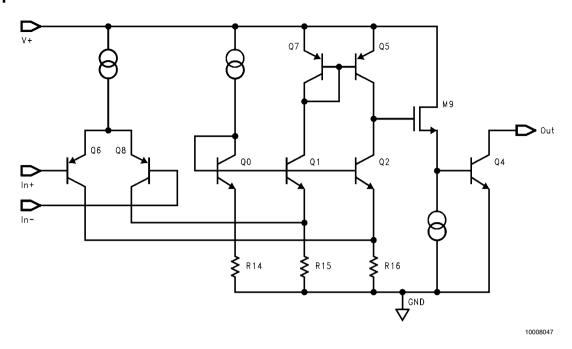

# **Simplified Schematic**

# **Application Circuits**

#### **BASIC COMPARATOR**

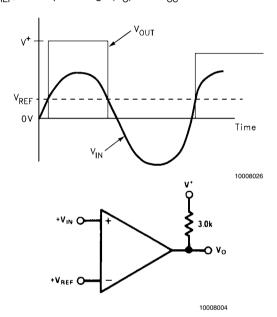

A basic comparator circuit is used for converting analog signals to a digital output. The LMV331/393/339 have an open-collector output stage, which requires a pull-up resistor to a positive supply voltage for the output to switch properly. When the internal output transistor is off, the output voltage will be pulled up to the external positive voltage.

The output pull-up resistor should be chosen high enough so as to avoid excessive power dissipation yet low enough to supply enough drive to switch whatever load circuitry is used on the comparator output. On the LMV331/393/339 the pull-up resistor should range between 1k to  $10k\Omega$ .

The comparator compares the input voltage  $(V_{IN})$  at the non-inverting pin to the reference voltage  $(V_{REF})$  at the inverting pin. If  $V_{IN}$  is less than  $V_{REF}$ , the output voltage  $(V_O)$  is at the saturation voltage. On the other hand, if  $V_{IN}$  is greater than  $V_{REF}$ , the output voltage  $(V_O)$  is at  $V_{CC}$ .

FIGURE 1. Basic Comparator

#### **COMPARATOR WITH HYSTERESIS**

The basic comparator configuration may oscillate or produce a noisy output if the applied differential input voltage is near the comparator's offset voltage. This usually happens when the input signal is moving very slowly across the comparator's switching threshold. This problem can be prevented by the addition of hysteresis or positive feedback.

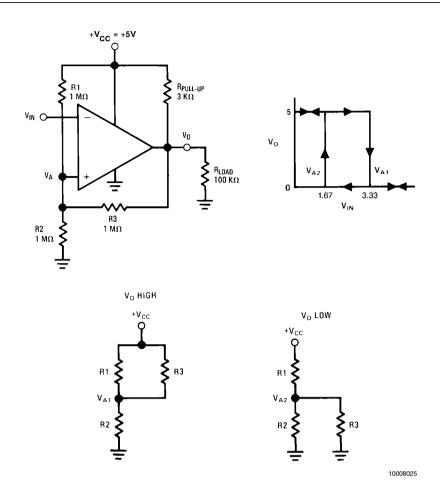

#### **INVERTING COMPARATOR WITH HYSTERESIS**

The inverting comparator with hysteresis requires a three resistor network that are referenced to the supply voltage  $V_{\rm CC}$  of the comparator. When  $V_{\rm in}$  at the inverting input is less than  $V_{\rm a}$ , the voltage at the non-inverting node of the comparator  $(V_{\rm in} < V_{\rm a}),$  the output voltage is high (for simplicity assume  $V_{\rm O}$  switches as high as  $V_{\rm CC}).$  The three network resistors can be represented as  $R_1/\!/R_3$  in series with  $R_2.$  The lower input trip voltage  $V_{\rm a1}$  is defined as

$$V_{a_1} = \frac{V_{CC} R_2}{(R_1 || R_3) + R_2}$$

When  $V_{in}$  is greater than  $V_a$  ( $V_{in} > V_a$ ), the output voltage is low very close to ground. In this case the three network resistors can be presented as  $R_2/\!/R_3$  in series with  $R_1$ . The upper trip voltage  $V_{a2}$  is defined as

$$V_{a2} = \frac{V_{CC}(R_2//R_3)}{R_1 + (R_2//R_3)}$$

The total hysteresis provided by the network is defined as

$$\Delta V_a = V_{a1} - V_{a2}$$

To assure that the comparator will always switch fully to  $V_{\rm CC}$  and not be pulled down by the load the resistors values should be chosen as follow:

$$R_{PULL-UP} \ll R_{LOAD}$$

and  $R_1 > R_{PULL-UP}$ .

FIGURE 2. Inverting Comparator with Hysteresis

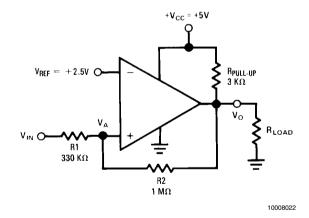

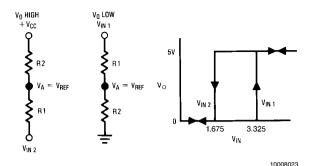

#### **NON-INVERTING COMPARATOR WITH HYSTERESIS**

Non inverting comparator with hysteresis requires a two resistor network, and a voltage reference ( $V_{\text{ref}}$ ) at the inverting input. When  $V_{\text{in}}$  is low, the output is also low. For the output to switch from low to high,  $V_{\text{in}}$  must rise up to  $V_{\text{in1}}$  where  $V_{\text{in1}}$  is calculated by

$$V_{in1} = \frac{V_{ref}(R_1 + R_2)}{R_2}$$

When  $V_{in}$  is high, the output is also high, to make the comparator switch back to it's low state,  $V_{in}$  must equal  $V_{ref}$  before  $V_A$  will again equal  $V_{ref}$ .  $V_{in}$  can be calculated by:

$$V_{in2} = \frac{V_{ref}(R_1 + R_2) - V_{CC}R_1}{R_2}$$

The hysteresis of this circuit is the difference between  $\boldsymbol{V}_{\text{in1}}$  and  $\boldsymbol{V}_{\text{in2}}.$

$$\Delta V_{in} = V_{CC}R_1/R_2$$

FIGURE 3.

FIGURE 4.

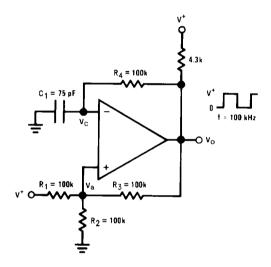

#### SQUAREWAVE OSCILLATOR

Comparators are ideal for oscillator applications. This square wave generator uses the minimum number of components. The output frequency is set by the RC time constant of the capacitor  $C_1$  and the resistor in the negative feedback  $R_4$ . The maximum frequency is limited only by the large signal propagation delay of the comparator in addition to any capacitive loading at the output, which would degrade the output slew rate.

FIGURE 5. Squarewave Oscillator

10008024

9

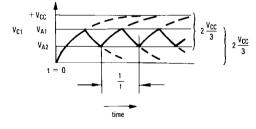

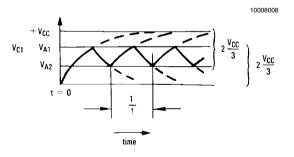

To analyze the circuit, assume that the output is initially high. For this to be true, the voltage at the inverting input  $V_c$  has to be less than the voltage at the non-inverting input  $V_a$ . For  $V_c$  to be low, the capacitor  $C_1$  has to be discharged and will charge up through the negative feedback resistor  $R_4.$  When it has charged up to value equal to the voltage at the positive input  $V_{a1}$ , the comparator output will switch.

V<sub>a1</sub> will be given by:

$$V_{a1} = \frac{V_{CC} R_2}{R_2 + (R_1 // R_2)}$$

If:

$$R_1 = R_2 = R_3$$

Then:

$$V_{a1} = 2V_{CC}/3$$

When the output switches to ground, the value of  ${\rm V_a}$  is reduced by the hysteresis network to a value given by:

$$V_{a2} = V_{CC}/3$$

Capacitor  $C_1$  must now discharge through  $R_4$  towards ground. The output will return to its high state when the voltage across the capacitor has discharged to a value equal to  $V_{a2}$ .

For the circuit shown, the period for one cycle of oscillation will be twice the time it takes for a single RC circuit to charge up to one half of its final value. The time to charge the capacitor can be calculated from

$$V_{C} = V_{max} e^{\frac{-t}{RC}}$$

Where  $V_{max}$  is the max applied potential across the capacitor =  $(2V_{\rm CC}/3)$

and  $V_C = Vmax/2 = V_{CC}/3$

One period will be given by:

$$1/\text{freq} = 2t$$

or calculating the exponential gives:

$$1/\text{freg} = 2(0.694) \text{ R}_{4} \text{ C}_{1}$$

Resistors  $R_3$  and  $R_4$  must be at least two times larger than  $R_5$  to insure that  $V_O$  will go all the way up to  $V_{CC}$  in the high state. The frequency stability of this circuit should strictly be a function of the external components.

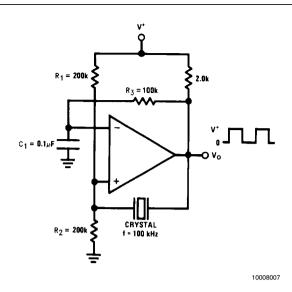

#### FREE RUNNING MULTIVIBRATOR

A simple yet very stable oscillator that generates a clock for slower digital systems can be obtained by using a resonator as the feedback element. It is similar to the free running multivibrator, except that the positive feedback is obtained through a quartz crystal. The circuit oscillates when the transmission through the crystal is at a maximum, so the crystal in its series-resonant mode.

The value of  $\rm R_1$  and  $\rm R_2$  are equal so that the comparator will switch symmetrically about +V $_{\rm CC}/2$ . The RC constant of  $\rm R_3$  and  $\rm C_1$  is set to be several times greater than the period of the oscillating frequency, insuring a 50% duty cycle by maintaining a DC voltage at the inverting input equal to the absolute average of the output waveform.

When specifying the crystal, be sure to order series resonant with the desired temperature coefficient

FIGURE 6. Crystal controlled Oscillator

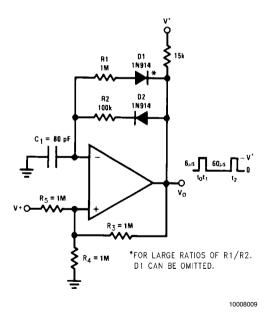

#### PULSE GENERATOR WITH VARIABLE DUTY CYCLE

The pulse generator with variable duty cycle is just a minor modification of the basic square wave generator. Providing a separate charge and discharge path for capacitor  $C_1$ generates a variable duty cycle. One path, through  $R_2$  and  $D_2$  will charge the capacitor and set the pulse width  $(t_1)$ . The other path,  $R_1$  and  $D_1$  will discharge the capacitor and set the time between pulses  $(t_2)$ .

By varying resistor  $R_1$ , the time between pulses of the generator can be changed without changing the pulse width. Similarly, by varying  $R_2$ , the pulse width will be altered without affecting the time between pulses. Both controls will change the frequency of the generator. The pulse width and time between pulses can be found from:

FIGURE 7. Pulse Generator

$$\begin{array}{c} V_1 = \ V_{max} \left(1-e^{-t_1/R_4C_1}\right) \ \ {\rm rise\ time} \\ V_1 = \ V_{max} = e^{-t_2/R_5C_1} \qquad {\rm fall\ time} \\ \end{array}$$

Where

$$\begin{array}{c} V_{max} = \frac{2\ V_{CC}}{3} \\ {\rm and} \\ V_1 = \frac{V_{max}}{3} = \frac{V_{CC}}{3} \\ \end{array}$$

Which gives

$$\frac{1}{2} = e^{-t_1/R_4C_1} \\ t_2 \ {\rm is\ then\ given\ by:} \\ \frac{1}{2} = e^{-t_2/R_5C_1} \end{array}$$

Solving these equations for t<sub>1</sub> and t<sub>2</sub>

$$t_1 = R_4 C_1 \ln 2$$

$$t_2 = R_5 C_1 \ln 2$$

These terms will have a slight error due to the fact that  $\rm V_{max}$  is not exactly equal to 2/3  $\rm V_{CC}$  but is actually reduced by the diode drop to:

$$V_{\text{max}} = \frac{2}{3} (V_{\text{CC}} - V_{\text{BE}})$$

$$\frac{1}{2(1 - V_{\text{BE}})} = e^{-t_1/R_4 C_1}$$

$$\frac{1}{2(1 - V_{\text{BE}})} = e^{-t_2/R_5 C_1}$$

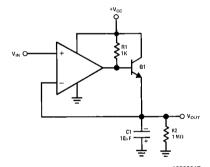

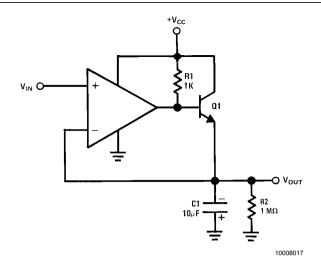

#### **POSITIVE PEAK DETECTOR**

Positive peak detector is basically the comparator operated as a unit gain follower with a large holding capacitor from the output to ground. Additional transistor is added to the output to provide a low impedance current source. When the output of the comparator goes high, current is passed through the transistor to charge up the capacitor. The only discharge path will be the 1  $\mathrm{M}\Omega$  resistor shunting C1 and any load that is connected to the output. The decay time can be altered simply by changing the 1  $\mathrm{M}\Omega$  resistor. The output should be used through a high impedance follower to a avoid loading the output of the peak detector.

FIGURE 8. Positive Peak Detector

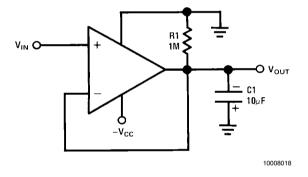

#### **NEGATIVE PEAK DETECTOR**

For the negative detector, the output transistor of the comparator acts as a low impedance current sink. The only discharge path will be the 1  $M\Omega$  resistor and any load impedance used. Decay time is changed by varying the 1  $M\Omega$  resistor

**FIGURE 9. Negative Peak Detector**

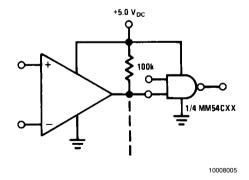

#### **DRIVING CMOS AND TTL**

The comparator's output is capable of driving CMOS and TTL Logic circuits.

FIGURE 10. Driving CMOS

FIGURE 11. Driving TTL

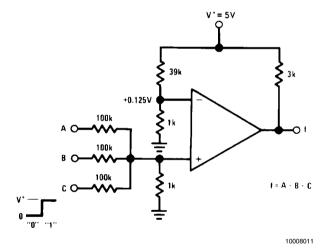

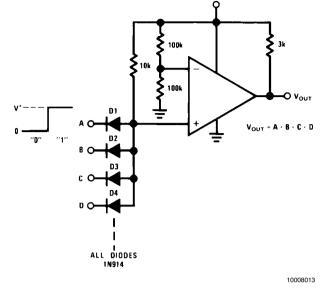

#### **AND GATES**

The comparator can be used as three input AND gate. The operation of the gate is as follow:

The resistor divider at the inverting input establishes a reference voltage at that node. The non-inverting input is the sum of the voltages at the inputs divided by the voltage dividers. The output will go high only when all three inputs are high, casing the voltage at the non-inverting input to go above that at inverting input. The circuit values shown work for a "0" equal to ground and a "1" equal to 5V.

The resistor values can be altered if different logic levels are desired. If more inputs are required, diodes are recommended to improve the voltage margin when all but one of the inputs are high.

FIGURE 12. AND Gate

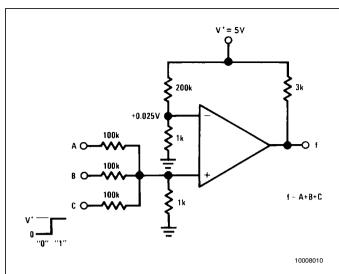

#### **OR GATES**

A three input OR gate is achieved from the basic AND gate simply by increasing the resistor value connected from the inverting input to  $V_{\rm cc}$ , thereby reducing the reference voltage. A logic "1" at any of the inputs will produce a logic "1" at the output.

FIGURE 13. OR Gate

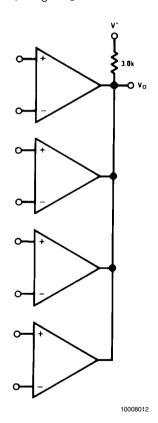

# **ORing THE OUTPUT**

By the inherit nature of an open collector comparator, the outputs of several comparators can be tied together with a pull up resistor to  $\rm V_{CC}.$  If one or more of the comparators outputs goes low, the output  $\rm V_O$  will go low.

FIGURE 15. Large Fan-In AND Gate

FIGURE 14. ORing the Outputs

# **Connection Diagrams**

# **Ordering Information**

| Package      | Temperature Range            | Packaging | Transport Media          | NSC      |

|--------------|------------------------------|-----------|--------------------------|----------|

|              | Industrial<br>-40°C to +85°C | Marking   |                          | Drawing  |

| 5-Pin SC70   | LMV331M7                     | C13       | 1k Units Tape and Reel   | MAA05A   |

| 5-4111 2070  | LMV331M7X                    | C13       | 3k Units Tape and Reel   | IVIAAUSA |

| 5-Pin SOT23  | LMV331M5                     | C12       | 1k Units Tape and Reel   | MEGEA    |

| 5-PIN 50123  | LMV331M5X                    | C12       | 3k Units Tape and Reel   | MF05A    |

| 8-Pin SOIC   | LMV393M                      | LMV393M   | Rails                    | M08A     |

| 6-PIII 50IC  | LMV393MX                     | LMV393M   | 2.5k Units Tape and Reel | IVIUOA   |

| O Die MCOD   | LMV393MM                     | V393      | 1k Units Tape and Reel   | MUA08A   |

| 8-Pin MSOP   | LMV393MMX                    | V393      | 3.5k Units Tape and Reel | MUAU8A   |

| 14-Pin SOIC  | LMV339M                      | LMV339M   | Rails                    | M14A     |

| 14-2111 2010 | LMV339MX                     | LMV339M   | 2.5k Units Tape and Reel | IVIT4A   |

| 14 Din TOOOD | LMV339MT                     | LMV339MT  | Rails                    | MTC14    |

| 14-Pin TSSOP | LMV339MTX                    | LMV339MT  | 2.5k Units Tape and Reel | MTC14    |

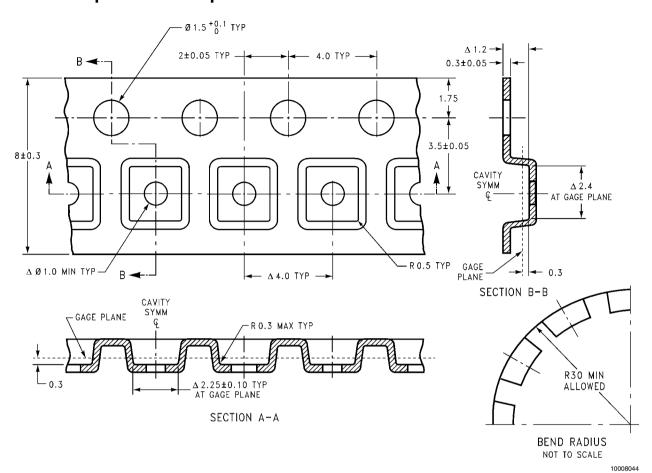

# **SC70-5 Tape and Reel Specification**

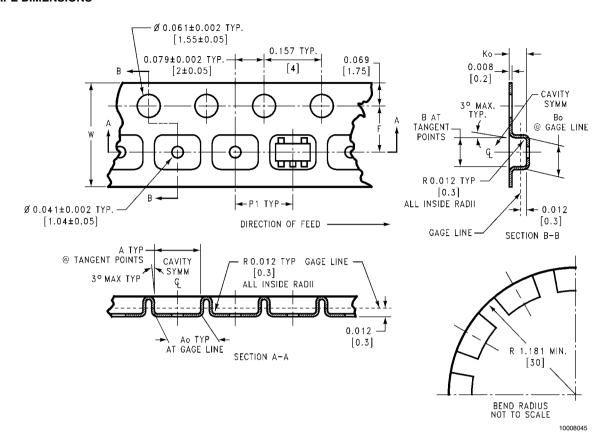

# **SOT-23-5 Tape and Reel Specification**

# TAPE FORMAT

| Tape Section | # Cavities   | Cavity Status | Cover Tape Status |

|--------------|--------------|---------------|-------------------|

| Leader       | 0 (min)      | Empty         | Sealed            |

| (Start End)  | 75 (min)     | Empty         | Sealed            |

| Carrier      | Carrier 3000 |               | Sealed            |

|              | 250          | Filled        | Sealed            |

| Trailer      | 125 (min)    | Empty         | Sealed            |

| (Hub End)    | 0 (min)      | Empty         | Sealed            |

## **TAPE DIMENSIONS**

| 8 mm      | 0.130 | 0.124  | 0.130 | 0.126  | 0.138 ±0.002 | 0.055 ±0.004 | 0.157  | 0.315 ±0.012 |

|-----------|-------|--------|-------|--------|--------------|--------------|--------|--------------|

|           | (3.3) | (3.15) | (3.3) | (3.2)  | (3.5 ±0.05)  | (1.4 ±0.11)  | (4)    | (8 ±0.3)     |

| Tape Size | DIM A | DIM Ao | DIM B | DIM Bo | DIM F        | DIM Ko       | DIM P1 | DIM W        |

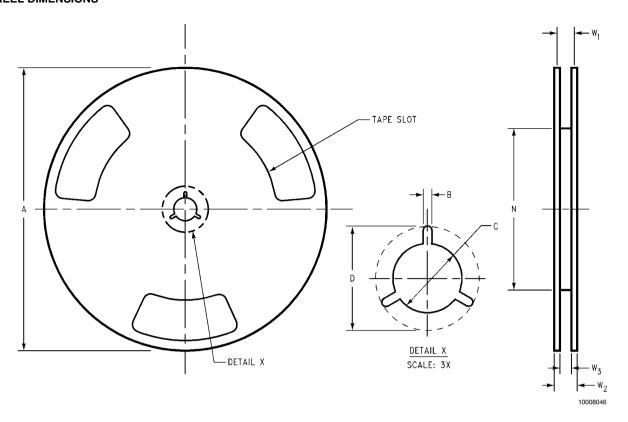

# REEL DIMENSIONS

| 8 mm      | 7.00   | 0.059 | 0.512 | 0.795 | 2.165 | 0.331 + 0.059/-0.000 | 0.567 | W1+ 0.078/-0.039 |

|-----------|--------|-------|-------|-------|-------|----------------------|-------|------------------|

|           | 330.00 | 1.50  | 13.00 | 20.20 | 55.00 | 8.40 + 1.50/-0.00    | 14.40 | W1 + 2.00/-1.00  |

| Tape Size | Α      | В     | С     | D     | N     | W1                   | W2    | W3               |

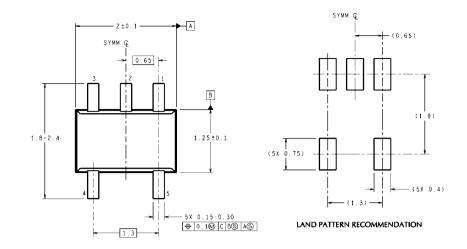

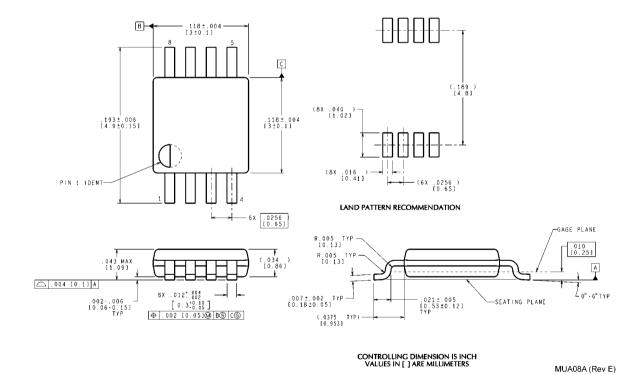

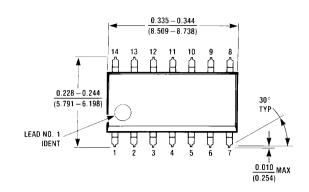

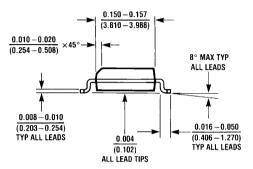

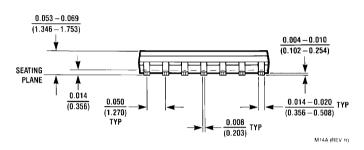

# Physical Dimensions inches (millimeters) unless otherwise noted

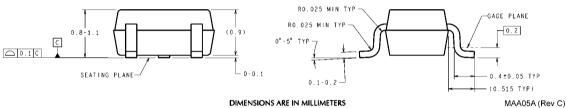

5-Pin SC70 NS Package Number MAA05A

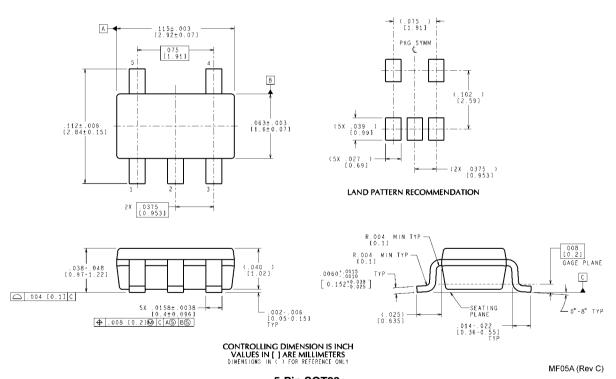

5-Pin SOT23 NS Package Number MF05A

SEATING PLANE

M08A (REV H)

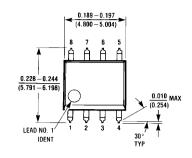

8-Pin SOIC **NS Package Number M08A**

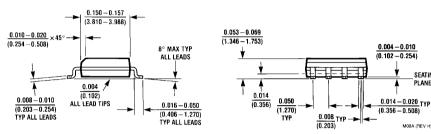

8-Pin MSOP **NS Package Number MUA08A**

14-Pin SOIC NS Package Number M14A

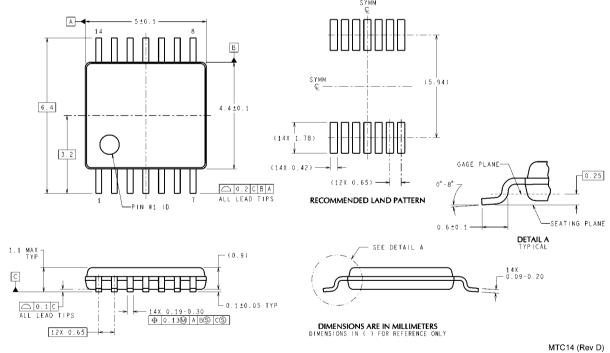

14-Pin TSSOP NS Package Number MTC14

# **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560