### **General Description**

The MAX13174E contains six pin-selectable, multiprotocol cable termination networks. Each network is capable of terminating V.11 (RS-422, RS-530, RS-530A, RS-449, V.36, and X.21) with a  $100\Omega$  differential load, V.35 with a T-network load, or V.28 (RS-232) and V.10 (RS-423) with an open-circuit load for use with transceivers having on-chip termination. The termination protocol can be selected by the serial interface cable wiring or by pin control. The MAX13174E replaces discrete resistor termination networks and expensive relays required for multiprotocol termination, saving space and cost.

The MAX13174E terminator is ideal to form a complete +5V cable- or pin-selectable multiprotocol DCE/DTE interface port when used with the MAX13170E and MAX13172E transceiver ICs. The MAX13174E terminator can use the VEE power generated by the MAX13170E charge pump, simplifying system design. The MAX13174E/MAX13170E/MAX13172E are pinfor-pin compatible with the MXL1344A/MXL1543/ MXL1544/MAX3175.

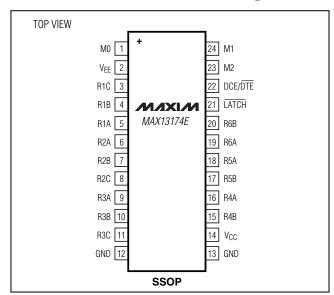

The MAX13174E is available in a 24-pin SSOP package and is specified for the 0°C to +70°C commercial temperature range.

#### **Features**

- ♦ Supports V.11 and V.35 Termination

- **♦ Pin-Selectable Termination**

- **♦ Pin-Selectable DCE/DTE Support**

- **♦** Replaces Discrete Resistor Termination Networks and Expensive Relays

- ♦ Available in 24-Pin SSOP Package

- **♦** Certified TBR-1 and TBR-2-Compliant Chipset (NET1 and NET2)—Pending Completion of Testing

### **Applications**

Data Networking PCI Cards

CSU and DSU Telecommunication Equipment

**Data Routers Data Switches**

### **Ordering Information**

| PART          | TEMP RANGE   | PIN-PACKAGE |

|---------------|--------------|-------------|

| MAX13174ECAG+ | 0°C to +70°C | 24 SSOP     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration appears at end of data sheet.

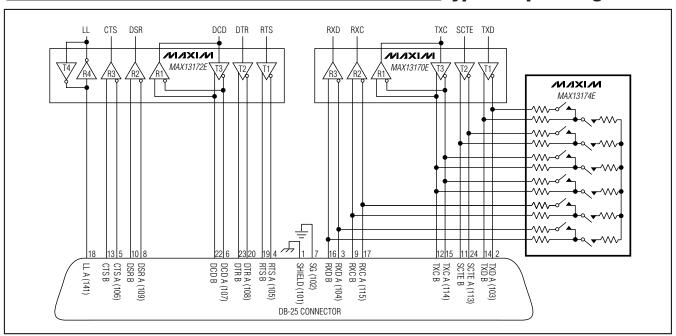

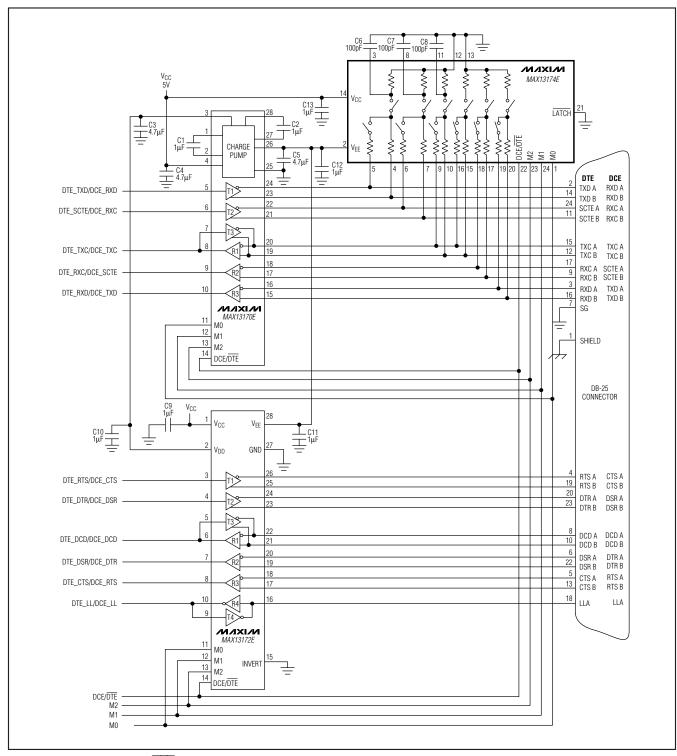

### Typical Operating Circuit

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages to GND, unless otherwise noted.) | R_    |

|------------------------------------------------|-------|

| Supply Voltages                                | R_    |

| V <sub>CC</sub> 0.3V to +6V                    | Cont  |

| VEE+0.3V to -7.1V                              | 24    |

| Logic-Input Voltages                           | Junc  |

| M0, M1, M2, DCE/DTE, LATCH0.3V to +6V          | 24    |

| Termination Network Inputs                     | Junc  |

| R_A, R_B, R_C15V to +15V                       | 24    |

| R_A to R_B (high-impedance state)±14V          | Ope   |

| R_A to R_B±6V                                  | Junc  |

| R_C to R_B (high-impedance state)±3V           | Stora |

| · -                                            | Lead  |

| R_A to R_C                                            | ±3V             |

|-------------------------------------------------------|-----------------|

| R_C to R_A (high-impedance state)                     | ±14V            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

| 24-Pin SSOP (derate 14.9mW/°C above +70°              | °C)1196mW       |

| Junction-to-Case Thermal Resistance (θJC) (No         | ote 1)          |

| 24-Pin SSOP                                           | 24.6°C/W        |

| Junction-to-Ambient Thermal Resistance (θJA)          | (Note 1)        |

| 24-Pin SSOP                                           |                 |

| Operating Temperature Range                           | 0°C to +70°C    |

| Junction Temperature                                  | +150°C          |

| Storage Temperature Range                             | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C          |

|                                                       |                 |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

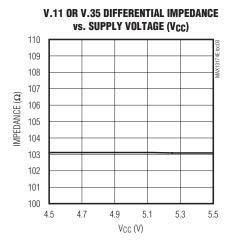

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +4.5V \text{ to } +5.5V, V_{EE} = -4V \text{ to } -7.1V, T_A = 0^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C, V_{CC} = +5V, V_{EE} = -5V, V_{CC} = +5V, V_{CC} = +$

| PARAMETER                                | SYMBOL          | CONDITIONS                                                                                         | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>CC</sub> Operating Range          | Vcc             |                                                                                                    | 4.5  | 5    | 5.5  | V     |

| VEE Operating Range                      | VEE             |                                                                                                    | -7.1 | -5   | -4   | V     |

| V <sub>CC</sub> POR Rising Threshold     |                 |                                                                                                    | 1    | 1.88 | 2.75 | V     |

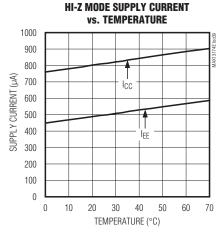

| V <sub>CC</sub> Supply Current           | Icc             | All inputs connected to GND or V <sub>CC</sub> , except no-cable mode                              |      | 2.2  | 6.15 | mA    |

|                                          | ICC_NOCAB       | V <sub>EE</sub> = 0V, M[x] = 1111 (Note 3)                                                         |      | 1.34 | 2.85 |       |

| V <sub>EE</sub> Supply Current           | I <sub>EE</sub> | All inputs connected to GND or V <sub>CC</sub> , except no-cable mode                              | -3.5 | -1   |      | mA    |

| TERMINATOR INPUTS                        |                 |                                                                                                    |      |      |      |       |

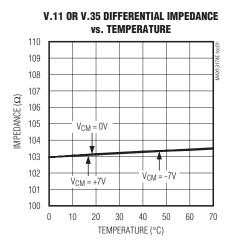

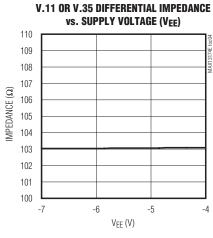

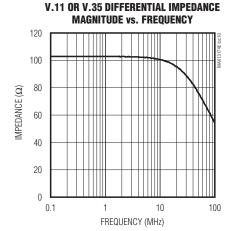

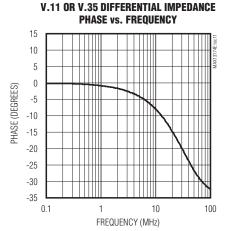

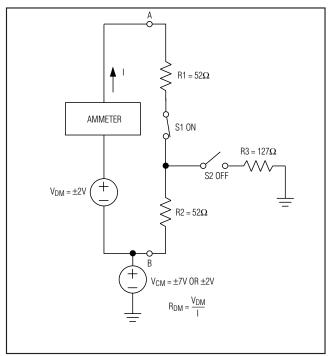

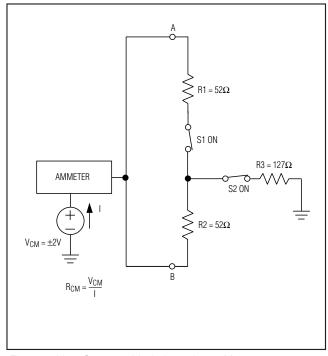

| Differential-Mode Impedance<br>V.35 Mode |                 | -2V ≤ V <sub>CM</sub> ≤ +2V, all channels (Figure 1)                                               | 90   | 104  | 110  | Ω     |

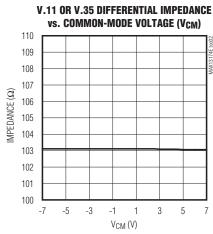

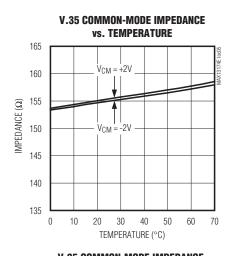

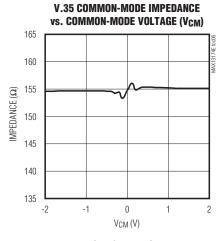

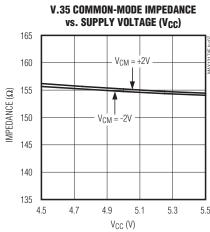

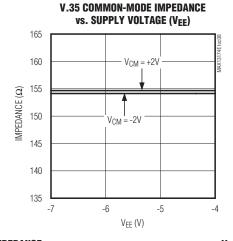

| Common-Mode Impedance<br>V.35 Mode       |                 | -2V ≤ V <sub>CM</sub> ≤ +2V, all channels (Figure 2)                                               | 135  | 153  | 165  | Ω     |

| Differential-Mode Impedance              |                 | $-7V \le V_{CM} \le +7V$ , all channels, except nocable mode (Figure 1)                            | 100  | 104  | 110  |       |

| V.11 Mode                                |                 | $-7V \le V_{CM} \le +7V$ , all channels, no-cable mode, $V_{EE} = 0V$ , $V_{AB} \le 2V$ (Figure 1) |      | 115  |      | Ω     |

| High-Impedance Leakage<br>Current        | IZ              | -15V ≤ V <sub>R_A</sub> ≤ +15V                                                                     | -50  |      | +50  | μΑ    |

| Differential Path Enable Time            |                 |                                                                                                    |      | 50   |      | μs    |

| Differential Path Disable Time           |                 |                                                                                                    |      | 300  |      | μs    |

| Common-Mode Path Enable Time             |                 |                                                                                                    |      | 12   |      | μs    |

| Common-Mode Path Disable                 |                 |                                                                                                    |      | 2    |      | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +4.5V \text{ to } +5.5V, V_{EE} = -4V \text{ to } -7.1V, T_A = 0^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C, V_{CC} = +5V, V_{EE} = -5V, V_{EE} = -$

| PARAMETER                                 | ER SYMBOL CONDITIONS |                                          |                            |     | MAX                        | UNITS |  |  |  |

|-------------------------------------------|----------------------|------------------------------------------|----------------------------|-----|----------------------------|-------|--|--|--|

| LOGIC INPUTS (M0, M1, M2, LATCH, DCE/DTE) |                      |                                          |                            |     |                            |       |  |  |  |

| Input High Voltage                        | V <sub>IH</sub>      |                                          | 0.66 x<br>V <sub>C</sub> C |     |                            | V     |  |  |  |

| Input Low Voltage                         | VIL                  |                                          |                            |     | 0.33 x<br>V <sub>C</sub> C | V     |  |  |  |

| Logic Input Current                       | I <sub>IN</sub>      | V <sub>IN</sub> = V <sub>CC</sub> or GND | -1                         |     | +1                         | μΑ    |  |  |  |

| ESD PROTECTION                            |                      |                                          |                            |     |                            |       |  |  |  |

|                                           |                      | Human Body Model                         |                            | ±15 |                            |       |  |  |  |

| R_A, R_B to GND                           |                      | Air Gap Discharge IEC 61000-4-2          |                            | ±10 |                            | kV    |  |  |  |

|                                           |                      | Contact Discharge IEC 61000-4-2          |                            | ±6  |                            |       |  |  |  |

| All Other Pins                            |                      | Human Body Model                         | ±2                         |     |                            | kV    |  |  |  |

Note 2: All parameters tested at a single temperature. Specifications over temperature are guaranteed by design.

Note 3: M[x] is the input bus DCE/DTE, M2, M1, M0.

## Typical Operating Characteristics

$(V_{CC} = +5V, V_{EE} = -5V, T_A = +25^{\circ}C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(VCC = +5V, VEE = -5V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN    | NAME    | FUNCTION                                                                                                                                                                              |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | MO      | Mode-Select Input (Table 1)                                                                                                                                                           |

| 2      | VEE     | Negative Supply Voltage (typically connected to VEE of MAX13170E). Bypass to GND with a 0.1µF capacitor.                                                                              |

| 3      | R1C     | Load 1, Center Tap                                                                                                                                                                    |

| 4      | R1B     | Load 1, Node B                                                                                                                                                                        |

| 5      | R1A     | Load 1, Node A                                                                                                                                                                        |

| 6      | R2A     | Load 2, Node A                                                                                                                                                                        |

| 7      | R2B     | Load 2, Node B                                                                                                                                                                        |

| 8      | R2C     | Load 2, Center Tap                                                                                                                                                                    |

| 9      | R3A     | Load 3, Node A                                                                                                                                                                        |

| 10     | R3B     | Load 3, Node B                                                                                                                                                                        |

| 11     | R3C     | Load 3, Center Tap                                                                                                                                                                    |

| 12, 13 | GND     | Ground                                                                                                                                                                                |

| 14     | Vcc     | +5V Supply Voltage. Bypass to GND with a 0.1µF capacitor.                                                                                                                             |

| 15     | R4B     | Load 4, Node B                                                                                                                                                                        |

| 16     | R4A     | Load 4, Node A                                                                                                                                                                        |

| 17     | R5B     | Load 5, Node B                                                                                                                                                                        |

| 18     | R5A     | Load 5, Node A                                                                                                                                                                        |

| 19     | R6A     | Load 6, Node A                                                                                                                                                                        |

| 20     | R6B     | Load 6, Node B                                                                                                                                                                        |

| 21     | LATCH   | Latch Signal Input. When $\overline{\text{LATCH}}$ is low, the input latches are transparent. When $\overline{\text{LATCH}}$ is high, the data at the mode-select inputs are latched. |

| 22     | DCE/DTE | DCE/DTE Mode-Select Input (Table 1)                                                                                                                                                   |

| 23     | M2      | Mode-Select Input (Table 1)                                                                                                                                                           |

| 24     | M1      | Mode-Select Input (Table 1)                                                                                                                                                           |

### **Detailed Description**

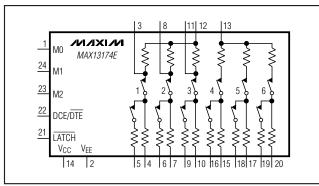

The MAX13174E contains six pin-selectable multiprotocol cable termination networks (Figure 3). Each network is capable of terminating V.11 (RS-422, RS-530, RS-530A, RS-449, V.36, and X.21) with a  $100\Omega$  differential load, V.35 with a T-network load, or V.28 (RS-232) and V.10 (RS-423) with an open-circuit load for use with transceivers that have on-chip termination. The termination protocol can be selected by the serial interface cable wiring or by pin control. The MAX13174E replaces discrete resistor termination networks and expensive relays required for multiprotocol termination, saving space and cost.

The MAX13174E terminator is designed to form a complete +5V cable- or pin-selectable multiprotocol DCE/DTE interface port when used with the MAX13170E and MAX13172E transceivers. The MAX13174E terminator

can use the VEE power generated by the MAX13170E charge pump, simplifying system design. The MAX13174E/MAX13170E/MAX13172E are functionally compatible with the MXL1344A/MXL1543/MXL1544/MAX3175.

#### **Termination Modes**

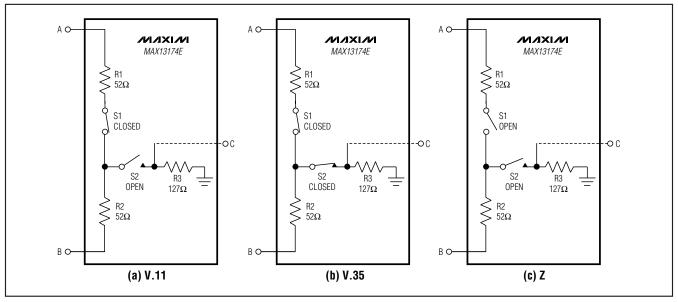

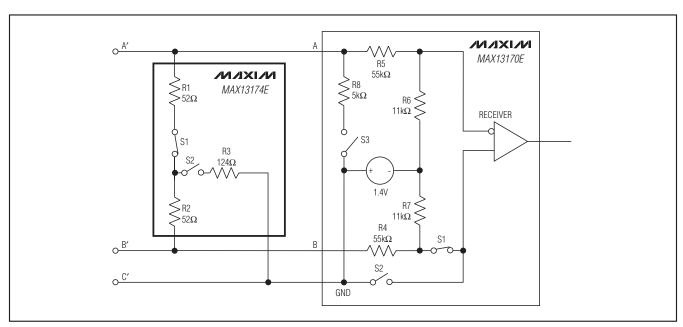

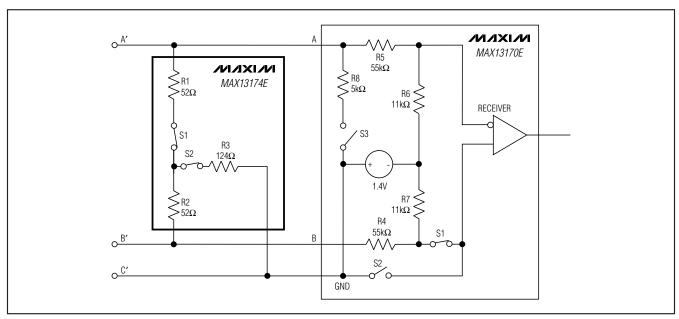

The termination networks in the MAX13174E can be set to one of three modes: V.11, V.35, or high impedance. As shown in Figure 4, in V.11 mode, switch S1 is closed and switch S2 is open, presenting 104 $\Omega$  across terminals A and B. In V.35 mode, switches S1 and S2 are both closed, presenting a T-network with 104 $\Omega$  differential impedance and 153 $\Omega$  common-mode impedance. In high-impedance mode, switches S1 and S2 are both open, presenting a high impedance across terminals A and B suitable for V.28 and V.10 modes.

Figure 1, V.11 or V.35 Differential Impedance Measurement

Figure 3. Block Diagram

The state of the MAX13174E's mode-select pins—M0, M1, M2, and DCE/DTE—determines the mode of each of the six termination networks. Table 1 shows a cross-reference of termination mode and select pin state for each of the six termination networks within the MAX13174E.

#### **No-Cable Mode**

The MAX13174E enters no-cable mode when the mode-select inputs—M0, M1, and M2—are connected high. In no-cable mode, all six termination networks are placed in V.11 mode, with S1 closed and S2 open (Figure 4).

Figure 2. V.35 Common-Mode Impedance Measurement

### \_Applications Information

Older multiprotocol interface termination circuits have been constructed using expensive relays with discrete resistors, custom cables with built-in termination, or complex circuit-board configurations to route signals to the correct termination. The MAX13174E provides a simple solution to this termination problem. All required termination configurations are easily cable- or pinselectable using the four mode-control input pins (M0, M1, M2, and DCE/DTE).

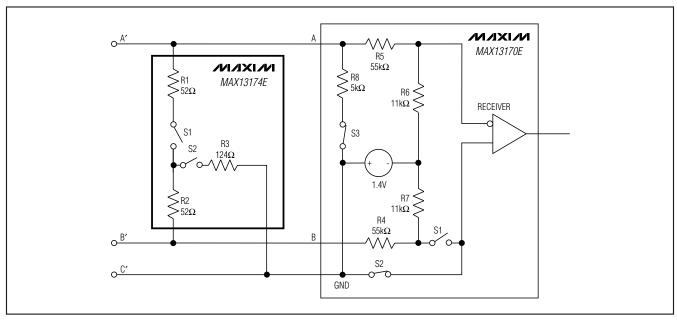

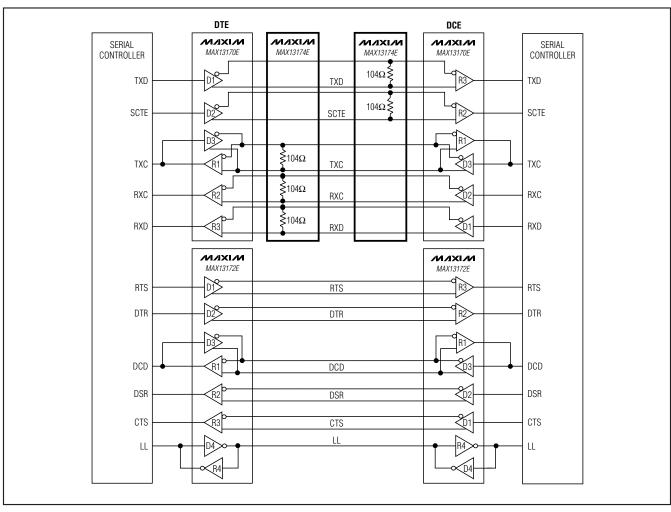

#### Using the MAX13174E in a Multiprotocol Serial Interface

The MAX13174E terminator is designed to form a complete +5V cable- or pin-selectable multiprotocol DCE/DTE interface port when used with the MAX13170E/MAX13172E differential drivers/receivers. The MAX13174E terminator is designed to use the VEE power generated by the MAX13171E's charge pump and meets all data sheet specifications when connected as illustrated in Figure 5. The mode-selection tables of all three devices are identical, allowing the M0, M1, M2, and DCE/DTE pins of each device to be connected to a single 4-wire control bus. The MAX13170E and MAX13172E provide internal pullups for the four lines,

**Table 1. Termination Mode Select Table**

| PROTOCOL    | DCE/ DTE | M2 | М1 | МО | R1   | R2   | R3   | R4   | R5   | R6   |

|-------------|----------|----|----|----|------|------|------|------|------|------|

| V.10/RS-423 | 0        | 0  | 0  | 0  | Z    | Z    | Z    | Z    | Z    | Z    |

| RS-530A     | 0        | 0  | 0  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

| RS-530      | 0        | 0  | 1  | 0  | Z    | Z    | Ζ    | V.11 | V.11 | V.11 |

| X.21        | 0        | 0  | 1  | 1  | Z    | Z    | Ζ    | V.11 | V.11 | V.11 |

| V.35        | 0        | 1  | 0  | 0  | V.35 | V.35 | Ζ    | V.35 | V.35 | V.35 |

| RS-449/V.36 | 0        | 1  | 0  | 1  | Z    | Z    | Ζ    | V.11 | V.11 | V.11 |

| V.28/RS-232 | 0        | 1  | 1  | 0  | Z    | Ζ    | Z    | Ζ    | Z    | Z    |

| No Cable    | 0        | 1  | 1  | 1  | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 |

| V.10/RS-423 | 1        | 0  | 0  | 0  | Z    | Z    | Ζ    | Z    | Z    | Z    |

| RS-530A     | 1        | 0  | 0  | 1  | Z    | Z    | Ζ    | Z    | V.11 | V.11 |

| RS-530      | 1        | 0  | 1  | 0  | Z    | Z    | Ζ    | Z    | V.11 | V.11 |

| X.21        | 1        | 0  | 1  | 1  | Z    | Z    | Z    | Z    | V.11 | V.11 |

| V.35        | 1        | 1  | 0  | 0  | V.35 | V.35 | V.35 | Z    | V.35 | V.35 |

| RS-449/V.36 | 1        | 1  | 0  | 1  | Z    | Z    | Ζ    | Z    | V.11 | V.11 |

| V.28/RS-232 | 1        | 1  | 1  | 0  | Z    | Z    | Ζ    | Z    | Z    | Z    |

| No Cable    | 1        | 1  | 1  | 1  | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 |

Note: Z indicates high impedance, 1 = high, and 0 = low. Z, V.11, and V.35 refer to termination modes (Figure 4).

Figure 4. Termination Modes

forcing them to the logic-high state if they are not grounded. This allows interface-mode configuration by simply strapping the appropriate pins to ground in the interconnect cable.

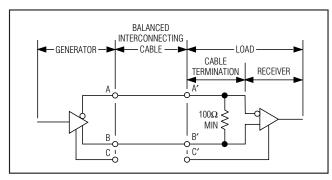

#### V.11 Termination

A standard V.11 interface is shown in Figure 6. For high-speed data transmission, the V.11 specification recommends terminating the cable at the receiver with a  $100\Omega$  (min) resistor. The resistor, although not required, prevents reflections from corrupting transmitted data.

Figure 5. Multiprotocol DCE/DTE Port

· \_\_\_\_\_\_\_\_\_\_\_//////

Figure 6. Typical V.11 Interface

In Figure 7, the MAX13174E is used to terminate the V.11 receiver on the MAX13170E. Internal to the MAX13174E, S1 is closed and S2 is open to present a  $104\Omega$  typical differential resistance and high-Z common-mode impedance. The MAX13170E's internal V.28 termination is disabled by opening S3.

The V.11 specification allows for signals with common-mode variations of  $\pm 7V$  and differential signal amplitudes from 2V to 6V. The MAX13174E maintains termination impedance between  $100\Omega$  and  $110\Omega$  over these conditions.

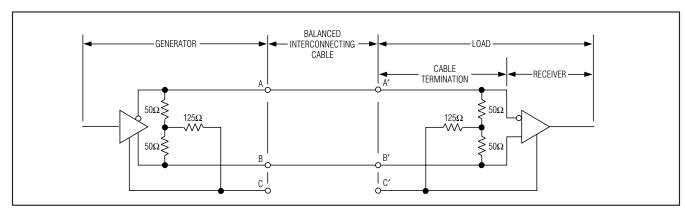

#### **V.35 Termination**

Figure 8 shows a standard V.35 interface. The generator and the load must both present a 100  $\Omega \pm 10\Omega$  differential

impedance and a  $150\Omega$  ± $15\Omega$  common-mode impedance. The V.35 driver generates a current output (±11mA, typ) that develops an output voltage between 440mV and 660mV across the load termination networks.

In Figure 9, the MAX13174E is used to implement the resistive T-network that is needed to properly terminate the V.35 receiver. Internal to the MAX13174E, S1 and S2 are closed to connect the T-network resistors to the circuit.

The V.35 specification allows for ±4V of ground difference between the V.35 generator and V.35 load. The MAX13174E maintains correct termination impedance over these conditions.

#### V.35 EMI reduction

For applications where EMI reduction is especially important, the MAX13174E termination networks provide a pin for shunting common-mode driver currents to GND. Mismatches between the driver A and B output propagation delays can create a common-mode disturbance on the cable. This common-mode energy can be shunted to GND by placing a 100pF capacitor to GND from the center tap of the T-network termination (R1C, R2C, and R3C as shown in Figure 5).

#### V.28 Termination

Most industry-standard V.28 receivers (including the MAX13170E and MAX13172E) do not require external termination because the receiver includes an internal  $5k\Omega$  termination resistor. When the MAX13174E is

Figure 7. V.11 Termination and Internal Resistance Networks

Figure 8. Typical V.35 Interface

Figure 9. V.35 Termination and Internal Resistance Networks

placed in V.28 mode, all six of the termination networks are placed in a high-Z mode. In high-Z mode, the MAX13174E termination networks do not interfere with the MAX13170E's internal  $5k\Omega$  termination.

In Figure 10, the MAX13174E and MAX13170E are placed in V.28 mode. Switches S1 and S2 are opened on the MAX13174E to place the network in high-Z mode. Switch S3 is closed on the MAX13170E to enable the  $5\mathrm{k}\Omega$  terminating resistor.

#### A Complete X.21 Interface

A complete DTE-to-DCE interface operating in X.21 mode is shown in Figure 11. The MAX13174E terminates the V.11 clock and data signals. The MAX13170E carries the clock and data signals, and the MAX13172E carries the control signals. The control signals generally do not require external termination.

#### **ESD Protection**

ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The differential resistors

Figure 10. V.28 Termination and Internal Resistance Networks

have extra protection against static electricity. Maxim's engineers have developed state-of-the-art structures to protect these pins against an ESD of ±15kV (Human Body Model) without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, the MAX13174E keeps working without latchup or damage. ESD protection can be tested in various ways. The *Electrical Characteristics* table shows the limits, and each device is characterized for protection to the following methods:

- Human Body Model

- Contact Method specified in IEC 61000-4-2

- Air Gap Discharge Method specified in IEC 61000-4-2

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

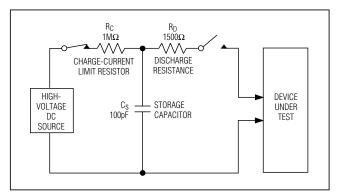

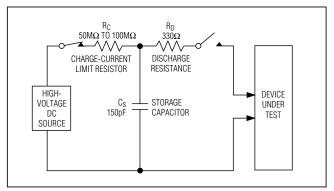

#### **Human Body Model**

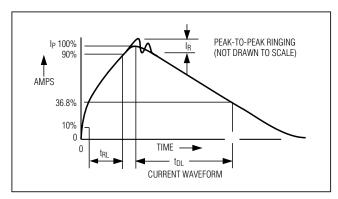

Figure 12a shows the Human Body Model, and Figure 12b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5 \mathrm{k}\Omega$  resistor.

#### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and the performance of finished equipment. However, it does not specifically refer to integrated circuits. The MAX13174E helps equipment designs to meet IEC 61000-4-2 without the need for additional ESD-protection components.

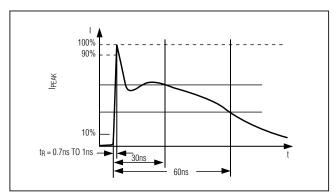

The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Figure 12c shows the IEC 61000-4-2 model, and Figure 12d shows the current waveform for the IEC 61000-4-2 ESD Contact Discharge test.

### Compliance Testing

A European Standard EN 45001 test report for the MAX13170E, MAX13172E, and MAX13174E chipset will be available from Maxim upon completion of testing. Contact Maxim Quality Assurance for a copy of the report.

Figure 11. DTE-to-DCE X.21 Interface

Figure 12a. Human Body ESD Test Model

Figure 12c. IEC 61000-4-2 ESD Test Model

Figure 12b. Human Body Current Waveform

Figure 12d. IEC 61000-4-2 ESD Generator Current Waveform

### **Pin Configuration**

\_Chip Information

PROCESS: BICMOS

### \_Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |  |  |

|--------------|--------------|----------------|--|--|

| 24 SSOP      | A24+3        | <u>21-0056</u> |  |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX13174ECAG+ MAX13174ECAG+T