# 300MHz to 450MHz Low-Power, Crystal-Based +10dBm ASK/FSK Transmitter

#### **General Description**

The MAX1479 crystal-referenced phase-locked-loop (PLL) VHF/UHF transmitter is designed to transmit ASK, OOK, and FSK data in the 300MHz to 450MHz frequency range. The MAX1479 supports data rates up to 100kbps in ASK mode and 20kbps in FSK mode (both Manchester coded). The device provides an adjustable output power of more than +10dBm into a  $50\Omega$  load. The crystal-based architecture of the MAX1479 eliminates many of the common problems of SAW-based transmitters by providing greater modulation depth, faster frequency settling, higher tolerance of the transmit frequency, and reduced temperature dependence. These improvements enable better overall receiver performance when using the MAX1479 together with a superheterodyne receiver such as the MAX1470, MAX1471, MAX1473, or MAX7033.

The MAX1479 is available in a 16-pin TQFN package (3mm x 3mm) and is specified for the automotive temperature range from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### **Applications**

- Remote Keyless Entry

- Tire Pressure Monitoring

- Security Systems

- Radio-Controlled Toys

- Wireless Game Consoles

- Wireless Computer Peripherals

- Wireless Sensors

- RF Remote Controls

- Garage Door Openers

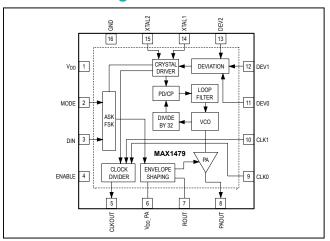

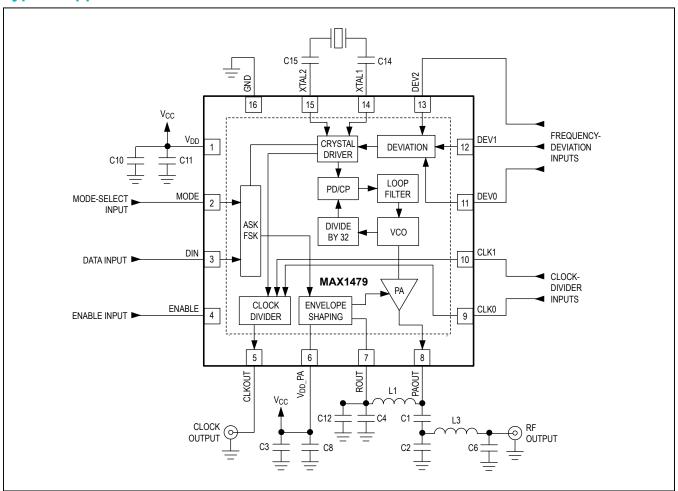

#### **Functional Diagram**

#### **Features**

- ETSI-Compliant EN300 220

- +2.1V to +3.6V Single-Supply Operation

- Supports ASK, OOK, and FSK Modulations

- Adjustable FSK Shift

- +10dBm Output Power into 50Ω Load

- Low Supply Current (6.7mA in ASK Mode, and 10.5mA in FSK Mode)

- Uses Small Low-Cost Crystal

- Small 16-Pin TQFN Package

- Fast-On Oscillator—200µs Startup Time

- Programmable Clock Output

# **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX1479ATE+ | -40°C to +125°C | 16 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Typical Application Circuit appears at end of data sheet.

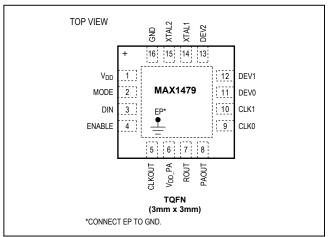

# **Pin Configuration**

<sup>\*</sup>EP = Exposed pad.

# 300MHz to 450MHz Low-Power, Crystal-Based +10dBm ASK/FSK Transmitter

# **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to +4V                     | Operating Temperature Range40°C to +125°C |

|-------------------------------------------------------|-------------------------------------------|

| All Other Pins to GND0.3V to (V <sub>DD</sub> + 0.3V) | Junction Temperature+150°C                |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Storage Temperature Range60°C to +150°C   |

| 16-Pin TQFN (derate 14.7mW/°C above +70°C)1176.5mW    | Lead Temperature (soldering, 10s)+300°C   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DC Electrical Characteristics (Typical Application Circuit, all RF inputs and outputs are referenced to 50Ω,  $V_{DD}$  = 2.1V to 3.6V,  $V_{ENABLE}$  =  $V_{DD}$ .  $T_A$  = -40°C to +125°C, unless otherwise noted. Min and Max values are 100% tested at  $T_A$  = +125°C and are guaranteed by design and characterization over temperature, unless otherwise noted. Typical values are at  $V_{DD} = +2.7V$ ,  $T_A = +25$ °C, unless otherwise noted.) (Note 1)

| PARAMETER               | SYMBOL                   | со                                    | NDITIONS                              | MIN                             | TYP  | MAX  | UNITS |    |

|-------------------------|--------------------------|---------------------------------------|---------------------------------------|---------------------------------|------|------|-------|----|

| Supply Voltage          | V <sub>DD</sub>          |                                       |                                       | 2.1                             |      | 3.6  | V     |    |

|                         |                          | PA off, V <sub>DIN</sub> at           | f <sub>RF</sub> = 315MHz              |                                 | 2.9  | 4.3  |       |    |

|                         |                          | 0% duty cycle<br>(ASK or FSK)         | f <sub>RF</sub> = 433MHz              |                                 | 3.3  | 4.8  |       |    |

| Supply Current          | I <sub>DD</sub>          | V <sub>DIN</sub> at 50%               | f <sub>RF</sub> = 315MHz              |                                 | 6.7  | 10.7 | mA    |    |

|                         |                          | duty cycle (ASK)<br>(Notes 2, 3)      | f <sub>RF</sub> = 433MHz              |                                 | 7.3  | 11.4 | -     |    |

|                         | V <sub>DIN</sub> at 100% | f <sub>RF</sub> = 315MHz              |                                       | 10.5                            | 17.1 |      |       |    |

|                         |                          | duty cycle (FSK)                      | f <sub>RF</sub> = 433MHz (Note 3)     |                                 | 11.4 | 18.1 |       |    |

|                         | I <sub>STDBY</sub>       | V <sub>ENABLE</sub> < V <sub>IL</sub> | T <sub>A</sub> = +25°C                |                                 | 0.2  |      |       |    |

| Standby Current         |                          |                                       | V <sub>ENABLE</sub> < V <sub>IL</sub> | T <sub>A</sub> < +85°C (Note 3) |      | 120  | 300   | nA |

|                         |                          |                                       | T <sub>A</sub> < +125°C               |                                 | 700  | 1600 | 1     |    |

| DIGITAL INPUTS AND OUTP | UTS                      |                                       |                                       |                                 |      |      |       |    |

| Data Input High         | V <sub>IH</sub>          |                                       |                                       | V <sub>DD</sub> -<br>0.25       |      |      | V     |    |

| Data Input Low          | V <sub>IL</sub>          |                                       |                                       |                                 |      | 0.25 | V     |    |

| Maximum Input Current   | I <sub>IN</sub>          |                                       |                                       |                                 | 20   |      | μA    |    |

| Output Voltage High     | V <sub>OH</sub>          | CLKOUT, load = 10kΩ    10pF (Note 3)  |                                       | V <sub>DD</sub> -<br>0.25       |      |      | V     |    |

| Output Voltage Low      | V <sub>OL</sub>          | CLKOUT, load = 10kΩ    10pF (Note 3)  |                                       |                                 |      | 0.25 | V     |    |

Maxim Integrated | 2 www.maximintegrated.com

#### **AC Electrical Characteristics**

(Typical Application Circuit, all RF inputs and outputs are referenced to  $50\Omega$ ,  $V_{DD}$  = 2.1V to 3.6V,  $V_{ENABLE}$  =  $V_{DD}$ .  $T_A$  = -40°C to  $+125^{\circ}$ C, unless otherwise noted. Min and Max values are 100% tested at  $T_A$  =  $+125^{\circ}$ C and are guaranteed by design and characterization over temperature, unless otherwise noted. Typical values are at  $V_{DD}$  = +2.7V,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                        | SYMBOL                        | cc                                       | ONDITIONS                    | MIN | TYP                  | MAX  | UNITS          |  |

|----------------------------------|-------------------------------|------------------------------------------|------------------------------|-----|----------------------|------|----------------|--|

| SYSTEM PERFORMANCE               |                               |                                          |                              |     |                      |      |                |  |

| Frequency Range                  | f <sub>RF</sub>               |                                          |                              | 300 |                      | 450  | MHz            |  |

| Turn-On Time (Note 4)            | 4                             | Settle to within 50kHz                   |                              |     | 200                  |      |                |  |

| rum-on time (Note 4)             | ton                           | Settle to within 5                       | ikHz                         |     | 350                  |      | μs             |  |

| Maximum Data Rate (Note 3)       |                               | ASK mode (Man                            | chester coded)               |     | 100                  |      | kbps           |  |

| Maximum Data Nate (Note 3)       |                               | FSK mode (Man                            | chester coded)               |     | 20                   |      | Kups           |  |

| Maximum FSK Frequency            |                               | DEV[2:0] = 111                           | f <sub>RF</sub> = 315MHz     |     | 55                   |      | kHz            |  |

| Deviation                        |                               | (Note 5)                                 | f <sub>RF</sub> = 433MHz     |     | 80                   |      | NI IZ          |  |

|                                  |                               | T <sub>A</sub> = +25°C, V <sub>DI</sub>  | <sub>D</sub> = +2.7V         | 6.8 | 10                   | 12.0 |                |  |

| Output Power                     | P <sub>OUT</sub>              | T <sub>A</sub> = +125°C, V <sub>[</sub>  | <sub>DD</sub> = +2.1V        | 2.7 | 5.3                  |      | dBm            |  |

|                                  |                               | T <sub>A</sub> = -40°C, V <sub>DD</sub>  | ) = +3.6V                    |     | 12.2                 | 16.1 | ]              |  |

| Transmit Efficiency with CW Tone |                               | f <sub>RF</sub> = 315MHz                 |                              |     | 35                   |      | 0/             |  |

| (Note 6)                         |                               | f <sub>RF</sub> = 433MHz                 |                              | 34  |                      |      | <del>-</del> % |  |

| Transmit Efficiency at 50% Duty  | ansmit Efficiency at 50% Duty |                                          | f <sub>RF</sub> = 315MHz     |     | 27                   |      | 0/             |  |

| Cycle                            |                               | f <sub>RF</sub> = 433MHz                 |                              |     | 25                   |      | - %            |  |

| PHASE-LOCKED-LOOP PERFOR         | MANCE                         |                                          |                              | '   | -                    |      | '              |  |

| VCO Gain                         | K <sub>VCO</sub>              |                                          |                              |     | 280                  |      | MHz/V          |  |

|                                  |                               | f <sub>OFFSET</sub> = 100kHz             |                              |     | -75                  |      |                |  |

| Dhara Nata                       |                               | f <sub>RF</sub> = 315MHz                 | f <sub>OFFSET</sub> = 1MHz   |     | -98                  |      | - ID - // L-   |  |

| Phase Noise                      |                               | f 400N4L                                 | f <sub>OFFSET</sub> = 100kHz |     | -74                  |      | dBc/Hz         |  |

|                                  |                               | $f_{RF} = 433MHz$ $f_{OFFSET} = 1MHz$    |                              | -98 |                      |      | 1              |  |

| Mariana Caria Harris             |                               | f <sub>RF</sub> = 315MHz                 |                              |     | -50                  |      | -ID-           |  |

| Maximum Carrier Harmonics        |                               | f <sub>RF</sub> = 433MHz                 |                              |     | -45                  |      | dBc            |  |

| Reference Spur                   |                               |                                          |                              |     | -40                  |      | dBc            |  |

| Loop Bandwidth                   | BW                            |                                          |                              |     | 300                  |      | kHz            |  |

| Crystal Frequency Range          | f <sub>XTAL</sub>             |                                          |                              |     | F <sub>RF</sub> /32  |      | MHz            |  |

| Crystal Tolerance                |                               |                                          |                              |     | 50                   |      | ppm            |  |

| Crystal Load Capacitance         | C <sub>LOAD</sub>             | (Note 7)                                 |                              | 4.5 |                      | pF   |                |  |

| Clock Output Frequency           |                               | Determined by CLK0 and CLK1; see Table 1 |                              |     | F <sub>XTAL</sub> /N |      | MHz            |  |

- Note 1: Supply current, output power, and efficiency are greatly dependent on board layout and PAOUT match.

- Note 2: 50% duty cycle at 10kHz ASK data (Manchester coded).

- Note 3: Guaranteed by design and characterization, not production tested.

- **Note 4:** V<sub>ENABLE</sub> = V<sub>IL</sub> to V<sub>ENABLE</sub> = V<sub>IH</sub>. f<sub>OFFSET</sub> is defined as the frequency deviation from the desired carrier frequency. **Note 5:** Dependent on crystal and PCB trace capacitance.

- Note 6:  $V_{ENABLE} > V_{IH}$ ,  $V_{DATA} > V_{IH}$ , Efficiency =  $P_{OUT}/(V_{DD} \times I_{DD})$ .

- Note 7: Dependent on PCB trace capacitance.

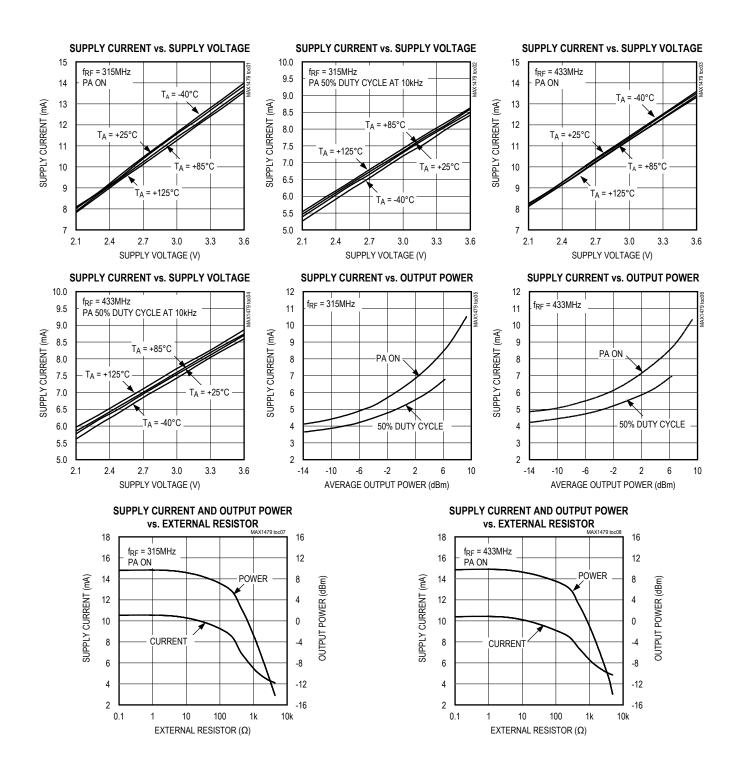

## **Typical Operating Characteristics**

(Typical Application Circuit, V<sub>DD</sub> = +2.7V, T<sub>A</sub> = +25°C, unless otherwise noted.)

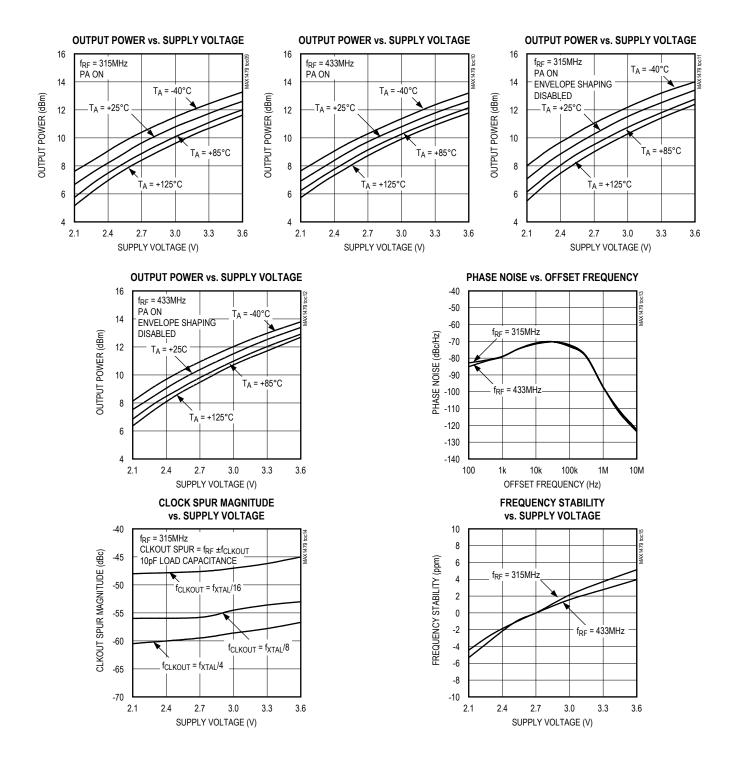

## **Typical Operating Characteristics (continued)**

(Typical Application Circuit, V<sub>DD</sub> = +2.7V, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### **Pin Description**

| PIN | NAME                | DESCRIPTION                                                                                                                                                        |

|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>DD</sub>     | Supply Voltage. Bypass to GND with a 10nF and 220pF capacitor as close to the pin as possible.                                                                     |

| 2   | MODE                | Mode Select. A logic low on MODE enables the device in ASK mode. A logic high on MODE enables the device in FSK mode.                                              |

| 3   | DIN                 | Data Input. Power amplifier is on when DIN is high in ASK mode. Frequency is high when DIN is high in FSK mode.                                                    |

| 4   | ENABLE              | Standby/Power-Up Input. A logic low on ENABLE sets the device in standby mode.                                                                                     |

| 5   | CLKOUT              | Buffered Clock Output. Programmable through CLK0 and CLK1. See Table 1.                                                                                            |

| 6   | V <sub>DD</sub> _PA | Power-Amplifier Supply Voltage. Bypass to GND with a 10nF and 220pF capacitor as close to the pin as possible.                                                     |

| 7   | ROUT                | Envelope-Shaping Output. ROUT controls the power-amplifier envelope rise and fall. Bypass to GND with a 680pF and 220pF capacitor as close to the pin as possible. |

| 8   | PAOUT               | Power-Amplifier Output. Requires a pullup inductor to the supply voltage, which can be part of the output-matching network to an antenna.                          |

| 9   | CLK0                | 1st Clock Divider Setting. See Table 1.                                                                                                                            |

| 10  | CLK1                | 2nd Clock Divider Setting. See Table 1.                                                                                                                            |

| 11  | DEV0                | 1st FSK Frequency-Deviation Setting. See Table 2.                                                                                                                  |

| 12  | DEV1                | 2nd FSK Frequency-Deviation Setting. See Table 2.                                                                                                                  |

| 13  | DEV2                | 3rd FSK Frequency-Deviation Setting. See Table 2.                                                                                                                  |

| 14  | XTAL1               | 1st Crystal Input. f <sub>RF</sub> = 32 x f <sub>XTAL</sub> .                                                                                                      |

| 15  | XTAL2               | 2nd Crystal Input. f <sub>RF</sub> = 32 x f <sub>XTAL</sub> .                                                                                                      |

| 16  | GND                 | Ground. Connect to system ground.                                                                                                                                  |

| _   | EP                  | Exposed Ground Pad. EP is the power amplifier's ground. It must be connected to PCB through a low-inductance path.                                                 |

### **Detailed Description**

The MAX1479 is a highly integrated ASK/FSK transmitter operating over the 300MHz to 450MHz frequency band. The device requires only a few external components to complete a transmitter solution. The MAX1479 includes a complete PLL and a highly efficient power amplifier. The device can be set into a 0.2nA low-power shutdown mode.

#### **Shutdown Mode**

ENABLE (pin 4) is internally pulled down with a 20µA current source. If it is left unconnected or pulled low, the MAX1479 goes into a low-power shutdown mode. In this mode, the supply current drops to 0.2nA. When ENABLE is high, the device is enabled and is ready for transmission after 200µs (frequency settles to within 50kHz).

The 200µs turn-on time of the MAX1479 is mostly dominated by the crystal oscillator startup time. Once the

oscillator is running, the 300kHz PLL bandwidth allows fast frequency recovery during power-amplifier toggling.

#### **Mode Selection**

MODE (pin 2) sets the MAX1479 in either ASK or FSK mode. When MODE is set low, the device operates as an ASK transmitter. If MODE is set high, the device operates as an FSK transmitter. In the ASK mode, the DIN pin controls the output of the power amplifier. A logic low on DIN turns off the PA, and a logic high turns on the PA. In the FSK mode, a logic low on the DIN pin is represented by the low FSK frequency, and a logic-high input is represented by the high FSK frequency. (The ASK carrier frequency and the lower FSK frequency are the same.) The deviation is proportional to the crystal load impedance and pulling capacitance. The maximum frequency deviation is 55kHz for  $f_{RF} = 315 \text{MHz}$  and 80 kHz for  $f_{RF} = 433 \text{MHz}$ .

www.maximintegrated.com Maxim Integrated | 6

#### **Clock Output**

The MAX1479 has a dedicated digital output pin for the frequency-divided crystal clock signal. This is to be used as the time base for a microprocessor. The frequency-division ratio is programmable through two digital input pins (CLK0, CLK1), and is defined in Table 1. The clock output is designed to drive a 3.5MHz CMOS rail-to-rail signal into a 10pF capacitive load.

#### **Envelope-Shaping Resistor**

The envelope-shaping resistor allows for a gentle turn-on/turn-off of the PA in ASK mode. This results in a smaller spectral width of the modulated PA output signal.

#### **Phase-Locked Loop**

The PLL block contains a phase detector, charge pump, integrated loop filter, VCO, asynchronous 32x clock divider, and crystal oscillator. The PLL requires no external components. The relationship between the carrier and crystal frequency is given by:

$$f_{XTAL} = f_{RF}/32$$

#### **Crystal Oscillator**

The crystal oscillator in the MAX1479 is designed to present a capacitance of approximately 3pF to ground from the XTAL1 and XTAL2 pins in ASK mode. In most cases, this corresponds to a 4.5pF load capacitance applied to the external crystal when typical PCB parasitics are added. In FSK mode, a percentage (defined by bits DEV0 to DEV2) of the 3pF internal crystal oscillator capacitance is removed for a logic 1 on the DIN pin to pull the transmit frequency. The frequency deviation is shown in Table 2. It is very important to use a crystal with a load capacitance that is equal to the capacitance of the MAX1479 crystal oscillator plus PCB parasitics. If very large FSK frequency deviations are desired, use a crystal with a larger motional capacitance and/or reduce PCB parasitic capacitances.

#### **Power Amplifier**

The PA of the MAX1479 is a high-efficiency, open-drain, switch-mode amplifier. With a proper output-matching network, the PA can drive a wide range of impedances, including small-loop PCB trace antennas and any  $50\Omega$  antennas. The output-matching network for a  $50\Omega$  antenna is shown in the *Typical Application Circuit*. The output-matching network suppresses the carrier harmonics and transforms the antenna impedance to an optimal impedance at PAOUT (pin 8), which is about  $250\Omega$ .

**Table 1. Clock Divider Settings**

| CLK1 | CLK0 | CLKOUT                |  |

|------|------|-----------------------|--|

| 0    | 0    | Logic 0               |  |

| 0    | 1    | F <sub>XTAL</sub> /4  |  |

| 1    | 0    | F <sub>XTAL</sub> /8  |  |

| 1    | 1    | f <sub>XTAL</sub> /16 |  |

**Table 2. Frequency-Deviation Settings**

| DEV2 | DEV1 | DEV0 | DEVIATION |  |

|------|------|------|-----------|--|

| 0    | 0    | 0    | 1/8 x max |  |

| 0    | 0    | 1    | 1/4 x max |  |

| 0    | 1    | 0    | 3/8 x max |  |

| 0    | 1    | 1    | 1/2 x max |  |

| 1    | 0    | 0    | 5/8 x max |  |

| 1    | 0    | 1    | 3/4 x max |  |

| 1    | 1    | 0    | 7/8 x max |  |

| 1    | 1    | 1    | Max       |  |

When the output-matching network is properly tuned, the power amplifier is highly efficient. The *Typical Application Circuit* delivers +10dBm at a supply voltage of +2.7V, and draws a supply current of 6.7mA for ASK/OOK operation (V<sub>DIN</sub> at 50% duty cycle) and 10.5mA for FSK operation. Thus, the overall efficiency at 100% duty cycle is 35%. The efficiency of the power amplifier itself is about 50%. An external resistor at ROUT sets the output power.

# **Applications Information**

#### Output Matching to 50Ω

When matched to a  $50\Omega$  system, the MAX1479 PA is capable of delivering more than +10dBm of output power at  $V_{DD}$  = 2.7V. The output of the PA is an open-drain transistor that requires external impedance matching and pullup inductance for proper biasing. The pullup inductance from PAOUT to  $V_{DD}$  serves three main purposes: It forms a resonant tank circuit with the capacitance of the PA output, provides biasing for the PA, and becomes a high-frequency choke to reduce the RF energy coupling into  $V_{DD}$ . Maximum efficiency is achieved when the PA drives a load of  $250\Omega$ . The recommended output-matching network topology is shown in the *Typical Application Circuit*.

# Output Matching to PCB Loop Antenna

In most applications, the MAX1479 power-amplifier output has to be impedance matched to a small-loop antenna. The antenna is usually fabricated out of a copper trace on a PCB in a rectangular, circular, or square pattern. The antenna has an impedance that consists of a lossy component and a radiative component. To achieve high radiating efficiency, the radiative component should be as high as possible, while minimizing the lossy component. In addition, the loop antenna has an inherent loop inductance associated with it (assuming the antenna is terminated to ground). For example, in a typical application, the radiative impedance is less than  $0.5\Omega,$  the lossy impedance is less than  $0.7\Omega,$  and the inductance is approximately 50nH to 100nH.

Table 3. Component Values for Typical Application Circuit

| COMPONENT | VALUE FOR<br>f <sub>RF</sub> = 433MHz | VALUE FOR<br>f <sub>RF</sub> = 315MHz |

|-----------|---------------------------------------|---------------------------------------|

| L1        | 22nH                                  | 27nH                                  |

| L3        | 18nH                                  | 22nH                                  |

| C1        | 6.8pF                                 | 15pF                                  |

| C2        | 10pF                                  | 22pF                                  |

| C3        | 10nF                                  | 10nF                                  |

| C4        | 680pF                                 | 680pF                                 |

| C6        | 6.8pF                                 | 15pF                                  |

| C8        | 220pF                                 | 220pF                                 |

| C10       | 10nF                                  | 10nF                                  |

| C11       | 220pF                                 | 220pF                                 |

| C12       | 220pF                                 | 220pF                                 |

| C14       | 100pF                                 | 100pF                                 |

| C15       | 100pF                                 | 100pF                                 |

The objective of the matching network is to match the power-amplifier output to the impedance of the small-loop antenna. The matching components thus tune out the loop inductance and transform the low radiative and resistive parts of the antenna into the much higher value of the PA output. This gives higher efficiency. The low radiative and lossy components of the small-loop antenna result in a higher Q matching network than the  $50\Omega$  network; thus, the harmonics are lower.

#### **Layout Considerations**

A properly designed PCB is an essential part of any RF/microwave circuit. On the power-amplifier output, use controlled-impedance lines and keep them as short as possible to minimize losses and radiation.

Keeping the traces short reduces parasitic inductance. Generally, 1in of PCB trace adds about 20nH of parasitic inductance. Parasitic inductance can have a dramatic effect on the effective inductance. For example, a 0.5in trace connecting a 100nH inductor adds an extra 10nH of inductance, or 10%.

To reduce the parasitic inductance, use wider traces and a solid ground or power plane below the signal traces. Using a solid ground plane can reduce the parasitic inductance from approximately 20nH/in to 7nH/in. Also, use low-inductance connections to ground on all GND pins and place decoupling capacitors close to all  $V_{\mbox{\scriptsize DD}}$  connections.

www.maximintegrated.com Maxim Integrated | 8

# **Typical Application Circuit**

## **Chip Information**

PROCESS: CMOS

# **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | DOCUMENT | LAND        |

|------------|---------|----------|-------------|

| TYPE       | CODE    | NO.      | PATTERN NO. |

| 16 TQFN-EP | T1633+2 | 21-0136  | 90-0030     |

www.maximintegrated.com Maxim Integrated | 9

# MAX1479

# 300MHz to 450MHz Low-Power, Crystal-Based +10dBm ASK/FSK Transmitter

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                   | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------------------------------|------------------|

| 0                  | 8/04             | Initial release                                                               | _                |

| 1                  | 6/09             | Changed part number in Ordering Information to lead free and corrected errors | 1, 2, 7          |

| 2                  | 2/15             | Revised Electrical Characteristics                                            | 2, 3             |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX1479ATE+ MAX1479ATE+T