### **General Description**

The MAX3877/MAX3878 are compact, low-power clock recovery and data retiming ICs for 2.488Gbps SONET/ SDH applications. The fully integrated phase-locked loop (PLL) recovers a synchronous clock signal from the serial NRZ data input, which is retimed by the recovered clock. An additional 2.488Gbps serial input is available for system loopback diagnostic testing, or this input can be connected to a 155MHz reference clock to maintain a valid clock output in the absence of data transitions. The MAX3877/MAX3878 provide vertical threshold and phase-adjust control to optimize system BER in DWDM applications.

These devices provide both loss-of-lock (LOL) and loss-of-signal (LOS) monitors. Differential CML outputs are provided for both clock and data signals on the MAX3877, and differential PECL outputs are provided for clock and data signals on the MAX3878.

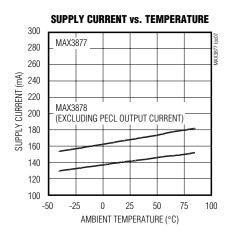

The MAX3877/MAX3878 are designed for both sectionregenerator and terminal-receiver applications in OC-48/STM-16 transmission systems. Their jitter performance exceeds all of the SONET/SDH specifications. These devices operate from a single +3.0V to +3.6V supply over a -40°C to +85°C temperature range. Typical power consumption is only 540mW with a +3.3V supply (MAX3878). They are available in a 32-pin TQFP-EP package with an exposed pad, as well as in die form.

## **Applications**

Long Haul and Metro Systems with Optical Amplification **DWDM Transmission Systems** SONET/SDH Receivers and Regenerators Add/Drop Multiplexers Digital Cross-Connects SONET/SDH Test Equipment

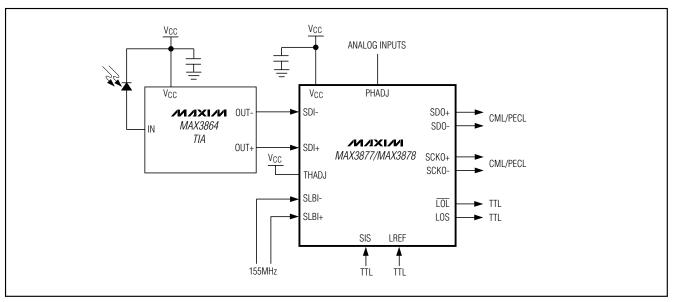

Typical Operating Circuit appears at end of data sheet.

### **Features**

- ♦ Exceeds ANSI, ITU, and Bellcore SONET/SDH **Specifications**

- ♦ Adjustable Input Threshold (±180mV)

- ◆ 10mVp-p to 1.2Vp-p Differential Input Range

- **♦** 540mW Power Dissipation (at +3.3V)

- ♦ Fully Integrated Clock Recovery and Data Retiming

- ♦ Optional Holdover Capability (Using External Reference Clock)

- ♦ 0.003UIRMS Clock Jitter Generation

- **♦** Tolerates >2000 Consecutive Identical Digits

- ♦ Additional 2.488Gbps Input for Diagnostic **Loopback Testing**

- ♦ Differential PECL or CML Data and Clock Outputs

- ♦ Loss-of-Signal Indicator

- ♦ Loss-of-Lock Indicator

## **Ordering Information**

| PART          | TEMP. RANGE    | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX3877EHJ    | -40°C to +85°C | 32 TQFP-EP* |

| MAX3877E/D*** | -40°C to +85°C | DICE**      |

| MAX3878EHJ    | -40°C to +85°C | 32 TQFP-EP* |

| MAX3878E/D*** | -40°C to +85°C | DICE**      |

<sup>\*</sup> Exposed pad

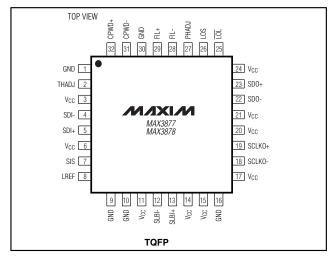

## Pin Configuration

<sup>\*\*</sup> Dice are designed to operate over this range, but are tested and guaranteed at  $T_A = +25^{\circ}C$  only. contact factory for avail-

<sup>\*\*\*</sup> Future product—contact factory for availability.

### **ABSOLUTE MAXIMUM RATINGS**

| 0.5V to +5.5V                 |

|-------------------------------|

| ) to (V <sub>CC</sub> + 0.5V) |

|                               |

| -16mA to +10mA                |

|                               |

| 0mA to 56mA                   |

|                               |

| ±22mA                         |

| -600µA to +4mA                |

|                               |

| Voltage at LOS, SIS, PHADJ, THADJ, CPWD+, CPWD-,                  |

|-------------------------------------------------------------------|

| <del>LOL</del> , FIL+, FIL-, LREF0.5V to (V <sub>CC</sub> + 0.5V) |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C)             |

| 32-Pin TQFP-EP (derate 22.2mW/°C above +85°C)1444mW               |

| Operating Temperature Range                                       |

| MAX3877/MAX3878EHJ40°C to +85°C                                   |

| Operating Junction Temperature Range (die)55°C to +150°C          |

| Storage Temperature Range65°C to +150°C                           |

| Processing Temperature (die)+400°C                                |

| Lead Temperature (soldering, 10s)+300°C                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                                                   | SYMBOL          | CONDITIONS                                                    | MIN                     | TYP                   | MAX                        | UNITS |

|-------------------------------------------------------------|-----------------|---------------------------------------------------------------|-------------------------|-----------------------|----------------------------|-------|

| SUPPLY CURRENT                                              |                 |                                                               | •                       |                       |                            |       |

| Cupalis Current                                             | 1               | MAX3877 (Note 2)                                              |                         | 175                   | 262                        | A     |

| Supply Current                                              | Icc             | MAX3878 (Note 2)                                              |                         | 163                   | 250                        | mA    |

| INPUT SPECIFICATION (SDI±, SL                               | Bl±)            |                                                               |                         |                       |                            |       |

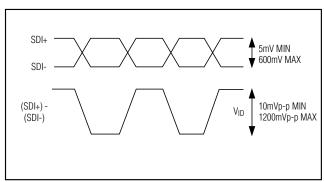

| Differential Input Voltage (SDI±)                           | V <sub>ID</sub> | Figure 1 (Note 3)                                             | 10                      |                       | 1200                       | mVp-p |

| Differential System Loopback<br>Input Voltage Range (SLBI±) | V <sub>ID</sub> |                                                               | 50                      |                       | 1200                       | mVp-p |

| Single-Ended Input Voltage<br>(SDI±, SLBI±)                 | VIS             |                                                               | V <sub>CC</sub> - 0.6   |                       | V <sub>CC</sub> + 0.3      | V     |

| Input Termination to V <sub>CC</sub> (SDI±, SLBI±)          | R <sub>IN</sub> |                                                               |                         | 52                    |                            | Ω     |

| MAX3878 PECL OUTPUT SPECIF                                  | FICATION (S     | DO±, SCLKO±)                                                  |                         |                       |                            |       |

| PECL Output High Voltage                                    |                 | $T_A = 0$ °C to +85°C                                         | V <sub>CC</sub> - 1.025 |                       | V <sub>CC</sub> - 0.88     | .,    |

| (SDO±, SCLKO±)                                              |                 | T <sub>A</sub> = -40°C                                        | V <sub>CC</sub> - 1.085 |                       | V <sub>CC</sub> - 0.88     | V     |

| PECL Output Low                                             |                 | $T_A = 0$ °C to +85°C                                         | V <sub>CC</sub> - 1.81  |                       | V <sub>CC</sub> -<br>1.62  | V     |

| Voltage (SDO±, SCLKO±)                                      |                 | T <sub>A</sub> = -40°C                                        | V <sub>CC</sub> - 1.83  |                       | V <sub>CC</sub> -<br>1.556 | V     |

| MAX3877 CML OUTPUT SPECIFI                                  | CATION (SE      | OO±, SCLKO±)                                                  |                         |                       |                            |       |

| CML Differential Output Swing                               |                 | $R_L = 50\Omega$ to $V_{CC}$                                  | 640                     | 800                   | 1000                       | mVp-p |

| CML Differential Output<br>Impedance                        | Ro              |                                                               | 85                      | 100                   | 115                        | Ω     |

| CML Output Common-Mode<br>Voltage                           |                 | DC-coupling (R <sub>L</sub> = $50\Omega$ to V <sub>CC</sub> ) |                         | V <sub>CC</sub> - 0.2 |                            | ٧     |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3 \text{V} \text{ and } T_A = +25 ^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                            | SYMBOL              | CONDITIONS                                              | MIN   | TYP | MAX   | UNITS |  |

|--------------------------------------|---------------------|---------------------------------------------------------|-------|-----|-------|-------|--|

| THRESHOLD SETTING SPECIFIC           | CATION (SD          | (±)                                                     |       |     |       |       |  |

| Differential Input Voltage Range     | V <sub>ID</sub>     | Note 4                                                  | 100   |     | 600   | mVp-p |  |

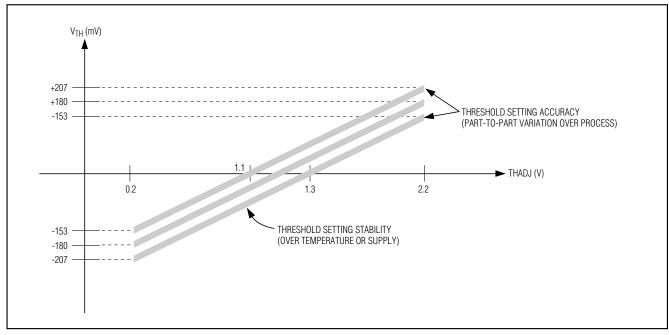

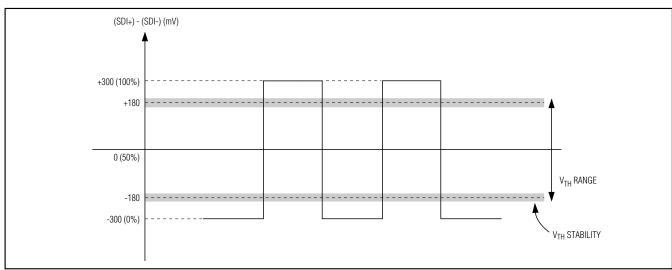

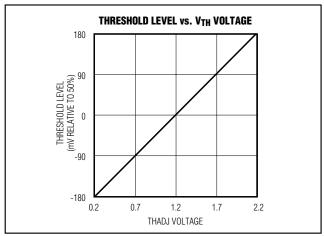

| Input Threshold Adjustment<br>Range  | V <sub>TH</sub>     | Figure 2                                                | -180  |     | 180   | mV    |  |

| THADJ Voltage Range                  | V <sub>THAD</sub> J | Figure 2                                                | 0.2   |     | 2.2   | V     |  |

| Threshold Control Linearity          |                     |                                                         | -5    |     | +5    | %     |  |

| Threshold Setting Accuracy           |                     | Figure 2                                                | -27   |     | +27   | mV    |  |

| Threshold Catting Stability          |                     | V <sub>TH</sub> = ±30mV to ±80mV<br>(Note 5, Figure 2)  | -7.0  |     | +7.0  | mV    |  |

| Threshold Setting Stability          |                     | V <sub>TH</sub> = ±80mV to ±180mV<br>(Note 5, Figure 2) | -11.5 |     | +11.5 | IIIV  |  |

| Maximum Input Current (THADJ, PHADJ) |                     | Control voltage = 0.2V to 2.2V                          | -10   |     | +10   | μA    |  |

| TTL INPUT/OUTPUT SPECIFICAT          | TION (SIS, LI       | REF, TOL, LOS)                                          |       |     |       |       |  |

| TTL Input High Voltage (SIS, LREF)   | VIH                 |                                                         | 2.0   |     |       | V     |  |

| TTL Input Low Voltage (SIS, LREF)    | VIL                 |                                                         |       |     | 0.8   | V     |  |

| TTL Input Current<br>(SIS, LREF)     |                     |                                                         | -10   |     | +10   | μΑ    |  |

| TTL Output High Voltage (LOL>, LOS)  | Vон                 | I <sub>OH</sub> = +40μA                                 | 2.4   |     |       | V     |  |

| TTL Output Low Voltage (LOL>, LOS)   | VoL                 | I <sub>OL</sub> = -2mA                                  |       |     | 0.4   | V     |  |

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}.)$  (Note 6)

| PARAMETER                 | SYMBOL          | CONDITIONS | MIN | TYP   | MAX | UNITS |

|---------------------------|-----------------|------------|-----|-------|-----|-------|

| Serial Output Clock Rate  |                 |            |     | 2.488 |     | Gbps  |

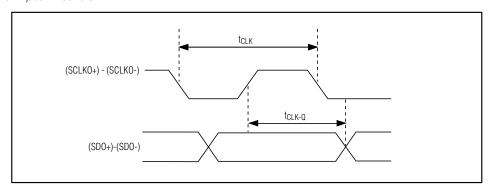

| Clock-to-Q Delay          |                 | (Figure 4) | 110 |       | 290 | ps    |

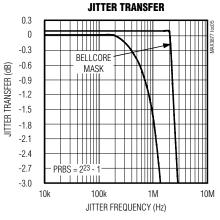

| Jitter Peaking            | J <sub>P</sub>  | f ≤ 2MHz   |     |       | 0.1 | dB    |

| Jitter Transfer Bandwidth | J <sub>BW</sub> |            |     | 1.1   | 2.0 | MHz   |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}.)$  (Note 6)

| PARAMETER                                       | SYMBOL | CONDITIONS                                                                        | MIN  | TYP   | MAX   | UNITS             |

|-------------------------------------------------|--------|-----------------------------------------------------------------------------------|------|-------|-------|-------------------|

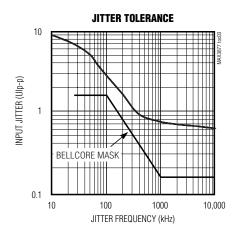

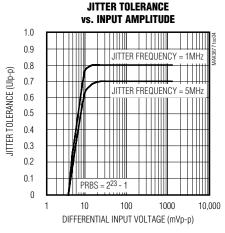

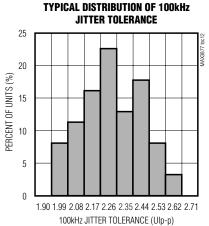

| Jitter Tolerance                                |        | f = 70kHz                                                                         |      | 3.18  |       |                   |

|                                                 |        | f = 100kHz (see "Jitter Tolerance" graph in<br>Typical Operating Characteristics) |      | 2.75  |       | Ulp-p             |

|                                                 |        | f = 1MHz                                                                          | 0.41 | 0.67  |       |                   |

|                                                 |        | f = 10MHz                                                                         | 0.36 | 0.45  |       |                   |

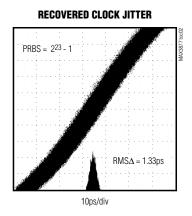

| littan Oananakian                               | 1.     | Jitter bandwidth = 12kHz to 20MHz                                                 |      | 0.003 | 0.006 | UI <sub>RMS</sub> |

| Jitter Generation                               | JGEN   | Jiller pandwidth = 12kHz to 20MHz                                                 |      | 0.026 | 0.056 | Ulp-p             |

| Clock Output Edge Speed                         |        | (20% to 80%)                                                                      |      |       | 120   | ps                |

| Data Output Edge Speed                          |        | (20% to 80%)                                                                      |      |       | 120   | ps                |

| Tolerated Consecutive Identical Digits          |        | BER ≤ 10 <sup>-10</sup>                                                           |      | 2000  |       | bits              |

| Inner the Determination of COLL CLOUD           |        | 100kHz to 2.5GHz                                                                  |      | 17    | dB    |                   |

| Input Return Loss (SDI±, SLBI±)                 |        | 2.5GHz to 4.0GHz                                                                  |      | 14.5  |       | ab                |

| PLL Acquisition Time                            |        |                                                                                   |      | 14    |       | ms                |

| LOS Assert Time                                 |        |                                                                                   |      | 1.65  |       | μs                |

| LOS Deassert Time                               |        |                                                                                   |      | 4.0   |       | μs                |

| Low-Frequency Cutoff for DC-Cancellation Loop   |        | C <sub>PWD</sub> = 0.1µF                                                          |      | 10    |       | kHz               |

| HOLDOVER SPECIFICATION                          | •      |                                                                                   |      |       |       | •                 |

| VCO Frequency Drift Rate in the Absence of Data | df/dt  | C <sub>FIL</sub> = 1µF                                                            |      | 6.2   |       | kHz/µs            |

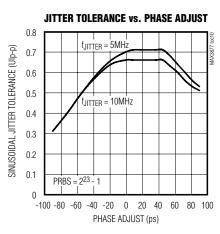

| PHASE ADJUST SPECIFICATION                      | 1      |                                                                                   |      | •     | -     |                   |

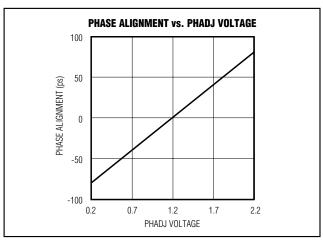

| Minimum Phase Adjust Range                      |        | (Note 7)                                                                          | -60  |       | +60   | ps                |

| Phase Adjust Stability                          |        | (Note 8)                                                                          | -8   |       | +8    | ps                |

- **Note 1:** At  $T_A = -40$ °C, DC characteristics are guaranteed by design and characterization.

- **Note 2:** Excluding PECL output termination, CML outputs open.

- **Note 3:** Jitter specifications are guaranteed for this data input voltage range, measured by connecting THADJ to V<sub>CC</sub>. Guaranteed by design and characterization.

- Note 4: Jitter specifications are guaranteed when input threshold is set to ≤ 30% of the differential input swing. Measured with edge speed ≤ 150ps (Figure 3). Guaranteed by design and characterization.

- Note 5: Threshold setting stability is guaranteed by design and characterization.

- Note 6: AC characteristics are guaranteed by design and characterization.

- Note 7: Phase adjust is disabled when PHADJ is connected to V<sub>CC</sub>.

- Note 8: Phase adjust stability is guaranteed over temperature and power-supply variation.

Figure 1. Input Amplitude

Figure 2. Setting the Input Threshold Level

Figure 3. Definition of Input Threshold

Figure 4. Output Clock-to-Q Delay

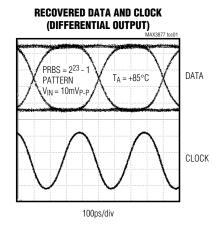

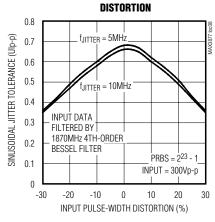

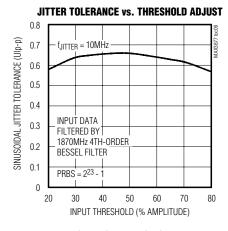

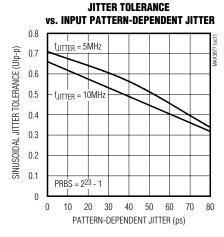

## Typical Operating Characteristics

( $V_{CC}$  = +3.3V,  $T_A$  = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

( $V_{CC}$  = +3.3V,  $T_A$  = +25 $^{\circ}C$ , unless otherwise noted.)

JITTER TOLERANCE vs. PULSE-WIDTH

## **Pin Description**

| PIN                                    | NAME   | FUNCTION                                                                                                                            |

|----------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9, 10,16,<br>30                     | GND    | Supply Ground                                                                                                                       |

| 3, 6, 11, 14,<br>15, 17, 20,<br>21, 24 | Vcc    | Supply Voltage                                                                                                                      |

| 2                                      | THADJ  | Threshold Control Voltage Input. Used for setting the data decision threshold. Connect to $V_{CC}$ if not used. See Figure 7.       |

| 4                                      | SDI-   | Negative Data Input. 2.488Gbps serial data stream.                                                                                  |

| 5                                      | SDI+   | Positive Data Input. 2.488Gbps serial data stream.                                                                                  |

| 7                                      | SIS    | Signal Input Selection, TTL. High for system loopback input. See Table 1.                                                           |

| 8                                      | LREF   | Lock to Reference Clock Control Signal, TTL.                                                                                        |

| 12                                     | SLBI-  | Negative System Loopback or Reference Clock (in holdover mode) Input                                                                |

| 13                                     | SLBI+  | Positive System Loopback or Reference Clock (in holdover mode) Input                                                                |

| 18                                     | SCLKO- | Negative Clock Output, CML (MAX3877) or PECL (MAX3878)                                                                              |

| 19                                     | SCLKO+ | Positive Clock Output, CML (MAX3877) or PECL (MAX3878)                                                                              |

| 22                                     | SDO-   | Negative Data Output, CML (MAX3877) or PECL (MAX3878)                                                                               |

| 23                                     | SDO+   | Positive Data Output, CML (MAX3877) or PECL (MAX3878)                                                                               |

| 25                                     | LOL    | Loss-of-Lock Indicator, TTL Active-Low                                                                                              |

| 26                                     | LOS    | Loss-of-Signal Indicator, TTL Active-High. LOS is asserted high if there are no incoming data transitions for approximately 1.65µs. |

| 27                                     | PHADJ  | Phase-Adjust Input. Used to optimize sampling point. Connect to V <sub>CC</sub> if not used. See Figure 6.                          |

| 28                                     | FIL-   | Negative PLL Loop Filter Connection. Connect a 1.0µF capacitor between FIL+ and FIL                                                 |

| 29                                     | FIL+   | Positive PLL Loop Filter Connection. Connect a 1.0µF capacitor between FIL+ and FIL                                                 |

| 31                                     | CPWD-  | Negative Pulse-Width Distortion Cancellation Capacitor. Connect a 0.1µF capacitor between CPWD+ and CPWD                            |

| 32                                     | CPWD+  | Positive Pulse-Width Distortion Cancellation Capacitor. Connect a 0.1µF capacitor between CPWD+ and CPWD                            |

## **Detailed Description**

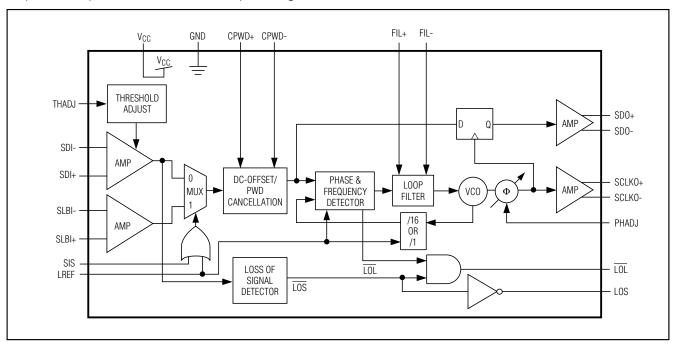

The MAX3877/MAX3878 consist of a fully integrated phase-locked loop (PLL), input amplifier, data retiming block, and CML output buffer (MAX3877) or PECL output buffer (MAX3878). The PLL consists of a phase/frequency detector (PFD), a loop filter, and a voltage-controlled oscillator (VCO). Figure 5 shows the functional diagram.

This device is designed to deliver the best combination of jitter performance and power dissipation by using a fully differential signal architecture and low-noise design techniques.

### **SDI Input Amplifier**

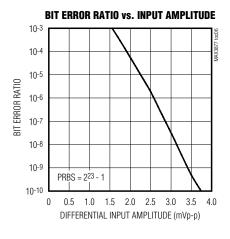

The SDI input amplifier accepts 2.488Gbps NRZ data with differential input swing from 10mVp-p up to 1200mVp-p. The bit error rate is better than 1 × 10<sup>-10</sup> for input signals as small as 4mVp-p, though the jitter tolerance performance will be degraded. This amplifier allows for adjustment of the input threshold level. For interfacing with PECL signal levels, see *Applications Information*, or refer to Applications Note HFAN 1.0, *Interfacing Between CML*, *PECL*, and *LVDS*.

### **SLBI Input Amplifier**

The SLBI input amplifier accepts either 2.488Gbps loopback data or a 155MHz reference clock. This amplifier accepts data with differential input swing from

50mVp-p up to 1200mVp-p. For interfacing with PECL signal levels, see *Applications Information*.

### **Phase/Frequency Detector**

The phase detector incorporated in the MAX3877 and MAX3878 produces a voltage proportional to the phase difference between the incoming data and the internal clock. Because of its feedback nature, the PLL drives the error voltage to zero, aligning the recovered clock to the center of the incoming data eye for retiming.

The digital frequency detector (FD) aids frequency acquisition during startup conditions. The frequency difference between the received data and the VCO clock is derived by sampling the in-phase and quadrature VCO output on the rising edges of the data input signal. The FD drives the VCO until the frequency difference is reduced to zero. Once frequency acquisition is complete, the FD returns to a neutral state. False locking is completely eliminated by this digital frequency detector.

While in holdover mode, a Type 4 phase/frequency detector (PFD) is implemented to track the 155MHz reference clock signal. This PFD compares the incoming 155MHz reference clock with the divided down VCO clock. The LREF input is used to enable holdover mode (see *Applications Information*).

Figure 5. Functional Diagram

Figure 6. Phase Alignment vs. PHADJ Voltage

### **Phase Adjust**

The internal clock is aligned to the center of the data eye. For specific applications, this sampling position can be shifted using the PHADJ input to optimize BER performance. Refer to Figure 6 for setting the voltage at PHADJ. When the phase adjust feature is not used, PHADJ should be tied directly to VCC.

### **Loop Filter and VCO**

The phase detector and frequency detector outputs are summed into the loop filter. An external capacitor, C<sub>F</sub>, is required to set the PLL damping ratio. Refer to *Design Procedure* for guidelines on selecting this capacitor.

The loop filter output controls the on-chip LC VCO running at 2.488GHz. The VCO provides low phase noise and is trimmed to the correct frequency. Clock jitter generation is typically 1.2ps<sub>RMS</sub> within a jitter bandwidth of 12kHz to 20MHz.

#### **Loss-of-Lock Monitor**

A loss-of-lock monitor is incorporated in the MAX3877/MAX3878 frequency detector. When the PLL is frequency locked, the internal LOL signal is high, and if the PLL is out of frequency lock, the internal LOL signal immediately becomes low.

### Loss-of-Signal Detector

A loss of signal detector is provided to detect a loss of incoming data. If there are no transitions to the SDI data input for approximately 1.65µs, the LOS signal becomes high.

# DC-Offset/Pulse-Width Distortion Cancellation Loop

The input signal is first limited in the forward signal path. The DC offset of this signal is detected and then amplified in the feedback path. CPWD sets the cutoff frequency of the low pass filter. This error signal is then subtracted from the incoming data. When threshold adjust is enabled, this loop acts as a pulse-width distortion cancellation loop. Shorting the CPWD± pins together disables the DC-offset/pulse-width distortion cancellation loop.

### **Threshold Adjust**

This analog input controls the decision threshold of the input stage. In applications where the noise density is not balanced between logical zeros and ones (i.e., optical amplification using EDFA amplifiers), it is possible to achieve lower bit-error ratios (BER) by adjusting the input threshold. Threshold adjust may be disabled by connecting THADJ to  $V_{\rm CC}$ . The threshold level is set relative to the center of the differential input voltage swing at the input. Refer to Figures 3 and 7 for setting the voltage at THADJ.

### **Input Select Pins**

TTL inputs SIS and LREF are provided to select between the SDI and SLBI inputs. Table 1 is a logical truth table describing the operation of SIS and LREF. In this way, the MAX3877/MAX3878 will automatically lock to the reference clock in the event of a loss-of-signal condition.

In systems where a valid clock output is required under loss-of-signal conditions, a 155MHz reference clock is applied to the SLBI inputs for holdover capabilities. This holdover mode is activated with the LREF input. LREF may be directly connected to the LOS pin or to an external system loss-of-signal monitor.

Figure 7. Threshold Level vs. THADJ Voltage

**Table 1. Selecting Input Path**

|          | SIS = 0                   | SIS = 1                        |  |  |

|----------|---------------------------|--------------------------------|--|--|

| LREF = 0 | SDI<br>(Normal Operation) | SLBI<br>(System Loopback Mode) |  |  |

| LREF = 1 | SLBI<br>(Holdover Mode)   | SLBI<br>(Holdover Mode)        |  |  |

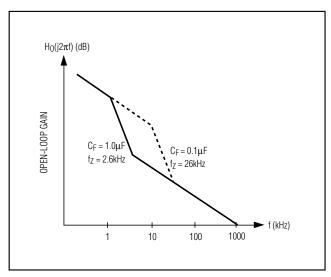

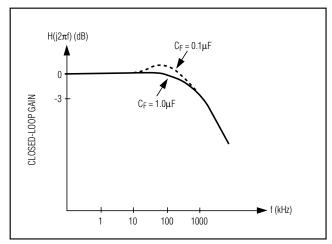

Figure 8. Open-Loop Transfer Function

Figure 9. Closed-Loop Transfer Function

## **Design Procedure**

### **Setting the Loop Filter**

The MAX3877/MAX3878 are designed for both regenerator and receiver applications. The fully integrated PLL is a classic second-order feedback system, with a loop bandwidth ( $f_L$ ) fixed at 1.4MHz. The external capacitor,  $C_F$ , can be adjusted to set the loop damping. Figures 8 and 9 show the open-loop and closed-loop transfer functions.

The PLL zero frequency,  $f_Z$ , is a function of external capacitor  $C_F$ , and can be approximated according to:

$$f_Z = \frac{1}{2\pi(60)C_F}$$

For an overdamped system (fz / fL < 0.25), the jitter peaking (Mp) of a second-order system can be approximated by:

$$M_P = 20\log\left(1 + \frac{f_Z}{f_L}\right)$$

For example, using  $C_F = 0.1 \mu F$  results in a jitter peaking of 0.16dB. Reducing  $C_F$  below 0.01 $\mu F$  may result in PLL instability. The recommended value of  $C_F = 1.0 \mu F$  is to guarantee a maximum jitter peaking of less than 0.1dB.  $C_F$  must be a low-TC, high-quality capacitor of type XR7 or better.

### **Input Termination**

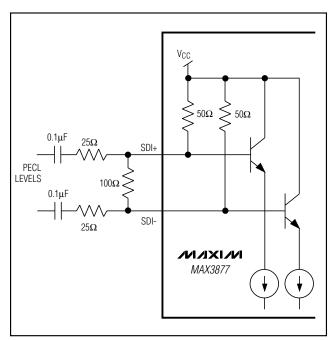

Inputs for the MAX3877/MAX3878 are current-mode logic (CML) compatible. The inputs all provide internal  $50\Omega$  termination to reduce the required number of external components. When interfacing to differential PECL levels, it is important to attenuate the signal while maintaining a  $50\Omega$  termination (see Figure 10). AC-coupling is also necessary to maintain the input common-mode level.

### **Output Termination (MAX3877)**

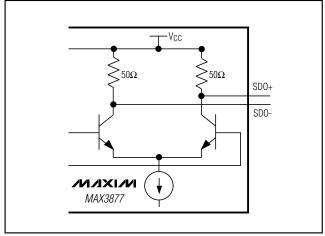

The MAX3877 uses current-mode logic (CML) for its high-speed digital outputs. CML outputs are  $50\Omega$  back-terminated, reducing the external component count. Refer to Figure 11 for the output structure. CML outputs may be terminated by  $50\Omega$  to  $V_{CC}$ , or by  $100\Omega$  differential impedance.

#### **Output Termination (MAX3878)**

The MAX3878 uses positive emitter-coupled logic (PECL) for its high-speed outputs. PECL outputs are designed to be terminated by  $50\Omega$  to (VCC - 2V). Refer to Applications Note HFAN 0.1.0, *Interfacing Between CML*, *PECL*, and *LVDS*, for more information.

Figure 10. Interfacing with PECL Levels

Figure 11. CML Outputs

### Jitter Tolerance and Input Sensitivity Trade-Offs

When the received data amplitude is higher than 10mVp-p, the MAX3877/MAX3878 provide a typical jitter tolerance of 0.64Ul at jitter frequencies greater than 10MHz. The SDH/SONET jitter tolerance specification is 0.15Ul, leaving a jitter allowance of 0.49Ul for receiver preamplifier and postamplifier design.

The BER is better than  $1\times 10^{-10}$  for input signals greater than 4mVp-p. At 5mVp-p, jitter tolerance will be degraded, but will still be above the SDH/SONET requirement. The user can make a trade-off between jitter tolerance and input sensitivity according to the specific application. Refer to *Typical Operating Characteristics* for Jitter Tolerance and BER vs. Input Amplitude.

## **Applications Information**

#### **Holdover Mode**

When in holdover mode, the MAX3877/MAX3878 can lock to an external reference clock to maintain a valid clock output in the absence of input data. When LREF is high, the PLL locks to an external 155.52MHz reference clock, which is applied to the SLBI inputs. To enter holdover mode automatically when there are no transitions to the SDI inputs, LOS can be directly tied to LREF. By maintaining frequency lock, the time required to reacquire lock is reduced.

### System Loopback

The system loopback input may be used as an auxiliary input for system loopback testing or as input for an external 155.52MHz reference clock. When used as a loopback test, the user can connect a serializer output in a transceiver directly to the SLBI inputs for system diagnostics. Using an external reference clock can maintain PLL frequency lock in the absence of transitions on the SDI inputs.

#### Consecutive Identical Digits (CID)

The MAX3877/MAX3878 have low frequency drift in the absence of data transitions. As a result, long runs of consecutive zeros and ones can be tolerated while maintaining a BER better than 1  $\times$  10<sup>-10</sup>. The CID tolerance is tested using a 2<sup>13</sup> - 1PRBS, substituting a long run of zeros to simulate the worst case. A CID tolerance of 2000 bits is typical.

The VCO frequency after 4096 bits (approximately 1.6µs) may be estimated by using the VCO drift rate:

f = 2.488GHz

$$\pm \left(1.65\mu s \times \frac{6.2kHz}{\mu s}\right)$$

= 2.488GHz  $\pm 10.21kHz = 2.488GHz \pm 4.1ppm$

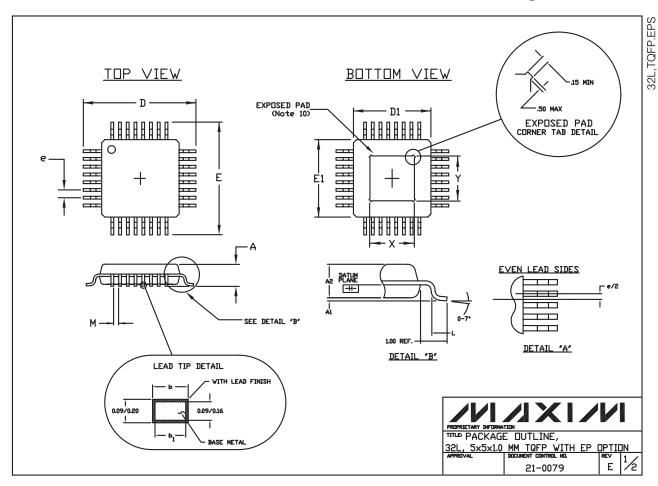

### Exposed Pad (EP) Package

The exposed pad, 32-pin TQFP incorporates features that provide a very low thermal-resistance path for heat removal from the IC. The pad is electrical ground on the MAX3877/MAX3878 and should be soldered to the circuit board for proper thermal and electrical performance.

Figure 12. Typical Application Circuit (Interfacing with the MAX3864 TIA without using threshold adjust)

### **Layout Considerations**

Performance can be significantly affected by circuit board layout and design. Use good high-frequency design techniques, including minimizing ground inductance and using fixed-impedance transmission lines on the data and clock signals. Power-supply decoupling should be placed as close to VCC as possible. Take care to isolate the input from the output signals to reduce feedthrough.

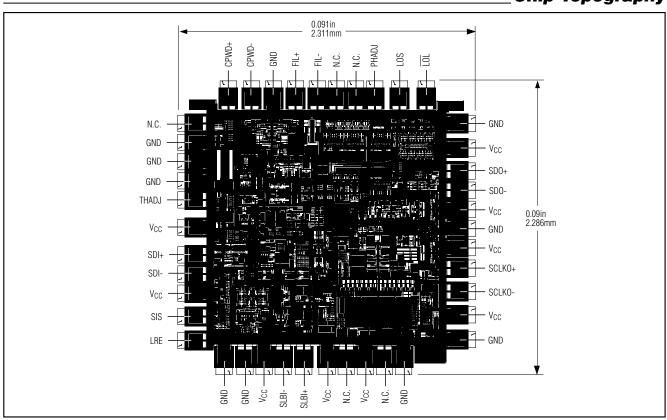

### **Chip Information**

TRANSISTOR COUNT: 1561

PROCESS: BiPOLAR

SUBSTRATE CONNECTED TO GND

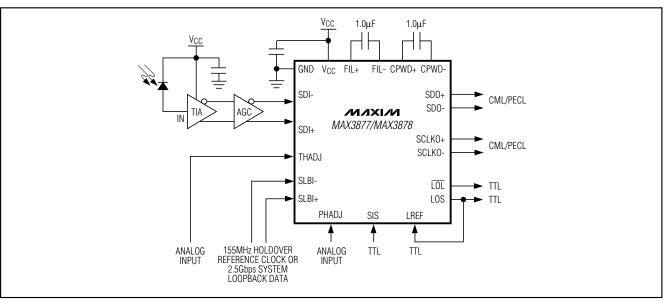

## **Typical Application Circuit**

## **Chip Topography**

14 \_\_\_\_\_\_ *NIXIN*

## **Package Information**

### Package Information (continued)

NOTES:

NOTES:

1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5-1982.

2. DATUM PLANE === IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

3. DIMENSIONS D1 AND E1 D0 NOT INCLUDE MOLD PROTRUSION.

ALLOWABLE MOLD PROTRUSION IS 0.254 MM ON D1 AND E1

DIMENSIONS.

THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.15 MILLIMETERS.

DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE 6 DIMENSION AT MAXIMUM MATERIAL CONDITION.

CONTROLLING DIMENSION: MILLIMETER.

THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95, REGISTRATION

M□-136.

MD-136.

8. LEADS SHALL BE COPLANAR WITHIN .004 INCH.

9. EXPOSED DIE PAD SHALL BE COPLANAR WITH BOTTOM OF PACKAGE WITHIN 2 MILS (.05 MM).

10. DIMENSIONS X AND Y APPLY TO EXPOSED PAD (EP) VERSIONS ONLY.

SEE INDIVIDUAL PRODUCT DATASHEET TO DETERMINE IF A PRODUCT USES EXPOSED PAD PACKAGE.

|                | JEDEC VARIATIONS          |       |            |        |  |  |

|----------------|---------------------------|-------|------------|--------|--|--|

|                | DIMENSIONS IN MILLIMETERS |       |            |        |  |  |

|                | A                         | Α     | AA-        | -EP*   |  |  |

|                | 5×5×1                     | LO MM | 5×5×1.0 MM |        |  |  |

|                | MIN.                      | MAX.  | MIN.       | MAX.   |  |  |

| Α              | ×                         | 1.20  | 34         | 1.20   |  |  |

| A <sub>1</sub> | 0.05                      | 0.15  | 0.05       | 0.15   |  |  |

| Az             | 0.95                      | 1.05  | 0.95       | 1.05   |  |  |

| D              | 7.00                      | BSC.  | 7.00       | BSC.   |  |  |

| $D_1$          | 5.00                      | BSC.  | 5.00 BSC.  |        |  |  |

| Ε              | 7.00                      | BSC.  | 7.00       | BSC.   |  |  |

| E <sub>1</sub> | 5.00                      | BSC.  | 5.00       | BSC.   |  |  |

| L              | 0.45                      | 0.75  | 0.45       | 0.75   |  |  |

| М              | 0.15                      | ×     | 0.15       | 1/2    |  |  |

| N              | 3                         | 2     | 3          | 2      |  |  |

| e              | 0.50 BSC.                 |       | 0.50       | BSC.   |  |  |

| b              | 0.17                      | 0.27  | 0.17       | 0.27   |  |  |

| b1             | 0.17                      | 0.23  | 0.17       | 0.23   |  |  |

| жX             | N/A                       | N/A   | 2.70       | 3.30   |  |  |

| *Y             | N/A                       | N/A   | 2.70       | 3.30   |  |  |

|                |                           |       | * EXPOS    | ED PAD |  |  |

TITLE PACKAGE DUTLINE, 32L, 5x5x1.0 MM TQFP WITH EP 21-0079

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX3877EHJ-T MAX3878EHJ-T