# **MIC2564A**

### **Dual Serial PCMCIA/CardBus Power Controller**

### **Preliminary Information**

### **General Description**

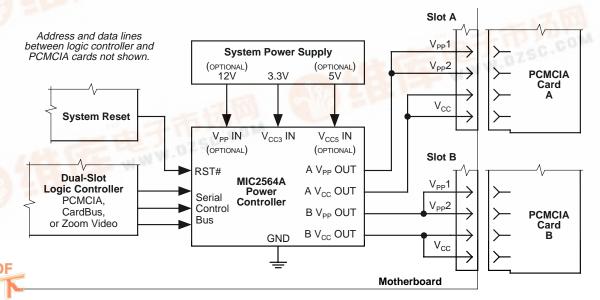

The MIC2564A is dual-slot PC Card (PCMCIA) and CardBus power controller. It is a sophisticated power switching matrix that controls  $V_{CC}$  and  $V_{PP}$  voltages to two PC Card slots. The MIC2564A is used in conjunction with a serial-data output logic controller using the standard three-wire serial control data format.

When connected to 3.3V, 5V, and 12V system power supplies, the MIC2564A can switch its  $V_{CC}$  outputs between 0V, 3.3V, 5.0V, and high-impedance states and  $V_{PP}$  outputs between 0V, 3.3V, 5V, 12V, and high-impedance states. The  $V_{CC}$  outputs will supply a minimum of 1A current to the socket and the  $V_{PP}$  outputs will supply a minimum of 120mA to the socket. Voltage rise and fall times are well controlled. The MIC2564A also features an efficient standby (sleep) mode at 0.3 $\mu$ A typical quiescent current.

12V and 5V supplies are not required for MIC2564A operation making it possible to omit one or both supplies when they are not needed by the system. An internal charge pump supplies the internal bias voltages required for high-performance switching.

The MIC2564A is protected by overtemperature shutdown, and protects itself and the system with current limiting and cross-conduction lockout.

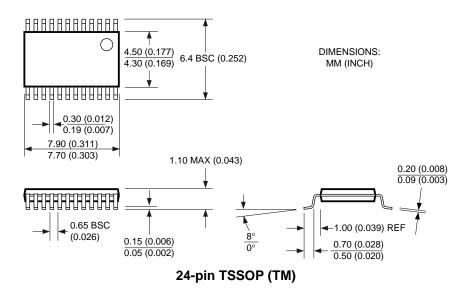

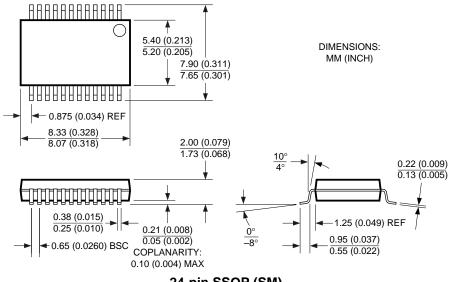

The MIC2564A is available in 24-pin SSOP and 24-pin TSSOP.

### **Features**

- Standard 3-wire serial control data input

- Controls two card slots from one surface mount device

- High-efficiency, low-resistance switches

- 12V supply optional (not required by MIC2564A)

- Current limit and overtemperature shutdown

- Ultralow 1µA-typical standby power consumption

- Cross-conduction lockout (no switching transients)

- Break-before-make switching

- 1A minimum V<sub>CC</sub> output per slot

- Independent V<sub>CC</sub> and V<sub>PP</sub> voltage output (MIC2564A-1)

- 120mA minimum V<sub>PP</sub> output current per slot

- 24-pin surface-mount SSOP and TSSOP packages

# **Applications**

- PC Card and CardBus power control

- Zoom Video port power control

- · Wireless communications

- Bar code data collection systems

- Docking stations (portable and desktop)

- Power supply management

# **Ordering Information**

|   | Part Number   | Temperature Range | Package      |

|---|---------------|-------------------|--------------|

|   | MIC2564A-0BSM | -40°C to +85°C    | 24-pin SSOP  |

| ĺ | MIC2564A-1BSM | –40°C to +85°C    | 24-pin SSOP  |

| ĺ | MIC2564A-0BTS | –40°C to +85°C    | 24-pin TSSOP |

|   | MIC2564A-1BTS | –40°C to +85°C    | 24-pin TSSOP |

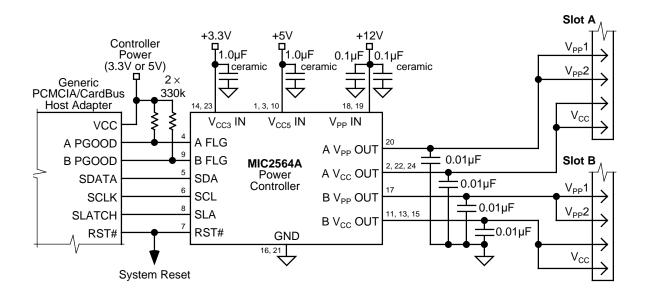

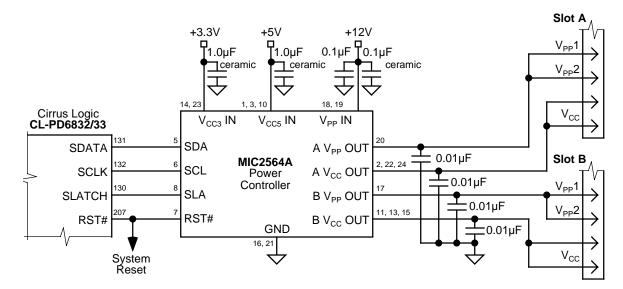

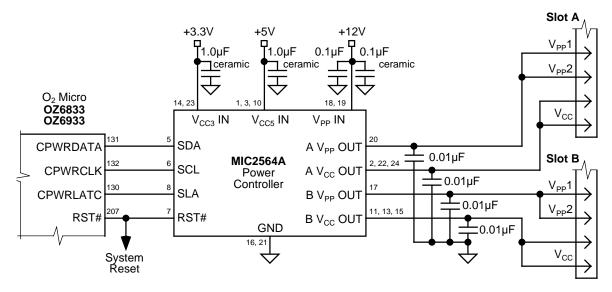

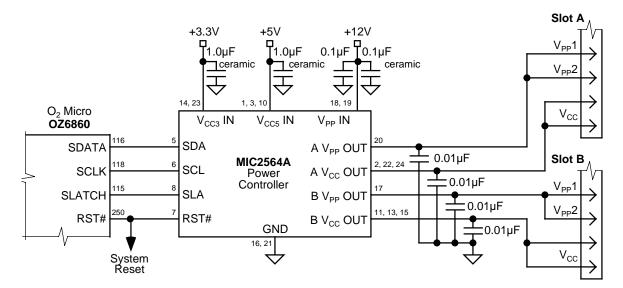

# **Typical Application**

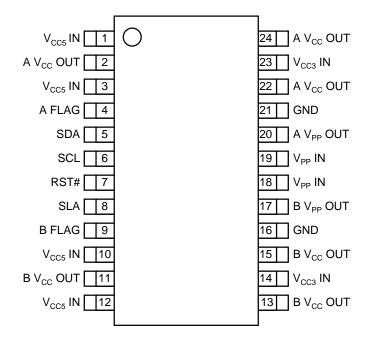

# **Pin Configuration**

24-lead SSOP (SM) 24-lead TSSOP (TS)

# **Pin Description**

| Pin Number | Pin Name              | Pin Function                                                                                                                                    |

|------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,3,10,12  | V <sub>CC5</sub> IN   | 5V Supply Input: Optional system power supply connection. Required only for 5V $\rm V_{CC}$ and $\rm V_{PP}$ output voltage.                    |

| 2,22,24    | A V <sub>CC</sub> OUT | Slot A V <sub>CC</sub> Output: Pins 2, 22, and 24 must be externally connected together.                                                        |

| 4          | A FLAG                | Channel A V <sub>CC</sub> and V <sub>PP</sub> Output Monitor (Output): Low on error condition.                                                  |

| 5          | SDA                   | Serial Data (Input)                                                                                                                             |

| 6          | SCL                   | Serial Clock (Input)                                                                                                                            |

| 7          | RST#                  | System Reset (Input): Active low signal deactivates the MIC2564A, clearing the serial registers and forcing the four power outputs to 0V (GND). |

| 8          | SLA                   | Serial Data Latch (Input)                                                                                                                       |

| 9          | B FLAG                | Channel B V <sub>CC</sub> and V <sub>PP</sub> Output Monitor (Output): Low on error condition.                                                  |

| 11,13,15   | B V <sub>CC</sub> OUT | Slot B V <sub>CC</sub> Output: Pins 11, 13, and 15 must be externally connected together.                                                       |

| 14,23      | V <sub>CC3</sub> IN   | 3.3V Supply Input: Required system power supply connection. Powers 3.3V $V_{\rm CC}$ and $V_{\rm PP}$ outputs and all internal circuitry.       |

| 16,21      | GND                   | Ground                                                                                                                                          |

| 17         | B V <sub>PP</sub> OUT | Slot B V <sub>PP</sub> Output                                                                                                                   |

| 18,19      | V <sub>PP</sub> IN    | 12V Supply Input: Optional system power supply connection. Required only for 12V $\rm V_{PP}$ output voltage.                                   |

| 20         | A V <sub>PP</sub> OUT | Slot A V <sub>PP</sub> Output                                                                                                                   |

#

| FF                                       | ·                                        |

|------------------------------------------|------------------------------------------|

| A or B V <sub>CC</sub> OUT               | >1A, Internally Limited                  |

| Power Dissipation at T <sub>A</sub> ≤ 25 | 5°C (P <sub>D</sub> ) Internally Limited |

| Storage Temperature                      | 65°C to +150°C                           |

| Lead Temperature (5 sec.)                | +260°C                                   |

| Lead Temperature (5 sec.) |

|---------------------------|

| ESD Rating, Note 3        |

| Opera | ating | Ratings | (Note 2) |

|-------|-------|---------|----------|

|       |       |         |          |

| V <sub>PP</sub> IN                                                         | 0V to +13.2V   |

|----------------------------------------------------------------------------|----------------|

| V <sub>CC3</sub> IN                                                        | +3.0V to +5.5V |

| V <sub>CC5</sub> IN                                                        | 0V to +5.5V    |

| V <sub>SCL</sub> , V <sub>SDA</sub> , V <sub>SLA</sub> , V <sub>RST#</sub> | 0V to +5.5V    |

| A or B V <sub>PP</sub> OUT                                                 | 0 to 120mA     |

| A or B V <sub>CC</sub> OUT                                                 | 0 to 1A        |

| Clock Frequency                                                            | 0 to 2MHz      |

| Ambient Temperature (T <sub>A</sub> )                                      | 40°C to +85°C  |

| Junction Temperature (T <sub>J</sub> )                                     | +125°C         |

| Package Thermal Resistance (θ, JA)                                         |                |

| SSOP                                                                       | 90°C/W         |

| TSSOP                                                                      | 83°C/W         |

### **Electrical Characteristics**

$V_{CC3} \ IN = 3.3 \text{V}, \ V_{CC5} \ IN = 5.0 \text{V}, \ V_{PP} \ IN = 12 \text{V}; \ T_A = 25 ^{\circ}\text{C}, \ \textbf{bold} \ \text{indicates} \ -40 ^{\circ}\text{C} \leq T_A \leq +85 ^{\circ}\text{C}; \ \text{unless noted}.$

| Symbol                      | Parameter                                | Conditions                                                                          | Min | Тур  | Max  | Units |

|-----------------------------|------------------------------------------|-------------------------------------------------------------------------------------|-----|------|------|-------|

| V <sub>PP</sub> Output      |                                          | ·                                                                                   |     |      |      |       |

| I <sub>PP</sub> OUT<br>Hi-Z | High Impedance Output<br>Leakage Current | shutdown mode<br>V <sub>PP</sub> OUT = 0V                                           |     | 1    | 10   | μА    |

| I <sub>PPSC</sub>           | Short Circuit Current Limit              | V <sub>PP</sub> OUT = 0V, normal mode, <b>Note 4</b>                                | 120 | 260  | 400  | mA    |

| R <sub>O</sub>              | Switch Resistance                        | V <sub>PP</sub> OUT = 5V selected,<br>I <sub>PP</sub> OUT = -100mA (sourcing)       |     | 1.6  | 5    | Ω     |

|                             |                                          | V <sub>PP</sub> OUT = 3.3V selected,<br>I <sub>PP</sub> OUT = -100mA (sourcing)     |     | 1.3  | 5    | Ω     |

|                             |                                          | $V_{PP}$ OUT = 12V selected, $V_{PP}$ IN = 12V, $I_{PP}$ OUT = -100 mA (sourcing)   |     | 1.3  | 2.3  | Ω     |

|                             |                                          | V <sub>PP</sub> OUT = 0V [ground] selected,<br>I <sub>PP</sub> OUT = 50μA (sinking) |     | 2000 | 5000 | Ω     |

| V <sub>PP</sub> Switchi     | ing Time (See Figure 2)                  |                                                                                     |     |      |      |       |

| t <sub>1</sub>              | Output Turn-On Delay, Note 5             | $V_{pp}$ OUT = Hi-Z to 10% of 3.3V, $R_L = 100\Omega$                               |     | 1    | 100  | μs    |

| $t_2$                       |                                          | $V_{PP}$ OUT = Hi-Z to 10% of 5V, $R_L$ = 100 $\Omega$                              |     | 1    | 100  | μs    |

| $t_3$                       |                                          | $V_{PP}$ OUT = Hi-Z to 10% of 12, RL = 100 $\Omega$                                 |     | 50   | 250  | μs    |

| t <sub>4</sub>              | Output Rise Time                         | $V_{pp}$ OUT = 10% to 90% of 3.3, $R_L = 100\Omega$                                 | 10  | 100  | 500  | μs    |

| $t_5$                       |                                          | $V_{pp} OUT = 10\% \text{ to } 90\% \text{ of } 5, R_L = 100\Omega$                 | 10  | 250  | 1000 | μs    |

| t <sub>6</sub>              |                                          | $V_{pp} OUT = 10\% \text{ to } 90\% \text{ of } 12, R_L = 100\Omega$                | 10  | 100  | 500  | μs    |

| t <sub>7</sub>              | Output Transition Time, Note 5           | $V_{PP}$ OUT = 3.3V to 90% of 12V, $R_L = 100\Omega$                                | 10  | 100  | 500  | μs    |

| t <sub>8</sub>              |                                          | $V_{PP}$ OUT = 5V to 90% of 12, $R_L = 100\Omega$                                   | 10  | 100  | 500  | μs    |

| t <sub>9</sub>              |                                          | $V_{PP} OUT = 12V \text{ to } 90\% \text{ of } 3.3, R_L = 100\Omega$                | 10  | 100  | 500  | μs    |

| t <sub>10</sub>             |                                          | $V_{PP}$ OUT = 12V to 90% of 5, $R_L$ = 100 $\Omega$                                | 10  | 250  | 1000 | μs    |

| t <sub>11</sub>             | Output Turnoff Fall Time                 | $V_{PP} OUT = 90\% \text{ to } 10\% \text{ of } 3.3, R_L = 100\Omega$               |     | 1    | 500  | μs    |

| t <sub>12</sub>             |                                          | $V_{PP} OUT = 90\% \text{ to } 10\% \text{ of } 5, R_L = 100\Omega$                 |     | 1    | 500  | μs    |

| <u>t<sub>13</sub></u>       |                                          | $V_{PP} OUT = 90\% \text{ to } 10\% \text{ of } 12, R_{L} = 100\Omega$              |     | 1    | 500  | μs    |

| Symbol                    | Parameter                                 | Conditions                                                                                            | Min                    | Тур  | Max                    | Units |

|---------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|-------|

| t <sub>14</sub>           | Output Turnoff Delay Time,                | $V_{PP}$ OUT = 3.3V to Hi-Z, $R_L$ = 100 $\Omega$                                                     |                        | 1    | 50                     | μs    |

| t <sub>15</sub>           | Notes 5, 7                                | $V_{PP}$ OUT = 5V to Hi-Z, $R_L$ = 100 $\Omega$                                                       |                        | 1    | 50                     | μs    |

| t <sub>16</sub>           |                                           | $V_{PP}$ OUT = 12V to Hi-Z, $R_L$ = 100 $\Omega$                                                      |                        | 1    | 50                     | μs    |

| V <sub>CC</sub> Output    |                                           |                                                                                                       |                        |      |                        |       |

| I <sub>CC OUT</sub> Hi-Z  | High Impedance Output<br>Leakage Current  | shutdown mode, V <sub>CC</sub> OUT = 0V                                                               |                        | 1    | 20                     | μА    |

| I <sub>CCSC</sub>         | Short Circuit Current Limit               | V <sub>CC</sub> OUT = 0, normal mode,<br>V <sub>CC3</sub> or V <sub>CC5</sub> switches, <b>Note 4</b> | 1.0                    | 2.0  | 3.0                    | Α     |

| R <sub>O</sub>            | Switch Resistance                         | $V_{CC}$ OUT = 3.3V selected,<br>$I_{CC}$ OUT = -1A (sourcing)                                        |                        | 120  | 150                    | mΩ    |

|                           |                                           | V <sub>CC</sub> OUT = 5V selected,<br>I <sub>CC</sub> OUT = -1A (sourcing)                            |                        | 85   | 120                    | mΩ    |

|                           |                                           | V <sub>CC</sub> OUT = 0V [ground] selected,<br>I <sub>CC</sub> OUT = 0.1mA (sinking)                  |                        | 2000 | 3900                   | Ω     |

| V <sub>CC</sub> Switching | ng Time (See Figure 3)                    |                                                                                                       |                        |      |                        |       |

| t <sub>17</sub>           | Output Turn-On Delay Time,                | $V_{CC}$ OUT = 0V to 10% of 3.3, $R_L$ = 10 $\Omega$                                                  |                        | 250  | 500                    | μs    |

| t <sub>18</sub>           | Note 5                                    | $V_{CC}$ OUT = 0V to 10% of 5.0, $R_L$ = $10\Omega$                                                   |                        | 500  | 1000                   | μs    |

| t <sub>19</sub>           | Output Rise Time                          | $V_{CC}$ OUT = 10% to 90% of 3.3V, $R_L = 10\Omega$                                                   | 750                    | 1200 | 5000                   | μs    |

| t <sub>20</sub>           |                                           | $V_{CC}$ OUT = 10% to 90% of 5, $R_L$ = 10 $\Omega$                                                   | 1000                   | 2200 | 5000                   | μs    |

| t <sub>21</sub>           | Output Fall Time                          | $V_{CC}$ OUT = 90% to 10% of 3.3, $R_{L}$ = 10 $\Omega$                                               | 100                    | 550  | 1000                   | μs    |

| t <sub>22</sub>           |                                           | $V_{CC}$ OUT = 90% to 10% of 5.0, $R_{L}$ = 10 $\Omega$                                               | 100                    | 400  | 2000                   | μs    |

| t <sub>23</sub>           | Output Turnoff Delay, Notes 5, 6          | $V_{CC}$ OUT = 3.3V to 90% of 3.3V , $R_L$ = $10\Omega$                                               |                        | 400  | 2000                   | μs    |

| t <sub>24</sub>           |                                           | $V_{CC}$ OUT = 5V to 90% of 5V, $R_L = 10\Omega$                                                      |                        | 400  | 2000                   | μs    |

| Power Supp                | ıly                                       |                                                                                                       | •                      |      |                        |       |

| I <sub>CC3</sub>          | V <sub>CC3</sub> IN Supply Current (3.3V) | V <sub>CC</sub> OUT = 5V or 3.3V, I <sub>CC</sub> OUT = 0                                             |                        | 120  | 200                    | μΑ    |

|                           | Note 7                                    | V <sub>CC</sub> OUT = Hi-Z (sleep mode)                                                               |                        | 5    | 10                     | μΑ    |

| I <sub>CC5</sub>          | V <sub>CC5</sub> IN Supply Current (5V)   | V <sub>CC</sub> OUT = 5V or 3.3V, I <sub>CC</sub> OUT = 0                                             |                        | 25   | 50                     | μΑ    |

|                           | Note 8                                    | V <sub>CC</sub> OUT = Hi-Z (sleep mode)                                                               |                        | 0.2  | 10                     | μΑ    |

| I <sub>PP</sub> IN        | V <sub>PP</sub> IN Supply Current (12V)   | $V_{PP}$ OUT = 0V, 3.3V, 5V, or Hi-Z; $I_{PP}$ OUT = 0                                                |                        | 1    | 10                     | μΑ    |

|                           | Note 8                                    | V <sub>PP</sub> OUT = V <sub>PP</sub> IN                                                              |                        | 4    | 50                     | μΑ    |

| $V_{CC3}$                 | Operating Input Voltage (3.3V)            | Note 7                                                                                                | 3.0                    | 3.3  | 5.5                    | V     |

| $V_{CC5}$                 | Operating Input Voltage (5V)              | Note 8                                                                                                | _                      | 5.0  | 5.5                    | V     |

| $V_{PP}$                  | Operating Input Voltage (12V)             | Note 8, 9                                                                                             | _                      | 12   | 13.2                   | V     |

| Thermal Shu               | utdown                                    |                                                                                                       |                        |      |                        |       |

| $T_{SD}$                  | Thermal Shutdown Temperature              |                                                                                                       |                        | 145  |                        | °C    |

|                           | ace DC Specifications                     |                                                                                                       | 1                      |      |                        |       |

| $\overline{V_{IH}}$       | Input Voltage: SDA, SCL, SLA pins         |                                                                                                       | 0.7V <sub>CC3</sub> IN |      | 5.5                    | V     |

| V <sub>IL</sub>           | Input Voltage: SDA, SCL, SLA pins         |                                                                                                       | -0.3                   |      | 0.3V <sub>CC3</sub> IN | V     |

| I <sub>IN</sub>           | Input Current                             | 0V < V <sub>IN</sub> < 5.5V                                                                           | -1                     | 0.2  | 1                      | μΑ    |

| Flag                      | ·                                         |                                                                                                       | •                      |      | 1                      |       |

|                           |                                           | V <sub>FLG</sub> = 5V                                                                                 |                        |      |                        |       |

| Symbol               | Parameter                       | Conditions                  | Min | Тур | Max | Units |

|----------------------|---------------------------------|-----------------------------|-----|-----|-----|-------|

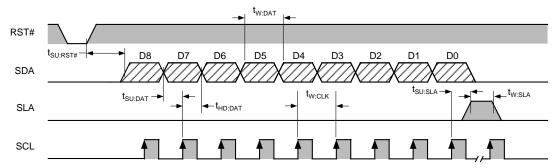

| Serial Inter         | face Timing Requirements (See F | igure 1), <b>Note 10</b>    | •   |     | •   |       |

| t <sub>HD:DAT</sub>  | SDA Hold Time                   |                             | 75  |     |     | ns    |

| t <sub>SU:DAT</sub>  | SDA Setup Time                  | data before clock           | 75  |     |     | ns    |

| t <sub>SU:SLA</sub>  | Latch Setup Time                |                             | 50  |     |     | ns    |

| t <sub>SU:RST#</sub> | Reset to Data Setup Time        | RST# before data            | 50  |     |     | ns    |

| $t_W$                | Minimum Pulse Width             | clock (t <sub>W:CLK</sub> ) | 50  |     |     | ns    |

|                      |                                 | latch (t <sub>W:SLA</sub> ) | 100 |     |     | ns    |

|                      |                                 | reset (t <sub>W:RST</sub> ) | 50  |     |     | ns    |

|                      |                                 | data (t <sub>W:DA</sub> )   | 50  |     |     | ns    |

- Note 1. Exceeding the absolute maximum rating may damage the device.

- Note 2. The device is not guaranteed to function outside its operating rating.

- Note 3. Devices are ESD sensitive. Handling precautions recommended.

- Note 4. Output enabled into short circuit.

- Note 5. Measurement is from the 50% point of the SLA rising edge.

- **Note 6.** Measurement is from the Hi-Z- or 0V-state command to the beginning of the slope. Measurement does not apply when device is in current limit or thermal shutdown.

- **Note 7.** V<sub>CC3</sub> IN powers all internal logic, bias, and drive circuitry, and is required for operation.

- **Note 8.**  $V_{PP}$  and  $V_{CC5}$  IN are not required for operation.

- Note 9. V<sub>PP</sub> IN must be either high impedance or greater than or approximately equal to the highest voltage V<sub>CC</sub> in the system. For example, if both 3.3V and 5V are connected to the MIC2564A, V<sub>PP</sub> IN must be either 5V, 12V, or high impedance.

- Note 10. Guaranteed by design not production tested.

# **Serial Control Timing Diagram**

Figure 1. Serial Control Timing Diagram

The MIC2564A uses a three-wire serial interface to control  $V_{CC}$  and  $V_{PP}$  outputs for both sections A and B. The three control lines have thresholds compatible with both 3.3V and 5V logic families. Data (SDA) is clocked in on the rising clock edge. The clock signal may be continuous or it may halt after all data is clocked in.

# **Output Timing Diagrams**

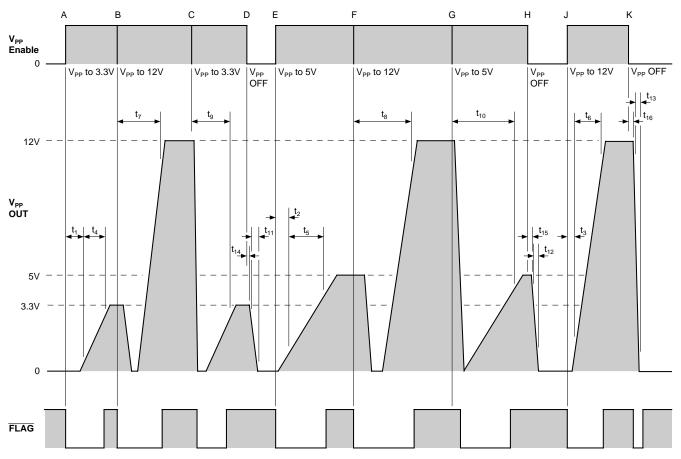

Figure 2. V<sub>PP</sub> Timing Diagram

$V_{PP}$  Enable is shown generically.  $R_L$  = 100 $\Omega$ .  $C_L$  = negligible. Refer to the serial control timing diagrams for details. At time **A**)  $V_{PP}$  = 3.3V is selected, **B**)  $V_{PP}$  is set to 12V, **C**)  $V_{PP}$  = 3.3V (from 12V), **D**)  $V_{PP}$  is disabled, **E**)  $V_{PP}$  is programmed to 5V, **F**)  $V_{PP}$  is set to 12V, **G**)  $V_{PP}$  is programmed to 5V, **H**)  $V_{PP}$  is disabled.

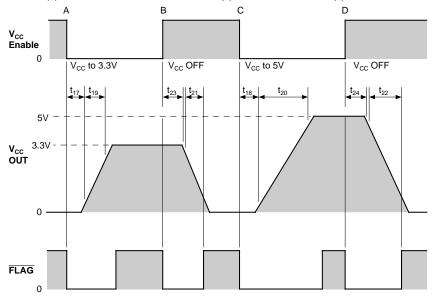

Figure 3.  $V_{CC}$  Timing Diagram

$V_{CC}$  Enable is shown generically.  $R_L = 10\Omega$ . Refer to the serial control timing diagrams for specific control logic input. At time **A**)  $V_{CC}$  is programmed to 3.3V, **B**)  $V_{CC}$  is disabled, **C**)  $V_{CC}$  is programmed to 5V, **D**)  $V_{CC}$  is disabled.

# AIC2564A-0 Logic Table

| 102 | 2564/                        | ٦    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      | IVIIC                                                             |

|-----|------------------------------|------|-----|------------------|-----|------|------|------|------|------|-----|-----|----|------|-----|------------------|-----|------|-----|------------------|-----|------|-----|-----|----|------|------|------|------|------|-----|------------------|-----|------|-------------------------------------------------------------------|

|     | A V <sub>CC</sub> OUT        | Hi-Z | *\0 | 1*\0             | *\0 | *\0  | 3.3V | 3.3V | 3.3V | 3.3V | 5V  | 5V  | 5V | 5V   | *\0 | 100              | *\0 | *\0  |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                                   |

|     | A V <sub>PP</sub> OUT        | Z-iH | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z | *\0  | 12V  | 3.3V | H-Z  | *\0 | 12V | 20 | Hi-Z | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                                   |

|     | B V <sub>CC</sub> OUT        | Hi-Z |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | *\0 | 1*\0             | *\0 | *\0  | 20  | 5V  | 2V | 2V   | 3.3V | 3.3V | 3.37 | 3.3V | *\0 | 1*\0             | *\0 | *\0  |                                                                   |

|     | B V <sub>PP</sub> OUT        | Hi-Z |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z | *\0 | 12V | 2V | Hi-Z | *\0  | 12V  | 3.3V | Hi-Z | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z |                                                                   |

|     | D0<br>A V <sub>PP_PGM</sub>  | ×    | 0   | _                | 0   | -    | 0    | -    | 0    | -    | 0   | _   | 0  | -    | 0   | _                | 0   | -    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                                   |

|     | D1<br>A V <sub>PP_</sub> vcc | ×    | 0   | 0                | _   | _    | 0    | 0    | _    | _    | 0   | 0   | _  | _    | 0   | 0                | -   | -    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                                   |

|     | D2<br>A V <sub>CC</sub> 3    | ×    | 0   | 0                | 0   | 0    | _    | _    | _    | _    | 0   | 0   | 0  | 0    | _   | _                | -   | -    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                                   |

|     | D3<br>A V <sub>CC</sub> 5    |      | 0   | 0                | 0   | 0    | 0    | 0    | 0    | 0    | -   | _   | -  | _    | ~   | _                | -   | -    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      | ecification.                                                      |

|     | D4<br>B V <sub>PP_PGM</sub>  | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | _                | 0   | _    | 0   | 1   | 0  | 1    | 0    | 1    | 0    | _    | 0   | _                | 0   | _    | ne PC Card Spe                                                    |

|     | D5<br>B V <sub>PP_VCC</sub>  | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | 0                | _   | _    | 0   | 0   | 1  | 1    | 0    | 0    | 1    | _    | 0   | 0                | 1   | _    | <sup>†</sup> illegal state per <i>The PC Card Specification</i> . |

|     | D6<br>B V <sub>CC</sub> 3    | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | 0                | 0   | 0    | _   | _   | 1  | 1    | 0    | 0    | 0    | 0    | _   |                  | 1   | _    |                                                                   |

| ן י | $^{ m D7}$ B $^{ m Cc}$ 5    | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | 0                | 0   | 0    | 0   | 0   | 0  | 0    | 1    | 1    | 1    | _    | 1   | _                | 1   | _    | = don't care, * clamped to ground,                                |

|     | D8<br>SHDN                   | 0    | 1   | _                | -   | _    | _    | _    | _    | _    | -   | _   | _  | _    | _   | _                | -   | -    | 7   | _                | -   | _    | -   | 1   | 1  | 1    | 1    | 1    | 1    | -    | _   | _                | 1   | _    | ( = don't care                                                    |

| Ø        |

|----------|

| <u> </u> |

| a        |

| _        |

| ပ        |

| ogic     |

| ŏ        |

| Ĭ        |

|          |

| _        |

| 7        |

| Ą-1      |

| 4A-1     |

| 564A-1   |

| 2564A-1  |

| C2564A-1 |

| - | 2004/                       | •    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      | VIIC                                           |

|---|-----------------------------|------|-----|------------------|-----|------|------|------|------|------|-----|-----|----|------|-----|------------------|-----|------|-----|------------------|-----|------|-----|-----|----|------|------|------|------|------|-----|------------------|-----|------|------------------------------------------------|

|   | A V <sub>CC</sub> OUT       | Hi-Z | *\0 | 1*\0             | *\0 | *\0  | 3.3V | 3.3V | 3.3V | 3.3V | 5V  | 5V  | 5V | 5V   | *\0 | 1V0              | *\0 | *\0  |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                |

|   | A V <sub>PP</sub> OUT       | Hi-Z | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z | *\0  | 12V  | 3.3V | 20   | *\0 | 12V | 20 | 3.3V | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                |

|   | B V <sub>CC</sub> OUT       | H-Z  |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | *\0 | 1*\\0            | *\0 | *\0  | 2\  | 2\  | 57 | 2\   | 3.3V | 3.3V | 3.3V | 3.3V | *\0 | 1*\0             | *\0 | *\0  |                                                |

|   | B V <sub>PP</sub> OUT       | Hi-Z |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z | *\0 | 12V | 5V | 3.3V | *\0  | 12V  | 3.3V | 5V   | *\0 | 12V <sup>†</sup> | *\0 | Hi-Z |                                                |

|   | D0<br>A V <sub>PP_PGM</sub> | ×    | 0   | _                | 0   | _    | 0    | -    | 0    | -    | 0   | -   | 0  | -    | 0   | _                | 0   | -    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                |

|   | D1<br>A V <sub>PP_VCC</sub> | ×    | 0   | 0                | -   | _    | 0    | 0    | _    | _    | 0   | 0   | ~  | _    | 0   | 0                | -   | ~    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                |

|   | D2<br>A V <sub>CC</sub> 3   | ×    | 0   | 0                | 0   | 0    | _    | _    | _    | _    | 0   | 0   | 0  | 0    | -   | _                | _   | -    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      |                                                |

|   | D3<br>A V <sub>CC</sub> 5   | ×    | 0   | 0                | 0   | 0    | 0    | 0    | 0    | 0    | _   | _   | _  | _    | -   | _                | _   | -    |     |                  |     |      |     |     |    |      |      |      |      |      |     |                  |     |      | cification.                                    |

|   | D4<br>B V <sub>PP_PGM</sub> | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | _                | 0   | _    | 0   | _   | 0  | ~    | 0    | 1    | 0    | _    | 0   | _                | 0   | 1    | † illegal state per The PC Card Specification. |

|   | D5<br>B V <sub>PP_VCC</sub> | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | 0                | _   | _    | 0   | 0   | _  | _    | 0    | 0    | _    | _    | 0   | 0                | 1   | _    | egal state per Th                              |

|   | D6<br>B V <sub>CC</sub> 3   | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | 0                | 0   | 0    | _   | _   | _  | _    | 0    | 0    | 0    | 0    | _   | _                | 1   | 1    |                                                |

|   | D7<br>B V <sub>CC</sub> 5   | ×    |     |                  |     |      |      |      |      |      |     |     |    |      |     |                  |     |      | 0   | 0                | 0   | 0    | 0   | 0   | 0  | 0    | _    | 1    | 1    | 1    | 1   | _                | 1   | 1    | e, * clamped to ground,                        |

|   | D8<br>SHDN                  | 0    | _   | _                | -   | _    | _    | -    | _    | _    | -   | _   | -  | _    | -   | _                | -   | _    | _   | _                | _   | _    | _   | _   | _  | -    | _    | 1    | _    | _    | 1   | _                | 1   | _    | = don't care,                                  |

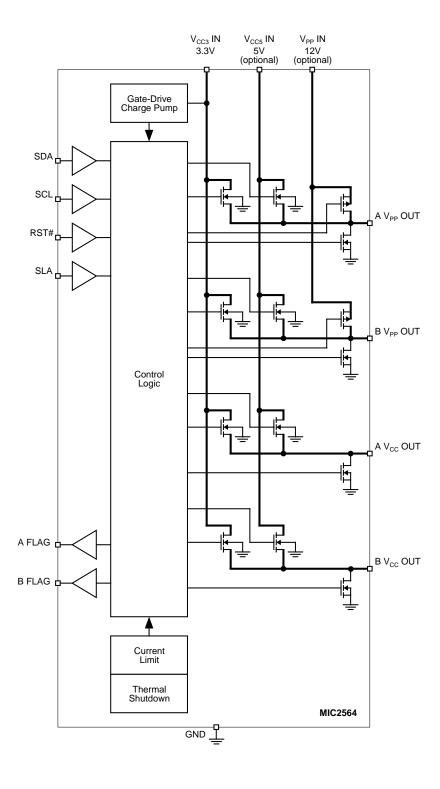

# **Functional Diagram**

# **Applications Information**

PC Card power control for two sockets is easily accomplished using the MIC2564A PC Card/CardBus power controller. Control commands from a three-wire (plus Reset) serial bus determine  $V_{CC}$  and  $V_{PP}$  output voltages and select standby or operate mode.

$V_{CC}$  outputs of 3.3V and 5V at the maximum allowable PC Card current are supported. The  $V_{CC}$  outputs also support GND (0V) and high-impedance states. The  $V_{PP}$  outputs support  $V_{PP}$  (12V),  $V_{CC}$  voltages (3.3V or 5V), GND (0V), or high impedance. When the  $V_{CC}$  = Hi-Z (high impedance) condition is selected, the device switches into sleep mode and draws only leakage current.

Full protection during hot switching is provided which prevents feedback from the  $V_{CC}$  output (for example, from the 5V supply into the 3.3V supply) by locking out the low voltage switch until the initial switch's gate voltage drops below 0.7V.

MIC2564A internal logic and MOSFET drive circuitry is powered from the  $V_{\rm CC3}$  input and internal charge-pump voltage multipliers. Switching speeds are carefully controlled to prevent damage to sensitive loads and meet all PC Card Specification timing requirements, including those for the CardBus option.

### **Supply Bypassing**

The MIC2564A is a switch and has no stability problems; however, supply bypass capacitors are recommended to reduce inductive transients and improve output ripple. As all internal device logic and comparison functions are powered from the  $V_{CC3}$  input, the power supply quality on this line is the most important. Micrel recommends placing  $1\mu F$  surfacemount ceramic (low ESR) capacitors from  $V_{CC3}$  IN and  $V_{CC5}$  IN pins to ground and two  $0.1\mu F$  surface-mount ceramic capacitors, one from each  $V_{PP}$  IN pin, to ground. Also, the  $V_{CC}$  OUT and  $V_{PP}$  OUT pins may use  $0.01\mu F$  to  $0.1\mu F$  capacitors for noise reduction and to reduce the chance of ESD (electrostatic discharge) damage.

### **Power Status Feedback (Flags)**

Two flag outputs monitor the  $V_{CC}$  and  $V_{PP}$  output voltages on both slot A and B, falling low when the voltage is not proper. Use of these open-drain flag outputs is optional; if they are used, a pull-up resistor to either the 3.3V or 5V supply is required. Unused flag outputs may be left open.

### **PC Card Slot Implementation**

The MIC2564A is designed for full compatibility with the Personal Computer Memory Card International Association (PCMCIA) PC Card Specification including the CardBus and Zoom Video (ZV) options.

When a PC card is initially inserted, it should receive  $V_{CC}$  (3.3V  $\pm$  0.3V or 5.0V  $\pm$ 5%). The initial voltage is determined by a combination of mechanical socket keys and voltage sense pins. The card sends a handshaking data stream to the logic controller, which then determines if this card requires  $V_{PP}$  and if the card is designed for dual  $V_{CC}$ . If the card is compatible with, and requires, a different  $V_{CC}$  level, the logic controller commands the power controller to make this change by disabling  $V_{CC}$ , waiting at least 100ms, and then republing the other  $V_{CC}$  voltage

If no card is inserted, or the system is in sleep mode, the logic controller commands the MIC2564A to shut down  $V_{CC}$ . This also places the switch into a shutdown (sleep) mode, where current consumption drops to nearly zero, with only tiny CMOS leakage currents flowing.

Internal device control logic, MOSFET drive and bias voltage is powered from  $V_{CC3}$  IN. The high voltage bias is generated by an internal charge pump multiplier. Input logic threshold voltages are compatible with common PC Card logic controllers using either 3.3V or 5V supplies.

### PC Card Voltage Regulation

The MIC2564A has been designed to meet or exceed PC Card voltage regulation specifications. The on-resistance of the FET switches will meet regulation requirements at 600mA and 1A respectively for  $V_{CC} = 5V \pm 3\%$  and 3.3V  $\pm 3\%$ .

### Flash Memory Implementation

When programming flash memory (standard +12V flash memories), the PC Card slot logic controller enables  $V_{PP}$  on the MIC2564A, which connects  $V_{PP}$  IN (nominally +12V) to  $V_{PP}$  OUT. The low on-resistance of the MIC2564A switch allows using a small bypass capacitor on the  $V_{PP}$  OUT pins, with the main filtering performed by a large filter capacitor on  $V_{PP}$  IN. (Usually the main power supply filter capacitor is sufficient.) Using a small-value capacitor such as  $0.1\mu F$  on the output causes little or no timing delays.

The  $V_{PP}$  OUT transition from  $V_{CC}$  to 12.0V typically takes 200 $\mu$ s. After programming is completed, the logic controller signals to the MIC2564A, which then reduces  $V_{PP}$  OUT to the  $V_{CC}$  level. Break-before-make switching action and controlled rise times reduce switching transients and lower current spikes through the switch.

### **Output Current and Protection**

The MIC2564A meets or exceeds all PCMCIA specifications. MIC2564A output switches are capable of passing the maximum current needed by any PC Card. For system and card protection, output currents are internally limited. For full system protection, long term (longer than a few milliseconds) output short circuits invoke overtemperature shutdown, protecting the MIC2564A, the system power supplies, the card socket pins, board traces, and the PC Card. Individual internal status registers for each slot indicate when power problems exist.

### Control Bus Interface Overview

The MIC2564A power controller communicates with a logic controller (host adapter) via a 3-wire serial interface. A fourth control line attaches to the system reset line (RST#) and places all MIC2564A switches in the high impedance (off) state. The reset function is active low.

Figure 4. Generic "3-Wire" Serial Control Interface

Figure 5. Cirrus Logic CL-PD6832 and CL-PD6833 Interface

Figure 6. O<sub>2</sub> Micro OZ6833 and OZ6933

Figure 7. O<sub>2</sub> Micro OZ6860

# **Package Dimensions**

24-pin SSOP (SM)