#### 80V 8-Channel Addressable Low-Side Driver

### **General Description**

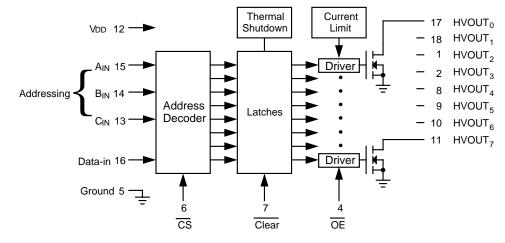

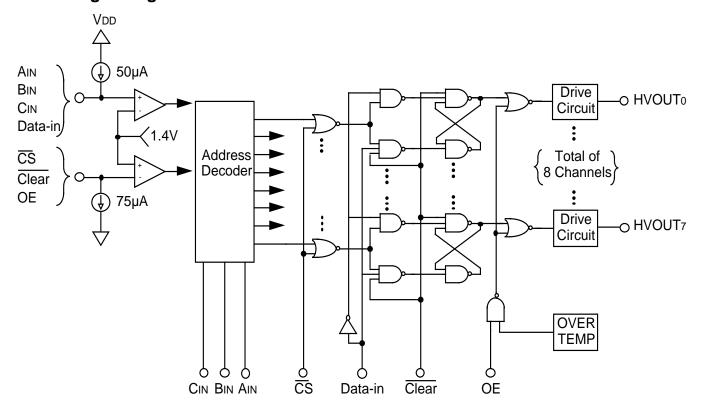

The MIC4807 is an 80V, 8-channel, addressable low side driver with latches and TTL/CMOS compatible logic inputs. Each logic input is composed of a comparator with a 1.4V bandgap-derived reference serving as the trip point. The addresses (A $_{\text{IN}}$ , B $_{\text{IN}}$ , and C $_{\text{IN}}$ ) and Data-in logic inputs have an internal 50 $\mu$ A pull-up current source, while the Output Enable (OE), Chip Select (CS), and Clear logic inputs have an internal 75 $\mu$ A pull-down sink. If the logic lines to the MIC4807 are severed, these currents guarantee that the outputs will turn OFF.

Individual latches in the MIC4807 are selected by a binary address presented at inputs  $A_{IN}$ ,  $B_{IN}$  and  $C_{IN}$ . Data-in is directed to the addressed latch while CS is held low, allowing an individual output to be pulse-width modulated. When  $\overline{CS}$  is set high again, the last Data-in is stored in the latch. If Data-in="1", the addressed output is turned on, and if Data-in="0", the addressed output is turned off.

Information presented to Data-in and the address inputs is transferred to the latches while  $\overline{\text{CS}}$  is pulled low. For application, where several outputs must be (Continued)

#### **Features**

- 4.5V to 16V Operation

- Eight 80V 100mA Outputs

- Off-state Leakage less than 10μA at 25°C

- Short-Circuit Proof

- · Thermal Shutdown with Hysteresis

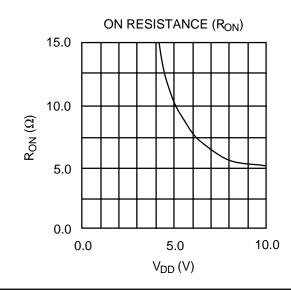

- DMOS Output Devices (R<sub>ON</sub> ≤ 7Ω at 25°C)

### **Applications**

- Lamp Drivers

- Solenoid Drivers

- Display Drivers

- -Electroluminescent

- -Vacuum Fluorescent

- -Plasma

- Relay Drivers

- Print Head Drivers

- Heater Drivers

- Power Semiconductor Drivers

- Security Systems

- Environmental Controls

- Process Controllers

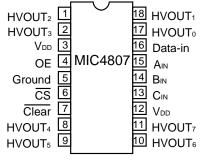

### Pin Diagram

### **Ordering Information**

| Part<br>Number | Operating Temperature-Range | Package            |  |  |

|----------------|-----------------------------|--------------------|--|--|

| MIC4807BN      | -40°C to 85°C               | 18-Pin Plastic DIP |  |  |

### **Block Diagram**

### General Description (Continued)

turned on simultaneously, Gray Code address sequencing  $\underline{can}$  be applied to Ain, Bin, Cin, while Data-in is held high and  $\overline{CS}$  is held low. Data-in will be transferred to each address in turn, without the need to toggle  $\overline{CS}$ . Similarly, a set of outputs could be simultaneously turned off by setting Data-in low. Gray Code ensures that no intermediate addresses are inadvertently accessed. A typical Gray Code is 0, 1, 3, 2, 6, 7, 5, 4.

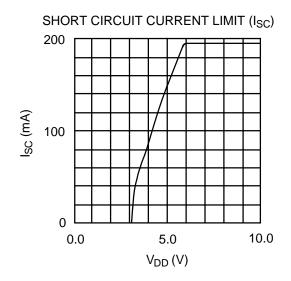

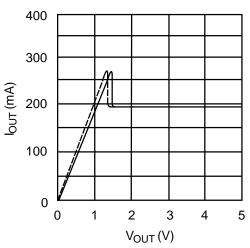

Each output drive circuit has a high-voltage, power DMOS device configured as a transconductance loop. This loop limits the output current to typically 200mA. While current limiting keeps the output device within its allowable safe-operating area (SOA), the power dissipation may be excessive. Long-term survival is guaranteed by thermal shutdown.

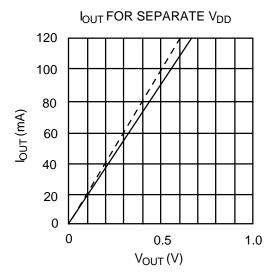

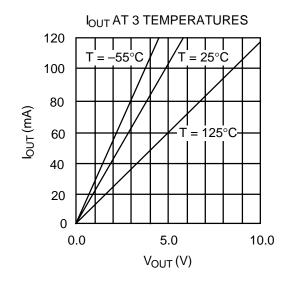

When operated below current limit, the outputs appear as small-valued resistors (typically  $5.1\Omega$  at  $25^{\circ}$ C) connected to ground. The "ON" resistance (R<sub>ON</sub>) has a strong, positive temperature coefficient (approximately 7500 ppm/°C) which promotes current sharing if two or more outputs are paralleled.

### Absolute Maximum Ratings (Notes 1, 2 and 3)

Output Voltage (V<sub>OUT</sub>, OFF) Supply Voltage (V<sub>DD</sub>) 16.5V Logic Input Voltage (V<sub>IN</sub>) -0.3V TO  $V_{DD} + 0.3$ Continuous Output Current (I<sub>OUT</sub>) Internally Limited Internally Limited Power Dissipation (P<sub>D</sub>, Note 2) -40°C to +85°C Ambient Temperature  $(T_A)$ : Maximum Junction Temperature  $(T_{JMAX})$ 150°C -65°C to +150°C Storage Temperature  $\theta_{\mathsf{JA}}$  - Plastic DIP 130°C/W

# **Electrical Characteristics:** (Note 6) MIC4807BN, $T_A = 25^{\circ}C$ , $V_{DD} = 15V$ unless otherwise specified (see Test Circuit).

| Symbol              | Parameter                                                                                 | Conditions                                                                                        | Min  | Тур          | Max         | Units    |

|---------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|--------------|-------------|----------|

| V <sub>DD</sub>     | Supply Voltage                                                                            |                                                                                                   | 4.5  |              | 16          | V        |

| I <sub>DD</sub>     | Supply Current                                                                            | OE = L (Note 3)<br>OE = H (Note 4)                                                                |      | 5.5<br>1.5   | 10<br>3     | mA<br>mA |

| V <sub>IN</sub> (0) | Logic Input Voltage                                                                       | 4.5V ≤ V <sub>DD</sub> ≤ 16V                                                                      |      |              | 0.8         | V        |

| V <sub>IN</sub> (1) |                                                                                           |                                                                                                   | 2.0  |              |             | V        |

| I <sub>IN</sub> (0) | Logic Input Current for A <sub>IN</sub> , B <sub>IN</sub> , C <sub>IN</sub> , and Data-in | V <sub>IN</sub> = 0V                                                                              | -150 | -70          | -25         | μА       |

| I <sub>IN</sub> (1) | Logic Input Current for CS,<br>OE, and Clear                                              | $V_{IN} = V_{DD}$                                                                                 | 25   | 130          | 250         | μА       |

| lout                | Output Leakage Current                                                                    | OE = 0V, V <sub>OUT</sub> = 80V                                                                   |      | 1            | 10          | μА       |

| R <sub>ON</sub>     | Output "ON" Resistance                                                                    | Output is ON, V <sub>OUT</sub> = 0.7V,V <sub>DD</sub> = 10V                                       |      | 5.1          | 7           | Ω        |

| Isc                 | Short Circuit Current                                                                     | Output is ON< V <sub>OUT</sub> = 50V<br>10V ≤ V <sub>DD</sub> ≤ 15V (Note 5)                      | 140  | 190          | 250         | mA       |

| V <sub>OUT</sub>    | Output Voltage (OFF)                                                                      |                                                                                                   |      |              | 80          | V        |

| Vout                | Output Voltage (ON)                                                                       | $I_{OUT} = 50 \text{mA}, V_{DD} = 10 \text{V}$<br>$I_{OUT} = 100 \text{mA}, V_{DD} = 10 \text{V}$ |      | 0.26<br>0.51 | 0.35<br>0.7 | V        |

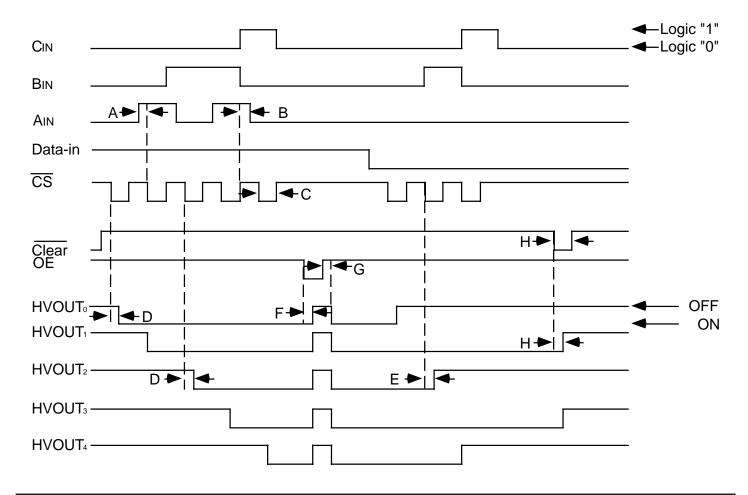

|                     | Data and Address<br>Set-up Time                                                           | V <sub>DD</sub> = 10V for all timing tests<br>(A, see <b>Timing Diagram</b> )                     | 400  |              |             | ns       |

|                     | Data and Address<br>Hold Time                                                             | (B)                                                                                               | 50   |              |             | ns       |

|                     | CS Pulse Width                                                                            | (C)                                                                                               | 500  |              |             | ns       |

|                     | Turn-on Delay                                                                             | (D)                                                                                               |      |              | 2.5         | ns       |

## **Electrical Characteristics:** (Note 6) T<sub>A</sub> = 25°C, V<sub>DD</sub> = 15V unless otherwise specified (see Test Circuit).

| Symbol | Parameter                       | Conditions | Min | Тур | Max | Units |

|--------|---------------------------------|------------|-----|-----|-----|-------|

|        | Turn-Off Delay                  | (E)        |     |     | 2.5 | μs    |

|        | Output Disable<br>Response Time | (F)        |     |     | 2   | μs    |

|        | Output Enable<br>Response Time  | (G)        |     |     | 2   | μs    |

|        | Clear Response Time             | (H)        |     |     | 2.5 | μs    |

|        | Clear Pulse Width               | (1)        | 500 |     |     | ns    |

# **Electrical Characteristics:** (Note 6) $T_A = -55^{\circ}C$ to $+125^{\circ}C$ , $V_{DD} = 15V$ unless otherwise specified (see Test Circuit).

| Symbol              | Parameter                                                                                    | Parameter Conditions                                                                              |      |     |            |        |  |  |

|---------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|-----|------------|--------|--|--|

| V <sub>DD</sub>     | Supply Voltage                                                                               |                                                                                                   | 4.5  |     | 16         | V      |  |  |

| I <sub>DD</sub>     | Supply Current                                                                               | OE = L (Note 3) OE = H (Note 4)  15 4                                                             |      |     |            |        |  |  |

| V <sub>IN</sub> (0) | Logic Input Voltage                                                                          |                                                                                                   | 0.8  | V   |            |        |  |  |

| V <sub>IN</sub> (1) |                                                                                              |                                                                                                   | 2.0  |     |            | V      |  |  |

| I <sub>IN</sub> (0) | Logic Input Current for A <sub>IN</sub> ,<br>B <sub>IN</sub> , C <sub>IN</sub> , and Data-in | V <sub>IN</sub> = 0V                                                                              | -250 |     | -10        | μА     |  |  |

| I <sub>IN</sub> (1) | Logic Input Current for CS, OE, and Clear                                                    | $V_{IN} = V_{DD}$                                                                                 | 25   |     | 400        | μА     |  |  |

| I <sub>OUT</sub>    | Output Leakage Current                                                                       | OE = 0V, V <sub>OUT</sub> = 80V                                                                   |      | 5.1 | 7          | μА     |  |  |

| R <sub>ON</sub>     | Output "ON" Resistance                                                                       | Output is ON, V <sub>OUT</sub> =0.7V,V <sub>DD</sub> =10V                                         |      |     | 12         | Ω      |  |  |

| I <sub>SC</sub>     | Short Circuit Current                                                                        | ort Circuit Current Output is $ON < V_{OUT} = 50V$ 100 30 $10V \le V_{DD} \le 15V$ (Note 5)       |      |     |            |        |  |  |

| Vout                | Output Voltage (OFF)                                                                         |                                                                                                   |      |     | 80         | V      |  |  |

| Vout                | Output Voltage (ON)                                                                          | I <sub>OUT</sub> = 50mA, V <sub>DD</sub> = 10V<br>I <sub>OUT</sub> = 100mA, V <sub>DD</sub> = 10V |      |     | 0.6<br>1.2 | V<br>V |  |  |

|                     | Data and Address<br>Set-up Time                                                              | V <sub>DD</sub> = 10V for all timing tests<br>(A, see <b>Timing Diagram</b> )                     | 700  |     |            | ns     |  |  |

|                     | Data and Address<br>Hold Time                                                                | (B)                                                                                               | 50   |     |            | ns     |  |  |

|                     | CS Pulse Width                                                                               | (C)                                                                                               | 1000 |     |            | ns     |  |  |

|                     | Turn-on Delay                                                                                | (D)                                                                                               |      |     | 5          | μs     |  |  |

### **Electrical Characteristics:** (Note 6) $T_A = 25$ °C, $V_{DD} = 15$ V unless otherwise specified (see Test Circuit).

| Symbol | Parameter                       | Conditions | Min  | Тур | Max | Units |

|--------|---------------------------------|------------|------|-----|-----|-------|

|        | Turn-Off Delay                  | (E)        |      |     | 5   | μs    |

|        | Output Disable<br>Response Time | (F)        |      |     | 4   | μs    |

|        | Output Enable<br>Response Time  | (G)        |      |     | 4   | μs    |

|        | Clear Response Time             | (H)        |      |     | 5   | μs    |

|        | Clear Pulse Width               | (I)        | 1000 |     |     | ns    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Electrical specifications do not apply when operating the device beyond its specified operating ratings.

**Note 2:** The junction temperature is internally limited by a thermal shutdown circuit. The maximum power dissipation is a function of  $T_{JMAX}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$ . If this dissipation is exceeded, the die temperature will rise above 150°C, and the MIC4807 will go into thermal shutdown.

Note 3: All outputs are off when OUTPUT ENABLE is pulled low.

Note 4: All outputs are turned on during this test.

Note 5: Pulse testing is used to avoid thermal shutown.

**Note 6:** Minimum and Maximum limits are tested and 100% guaranteed over the temperature range specified. Typicals are measured at 25°C and represent the most likely parametric norm.

### **Timing Diagram**

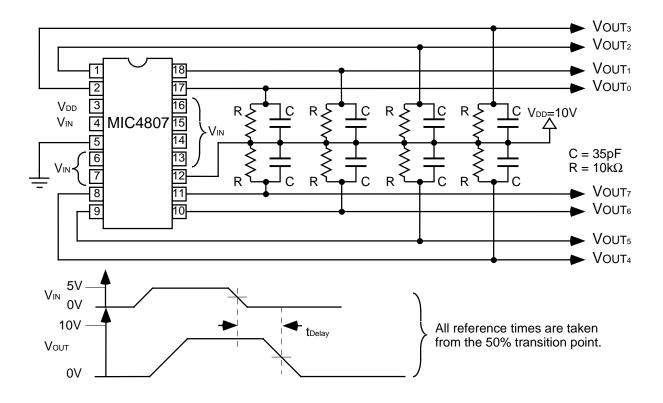

### **Test Circuit and AC Waveform Measurement Standards**

### **Equivalent Logic Diagram**

### **Truth Table**

| CS | Clear | Data-In | CIN | B <sub>IN</sub> | A <sub>IN</sub> | ΟE | HVOUT <sub>0</sub> | HVOUT <sub>1</sub> | HVOUT <sub>2</sub> | HVOUT <sub>3</sub> | HVOUT <sub>4</sub> | HVOUT <sub>5</sub> | HVOUT <sub>6</sub> | HVOUT <sub>7</sub> | Functional Mode            |  |

|----|-------|---------|-----|-----------------|-----------------|----|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------------|--|

| Х  | L     | Х       | Х   | Х               | Х               | Х  | Н                  | Н                  | Н                  | Н                  | Н                  | Н                  | Н                  | Н                  | Clear                      |  |

| Н  | Н     | х       | Х   | Х               | Х               | Н  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | Memory                     |  |

| L  | Н     | D       | L   | L               | L               | Н  | D                  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | Address HVOUT <sub>0</sub> |  |

| L  | Н     | D       | L   | L               | Н               | Н  | Р                  | D                  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | Address HVOUT <sub>1</sub> |  |

| ٦  | Н     | D       | L   | Н               | L               | н  | Р                  | Р                  | D                  | Р                  | Р                  | Р                  | Р                  | Р                  | Address HVOUT <sub>2</sub> |  |

| L  | Н     | D       | L   | Н               | Н               | Н  | Р                  | Р                  | Р                  | D                  | Р                  | Р                  | Р                  | Р                  | Address HVOUT <sub>3</sub> |  |

| L  | Н     | D       | н   | L               | L               | н  | Р                  | Р                  | Р                  | Р                  | D                  | Р                  | Р                  | Р                  | Address HVOUT <sub>4</sub> |  |

| L  | Н     | D       | Н   | L               | Н               | Н  | Р                  | Р                  | Р                  | Р                  | Р                  | D                  | Р                  | Р                  | Address HVOUT <sub>5</sub> |  |

| ٦  | Н     | D       | Н   | Н               | L               | н  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | D                  | Р                  | Address HVOUT <sub>6</sub> |  |

| L  | Н     | D       | Н   | Н               | Н               | Н  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | Р                  | D                  | Address HVOUT <sub>7</sub> |  |

| Х  | Х     | х       | х   | Х               | х               | L  | Н                  | Н                  | н                  | Н                  | Н                  | Н                  | Н                  | Н                  | Blanking                   |  |

$\begin{tabular}{lll} $L = Low Logic Level & $X = Don't Care \\ $H = High Logic Level & $P = Previous State \\ \end{tabular}$

D = Data (High or Low)

### Typical DC Output Characteristics for the "On" State:

$(V_{DD} = 10V \text{ and } T_A = 25^{\circ}C \text{ unless other wise specified})$

$$V_{DD} = 10V$$

$V_{DD} = 15V$

SHORT CIRCUIT CURRENT

400

300

100

0 20 40 60 80

Vout (V)

### **Pin Description**

| Pin No.                        | Pin Name                                      | Functional Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                              | Ground                                        | Electrical ground to chip substrate.                                                                                                                                                                                                                                                                                                                                                                   |

| 12                             | V <sub>DD</sub>                               | Positive logic supply voltage (10V-15V).                                                                                                                                                                                                                                                                                                                                                               |

| 1, 2, 8,<br>9,10, 11,<br>17,18 | HVOUT <sub>0</sub> through HVOUT <sub>7</sub> | These are the high voltage (HV) open outputs, each of which is capable of sinking 100mA when switched on, and standing off 80V when switched off. In addition, each output channel is equipped with an analog current limiter to protect it from shorts to the positive high voltage supply. When an output is shorted (up to 80V), a maximum of 225mA (200mA nominal) will flow through it to ground. |

| 13, 14, 15                     | $C_{IN}$ , $B_{IN}$ , & $A_{IN}$              | When these inputs are combined together they form the BCD address used to select the desired output. Each input is TTL compatible with an internal pull-up current source of 50mA.                                                                                                                                                                                                                     |

| 6                              | CS                                            | When $\overline{\text{CS}}$ is at logic "0" the device is actively addressed, and when $\overline{\text{CS}}$ is at logic "1" the decoded address and input Data are inhibited, making the part unaddressable. $\overline{\text{CS}}$ is TTL compatible with an internal pull-down current sink of 75 $\mu$ A.                                                                                         |

| 7                              | Clear                                         | Clear resets all the outputs to the off state when pulled to logic "0", and is TTL compatible with an internal pull-down current sink of 75μA.                                                                                                                                                                                                                                                         |

| 16                             | Data-in                                       | Data-in determines the state of the output being addressed. When Data-in is at logic "0" the addressed output is turned off, and when Data-in is at logic "1" the addressed output is turned on. Data-in is TTL compatible with an internal pull-up current source of 50µA.                                                                                                                            |

| 4                              | OE                                            | OE allows the bank of eight outputs to be duty cycled together. When OE is at logic "1" the outputs are enabled to follow their respective latches, and when OE is at logic "0" all the outputs are turned off. OE is TTL Compatible with a pull-down current sink of $75\mu A$ .                                                                                                                      |