# Dual 1 W Output AMOLED Driver Supply

The NCP5810D is a dual-output DC/DC converter which can generate both a positive and a negative voltage. Both PWM converters achieve high efficiency for portable application. Thanks to the high output voltage accuracy and signal integrity the NCP5810D is particularly suitable for powering applications such as AMOLED display drivers. The output voltage of the inverter is fully configurable using external feedback resistors, where the output voltage of the boost is internally fixed. The switching regulator operates at 1.75 MHz which allows the use of small inductors and ceramic capacitors. In addition both converters are internally compensated which simplifies the design and reduces the PCB component count. Cycle-by-cycle peak current limit and thermal shut down provide value added features to protect the device. The NCP5810D is housed in low profile space-efficient 3x3 mm UDFN package.

#### **Features**

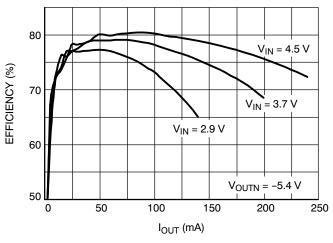

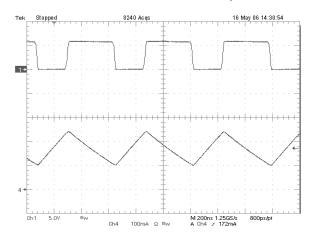

- High Overall Efficiency: 83% (Refer to Figure 4)

- Low Noise 1.75 MHz PWM DC/DC Converter

- Positive Output Fixed + 4.6 V

- Negative Output from 2.0 to 15.0 V

- High Output Voltage Accuracy

- Excellent Line Transient Rejection

- Soft Start to Limit Inrush Current

- Enable Control Facility with True-Cutoff

- Out-of-Regulation Protection

- Small UDFN 3x3 mm Packages

- These are Pb-Free Devices

#### **Typical Applications**

- AMOLED Driver Supply

- Cellular Phones

- Digital Cameras

- Personal Digital Assistant and Portable Media Player

1

• GPS

#### ON Semiconductor®

http://onsemi.com

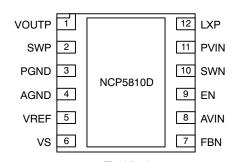

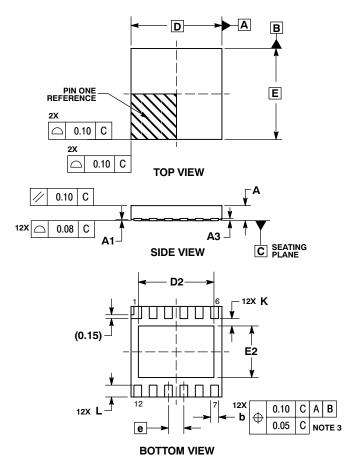

12 PIN UDFN MU SUFFIX CASE 517AM

#### **MARKING DIAGRAM**

5810D = Device Code A = Assembly Location

Y = Year

W = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

(Top View) 12-pin 3 x 3 x 0.55 mm UDFN

Exposed pad must be soldered to PCB Ground plane

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

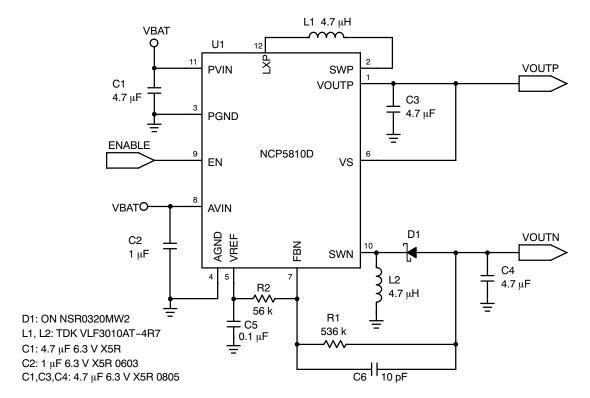

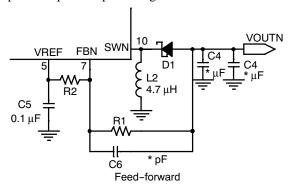

**Figure 1. Typical Application Circuit**

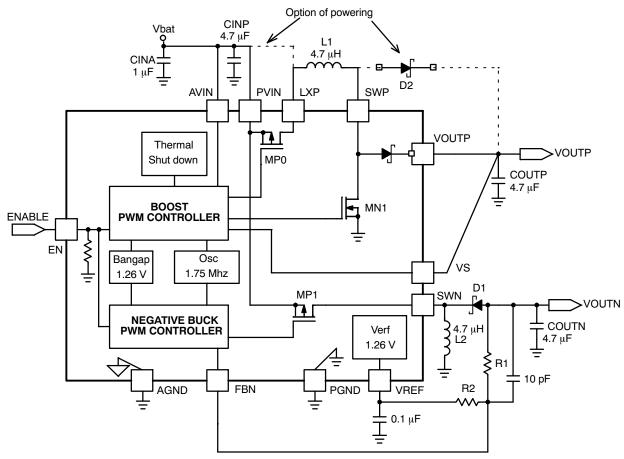

Figure 2. Simplified Block Diagram

#### PIN FUNCTION DESCRIPTION

| Pin | Pin Name | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                               |  |

|-----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | VOUTP    | OUTPUT | <b>Positive Power Output:</b> A filter capacitor is necessary on this pin for the stability of the loop, to smooth the current flowing into the load, and limit the noise created by the fast transients present in this circuitry. A 4.7 $\mu$ F ceramic bypass capacitor to GND is recommended. Care must be observed to avoid EMI through the PCB copper tracks connected to this pin. |  |

| 2   | SWP      | POWER  | <b>Switch LXP:</b> Positive power switch pin where one end of the L1 inductor is connected. Typical application uses a 4.7 $\mu$ H inductor.                                                                                                                                                                                                                                              |  |

| 3   | PGND     | POWER  | <b>Power Ground:</b> This pin is the power ground and carries the high switching current. A high quality ground must be provided to avoid any noise spikes/uncontrolled operation. Care must be observed to avoid high-density current flow in a limited PCB copper track.                                                                                                                |  |

| 4   | AGND     | POWER  | Analog Ground: This pin is the analog ground of the device notably used by VREF.                                                                                                                                                                                                                                                                                                          |  |

| 5   | VREF     | OUTPUT | <b>Voltage Reference:</b> This output provides a 1.265 V voltage reference used notably for the negative feedback resistive network.                                                                                                                                                                                                                                                      |  |

| 6   | VS       | INPUT  | Positive Output Voltage Sense: This pin is the output voltage sense input for the positive boost converter and must be connected to COUTP bypass capacitor.                                                                                                                                                                                                                               |  |

| 7   | FBN      | INPUT  | <b>Feedback Negative:</b> This pin is the feedback voltage input for the negative Buck-Boost inverter. The middle point of a resistive bridge divider must be connected here. The resistive network must be connected between VREF and the anode of external Schottky.                                                                                                                    |  |

| 8   | AVIN     | POWER  | <b>Analog Power Supply:</b> The external voltage supply is connected to this pin. A 4.7 $\mu$ F ceramic capacitor must be connected across this pin and the power ground to achieve the specified output power parameters.                                                                                                                                                                |  |

| 9   | EN       | INPUT  | <b>Enable:</b> An active high logic level on this pin enables the circuit. A built-in pull-down resistor disables the device if the pin is left open. Also in disable condition the device provides a true cut-off from PVIN to VOUTP and SWN.                                                                                                                                            |  |

| 10  | SWN      | INPUT  | Switch Negative: Negative power switch pin where one end of the L2 inductor is connected. Typical application uses a 4.7 $\mu$ H inductor.                                                                                                                                                                                                                                                |  |

| 11  | PVIN     | POWER  | <b>Power Supply:</b> This pin is the power supply of the device. A 4.7 $\mu$ F ceramic capacitor or larger must bypass this input to the ground. This capacitor should be placed as close as possible to this input.                                                                                                                                                                      |  |

| 12  | LXP      | POWER  | <b>Switch LXP:</b> The inductor should be connected between this node and SWP. This output supplies power from PVIN and gives a true-cut off function in disable condition.                                                                                                                                                                                                               |  |

#### **MAXIMUM RATINGS** (Note 1)

| Rating                                                                  | Symbol             | Value                               | Unit    |

|-------------------------------------------------------------------------|--------------------|-------------------------------------|---------|

| AVIN and PVIN Pin: Power Supply Voltage (Note 2)                        | V <sub>BAT</sub>   | 7.0                                 | V       |

| EN Pin: Digital Logic Input (Note 2)                                    | V <sub>EN</sub>    | $-0.3 \le V_{IN} \le V_{BAT} + 0.3$ | V       |

| LXP Pin: Output (Note 2)                                                | $V_{LXP}$          | $-0.3 \le V_{IN} \le V_{BAT} + 0.3$ | V       |

| VREF Pin: Output Reference Voltage (Note 2)                             | $V_{VREF}$         | $-0.3 \le V_{IN} \le V_{BAT} + 0.3$ | V       |

| VS Pin: Input (Note 2)                                                  | V <sub>VS</sub>    | +17                                 | V       |

| SWN Pin: Output (Note 2)                                                | V <sub>SWN</sub>   | -17                                 | V       |

| SWP Pin: Input (Note 2)                                                 | $V_{SWP}$          | 9.8                                 | V       |

| VOUTP Pin: Output (Note 2)                                              | V <sub>VOUTP</sub> | +17                                 | V       |

| FBN Pin: Input (Note 2)                                                 | $V_{FBN}$          | $-0.3 \le V_{IN} \le V_{BAT} + 0.3$ | V       |

| Human Body Model (HBM) ESD Rating are (Note 3)                          | ESD HBM            | 2000                                | V       |

| Machine Model (MM) ESD Rating are (Note 3)                              | ESD MM             | 200                                 | V       |

| Digital Input Voltage<br>Digital Input Current                          | EN                 | $-0.3 \le V_{IN} \le V_{BAT} + 0.3$ | V<br>mA |

| UDFN 3x3 mm package (Notes 6 and 7) Thermal Resistance Junction-to-Case | $R_{	heta JC}$     | 12                                  | °C/W    |

| Operating Ambient Temperature Range                                     | T <sub>A</sub>     | -40 to +85                          | °C      |

| Operating Junction Temperature Range                                    | TJ                 | -40 to +125                         | °C      |

| Maximum Junction Temperature                                            | T <sub>JMAX</sub>  | +150                                | °C      |

| Storage Temperature Range                                               | T <sub>STG</sub>   | -65 to +150                         | °C      |

| Moisture Sensitivity (Note 5)                                           | MSL                | Level 1                             |         |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### NOTES:

- 1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at TA = 25°C

- 2. According to JEDEC standard JESD22-A108B.

- This device series contains ESD protection and passes the following tests: Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22-A114 for all pins. Machine Model (MM) ±200 V.

- Latchup Current Maximum Rating: ±100 mA per JEDEC standard: JESD78., class II

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

- The thermal shutdown set to 165°C (typical) avoids irreversible damage on the device due to power dissipation.

The R<sub>0CA</sub> is dependent on the PCB heat dissipation. The maximum power dissipation (P<sub>D</sub>) is dependent on the min input voltage, the max output current and external components selected.

$$R_{\theta CA} = \frac{125 - T_A}{P_D} - R_{\theta JC}$$

**ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between -40°C to +85°C and  $V_{IN}$  between 2.7 V to 4.6 V (Unless otherwise noted). Typical values are referenced to  $T_A$  = +25°C and  $V_{IN}$  = 3.7 V (Unless otherwise noted)

| Characteristic                                                                                          | Symbol                                 | Min         | Тур           | Max        | Unit    |

|---------------------------------------------------------------------------------------------------------|----------------------------------------|-------------|---------------|------------|---------|

| BOOST REGULATOR                                                                                         |                                        |             |               |            |         |

| Positive Operational Output Voltage Range                                                               | V <sub>OUTP</sub>                      | 4.55        | 4.6           | 4.65       | V       |

| Maximum Inductor Peak Current                                                                           | I <sub>PEAKP_MAX</sub>                 | 630         | 800           | 900        | mA      |

| Switches P0 ON Resistance                                                                               | P0 <sub>MOS</sub><br>R <sub>DSON</sub> | -           | 320           | 640        | mΩ      |

| Switches N1 ON Resistance                                                                               | N <sub>1MOS</sub><br>R <sub>DSON</sub> | -           | 300           | 600        | mΩ      |

| Switches N1 Leakage Current<br>At V <sub>IN</sub> = 4.2 V                                               | N <sub>1MOS</sub> L                    | -           | 0.05          | 0.5        | μΑ      |

| Efficiency (Notes 8, 9)                                                                                 | E <sub>FF</sub>                        | -           | 85            | -          | %       |

| V <sub>OUTP</sub> Range Load Current (Notes 9, 10)                                                      | I <sub>OUTP</sub>                      |             |               |            | mA      |

| VIN ≥ 3.2 V, $T_A$ between 0 to +85°C<br>VIN ≥ 2.9 V, $T_A$ between 0 to +85°C                          |                                        | -<br>-<br>- | 270<br>-<br>- | 230<br>200 |         |

| Output Voltage Line Regulation I <sub>OUTP</sub> = 0 mA<br>2.7 < V <sub>IN</sub> < 4.6                  | L <sub>INE_RP</sub>                    | -           | -             | 10         | mV      |

| Output Voltage Line Transient Overshoot (Note 12)                                                       | L <sub>INE_TP</sub>                    | -           | 4.0           | -          | mV      |

| Power Supply Ripple Rejection (Notes 9, 13) 1.0 Hz to 1.0 kHz 1.0 kHz to 10 kHz                         | P <sub>SRRP</sub>                      | -           | 60<br>40      |            | dB      |

| Output Voltage Load Regulation (Note 14)                                                                | L <sub>OAD_RP</sub>                    | _           | _             | 0.5        | %/100mA |

| Output Voltage Load Transient Response: Overshoot and Undershoot Vs. Steady State Voltage (Notes 9, 15) | L <sub>TRP</sub>                       | -           | -             | 100        | mV      |

| BUCK/BOOST REGULATOR                                                                                    |                                        |             | ·             | I.         |         |

| Typical Negative Operational Output Voltage Range                                                       | V <sub>OUTN</sub>                      | -15         | -             | -2.0       | V       |

| Peak Inductor Current (Note 9)                                                                          | I <sub>PEAKN_MAX</sub>                 | 720         | 900           | 1020       | mA      |

| Switches P2 ON Resistance                                                                               | P <sub>2MOS</sub><br>R <sub>DSON</sub> | -           | 1.0           | 2.0        | Ω       |

| Switches P2 Leakage Current<br>At V <sub>IN</sub> = 4.2 V                                               | P <sub>2MOS</sub> L                    | -           | 0.05          | 0.5        | μΑ      |

| Efficiency (Notes 8, 9)                                                                                 | E <sub>FF</sub>                        | -           | 80            | -          | %       |

| V <sub>OUTN</sub> Range Load Power (Notes 9, 10)                                                        | P <sub>OUTN</sub>                      |             |               |            | mW      |

| VIN ≥ 3.2 V, T <sub>A</sub> between 0 to +85°C                                                          |                                        | _           | 1000          | -<br>800   |         |

| VIN $\geq$ 2.9 V, T <sub>A</sub> between 0 to +85°C                                                     |                                        | _           | _             | 700        |         |

| Output Voltage Reference 0 $\mu$ A < I <sub>REF</sub> < 100 $\mu$ A                                     | O <sub>VR</sub>                        | -1 %        | 1.265         | +1 %       | V       |

| Feedback Voltage Threshold in Steady State: $2.7 < V_{IN} < 4.6$                                        | F <sub>BVN</sub>                       | -2 %        | 0.632         | +2 %       | mV      |

| Feedback Input Current                                                                                  | F <sub>BICN</sub>                      | -50         | -             | 50         | nA      |

| Output Voltage Line Regulation at I <sub>OUTN</sub> = 0 mA (Note 11) 2.7 < V <sub>IN</sub> < 4.6        | L <sub>INE_RN</sub>                    | -           | -             | 20         | mV      |

| Output Voltage Line Transient Overshoot (Note 12)                                                       | L <sub>INE_TN</sub>                    | -           | 4.0           | -          | mV      |

| Power Supply Ripple Rejection (Notes 9, 13) 1.0 Hz to 1.0 kHz 1.0 kHz to 10 kHz                         | P <sub>SRRN</sub>                      | -           | 60<br>40      |            | dB      |

| Load Regulation (Notes 11, 14)                                                                          | L <sub>OAD RN</sub>                    | -           | _             | 0.5        | %/100mA |

| Load Transient Response: Overshoot and Undershoot Vs.<br>Steady State Voltage (Notes 9, 15)             | L <sub>TRN</sub>                       | -           | -             | 100        | mV      |

ELECTRICAL CHARACTERISTICS (Min & Max Limits apply for TA between -40°C to +85°C and VIN between 2.7 V to 4.6 V. Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 3.7$  V, unless otherwise noted)

| Rating                                                                                                        | Symbol           | Min | Тур        | Max | Unit |

|---------------------------------------------------------------------------------------------------------------|------------------|-----|------------|-----|------|

| Operational Power Supply                                                                                      | V <sub>IN</sub>  | 2.7 | -          | 4.6 | V    |

| Internal Oscillator Frequency, T <sub>A</sub> = 25°C, V <sub>IN</sub> = 3.7 V                                 | Fosc             | 1.6 | 1.75       | 1.9 | MHz  |

| Maximum Duty Cycle                                                                                            | M <sub>DCY</sub> | 87  | 90         | -   | %    |

| Stand by Current at $I_{OUTP} = I_{OUTN} = 0$ mA, EN = Low $V_{IN} = 4.2$ V, $T_A = +25^{\circ}\text{C}$      | I <sub>STB</sub> | -   | -          | 2.0 | μΑ   |

| Quiescent Current @ V <sub>OUTN</sub> = -5.4 V @ T <sub>A</sub> = +25°C<br>Switching (Note 9)<br>No Switching | IQ               | -   | 1.5<br>1.0 | 3.0 | mA   |

| Soft Start Time to limit the Inrush Current                                                                   | S <sub>ST</sub>  | -   | 2.0        | -   | ms   |

| Thermal Shut Down Protection                                                                                  | T <sub>SD</sub>  | -   | 165        | -   | °C   |

| Thermal Shut Down Protection Hysteresis                                                                       | T <sub>SDH</sub> | -   | 15         | -   | °C   |

| Voltage Input Logic Low                                                                                       | V <sub>IL</sub>  | -   | -          | 0.4 | V    |

| Voltage Input Logics High                                                                                     | V <sub>IH</sub>  | 1.2 | -          | -   | V    |

| EN pin Pull Down Resistance                                                                                   | R <sub>EN</sub>  | 280 | 400        | 670 | kΩ   |

#### NOTES:

- 8. Efficiency is defined by 100 \* (Pout / Pin), Vin = 3.1 to 4.2 V, L = VLF3010AT-4R7MR70 (DCR = 280 m $\Omega$  max, Isat = 700 mA), Load = 15 to 30 mA, Voutn = -5.4 V.

- 9. Guaranteed by design and characterized.

- 10. Typical application circuit and components depicted Figure 1.

- 11. Tested at 25°C and guaranteed from -40°C to +85°C by characterization. 12. Line drop and rise between 3.4 to 2.9 V in 50  $\mu$ s at  $I_{OUT} = 25$  mA,  $V_{OUTN} = -5.4$  V. 13. Ripple = 0.2 V p-p at 25°C, Cout = 4.7  $\mu$ F,  $I_{OUT} = 0$  to 100 mA,  $V_{IN} = 3.7$  V.

- 14. I<sub>OUT</sub> from 0 to 100 mA.

- 15. Load step 10 to 90 mA and 90 to 10 mA, rising and falling edge in 10  $\mu$ s, Cout = 4.7  $\mu$ F, V<sub>IN</sub> = 3.7 V. 16. Maximum range load (I<sub>OUTN\_MAX</sub>) is dependent by the output voltage setup (V<sub>OUTN</sub>), P<sub>OUTN</sub> for a given condition and work out by equation below.

$$I_{OUTN\_MAX} = \frac{P_{OUTN}}{V_{OUTN}}$$

For example, should one need setup – 4.9 for  $V_{OUTN}$ , at  $V_{IN} \ge 3.2 \text{ V}$ ,

$$I_{OUTN\_MAX} = \frac{0.8}{4.9} = 163 \text{ mA}$$

#### TYPICAL OPERATING CHARACTERISTICS

Figure 3. Efficiency vs. I<sub>OUT</sub> L = MARUWA CXFU0208-4R7

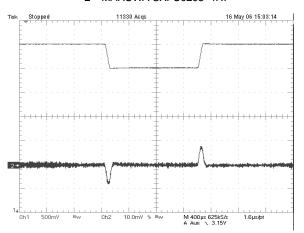

Figure 5. Line Transient Response  $V_{OUTP}$  at 100 mA 1 VBAT, 500 mV/div DC, from 3.5 to 3.0 V in 50  $\mu$ s 2 VOUTP, 10 mV/div AC, T = 400  $\mu$ s/div

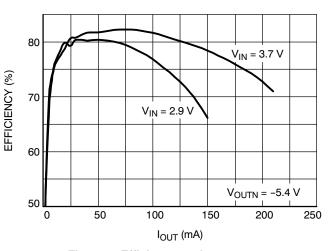

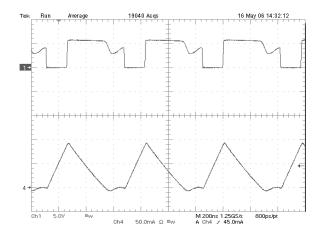

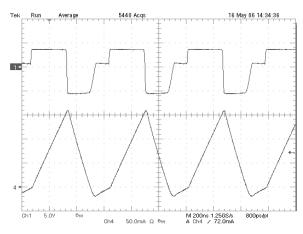

Figure 7. Continuous Conduction Mode (CCM)

1 SWP, 5 V/div DC, 4 I<sub>LP</sub>, 100 mA/div, DC, I<sub>OUTP</sub> = 100 mA

**Figure 4. Efficiency vs. I<sub>OUT</sub>**, L = MARUWA CXFU0208-4R7 plus Optional D2 NSR0320MW2

Figure 6. Line Transient Response  $V_{OUTN}$  = -5.4 V, 100 mA 1 VBAT, 500 mV/div DC, from 3.5 to 3.0 V in 50  $\mu$ s 2 VOUTN, 10 mV/div AC, T = 400  $\mu$ s/div

**Figure 8. Discontinuous Current Mode (DCM)** 1 SWP, 5 V/div, DC 4 I<sub>LP</sub>, 50 mA/div, DC, I<sub>OUTP</sub> = 20 mA

Figures 7 and 8 have been done at VBAT = 3.7 V,  $V_{OUTN} = -5.4 \text{ V}$

#### TYPICAL OPERATING CHARACTERISTICS

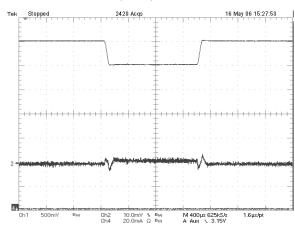

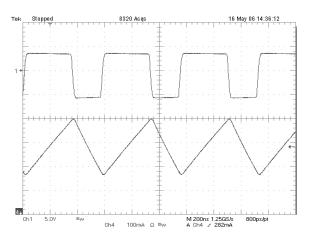

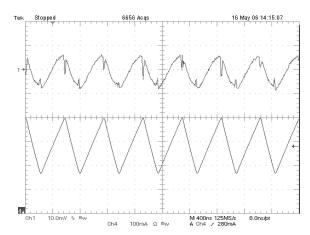

Figure 9. Continuous Conduction Mode (CCM) 1 SWN, 5 V/div DC, 4  $I_{LN}$ , 100 mA/div, DC,  $I_{OUTN}$  = 100 mA

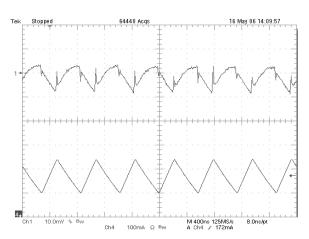

Figure 11. Positive Output Voltage Ripple in CCM 1 V<sub>OUTP</sub>, 10 mV/div AC, 4 I<sub>LP</sub>, 100 mA/div DC, I<sub>OUTP</sub> = 100 mA

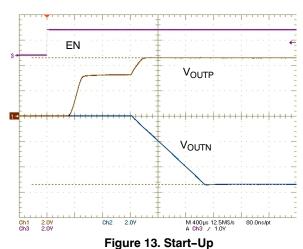

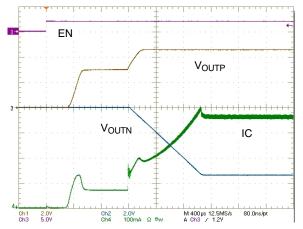

1 VOUTP, 2 V/div, 2 VOUTN, 2 V/div, 3 EN pin, 2 V/div

**Figure 10. Discontinuous Current Mode (DCM)** 1 SWN, 5 V/div, DC 4 I<sub>LN</sub>, 50 mA/div, DC, I<sub>OUTN</sub> = 20 mA

Figure 12. Negative Output Voltage Ripple in CCM 1  $V_{OUTN}$ , 10 mV/div AC, 4  $I_{LN}$ , 100 mA/div DC,  $I_{OUTN}$  = 100 mA

Figure 14. Inrush Current at I<sub>OUT</sub> = 100 mA

1 VOUTP, 2 V/div, 2 VOUTN, 2 V/div, 3 EN pin, 5 V/div,

4 IC (Input Current), 100 mA/div

Figures 9 through 12 have been done at VBAT = 3.7 V and schematic depict Figure 1

#### **DETAILED OPERATING DESCRIPTION**

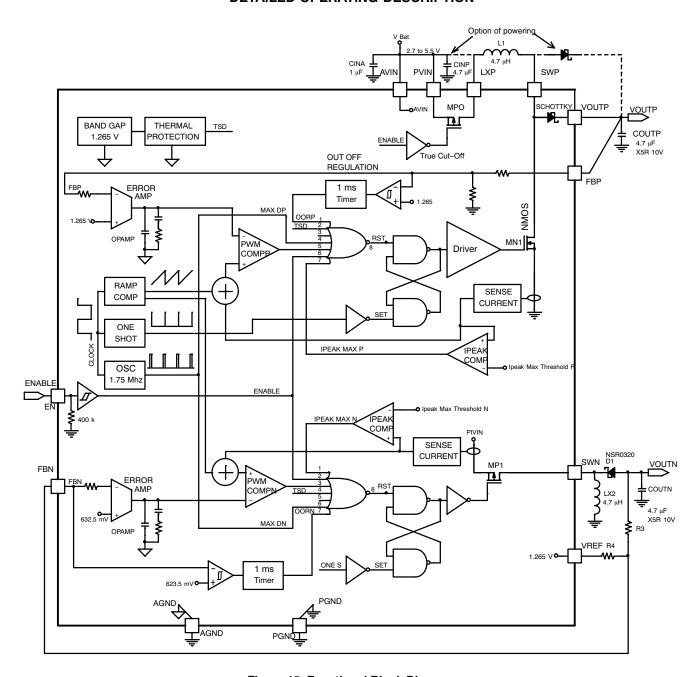

Figure 15. Functional Block Diagram

#### **Detailed Descriptions**

The NCP5810D is a dual-output DC/DC converter which can generate both a positive and a negative voltage. The output voltage of the inverter is fully configurable using external feedback resistors. The switching regulator operates at 1.75 MHz which allows the use of small inductors and ceramic capacitors. The both converters are internally compensated which simplifies the design and reduces the PCB component count. Cycle-by-cycle peak current limit and thermal provide value added features to protect the device.

#### **Boost Operation**

The internal oscillator provides a 1.75 MHz clock signal to trigger the PWM controller on each rising edge (SET signal) which starts a cycle. During this phase the low side MN1 switch is turned on thus increasing the current through the inductor L1. The switch current is measured by the SENSE CURRENT and added to the RAMP COMP signal. Then PWM COMPP compares the output of the adder and the signal from ERROR AMP. When the comparator threshold is exceeded, the MN1 power switch is turned off until the rising edge of the next clock cycle. In

addition, there are five functions which can reset the flip-flop logic to switch off the MN1. The MAX DP monitors the pulse width and if it exceeds 88% (nom) of the cycle time the switch will be turned off. This limits the switch from being on for more than one cycle. IPEAK COMP compares the sensed inductor current with the IPEAK\_MAX threshold set at 700 mA (nom). If the current exceeds this value, the controller turns off the NMOS switch for the remainder of the cycle. This is a safety function to prevent any excessive current that could overload the inductor and the power stage. The boost regulator is internally compensated and provides a minimum of 45° phase margin.

#### **Buck-Boost Inverter Operation**

Figure 9 depicts the two intervals of the buck-boost operation in Continuous Conduction Mode (CCM) in a simplified way. During the first interval, the internal PMOS power switch is turned on and the external Schottky diode is reverse biased. The inductor stores energy through the battery while the load is supplied by the output capacitor to maintain regulation. During the second interval, the switch is turned off and the diode is forward biased, this allows the energy stored in the inductor to be supplied to both the load and the capacitor.

In CCM, the voltage ratio of a buck-boost inverter converter can be expressed as:

$$\frac{V_{OUT\_N}}{V_{IN}} = \frac{D}{1-D} \text{ where } D = \frac{T_{ON}}{T_{SW}}$$

The internal oscillator provides a 1.75 MHz clock signal to trigger the PWM controller on each rising edge (SET signal) which starts a cycle. During this phase the high side PMOS switch is turned on thus increasing the current through the inductor. The switch current is measured by the SENSE CURRENT and added to the RAMP COMP signal. Then PWM COMPN compares the output of the adder and the signal from ERROR AMP. When the comparator threshold is exceeded, the PMOS power switch is turned off until the rising edge of the next clock cycle. In addition, there are five functions which can reset the flip-flop logic to switch off the NMOS. The MAX DUTY CYCLE COMP monitors the pulse width and if it exceeds 88% (nom) of the cycle time the switch will be turned off. This limits the switch from being on for more than one cycle. IPEAK COMP compares the sensed inductor current with the IPEAK MAX threshold set at 800 mA (nom). If the current exceeds this value, the controller turns off the PMOS switch for the remainder of the cycle. This is a safety function to prevent any excessive current that could overload the inductor and the power stage.

#### **Buck-Boost Compensation**

Basically the buck-boost inverter is internally compensated and provides a minimum of  $45^{\circ}$  phase margin. But a 10 pF (C6) feed-forward capacitor is needed to improved stability with  $C_{OUTN} = 4.7 \, \mu F$  (C4) used to

bypass VOUTN. Moreover in order to achieve excellent the line transient rejection in critical conduction mode two  $10~\mu F$  X5R in parallel for  $C_{OUTN}$  can be used. In this case the feed-forward capacitor (C6) must be change from 10~pF to 68~pF as depicted Figure 16.

Figure 16. Inverter Compensation

#### **High Output Voltage Accuracy**

NCP5810D integrates a very accurate internal voltage reference (1% nom). Combined with the use of precision feedback resistors, the NCP5810D will achieve highly precise output voltages.

## Excellent Line Transient Rejection and High Power Supply Rejection Ratio

High output voltage accuracy and signal integrity makes the NCP5810D the perfect solution for biasing Active Matrix OLED displays. In order to have a steady, clean display, OLEDs have to be biased by a very accurate voltage with high immunity to line and load transients. Both regulators have been specifically designed with high loop gain and high phase margin to satisfy the great constraints of AMOLED driving.

The boost converter features a high power supply rejection ratio of 60 dB (nom).

PSRR is defined by

$$-20LOG\left(\frac{OutputRipple}{VinRipple}\right)$$

#### **Out-of-Regulation Protection**

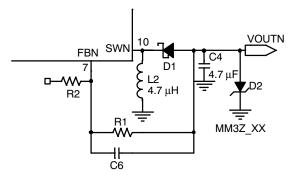

Both DC/DC regulators have implemented monitoring feedback voltage protection. After soft-start sequence the device is set to detect an out-of-regulation condition. Under normal operation if the feedback voltage goes beyond the nominal value by typically +/- 15% a fault is detected. This fault could be caused by an overload, a short-circuit or an open feedback condition. If this fault remains for more than 1 ms, both converters shuts down to protect device itself and any connected circuitry. The NCP5810D remains in disable condition until reinitialized by a rising edge on EN pin. Moreover to limit any overvoltage during the power-up or the 1 ms delay caused by and open feedback condition a small zener diode (D2) is recommended as depicted Figure 17.

Figure 17. Zener Protection

Zener voltage must choose to be 25 % above steady state voltage operation setup. For example, if one needs  $V_{OUTN}$  = -5.4 V,  $V_Z$  = 5.4 + 25 % = 6.8 V. Some recommended zener diodes include but are not limited to:

ON SEMICONDUCTOR: MM3Z6V8T1

#### **Enable**

This input logic allows enabling and disabling the converter. An active high logic level on this pin enables the device. A built-in pull-down resistor disables the device if the pin is left open.

#### **True Shut Down**

When in disable condition, the switch MP0 is turned off and truly isolates the battery from the output. The True shut down eliminates the leakage current from the battery to the load and significantly reduces battery consumption during disable condition, thus increasing battery life.

#### **Inrush Current Limiting Circuitry**

Before the NCP5810D boost converter is turned on, it is unknown whether the output capacitor COUTP is charged or discharged. If the output capacitor is discharged, a common boost converter shows high inductor inrush current at start-up. The internal circuitry of the NCP5810D has been carefully designed to limit the amplitude of the inrush current at start-up.

#### Thermal Shutdown

When the IC junction temperature exceeds 165°C (nom), the power section of the device is disabled. Normal operation will resume when the junction temperature drops below 150°C (nom).

#### **Design Procedure**

#### **Buck-Boost Inverter Output Voltage Setting**

The output voltage of the buck-boost inverter is also adjusted using external feedback resistors, and can be set from -2 V down to -15 V. Unlike for the boost converter, the lower feedback resistor R2 does not use the ground as a reference but uses the reference voltage (nom 1.265 V). R2 is placed between the feedback pin FBN (nom 632 mV) and the reference pin REF. As for the boost converter, the current flowing out of the feedback resistors must be as low as possible to ensure high efficiency in low load conditions. Nevertheless the feedback resistor impedance must not be

too high to keep good voltage accuracy. Therefore it is recommended to use values in the  $10~\text{k}\Omega$  to  $100~\text{k}\Omega$  range for the lower resistor R2. The upper feedback resistor R1 can calculated using the following equation:

$$\begin{aligned} & R_1 = R_2 \times \left( \frac{V_{OUTN} - V_{FBN}}{V_{FBN} - V_{REF}} \right) \\ & But: V_{FBN} = \frac{V_{REF}}{2} \\ & So: R_1 = R_2 \times \left( 1 + \frac{2 \times |V_{OUTN}|}{V_{REF}} \right) \end{aligned}$$

For example, should one need -5.4 V for V<sub>OUTN</sub>, if a  $56 \text{ k}\Omega \pm 1\%$  is selected of R2, R1 should be selected according to the following equation:

$$R_1 = 56 \times \left(1 + \frac{2 \times 5.4}{1.265}\right) = 536 \text{ k}\Omega \pm 1\%$$

#### **Components Selection**

#### **Inductor Selection**

Three different electrical parameters need to be considered when selecting an inductor, the absolute value of the inductor, the saturation current and the DCR. During normal operation, the NCP5810D is intended to operate in Continuous Conduction Mode (CCM). The two equations below can be used to calculate the peak current for each converters:

$$I_{PEAK\_P} = \frac{I_{OUT\_P}}{\eta_P \times (1-D_P)} + \frac{V_{IN} \times D_P}{2 \times L_P \times F}$$

For the boost converter

$$I_{PEAK\_N} = \frac{I_{OUT\_N} \times D_N}{\eta_N \times (1 - D_N)} + \frac{V_{IN} \times D_N}{2 \times L_N \times F}$$

For the buck-boost inverter

Where  $V_{IN}$  is the battery voltage,  $I_{OUT\_X}$  is the load current, L the inductor value, F the switching frequency, and  $D_X$  the duty cycle.

The global converter efficiency η varies with load current. A good approximation is to use  $\eta = 0.8$  from the boost and  $\eta = 0.75$  for the buck-boost inverter. It is important to ensure that the inductor current rating is high enough such that it not saturate. As the inductor size is reduced, the peak current for a given set of conditions increases along with higher current ripple so it is not possible to deliver maximum output power at lower inductor values. Finally an acceptable DCR must be selected regarding losses in the coil and must be lower than  $300 \text{ m}\Omega$  to limit excessive voltage drop. In addition, as DCR is reduced, overall efficiency will improve. The inductor value should range between 2.7 µH and 6.8 µH, typically for each DC/DC converter, it is recommended to use a 4.7 µH low profile inductor. Some recommended inductors include but are not limited to:

TDK: VLF3010AT-4R7MR70 (1.0 mm)

TDK: MLP3216S2R7T (0.6 mm) SUMIDA: CDH2D09BNP (1.0 mm) MARUWA CXFU0208-4R7 (0.8 mm)

#### **Schottky Diode Selection**

An external diode is required for the rectification of the negative output. The reverse voltage rating of the selected diode must be equal to or greater than the difference between the output voltage of the inverter and the input voltage. The average current rating of the diode must be greater than the maximum output load current. The peak current rating must be larger than the maximum peak inductor current. It is recommended to use a Schottky diode with lower forward voltage to minimize the power dissipation and therefore to maximize the efficiency of the converter.

Also a particular care must be observed for parasitic capacitance versus reverse voltage and leakage current versus junction diode temperature. Both parameters are impacting the efficiency in low load condition and switching quiescent current.

Some recommended Schottky diodes include but are not limited to:

ON SEMICONDUCTOR: NSR0320MW2 ON SEMICONDUCTOR: RB521S30

ROHM: RSX051VA-30 PHILIPS: PMEG2005AEL

#### **Input Capacitor Selection**

To achieve high performances (signal integrity) one 4.7  $\trianglerighteq F$  6.3 V X5R should be used to bypass the power input supply  $C_{INP}$  (PVIN) and one 1.0  $\trianglerighteq F$  6.3 V X5R to bypass the analog input supply  $C_{INA}$  (AVIN).

#### **Output Capacitor Selection**

The output capacitor directly affects the output ripple voltage and the loop stability.  $C_{OUTP}$  and  $C_{OUTN}$  store energy during the  $T_{OFF}$  phase and sustain the load during the  $T_{ON}$  phase. In order to minimize the output ripple, typically a 4.7  $\mu F$  low ESR multi-layer ceramic capacitor type X5R is recommended. Moreover two 10  $\mu F$  in parallel can be used to improved the line transient rejection in critical conduction mode of the inverter in this case see recommendation in Buck-Boost Compensation paragraph.

#### **Ceramic Capacitor Caution**

A particular care must be observed to select ceramic capacitors. Actually capacitance can decrease dramatically with the increased applied DC voltage. This

characteristic is DC bias effect that especially affects capacitor in small case-size. The capacitance value can drop below 50% to 70% or even more of the nominal value. For the boost and buck-boost regulator stability viewpoint the percentage drop in capacitance for the chosen input and output operating voltage must be limit to 30% maximum over operating temperature range. Also too low capacitance will increase the output voltage ripple and the noise. Below is a list of recommended capacitors include but are not limited to, please consult the manufacturers for more detailed information.

4.7 µF 6.3 V 0603

TDK: C1608X5R0J475MT

TDK: CGB4B1X5R0J475M (0.5 mm)

4.7 µF 10 V 0805

TDK: C2012X5R1A475MT MURATA: GRM219R61A475KE

10.0 μF 6.3 V 0805

TDK: C2012X5R0J106M (0.95 mm max)

10.0 μF 10 V 0805

TDK: C2012X5R1A106MT (1.25 mm)

#### **Layout Recommendations**

The high speed operation of the NCP5810D demands careful attention to board layout and component placement. To prevent electromagnetic interference (EMI) problems and reduce voltage ripple of the device any high current copper trace which see high frequency switching should be optimized. Therefore, use short and wide traces for power current paths and for power ground tracks.

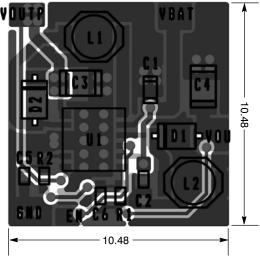

In this application both couples of elements formed by the Schottky diode D1 / capacitor C4 and D2 (optional) / C3 are in the high frequency switching path where current flow is discontinuous. These components (D1/C4) in one hand and (D2/C3) in other hand should be placed as close as possible to reduce parasitic inductance connection. Also it is important to minimize the area of the SWP and SWN nodes and used the ground plane under them to minimize cross-talk to sensitive signals and IC. The exposed pad of the package must be connected to ground plane of the board that is important for EMI and thermal management. Also, PGND and AGND pin connection must be connected to the ground plane. In addition, the inductors track connection L1, L2 and input bypass capacitor C1, C2 must be placed shortly to the NCP5810D pins connection to reduce EMI. Finally it is always good practice to keep the sensitive tracks such as feedback connection (VS and FBN) away from switching signal connections (SWP and SWN) by laying the tracks on the other side of PCB. Figure 18 show an example of optimized PCB layout.

Figure 18. Recommended PCB Layout

#### **Thermal Considerations**

Careful attention must be paid to the internal power dissipation of the NCP5810D. The power dissipation is a function of efficiency and output power. Hence, increasing the output power requires better components selection. For example, should one change inductors: larger inductor value (in micro Henri) and/or lower DCR may improve efficiency. Adding the optional Schottky diode D2 provides a lower drop when the current flowing from the inductor to the load, thereby improving the boost converter efficiency.

The exposed thermal pad that is designed to be soldered to the ground plane to used the PCB as a heatsink. This ground should then be connected to an internal copper ground plane with thermal via placed directly under the package to spread out the heat dissipated by the NCP5810D as depicted in Figure 18.

#### **ORDERING INFORMATION**

| Device        | Package                    | Shipping <sup>†</sup> |

|---------------|----------------------------|-----------------------|

| NCP5810DMUTXG | UDFN-123x3 mm<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### Demo Board Available:

• The NCP5810DGEVB/D evaluation board that configures the device in typical application to supply constant voltage.

#### PACKAGE DIMENSIONS

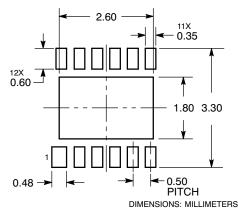

UDFN12, 3x3 **MU SUFFIX** CASE 517AM-01 **ISSUE O**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 0.45        | 0.55 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| A3  | 0.07 REF    |      |  |  |

| b   | 0.20        | 0.30 |  |  |

| D   | 3.00 BSC    |      |  |  |

| D2  | 2.40        | 2.60 |  |  |

| E   | 3.00        | BSC  |  |  |

| E2  | 1.60        | 1.80 |  |  |

| е   | 0.50 BSC    |      |  |  |

| K   | 0.20        |      |  |  |

| L   | 0.30        | 0.50 |  |  |

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and una are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your loca Sales Representative

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor: NCP5810DMUTXG