# **SAF1760**

# Hi-Speed Universal Serial Bus host controller for embedded applications

Rev. 2 — 19 June 2012

**Product data sheet**

# 1. General description

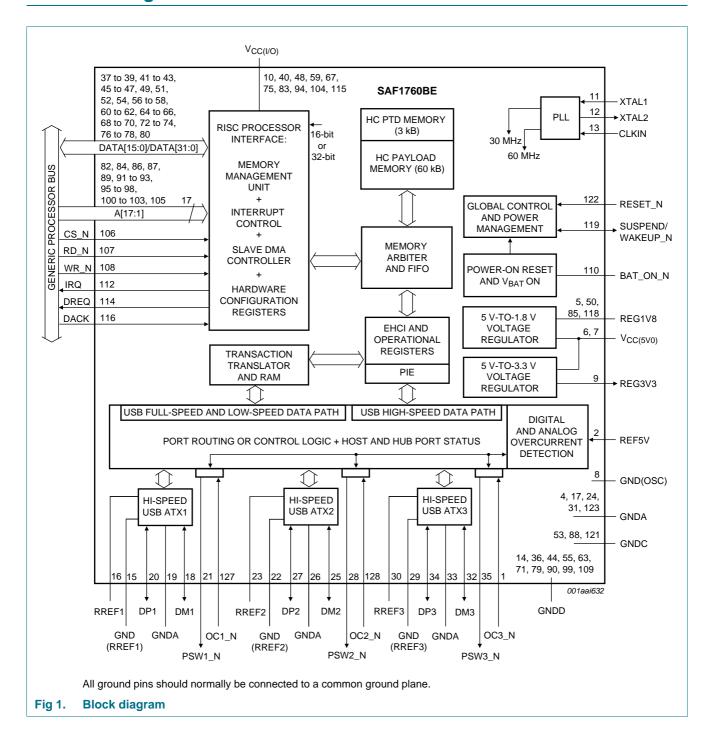

The SAF1760 is a Hi-Speed Universal Serial Bus (USB) host controller with a generic processor interface. It integrates one Enhanced Host Controller Interface (EHCI), one Transaction Translator (TT) and three transceivers. The host controller portion of the SAF1760 and the three transceivers comply to Ref. 1 "Universal Serial Bus Specification Rev. 2.0". The EHCI portion of the SAF1760 is adapted from Ref. 2 "Enhanced Host Controller Interface Specification for Universal Serial Bus Rev. 1.0".

The integrated high-performance Hi-Speed USB transceivers enable the SAF1760 to handle all Hi-Speed USB transfer speed modes: high-speed (480 Mbit/s), full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s). The three downstream ports allow simultaneous connection of three devices at different speeds (high-speed, full-speed and low-speed).

The generic processor interface allows the SAF1760 to be connected to various processors as a memory-mapped resource. The SAF1760 is a slave host: it does not require **bus-mastering** capabilities of the host system bus. The interface can be configured, ensuring compatibility with a variety of processors. Data transfer can be performed on 16 bits or 32 bits, using Programmed Input/Output (PIO) or Direct Memory Access (DMA) with major control signals configurable as active LOW or active HIGH.

Integration of the TT allows connection to full-speed and low-speed devices, without the need of integrating Open Host Controller Interface (OHCI) or Universal Host Controller Interface (UHCI). Instead of dealing with two sets of software drivers, EHCI and OHCI or UHCI, you need to deal with only one set, EHCI, that dramatically reduces software complexity and IC cost.

## 2. Features and benefits

- Automotive qualified in accordance with AEC-Q100

- The host controller portion of the SAF1760 complies with Ref. 1 "Universal Serial Bus Specification Rev. 2.0"

- The EHCl portion of the SAF1760 is adapted from Ref. 2 "Enhanced Host Controller Interface Specification for Universal Serial Bus Rev. 1.0"

- Contains three integrated Hi-Speed USB transceivers that support high-speed, full-speed and low-speed modes

- Integrates a TT for original USB (full-speed and low-speed) device support

- Up to 64 kB internal memory (8 k × 64 bit) accessible through a generic processor interface; operation in multitasking environments is made possible by the implementation of virtual segmentation mechanism with bank switching on task request

## **Embedded Hi-Speed USB host controller**

- Generic processor interface, non-multiplexed and variable latency, with a configurable 32-bit or 16-bit external data bus; the processor interface can be defined as variable-latency or SRAM type (memory mapping)

- Slave DMA support to reduce the load of the host system CPU during the data transfer to or from the memory

- Integrated Phase-Locked Loop (PLL) with a 12 MHz crystal or an external clock input

- Integrated multi-configuration FIFO

- Optimized msec-based or multi-msec-based Proprietary Transfer Descriptor (PTD) interrupt

- Tolerant I/O for low voltage CPU interface (1.65 V to 3.6 V)

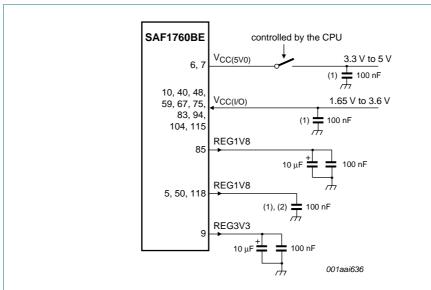

- 3.3 V-to-5.0 V external power supply input

- Integrated 5.0 V-to-1.8 V or 3.3 V-to-1.8 V voltage regulator (internal 1.8 V for low-power core)

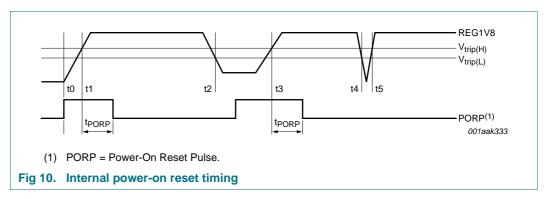

- Internal power-on reset and low-voltage reset

- Supports suspend and remote wake-up

- Target current consumption:

- ◆ Normal operation; one port in high-speed active: I<sub>CC</sub> < 100 mA</p>

- Suspend mode: I<sub>CC(susp)</sub> < 150 μA at room temperature</li>

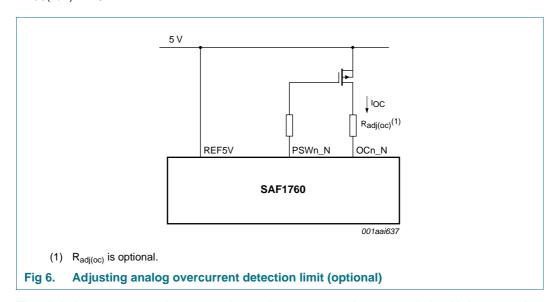

- Built-in configurable overcurrent circuitry (digital or analog overcurrent protection)

# 3. Applications

The SAF1760 can be used to implement a Hi-Speed USB compliant host controller connected to most of the CPUs present in the market today, having a generic processor interface with de-multiplexed address and data bus. This is because of the efficient slave-type interface of the SAF1760.

This NXP USB product can only be used in automotive applications. Inclusion or use of the NXP USB products in other than automotive applications is not permitted and for your company's own risk. Your company agrees to full indemnify NXP for any damages resulting from such inclusion or use.

# 4. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                     |          |  |  |

|-------------|---------|-------------------------------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                                         | Version  |  |  |

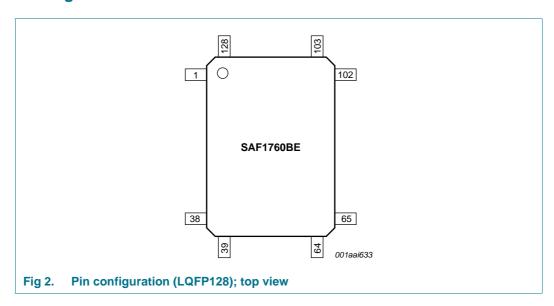

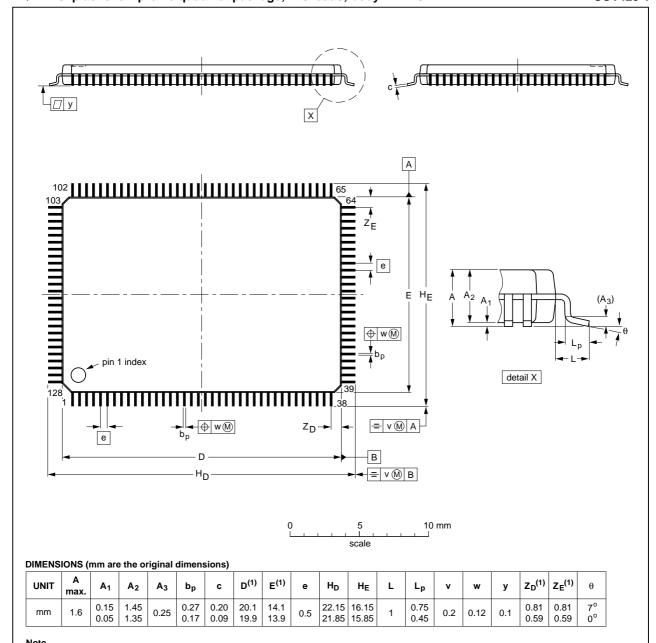

| SAF1760BE   | LQFP128 | plastic low profile quad flat package; 128 leads; body $14 \times 20 \times 1.4$ mm | SOT425-1 |  |  |

#### **Embedded Hi-Speed USB host controller**

# 5. Block diagram

Embedded Hi-Speed USB host controller

# 6. Pinning information

# 6.1 Pinning

# 6.2 Pin description

Table 2. Pin description

| Symbol[1][2]         | Pin<br>LQFP128 | Type[3] | Description                                                                                                                                                                     |  |

|----------------------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OC3_N                | 1              | AI      | port 3 analog (5 V input) and digital overcurrent input; if not used, connect to $V_{CC(I/O)}$ through a 10 k $\Omega$ resistor input, 5 V tolerant                             |  |

| REF5V                | 2              | Al      | 5 V reference input for analog OC detector; connect a 100 nF decoupling capacitor                                                                                               |  |

| TEST1                | 3              | I       | connect to ground                                                                                                                                                               |  |

| GNDA                 | 4              | G       | analog ground                                                                                                                                                                   |  |

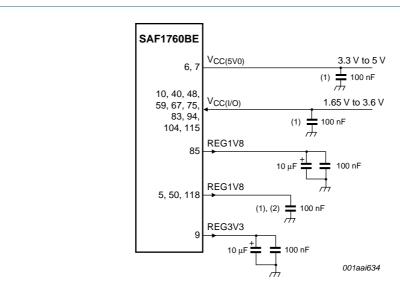

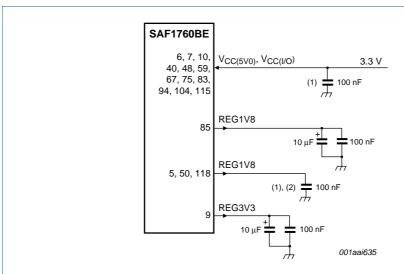

| REG1V8               | 5              | Р       | core power output (1.8 V); internal 1.8 V for the digital core; used for decoupling; connect a 100 nF capacitor; for details on additional capacitor placement, see Section 7.8 |  |

| V <sub>CC(5V0)</sub> | 6              | Р       | input to internal regulators (3.0 V to 5.5 V); connect a 100 nF decoupling capacitor; see Section 7.8                                                                           |  |

| V <sub>CC(5V0)</sub> | 7              | Р       | input to internal regulators (3.0 V to 5.5 V); connect a 100 nF decoupling capacitor; see Section 7.8                                                                           |  |

| GND(OSC)             | 8              | G       | oscillator ground                                                                                                                                                               |  |

| REG3V3               | 9              | Р       | regulator output (3.3 V); for decoupling only; connect a 100 nF capacitor and a 4.7 $\mu$ F-to-10 $\mu$ F capacitor; see Section 7.8                                            |  |

| V <sub>CC(I/O)</sub> | 10             | Р       | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8                                                                                 |  |

| XTAL1                | 11             | Al      | 12 MHz crystal connection input; connect to ground if an external clock is used; see Table 89                                                                                   |  |

| XTAL2                | 12             | AO      | 12 MHz crystal connection output                                                                                                                                                |  |

Table 2.

Pin description ...continued

| Symbol[1][2]        | Pin     | Type[3] | Description                                                                                                             |  |

|---------------------|---------|---------|-------------------------------------------------------------------------------------------------------------------------|--|

|                     | LQFP128 |         |                                                                                                                         |  |

| CLKIN               | 13      | I       | 12 MHz oscillator or clock input; when not in use, connect to $V_{\text{CC(I/O)}}$                                      |  |

| GNDD                | 14      | G       | digital ground                                                                                                          |  |

| GND(RREF1)          | 15      | G       | RREF1 ground                                                                                                            |  |

| RREF1               | 16      | Al      | reference resistor connection; connect a 12 k $\Omega\pm1$ % resistor between this pin and the RREF1 ground             |  |

| GNDA[4]             | 17      | G       | analog ground                                                                                                           |  |

| DM1                 | 18      | AI/O    | downstream data minus port 1                                                                                            |  |

| GNDA                | 19      | G       | analog ground                                                                                                           |  |

| DP1                 | 20      | AI/O    | downstream data plus port 1                                                                                             |  |

| PSW1_N              | 21      | OD      | power switch port 1, active LOW                                                                                         |  |

|                     |         |         | output pad, push-pull open-drain, 8 mA output drive, 5 V tolerant                                                       |  |

| GND(RREF2)          | 22      | G       | RREF2 ground                                                                                                            |  |

| RREF2               | 23      | Al      | reference resistor connection; connect a 12 k $\Omega\pm1$ % resistor between this pin and the RREF2 ground             |  |

| GNDA <sup>[5]</sup> | 24      | G       | analog ground                                                                                                           |  |

| DM2                 | 25      | AI/O    | downstream data minus port 2                                                                                            |  |

| GNDA                | 26      | G       | analog ground                                                                                                           |  |

| DP2                 | 27      | AI/O    | downstream data plus port 2                                                                                             |  |

| PSW2_N              | 28      | OD      | power switch port 2, active LOW output pad, push-pull open-drain, 8 mA output drive, 5 V tolerant                       |  |

| GND(RREF3)          | 29      | G       | RREF3 ground                                                                                                            |  |

| RREF3               | 30      | Al      | reference resistor connection; connect a 12 k $\Omega\pm 1$ % resistor between this pin and the RREF3 ground            |  |

| GNDA[6]             | 31      | G       | analog ground                                                                                                           |  |

| DM3                 | 32      | AI/O    | downstream data minus port 3                                                                                            |  |

| GNDA                | 33      | G       | analog ground                                                                                                           |  |

| DP3                 | 34      | AI/O    | downstream data plus port 3                                                                                             |  |

| PSW3_N              | 35      | OD      | power switch port 3, active LOW output pad, push-pull open-drain, 8 mA output drive, 5 V tolerant                       |  |

| GNDD                | 36      | G       | digital ground                                                                                                          |  |

| DATA0               | 37      | I/O     | data bit 0 input and output<br>bidirectional pad, push-pull input, 3-state output, 4 mA output<br>drive, 3.3 V tolerant |  |

| DATA1               | 38      | I/O     | data bit 1 input and output bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant       |  |

| DATA2               | 39      | I/O     | data bit 2 input and output<br>bidirectional pad, push-pull input, 3-state output, 4 mA output<br>drive, 3.3 V tolerant |  |

Table 2.

Pin description ...continued

| Symbol[1][2]         | Pin<br>LQFP128 | Type <sup>[3]</sup> | Description                                                                                                                                                                                               |  |

|----------------------|----------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CC(I/O)</sub> | 40             | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8                                                                                                           |  |

| DATA3                | 41             | I/O                 | data bit 3 input and output                                                                                                                                                                               |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| DATA4                | 42             | I/O                 | data bit 4 input and output                                                                                                                                                                               |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| DATA5                | 43             | I/O                 | data bit 5 input and output                                                                                                                                                                               |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| GNDD                 | 44             | G                   | digital ground                                                                                                                                                                                            |  |

| DATA6                | 45             | I/O                 | data bit 6 input and output                                                                                                                                                                               |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| DATA7                | 46             | I/O                 | data bit 7 input and output                                                                                                                                                                               |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| DATA8                | 47             | I/O                 | data bit 8 input and output                                                                                                                                                                               |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| V <sub>CC(I/O)</sub> | 48             | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8                                                                                                           |  |

| DATA9                | 49             | I/O                 | data bit 9 input and output                                                                                                                                                                               |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| REG1V8               | 50             | Р                   | core power output (1.8 V); internal 1.8 V for the digital core; used for decoupling; connect a 100 nF capacitor; for details on additional capacitor placement, see <a href="Section 7.8">Section 7.8</a> |  |

| DATA10               | 51             | I/O                 | data bit 10 input and output                                                                                                                                                                              |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| DATA11               | 52             | I/O                 | data bit 11 input and output                                                                                                                                                                              |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| GNDC                 | 53             | G                   | core ground                                                                                                                                                                                               |  |

| DATA12               | 54             | I/O                 | data bit 12 input and output                                                                                                                                                                              |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

| GNDD                 | 55             | G                   | digital ground                                                                                                                                                                                            |  |

| DATA13               | 56             | I/O                 | data bit 13 input and output                                                                                                                                                                              |  |

|                      |                |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                                     |  |

Table 2.

Pin description ...continued

| Symbol[1][2]         | Pin     | Type <sup>[3]</sup> | Description                                                                                     |  |

|----------------------|---------|---------------------|-------------------------------------------------------------------------------------------------|--|

|                      | LQFP128 | -                   |                                                                                                 |  |

| DATA14               | 57      | I/O                 | data bit 14 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA15               | 58      | I/O                 | data bit 15 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| V <sub>CC(I/O)</sub> | 59      | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8 |  |

| DATA16               | 60      | I/O                 | data bit 16 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA17               | 61      | I/O                 | data bit 17 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA18               | 62      | I/O                 | data bit 18 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| GNDD                 | 63      | G                   | digital ground                                                                                  |  |

| DATA19               | 64      | I/O                 | data bit 19 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA20               | 65      | I/O                 | data bit 20 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA21               | 66      | I/O                 | data bit 21 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| V <sub>CC(I/O)</sub> | 67      | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8 |  |

| DATA22               | 68      | I/O                 | data bit 22 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA23               | 69      | I/O                 | data bit 23 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA24               | 70      | I/O                 | data bit 24 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| GNDD                 | 71      | G                   | digital ground                                                                                  |  |

| DATA25               | 72      | I/O                 | data bit 25 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

| DATA26               | 73      | I/O                 | data bit 26 input and output                                                                    |  |

|                      |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant           |  |

Table 2.

Pin description ...continued

| lable 2. Pin descriptioncontinued |         |                     |                                                                                                                                                                                      |  |

|-----------------------------------|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol[1][2]                      | Pin     | Type <sup>[3]</sup> | Description                                                                                                                                                                          |  |

|                                   | LQFP128 |                     |                                                                                                                                                                                      |  |

| DATA27                            | 74      | I/O                 | data bit 27 input and output                                                                                                                                                         |  |

|                                   |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                |  |

| V <sub>CC(I/O)</sub>              | 75      | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8                                                                                      |  |

| DATA28                            | 76      | I/O                 | data bit 28 input and output                                                                                                                                                         |  |

|                                   |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                |  |

| DATA29                            | 77      | I/O                 | data bit 29 input and output                                                                                                                                                         |  |

|                                   |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                |  |

| DATA30                            | 78      | I/O                 | data bit 30 input and output                                                                                                                                                         |  |

|                                   |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                |  |

| GNDD                              | 79      | G                   | digital ground                                                                                                                                                                       |  |

| DATA31                            | 80      | I/O                 | data bit 31 input and output                                                                                                                                                         |  |

|                                   |         |                     | bidirectional pad, push-pull input, 3-state output, 4 mA output drive, 3.3 V tolerant                                                                                                |  |

| TEST2                             | 81      | G                   | connect to ground                                                                                                                                                                    |  |

| A1                                | 82      | I                   | address pin 1                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

| V <sub>CC(I/O)</sub>              | 83      | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8                                                                                      |  |

| A2                                | 84      | I                   | address pin 2                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

| REG1V8                            | 85      | Р                   | core power output (1.8 V); internal 1.8 V for the digital core; used for decoupling; connect a 100 nF capacitor and a 4.7 $\mu\text{F-to-}10~\mu\text{F}$ capacitor; see Section 7.8 |  |

| A3                                | 86      | I                   | address pin 3                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

| A4                                | 87      | I                   | address pin 4                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

| GNDC                              | 88      | G                   | core ground                                                                                                                                                                          |  |

| A5                                | 89      | I                   | address pin 5                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

| GNDD                              | 90      | G                   | digital ground                                                                                                                                                                       |  |

| A6                                | 91      | I                   | address pin 6                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

| A7                                | 92      | I                   | address pin 7                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

| A8                                | 93      | I                   | address pin 8                                                                                                                                                                        |  |

|                                   |         |                     | input, 3.3 V tolerant                                                                                                                                                                |  |

Table 2.

Pin description ...continued

| Symbol[1][2]         | Pin     | Type <sup>[3]</sup> | Description                                                                                                                                 |  |

|----------------------|---------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | LQFP128 |                     |                                                                                                                                             |  |

| V <sub>CC(I/O)</sub> | 94      | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8                                             |  |

| A9                   | 95      | I                   | address pin 9                                                                                                                               |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| A10                  | 96      | I                   | address pin 10                                                                                                                              |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| A11                  | 97      | I                   | address pin 11                                                                                                                              |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| A12                  | 98      | I                   | address pin 12                                                                                                                              |  |

|                      |         | _                   | input, 3.3 V tolerant                                                                                                                       |  |

| GNDD                 | 99      | G                   | digital ground                                                                                                                              |  |

| A13                  | 100     | I                   | address pin 13                                                                                                                              |  |

|                      |         | _                   | input, 3.3 V tolerant                                                                                                                       |  |

| A14                  | 101     | I                   | address pin 14                                                                                                                              |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| A15                  | 102     | I                   | address pin 15                                                                                                                              |  |

| 440                  | 100     |                     | input, 3.3 V tolerant                                                                                                                       |  |

| A16                  | 103     | I                   | address pin 16                                                                                                                              |  |

| \ <u>\</u>           | 404     | <u> </u>            | input, 3.3 V tolerant digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF                                                             |  |

| V <sub>CC(I/O)</sub> | 104     | Р                   | decoupling capacitor; see Section 7.8                                                                                                       |  |

| A17                  | 105     | I                   | address pin 17                                                                                                                              |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| CS_N                 | 106     | I                   | chip select signal assertion indicates the SAF1760 being accessed; active LOW                                                               |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| RD_N                 | 107     | I                   | read enable; active LOW                                                                                                                     |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| WR_N                 | 108     | I                   | write enable; active LOW                                                                                                                    |  |

|                      |         |                     | input, 3.3 V tolerant                                                                                                                       |  |

| GNDD                 | 109     | G                   | digital ground                                                                                                                              |  |

| BAT_ON_N             | 110     | OD                  | to indicate the presence of a minimum 3.3 V on pins 6 and 7 (open-drain); connect to $V_{CC(I/O)}$ through a 10 k $\Omega$ pull-up resistor |  |

|                      |         |                     | output pad, push-pull open-drain, 8 mA output drive, 5 V tolerant                                                                           |  |

| n.c.                 | 111     | NC                  | not connected                                                                                                                               |  |

| IRQ                  | 112     | 0                   | host controller interrupt signal                                                                                                            |  |

|                      |         |                     | output pad, 4 mA drive, 3.3 V tolerant                                                                                                      |  |

| n.c.                 | 113     | NC                  | not connected                                                                                                                               |  |

| DREQ                 | 114     | 0                   | DMA controller request for the host controller                                                                                              |  |

|                      |         |                     | output pad, 4 mA drive, 3.3 V tolerant                                                                                                      |  |

Table 2.

Pin description ...continued

| Symbol <sup>[1][2]</sup> | Pin<br>LQFP128 | Type <sup>[3]</sup> | Description                                                                                                                                                                     |  |

|--------------------------|----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CC(I/O)</sub>     | 115            | Р                   | digital supply voltage; 1.65 V to 3.6 V; connect a 100 nF decoupling capacitor; see Section 7.8                                                                                 |  |

| DACK                     | 116            | I                   | host controller DMA request acknowledgment; when not in use, connect to $V_{CC(I/O)}$ through a 10 k $\Omega$ pull-up resistor input, 3.3 V tolerant                            |  |

| TEST3                    | 117            | <u> </u>            | connect to $V_{CC(I/O)}$ through a 10 k $\Omega$ pull-up resistor                                                                                                               |  |

| REG1V8                   | 118            | Р                   | core power output (1.8 V); internal 1.8 V for the digital core; used for decoupling; connect a 100 nF capacitor; for details on additional capacitor placement, see Section 7.8 |  |

| SUSPEND/<br>WAKEUP_N     | 119            | I/OD                | host controller suspend and wake-up; 3-state suspend output (active LOW) and wake-up input circuits are connected together                                                      |  |

|                          |                |                     | <ul> <li>HIGH = output is 3-state; SAF1760 is in suspend mode</li> </ul>                                                                                                        |  |

|                          |                |                     | <ul> <li>LOW = output is LOW; SAF1760 is not in suspend mode</li> </ul>                                                                                                         |  |

|                          |                |                     | connect to $V_{CC(I/O)}$ through an external 10 $k\Omega$ pull-up resistor                                                                                                      |  |

|                          |                |                     | output pad, open-drain, 4 mA output drive, 3.3 V tolerant                                                                                                                       |  |

| TEST4                    | 120            | l                   | pull up to V <sub>CC(I/O)</sub>                                                                                                                                                 |  |

| GNDC                     | 121            | G                   | core ground                                                                                                                                                                     |  |

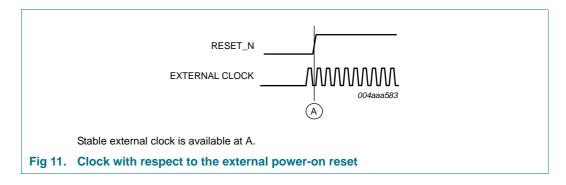

| RESET_N                  | 122            | 1                   | external power-up reset; active LOW; when reset is asserted, it is expected that bus signals are idle, that is, not toggling input, 3.3 V tolerant                              |  |

|                          |                |                     | <b>Remark:</b> During reset, ensure that all the input pins to the SAF1760 are not toggling and are in their inactive states.                                                   |  |

| GNDA                     | 123            | G                   | analog ground                                                                                                                                                                   |  |

| TEST5                    | 124            | AI/O                | connect a 220 nF capacitor between this pin and pin 125                                                                                                                         |  |

| TEST6                    | 125            | AI/O                | connect a 220 nF capacitor between this pin and pin 124                                                                                                                         |  |

| TEST7                    | 126            | I                   | connect to 3.3 V                                                                                                                                                                |  |

| OC1_N                    | 127            | Al                  | port 1 analog (5 V input) and digital overcurrent input; if not used, connect to $V_{CC(I/O)}$ through a 10 k $\Omega$ resistor                                                 |  |

|                          |                |                     | input, 5 V tolerant                                                                                                                                                             |  |

| OC2_N                    | 128            | Al                  | port 2 analog (5 V input) and digital overcurrent input; if not used, connect to $V_{CC(I/O)}$ through a 10 k $\Omega$ resistor input, 5 V tolerant                             |  |

|                          |                |                     |                                                                                                                                                                                 |  |

<sup>[1]</sup> Symbol names ending with underscore N, for example, NAME\_N, represent active LOW signals.

<sup>[2]</sup> All ground pins should normally be connected to a common ground plane.

<sup>[3]</sup> I = input only; O = output only; I/O = digital input/output; OD = open-drain output; AI/O = analog input/output; AI = analog input; P = power; G = ground supply; NC = not connected.

<sup>[4]</sup> For port 1.

<sup>[5]</sup> For port 2.

<sup>[6]</sup> For port 3.

**Embedded Hi-Speed USB host controller**

# 7. Functional description

# 7.1 SAF1760 internal architecture: advanced NXP slave host controller and hub

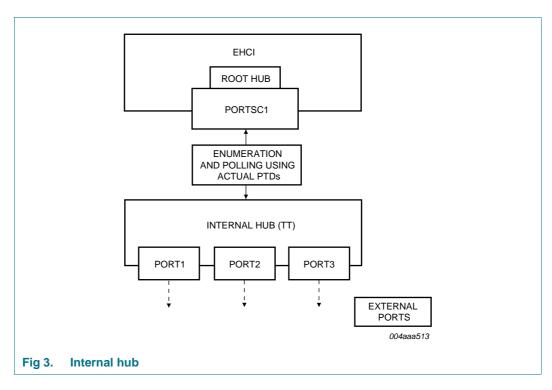

The EHCI block and the Hi-Speed USB hub block are the main components of the advanced NXP slave host controller.

The EHCI is the latest generation design, with improved data bandwidth. The EHCI in the SAF1760 is adapted from Ref. 2 "Enhanced Host Controller Interface Specification for Universal Serial Bus Rev. 1.0".

The internal Hi-Speed USB hub block replaces the companion host controller block used in the original architecture of a PCI Hi-Speed USB host controllers to handle full-speed and low-speed modes. The hardware architecture in the SAF1760 is simplified to help reduce cost and development time, by eliminating the additional work involved in implementing the OHCI software required to support full-speed and low-speed modes.

<u>Figure 3</u> shows the internal architecture of the SAF1760. The SAF1760 implements the EHCI that has an internal port, the root hub port (not available externally), on which the internal hub is connected. The three external ports are always routed to the internal hub. The internal hub is a Hi-Speed USB (USB 2.0) hub including the TT.

**Remark:** The root hub must be enabled and the internal hub must be enumerated. Enumerate the internal hub as if it is externally connected.

At the host controller reset and initialization, the internal root hub port will be polled until a new connection is detected, showing the connection of the internal hub.

The internal Hi-Speed USB hub is enumerated using a sequence similar to a standard Hi-Speed USB hub enumeration sequence, and the polling on the root hub is stopped because the internal Hi-Speed USB hub will never be disconnected. When enumerated, the internal hub will report the three externally available ports.

#### **Embedded Hi-Speed USB host controller**

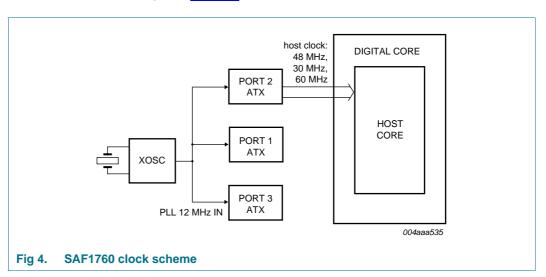

## 7.1.1 Internal clock scheme and port selection

The SAF1760 has three ports. Figure 4 shows the internal clock scheme of the SAF1760.

<u>Figure 4</u> shows that the host clock is derived from port 2. Port 2 does not need to be enabled by software, if only port 1 or port 3 is used. No port needs to be disabled by external pull-up resistors, if not used. The DP and DM of the unused ports need not be externally pulled HIGH because there are internal pull-down resistors on each port that are enabled by default.

Table 3 lists the various port connection scenarios.

#### **Embedded Hi-Speed USB host controller**

Table 3. Port connection scenarios

| 5                              | D. 14                                   | D. 10                                   | D. 10                                   |

|--------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| Port configuration             | Port 1                                  | Port 2                                  | Port 3                                  |

| One port (port 1)              | DP and DM are routed to USB connector   | DP and DM are not connected (left open) | DP and DM are not connected (left open) |

| One port (port 2)              | DP and DM are not connected (left open) | DP and DM are routed to USB connector   | DP and DM are not connected (left open) |

| One port (port 3)              | DP and DM are not connected (left open) | DP and DM are not connected (left open) | DP and DM are routed to USB connector   |

| Two ports (ports 1 and 2)      | DP and DM are routed to USB connector   | DP and DM are routed to USB connector   | DP and DM are not connected (left open) |

| Two ports (ports 2 and 3)      | DP and DM are not connected (left open) | DP and DM are routed to USB connector   | DP and DM are routed to USB connector   |

| Two ports (ports 1 and 3)      | DP and DM are routed to USB connector   | DP and DM are not connected (left open) | DP and DM are routed to USB connector   |

| Three ports (ports 1, 2 and 3) | DP and DM are routed to USB connector   | DP and DM are routed to USB connector   | DP and DM are routed to USB connector   |

# 7.2 Host controller buffer memory block

#### 7.2.1 General considerations

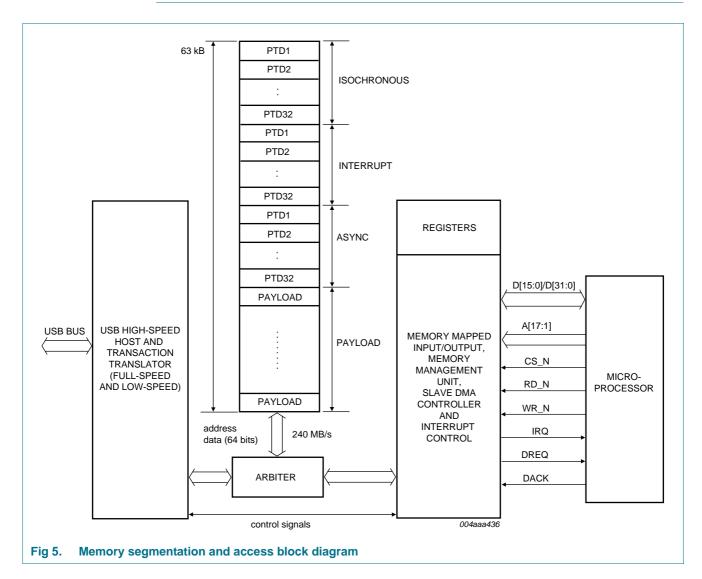

The internal addressable host controller buffer memory is 63 kB. The 63 kB effective memory size is the result of subtracting the size of the registers (1 kB) from the total addressable memory space defined in the SAF1760 (64 kB). This is the optimized value to achieve the highest performance with minimal cost.

The SAF1760 is a slave host controller. This means that it does not need access to the local bus of the system to transfer data from the system memory to the SAF1760 internal memory, unlike the case of the original PCI Hi-Speed USB host controllers. Therefore, correct data must be transferred to both the PTD area and the payload area by PIO (using CPU access) or programmed DMA.

The **slave-host** architecture ensures better compatibility with most of the processors present in the market today because not all processors allow a **bus-master** on the local bus. It also allows better load balancing of the processors local bus because only the internal bus arbiter of the processor controls the transfer of data dedicated to USB. This prevents the local bus from being busy when other more important transfers may be in the queue; and therefore achieving a **linear** system data flow that has less impact on other processes running at the same time.

The considerations mentioned are also the main reason for implementing the pre-fetching technique, instead of using a READY signal. The resulting architecture avoids **freezing** of the local bus, by asserting READY, enhancing the SAF1760 memory access time, and avoiding introduction of programmed additional wait states. For details, see <u>Section 7.3</u> and <u>Section 8.3.8</u>.

The total amount of memory allocated to the payload determines the maximum transfer size specified by a PTD, a larger internal memory size results in less CPU interruption for transfer programming. This means less time spent in context switching, resulting in better CPU usage.

## **Embedded Hi-Speed USB host controller**

A larger buffer also implies a larger amount of data can be transferred. The transfer, however, can be done over a longer period of time, to maintain the overall system performance. Each transfer of the USB data on the USB bus can span for up to a few milliseconds before requiring further CPU intervention for data movement.

The internal architecture of the SAF1760 allows a flexible definition of the memory buffer for optimization of the data transfer on the CPU extension bus and the USB. It is possible to implement various data transfer schemes, depending on the number and type of USB devices present. For example: push-pull; data can be written to half of the memory while data in the other half is being accessed by the host controller and sent on the USB bus. This is useful especially when a high-bandwidth **continuous or periodic** data flow is required.

Through an analysis of the hardware and software environment regarding the usual data flow and performance requirements of most embedded systems, NXP has determined the optimal size for the internal buffer as approximately 64 kB.

## 7.2.2 Structure of the SAF1760 host controller memory

The 63 kB internal memory consists of the PTD area and the payload area.

PTD memory zone is divided into three dedicated areas for each main type of USB transfer: ISOchronous (ISO), INTerrupt (INT) and Asynchronous Transfer List (ATL). As shown in <a href="Table 4">Table 4</a>, the PTD areas for ISO, INT and ATL are grouped at the beginning of the memory, occupying the address range 0400h to 0FFFh, following the register address space. The payload or data area occupies the next memory address range 1000h to FFFFh, meaning that 60 kB of memory are allocated for the payload data.

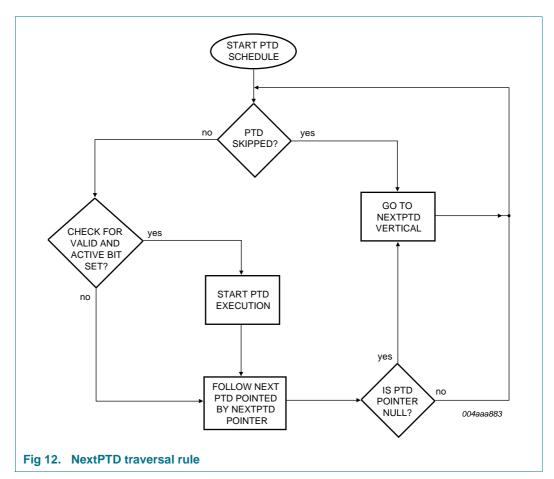

A maximum of 32 PTD areas and their allocated payload areas can be defined for each type of transfer. The structure of a PTD is similar for every transfer type and consists of eight Double Words (DWs) that must be correctly programmed for a correct USB data transfer. The reserved bits of a PTD must be set to logic 0. A detailed description of the PTD structure can be found in <u>Section 9</u>.

The transfer size specified by the PTD determines the contiguous USB data transfer that can be performed without any CPU intervention. The respective payload memory area must be equal to the transfer size defined. The maximum transfer size is flexible and can be optimized, depending on the number and nature of USB devices or PTDs defined and their respective MaxPacketSize.

The CPU will program the DMA to transfer the necessary data in the payload memory. The next CPU intervention will be required only when the current transfer is completed and DMA programming is necessary to transfer the next data payload. This is normally signaled by the IRQ that is generated by the SAF1760 on completing the current PTD, meaning all the data in the payload area was sent on the USB bus. The external IRQ signal is asserted according to the settings in the IRQ Mask OR or IRQ Mask AND registers, see Section 8.4.

The RAM is structured in blocks of PTDs and payloads so that while the USB is executing on an active transfer-based PTD, the processor can simultaneously fill up another block area in the RAM. A PTD and its payload can then be updated on-the-fly without stopping or delaying any other USB transaction or corrupting the RAM data.

# **Embedded Hi-Speed USB host controller**

## Some of the design features are:

- The address range of the internal RAM buffer is from 0400h to FFFFh.

- The internal memory contains isochronous, interrupt and asynchronous PTDs, and respective defined payloads.

- All accesses to the internal memory are double word aligned.

- Internal memory address range calculation:

Memory address = (CPU address 0400h) (shift right >> 3). Base address is 0400h.

Table 4. Memory address

| Memory map | CPU address    | Memory address |

|------------|----------------|----------------|

| ISO        | 0400h to 07FFh | 0000h to 007Fh |

| INT        | 0800h to 0BFFh | 0080h to 00FFh |

| ATL        | 0C00h to 0FFFh | 0100h to 017Fh |

| Payload    | 1000h to FFFFh | 0180h to 1FFFh |

## **Embedded Hi-Speed USB host controller**

Both the CPU interface logic and the USB host controller require access to the internal SAF1760 RAM at the same time. The internal arbiter controls these accesses to the internal memory, organized internally on a 64-bit data bus width, allowing a maximum bandwidth of 240 MB/s. This bandwidth avoids any bottleneck on accesses both from the CPU interface and the internal USB host controller.

# 7.3 Accessing the SAF1760 host controller memory: PIO and DMA

The CPU interface of the SAF1760 can be configured for a 16-bit or 32-bit data bus width.

When the SAF1760 is configured for a 16-bit data bus width, the upper unused 16 data lines must be pulled up to  $V_{CC(I/O)}$ . This can be achieved by connecting DATA[31:16] lines together to a single 10 k $\Omega$  pull-up resistor. The 16-bit or 32-bit data bus width configuration is done by programming bit 8 of the HW Mode Control register. This will determine the register and memory access types in both PIO and DMA modes. All accesses must be word-aligned for 16-bit mode and double word aligned for 32-bit mode, where one word = 16 bits. When accessing the host controller registers in 16-bit mode, the register access must always be completed using two subsequent accesses. In the case of a DMA transfer, the 16-bit or 32-bit data bus width configuration will determine the number of bursts that will complete a certain transfer length.

In PIO mode, CS\_N, WR\_N and RD\_N are used to access registers and memory. In DMA mode, the data validation is performed by DACK, instead of CS\_N, together with the WR\_N and RD\_N signals. The DREQ signal will always be asserted as soon as the SAF1760 DMA is enabled.

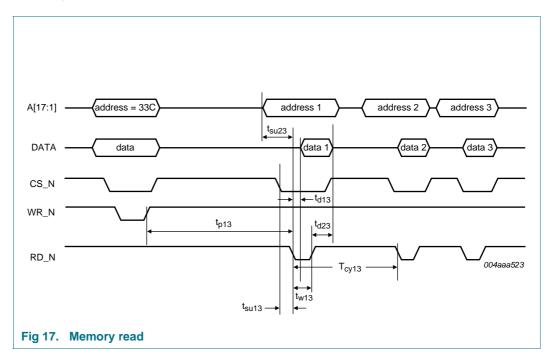

# 7.3.1 PIO mode access, memory read cycle

The following method has been implemented to reduce the read access timing in the case of a memory read:

- The Memory register contains the starting address and the bank selection to read from the memory. Before every new read cycle of the same or different banks, an appropriate value is written to this register.

- Once a value is written to this register, the address is stored in the FIFO of that bank and is then used to pre-fetch data for the memory read of that bank.

- For every subsequent read operation executed at a contiguous address, the address pointer corresponding to that bank is automatically incremented to pre-fetch the next data to be sent to the CPU.

- Memory read accesses for multiple banks can be interleaved. The FIFO block handles the multiplexing of appropriate data to the CPU.

- The address written to the Memory register is incremented and used to successively

pre-fetch data from the memory irrespective of the value on the address bus for each

bank, until a new value for a bank is written to the Memory register. This is valid only

when the address refers to the memory space (400h to FFFFh).

For example, consider the following sequence of operations:

Write the starting (read) address 4000h and bank1 = 01b to the Memory register.

When RD\_N is asserted for three cycles with A[17:16] = 01b, the returned data corresponds to addresses 4000h, 4004h and 4008h.

# **Embedded Hi-Speed USB host controller**

**Remark:** Once 4000h is written to the Memory register for bank1, the bank select value determines the successive incremental addresses used to fetch data. That is, the fetching of data is independent of the address on A[15:0] lines.

Write the starting (read) address 4100h and bank2 = 10b to the Memory register.

When RD\_N is asserted for four cycles with A[17:16] = 10b, the returned data corresponds to addresses 4100h, 4104h, 4108h and 410Ch.

Consequently, the RD\_N assertion with A[17:16] = 01b will return data from 400Ch because the bank1 read stopped there in the previous cycle. Also, RD\_N assertions with A[17:16] = 10b will now return data from 4110h because the bank2 read stopped there in the previous cycle.

#### 7.3.2 PIO mode access, memory write cycle

The PIO memory writes access is similar to a normal memory access. It is not necessary to set the pre-fetching address before a write cycle to the memory.

The SAF1760 internal write address will not be automatically incremented during consecutive write accesses; unlike in a series of SAF1760 memory read cycles. The memory write address must be incremented before every access.

# 7.3.3 PIO mode access, register read cycle

The PIO register read access is similar to a general register access. It is not necessary to set a pre-fetching address before a register read.

The SAF1760 register read address will not be automatically incremented during consecutive read accesses; unlike in a series of SAF1760 memory read cycles. The SAF1760 register read address must be correctly specified before every access.

#### 7.3.4 PIO mode access, register write cycle

The PIO register write access is similar to a general register access. It is not necessary to set a pre-fetching address before a register write.

The SAF1760 register write address will not be automatically incremented during consecutive write accesses; unlike in a series of SAF1760 memory read cycles. The SAF1760 register write address must be correctly specified before every access.

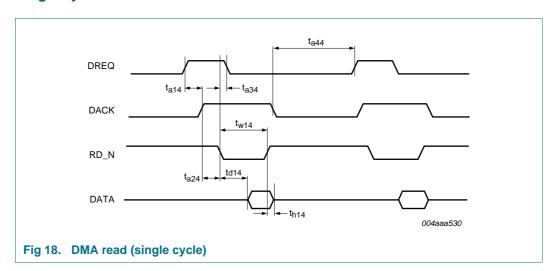

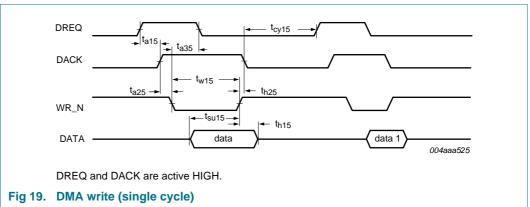

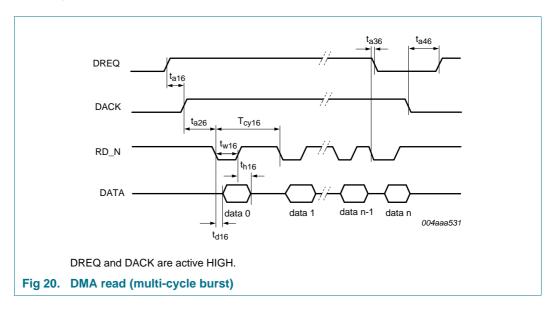

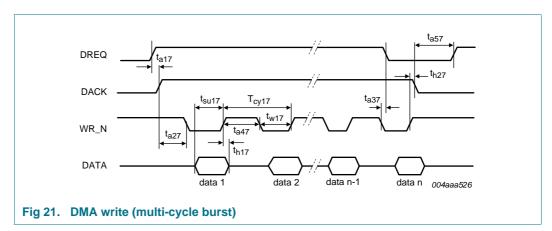

# 7.3.5 DMA mode, read and write operations

The internal SAF1760 host controller DMA is a slave DMA. The host system processor or DMA must ensure the data transfer to or from the SAF1760 memory.

The SAF1760 DMA supports a DMA burst length of 1, 4, 8 and 16 cycles for both the 16-bit and 32-bit data bus width. DREQ will be asserted at the beginning of the first burst of a DMA transfer and will be de-asserted on the last cycle, RD\_N or WR\_N active pulse, of that burst. It will be reasserted shortly after the DACK de-assertion, as long as the DMA transfer counter was not reached. DREQ will be de-asserted on the last cycle when the DMA transfer counter is reached and will not be reasserted until the DMA reprogramming is performed. Both DREQ and DACK signals are programmable as active LOW or active HIGH, according to the system requirements.

## **Embedded Hi-Speed USB host controller**

The DMA start address must be initialized in the respective register, and the subsequent transfers will automatically increment the internal SAF1760 memory address. A register or memory access or access to other system memory can occur in between DMA bursts, whenever the bus is released because DACK is de-asserted, without affecting the DMA transfer counter or the current address.

Any memory area can be accessed by the systems DMA at any starting address because there are no predefined memory blocks. The DMA transfer must start on a word or double word address, depending on whether the data bus width is set to 16 bit or 32 bit. DMA is the most efficient method to initialize the payload area, to reduce the CPU usage and overall system loading.

The SAF1760 does not implement EOT to signal the end of a DMA transfer. If programmed, an interrupt may be generated by the SAF1760 at the end of the DMA transfer.

The slave DMA of the SAF1760 will issue a DREQ to the DMA controller of the system to indicate that it is programmed for transfer and data is ready. The system DMA controller may also start a transfer without the need of the DREQ, if the SAF1760 memory is available for the data transfer and the SAF1760 DMA programming is completed.

It is also possible that the systems DMA will perform a memory-to-memory type of transfer between the system memory and the SAF1760 memory. The SAF1760 will be accessed in PIO mode. Consequently, memory read operations must be preceded by initializing the Memory register (address 033Ch), as described in <a href="Section 7.3.1">Section 7.3.1</a>. No IRQ will be generated by the SAF1760 on completing the DMA transfer but an internal processor interrupt may be generated to signal that the DMA transfer is completed. This is mainly useful in implementing the double-buffering scheme for data transfer to optimize the USB bandwidth.

The SAF1760 DMA programming involves:

- Set the active levels of signals DREQ and DACK in the HW Mode Control register.

- The DMA Start Address register contains the first memory address at which the data transfer will start. It must be word-aligned in 16-bit data bus mode and double word aligned in 32-bit data bus mode.

- The programming of the DMA Configuration register specifies:

- The type of transfer that will be performed: read or write.

- The burst size, expressed in bytes, is specified, regardless of the data bus width.

For the same burst size, a double number of cycles will be generated in 16-bit mode data bus width as compared to 32-bit mode.

- The transfer length, expressed in number of bytes, defines the number of bursts. The DREQ will be de-asserted and asserted to generate the next burst, as long as there are bytes to be transferred. At the end of a transfer, the DREQ will be de-asserted and an IRQ can be generated if DMAEOTINT (bit 3 in the Interrupt register) is set. The maximum DMA transfer size is equal to the maximum memory size. The transfer size can be an odd or even number of bytes, as required. If the transfer size is an odd number of bytes, the number of bytes transferred by the systems DMA is equal to the next multiple of two for the 16-bit data bus width or four for the 32-bit data bus width. For a write operation, however, only the specified odd number of bytes in the SAF1760 memory will be affected.

#### **Embedded Hi-Speed USB host controller**

Enable ENABLE\_DMA (bit 1) of the DMA Configuration register to determine the assertion of DREQ immediately after setting the bit.

After programming the preceding parameters, the systems DMA may be enabled, waiting for the DREQ to start the transfer or immediate transfer may be started.

The programming of the systems DMA must match the programming of the SAF1760 DMA parameters. Only one DMA transfer may take place at a time. PIO mode data transfer may occur simultaneously with a DMA data transfer, in the same or a different memory area.

## 7.4 Interrupts

The SAF1760 will assert an IRQ according to the source or event in the Interrupt register. The main steps to enable the IRQ assertion are:

- 1. Set GLOBAL\_INTR\_EN (bit 0) in the HW Mode Control register.

- 2. Define the IRQ active as level or edge in INTR\_LEVEL (bit 1) of the HW Mode Control register.

- Define the IRQ polarity as active LOW or active HIGH in INTR\_POL (bit 2) of the HW Mode Control register. These settings must match the IRQ settings of the host processor.

- By default, interrupt is level-triggered and active LOW.

- 4. Program the individual interrupt enable bits in the Interrupt Enable register. The software will need to clear the interrupt status bits in the Interrupt register before enabling individual interrupt enable bits.

Additional IRQ characteristics can be adjusted in the Edge Interrupt Count register, as necessary, applicable only when IRQ is set to be edge-active; a pulse of a defined width is generated every time IRQ is active.

Bits 15 to 0 of the Edge Interrupt Count register define the IRQ pulse width. The maximum pulse width that can be programmed is FFFFh, corresponding to a 1 ms pulse width. This setting is necessary for certain processors that may require a different minimum IRQ pulse width from the default value. The default IRQ pulse width set at power-on is approximately 500 ns.

Bits 31 to 24 of the Edge Interrupt Count register define the minimum interval between two interrupts to avoid frequent interrupts to the CPU. The default value of 00h attributed to these bits determines the normal IRQ generation, without any delay. When a delay is programmed and the IRQ becomes active after the respective delay, several IRQ events may have already occurred.

All the interrupt events are represented by the respective bits allocated in the Interrupt register. There is no mechanism to show the order or the moment of occurrence of an interrupt.

The asserted bits in the Interrupt register can be cleared by writing back the same value to the Interrupt register. This means that writing logic 1 to each of the set bits will reset the corresponding bits to the initial inactive state.

## **Embedded Hi-Speed USB host controller**

The IRQ generation rules that apply according to the preceding settings are:

- If an event of interrupt occurs but the respective bit in the Interrupt Enable register is not set, then the respective Interrupt register bit is set but the interrupt signal is not asserted.

- An interrupt will be generated when interrupt is enabled and the respective bit in the Interrupt Enable register is set.

- For a level trigger, an interrupt signal remains asserted until the processor clears the Interrupt register by writing logic 1 to clear the Interrupt register bits that are set.

- If an interrupt is made edge-sensitive and is asserted, writing to clear the Interrupt register will not have any effect because the interrupt will be asserted for a prescribed amount of clock cycles.

- The clock stopping mechanism does not affect the generation of an interrupt. This is useful during suspend and resume cycles, when an interrupt is generated to signal a wake-up event.

The IRQ generation can also be conditioned by programming the IRQ Mask OR and IRQ Mask AND registers.

With the help of the IRQ Mask AND and IRQ Mask OR registers for each type of transfer (ISO, INT and bulk), software can determine which PTDs get priority and an interrupt will be generated when the AND or OR conditions are met. The PTDs that are set will wait until the respective bits of the remaining PTDs are set and then all PTDs generate an interrupt request to the CPU together.

The registers definition shows that the AND or OR conditions are applicable to the same category of PTDs: ISO, INT, ATL.

When an IRQ is generated, the PTD Done Map registers and the respective V bits will show which PTDs were completed.

The rules that apply to the IRQ Mask AND or IRQ Mask OR settings are:

- The OR mask has a higher priority over the AND mask. An IRQ is generated if bit n of the done map is set and the corresponding bit n of the OR Mask register is set.

- If the OR mask for any done bit is not set, then the AND mask comes into picture. An IRQ is generated if all the corresponding done bits of the AND Mask register are set.

For example: If bits 2, 4 and 10 are set in the AND Mask register, an IRQ is generated only if bits 2, 4, 10 of the done map are set.

- If using the IRQ interval setting for the bulk PTD, an interrupt will only occur at the

regular time interval as programmed in the ATL Done Timeout register. Even if an

interrupt event occurs before the time-out of the register, no IRQ will be generated

until the time is up.

For an example on using the IRQ Mask AND or IRQ Mask OR registers without the ATL Done Timeout register, see Table 5.

The AND function: Activate the IRQ only if PTDs 1, 2 and 4 are done.

The OR function: If any of the PTDs 7, 8 or 9 are done, an IRQ for each of the PTD will be raised.

#### **Embedded Hi-Speed USB host controller**

| Table 5. | Using the ik | Q Wask AND O | IRQ Wask | OR registers |                       |

|----------|--------------|--------------|----------|--------------|-----------------------|

| PTD      | AND register | OR register  | Time     | PTD done     | IRQ                   |

| 1        | 1            | 0            | 1 ms     | 1            | -                     |

| 2        | 1            | 0            | -        | 1            | -                     |

| 3        | 0            | 0            | -        | -            | -                     |

| 4        | 1            | 0            | 3 ms     | 1            | active because of AND |

| 5        | 0            | 0            | -        | -            | -                     |

| 6        | 0            | 0            | -        | -            | -                     |

| 7        | 0            | 1            | 5 ms     | 1            | active because of OR  |

| 8        | 0            | 1            | 6 ms     | 1            | active because of OR  |

| 9        | 0            | 1            | 7 ms     | 1            | active because of OR  |

Table 5. Using the IRQ Mask AND or IRQ Mask OR registers

## 7.5 Phase-Locked Loop (PLL) clock multiplier