RoHS

COMPLIANT

HALOGEN FREE

Vishay Siliconix

# 3 A, Fault Protected, Slew Rate Controlled Load Switch

### **DESCRIPTION**

The SiP32441 is an integrated slew rate control load switch operates in the voltage range of 1.7 V to 5.5 V. The integrated charge pump drivers enable the part with low on resistance over the wide input voltage range. Its  $V_{\rm IN}$  can tolerate over -2 V without causing damage or device malfunction.

The SiP32441 features a controlled soft-on slew rate of typical 2.5 ms that limits the inrush current for designs of heavy capacitive load and minimizes the resulting voltage droop at the power rails.

The SiP32441 integrated a special logic circuit to define the status of the power switch. This is to meet system design of both removable and embedded types.

The SiP32441 has exceptionally low shutdown current and provides reverse blocking to prevent high current flowing into the power source when the switch is off or  $V_{\rm IN}$  is ground.

The switch blocks the current flow at both forward and reverse directions at off state. When  $V_{\text{IN}}$  and EN are OPEN, the switch will remains OFF in case voltage is applied on OUT pin.

This device is specified to operate over the industrial temperature range of -40  $^{\circ}$ C to +85  $^{\circ}$ C

#### **FEATURES**

- 1.7 V to 5.5 V input voltage range

- Negative input voltage tolerance down to -2 V

- 38 m $\Omega$  typical R<sub>ON</sub> from 1.8 V to 5 V

- 3 A maximum continuous switch current

- Slew rate controlled turn-on: 2.5 ms at 3.6 V

- 2.3 V UVLO when EN is open

- Reverse current blocking when switch is off or V<sub>IN</sub> is ground

- ESD protected

- HBM: > 6 kV

- MM: > 300 V

- IEC61000-4-2 air discharge: > 15 kV

- IEC61000-4-2 contact discharge: > 8 kV

- Compact TDFN4 package

- Material categorization: for definitions of compliance please see <a href="https://www.vishay.com/doc?99912">www.vishay.com/doc?99912</a>

#### **APPLICATIONS**

- PDAs / smart phones

- Notebook / netbook computers

- Tablet PC

- Portable media players

- Digital camera

- · GPS navigation devices

- Data storage devices

- · Optical, industrial, medical, and healthcare devices

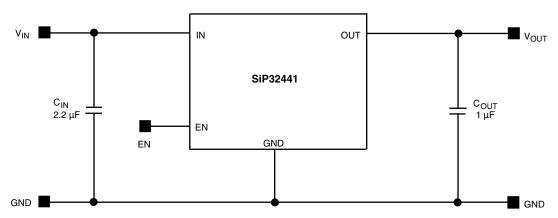

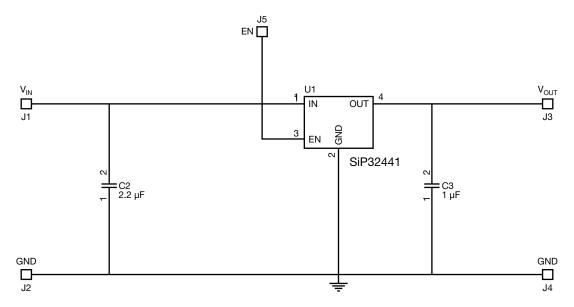

### TYPICAL APPLICATION CIRCUIT

Fig. 1 - SiP32441 Typical Application Circuit

| ORDERING INFORMATION |                       |         |                   |  |  |

|----------------------|-----------------------|---------|-------------------|--|--|

| Part Number Package  |                       | Marking | Temperature Range |  |  |

| SiP32441DNP-T1-GE4   | TDFN4 1.2 mm x 1.6 mm | Tx      | -40 °C to +85 °C  |  |  |

#### Notes

- x = Lot code

- GE4 denotes halogen-free and RoHS compliant

| ABSOLUTE MAXIMUM RATINGS                                            |                                                |             |      |  |

|---------------------------------------------------------------------|------------------------------------------------|-------------|------|--|

| Parameter                                                           | Limit                                          | Unit        |      |  |

| Supply Input Voltage (V <sub>IN</sub> )                             | -2 to +6                                       |             |      |  |

| Enable Input Voltage (V <sub>EN</sub> )                             | able Input Voltage (V <sub>EN</sub> ) -2 to +6 |             | V    |  |

| Output Voltage (V <sub>OUT</sub> )                                  | -0.3 to +6                                     |             |      |  |

| Maximum Continuous Switch Current (I <sub>max.</sub> ) <sup>c</sup> |                                                | 3.5         | A    |  |

| Maximum Repetitive Pulsed Current (1 ms, 1                          | 7                                              |             |      |  |

| Maximum Non-Repetitive Pulsed Current (10                           | 12                                             |             |      |  |

| Junction Temperature (T <sub>J</sub> )                              |                                                | -40 to +150 | °C   |  |

| Thermal Resistance (q <sub>JA</sub> ) <sup>a</sup>                  |                                                | 170         | °C/W |  |

| Power Dissipation (P <sub>D</sub> ) a,b                             |                                                | 735         | mW   |  |

| ESD Rating                                                          | НВМ                                            | 6           | kV   |  |

|                                                                     | MM                                             | 300         | V    |  |

|                                                                     | IEC41000-4-2 Air Discharge <sup>d</sup>        | 15          | kV   |  |

|                                                                     | IEC41000-4-2 Contact Discharge <sup>d</sup>    | 8           | r. v |  |

### Notes

- a. Device mounted with all leads and power pad soldered or welded to PC board, see PCB layout.

- b. Derate 5.9 mW/°C above  $T_A = 25$  °C, see PCB layout.

- c.  $T_A = 25$  °C, see PCB layout.

- d. Tested on  $V_{\text{IN}}$  with 2.2  $\mu\text{F}$   $C_{\text{IN}}.$   $V_{\text{IN}}$  connected to micro-USB connector.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE                            |             |      |  |  |

|--------------------------------------------------------|-------------|------|--|--|

| Parameter                                              | Limit       | Unit |  |  |

| Input Voltage Range (V <sub>IN</sub> )                 | 1.7 to 5.5  | V    |  |  |

| Operating Junction Temperature Range (T <sub>J</sub> ) | -40 to +125 | °C   |  |  |

| SPECIFICATIONS                   |                      |                                                                                                    |                            |        |                  |        |  |

|----------------------------------|----------------------|----------------------------------------------------------------------------------------------------|----------------------------|--------|------------------|--------|--|

| Parameter                        | Symbol               | Test Conditions Unless Specified V <sub>IN</sub> = 1.8 V to 5 V, T <sub>A</sub> = -40 °C to +85 °C | Limits<br>-40 °C to +85 °C |        |                  | Unit   |  |

|                                  |                      | (typical values are at T <sub>A</sub> = 25 °C)                                                     | Min. a                     | Typ. b | Max. a           |        |  |

| Operating Voltage                | V <sub>IN</sub>      |                                                                                                    | 1.8                        | -      | 5.5              | ٧      |  |

| Negative Input Voltage Tolerance | I <sub>NEG</sub>     | V <sub>IN</sub> = -2 V                                                                             | -                          | -15    | -                | mA     |  |

| Linday Voltage Look Out          | UVLO <sub>H-L</sub>  | EN = open, 25 °C (switch On to Off)                                                                | -                          | -      | 2                |        |  |

| Under Voltage Lock Out           | UVLO <sub>L-H</sub>  | EN = open, 25 °C (switch Off to On)                                                                | 2.5                        | 2.3    | -                | V      |  |

| UVLO Hysteresis                  | UVLO <sub>HYS</sub>  | EN = open, 25 °C                                                                                   | -                          | 0.25   | -                |        |  |

|                                  |                      | $V_{IN} = 1.8 \text{ V}, \text{ EN} = \text{active}$                                               | -                          | 38     | 50               |        |  |

|                                  |                      | $V_{IN} = 2.5 \text{ V}$                                                                           | -                          | 58     | 70 <sup>d</sup>  |        |  |

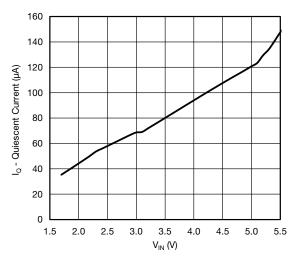

| Quiescent Current                | IQ                   | V <sub>IN</sub> = 3.6 V                                                                            | -                          | 82     | 100 <sup>d</sup> |        |  |

|                                  |                      | V <sub>IN</sub> = 4.3 V                                                                            | -                          | 101    | 120 <sup>d</sup> |        |  |

|                                  |                      | V <sub>IN</sub> = 5 V                                                                              | -                          | 119    | 150              | μA     |  |

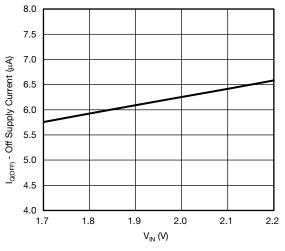

| Off Supply Current               | I <sub>Q(off)</sub>  | V <sub>IN</sub> = 2 V, V <sub>EN</sub> = 0 V, OUT = open                                           | -                          | 6.3    | 10               |        |  |

| Off Switch Current               | I <sub>DS(off)</sub> | $V_{IN} = 2 \text{ V}, V_{EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$                                | -                          | -      | 1                |        |  |

| Reverse Blocking Current         | I <sub>RB</sub>      | $V_{OUT} = 5 \text{ V}, V_{IN} = 0 \text{ V}, V_{EN} = 0 \text{ V} \text{ or open}$                | -                          | -      | 10               |        |  |

|                                  |                      | V <sub>IN</sub> = 1.8 V, I <sub>L</sub> = 500 mA, T <sub>A</sub> = 25 °C                           | -                          | 38     | 43               |        |  |

|                                  |                      | V <sub>IN</sub> = 2.5 V, I <sub>L</sub> = 500 mA, T <sub>A</sub> = 25 °C                           | -                          | 38     | 43               |        |  |

| On-Resistance                    | R <sub>DS(on)</sub>  | $V_{IN} = 3.6 \text{ V}, I_L = 500 \text{ mA}, T_A = 25 \text{ °C}$                                | -                          | 38     | 43               | mΩ     |  |

|                                  |                      | $V_{IN} = 4.3 \text{ V}, I_L = 500 \text{ mA}, T_A = 25 \text{ °C}$                                | -                          | 38     | 43               |        |  |

|                                  |                      | $V_{IN} = 5 \text{ V}, I_L = 500 \text{ mA}, T_A = 25 ^{\circ}\text{C}$                            | -                          | 38     | 43               |        |  |

|                                  |                      | V <sub>IN</sub> = 1.8 V                                                                            | -                          | -      | 0.5              |        |  |

|                                  | V <sub>IL</sub>      | $V_{IN} = 2.5 \text{ V}$                                                                           | -                          | -      | 0.7 <sup>d</sup> | <br> - |  |

| Input Logic Low <sup>c</sup>     |                      | V <sub>IN</sub> = 3.6 V                                                                            | -                          | -      | 1.1 <sup>d</sup> | -      |  |

|                                  |                      | V <sub>IN</sub> = 4.3 V                                                                            | -                          | -      | 1.3 <sup>d</sup> |        |  |

|                                  |                      | V <sub>IN</sub> = 5 V                                                                              | -                          | -      | 1.5 <sup>d</sup> |        |  |

|                                  | V <sub>IH</sub>      | V <sub>IN</sub> = 1.8 V                                                                            | 1.3                        | -      | -                | V      |  |

|                                  |                      | V <sub>IN</sub> = 2.5 V                                                                            | 1.6 <sup>d</sup>           | -      | -                |        |  |

| Input Logic High <sup>c</sup>    |                      | V <sub>IN</sub> = 3.6 V                                                                            | 1.9 <sup>d</sup>           | -      | -                |        |  |

|                                  |                      | V <sub>IN</sub> = 4.3 V                                                                            | 2.1 <sup>d</sup>           | -      | -                | -<br>- |  |

|                                  |                      | V <sub>IN</sub> = 5 V                                                                              | 2.4 <sup>d</sup>           | -      | -                |        |  |

| Enable Pin Bias Current          | I <sub>EN</sub>      | V <sub>EN</sub> = 5 V                                                                              | -                          | 5.4    | 7                | μA     |  |

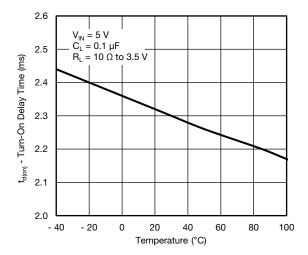

| Output Turn-On Delay Time        | t <sub>d(on)</sub>   |                                                                                                    | -                          | 1.3    | -                |        |  |

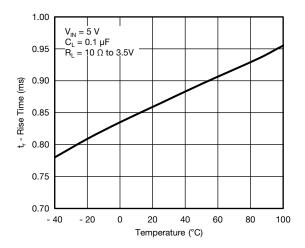

| Output Turn-On Rise Time         | t <sub>(on)</sub>    | $V_{IN} = 3.6 \text{ V}, R_{load} = 10 \Omega,$<br>$C_L = 0.1 \mu F, T_A = 25 \text{ °C}$          | -                          | 1.8    | 2.5              | ms     |  |

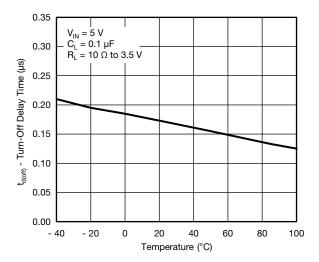

| Output Turn-Off Delay Time       | t <sub>d(off)</sub>  | Ο <sub>L</sub> = 0.1 μ1, 1 <sub>A</sub> = 20 0                                                     | -                          | 0.0002 | -                |        |  |

#### Notes

- a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

- b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- c. For  $V_{\text{IN}}$  outside this range consult typical EN threshold curve.

- d. Not tested, guarantee by design.

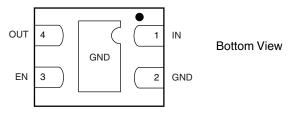

### **PIN CONFIGURATION**

Fig. 2 - TDFN4 1.2 mm x 1.6 mm Package

| PIN DESCRIPTION |      |                                      |  |

|-----------------|------|--------------------------------------|--|

| Pin Number      | Name | Function                             |  |

| 1               | IN   | This is the input pin of the switch  |  |

| 2               | GND  | Ground connection                    |  |

| 3               | EN   | Enable input                         |  |

| 4               | OUT  | This is the output pin of the switch |  |

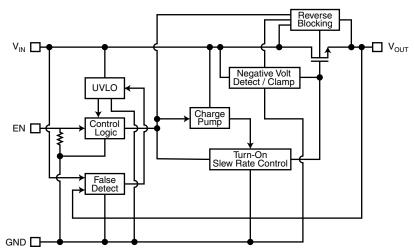

#### **BLOCK DIAGRAM**

Fig. 3 - Functional Block Diagram

| TRUTH TABLE |        |        |     |        |  |

|-------------|--------|--------|-----|--------|--|

| IN          |        | OUT    | EN  | SWITCH |  |

|             | L      | X      | X   | OFF    |  |

|             | > UVLO |        | X   | ON     |  |

| Н           | > 1.5  |        | Н   | ON     |  |

|             | < UVLO |        | L   | OFF    |  |

|             | L      | $\int$ | X   | OFF    |  |

| _           | Γ      | Н      | Н   | ON     |  |

| -           | Γ      | Н      | L   | OFF    |  |

| _           |        | Н      | (1) | ON     |  |

## Notes

- (1) It will be depending on the status of latch of the OR gate output. If latch is at high, then EN cannot off the switch. If latch is low, then EN can off the switch.

- IN has UVLO. High at IN column means a voltage source is applied to IN, that is high enough to power the logic circuit but could be lower than the UVLO threshold.

- EN pin has a pull down of ~1 MΩ.

- UVLO threshold is about 2.3 V.

#### **DETAILED DESCRIPTION**

SiP32441 is an advanced slew rate controlled high side load switch with an integrated N-channel power switch. When the device is on the gate of the power switch is turned on at a controlled rate to avoid excessive inrush current. Once fully on the gate to source voltage of the power switch is biased at a constant level. The design gives a flat on resistance throughout the operating voltages. A special reverse blocking circuitry prevents current flowing from output to input when the switch is off. The  $V_{\rm IN}$  and EN pin can tolerate -2 V voltage without drawing excessive current. The device is turn-on after the UVLO voltage regardless the condition of the EN pin. A fault protection circuitry is incorporated to define the status of the switch. Its states are described in the truth table.

#### **APPLICATION INFORMATION**

#### **Input Capacitor**

In general, under steady state conditions the SiP32441 does not require an input capacitor. Nevertheless, an input bypass capacitor is recommended in order to reduce the input voltage drop caused by transient inrush currents. Commonly, a 2.2  $\mu F$  ceramic capacitor is sufficient and should be placed in close proximity to  $V_{IN}$  and GND pins. A higher value input capacitor can help to further reduce the voltage drop. Ceramic capacitors are recommended for their low ESR characteristic.

#### **Output Capacitor**

While these devices work without an output capacitor, a 1  $\mu F$  or higher value capacitor across  $V_{OUT}$  and GND is recommended in order to handle potential load transient conditions. In the event that the switch is turning of while running high current, circuit stray inductances might force the output to some negative voltage in order to mitigate this phenomenon a proper output capacitor is required.

#### **Enable**

The device is logic high active, the enable pin voltage can exceed  $V_{\text{IN}}$  as long as it is within the absolute maximum rating range.

If the input voltage is available before output voltage and either input or output voltage is above input UVLO threshold, the switch is on regardless of the enable pin voltage even if the input pin is left open later. In this case, the enable pin cannot be used to turn off the switch except in the certain fault conditions as described by the truth table.

If the input voltage is available before output voltage and both the input voltage and output voltage are lower than the input UVLO threshold and above 1.5 V, the enable pin can be used to turn on and off the switch even if either input pin or output pin is left open later.

If the output voltage is available before the input voltage, the enable pin can be used to turn on/off the switch.

#### **Reverse Voltage Protection**

The SiP32441 contains a reverse blocking circuitry to protect the current from going to the input from the output when the switch is off. Reverse blocking works for input voltage as low as 0 V.

#### THERMAL CONSIDERATIONS

The maximum allowed DC Current depends on the thermal condition in which the device operates. In order to calculate max allowed DC current, first the max power dissipation should be considered.

The SiP32441 is packaged in a TDFN4 1.2 mm x 1.6 mm package which has a thermal resistance of  $\theta_{J-A}{}^a = 170 \, ^{\circ}\text{C/W}$ .

#### Note

Device mounted with all leads and power pad soldered or welded to PC board, see PCB layout. For any other layout configuration the actual junction to ambient thermal impedance should be considered

The following formula shows the maximum allowed power dissipation as a function of the ambient temperature  $T_A$  when the maximum junction temperature is limited to  $T_{J\,(max.)} = 125\,^{\circ}\text{C}$ :

$$P_{\text{max.}} = \frac{T_{J}(\text{max.}) - T_{A}}{\theta_{J-A}} = \frac{125 - T_{A}}{170}$$

For example at ambient temperature of 70 °C, the maximum power dissipation will be limited to about 324 mW.

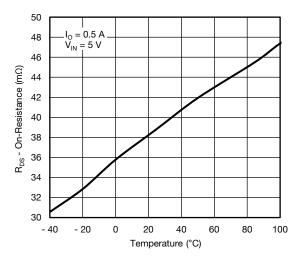

In order to calculate the maximum allowed DC current the switch  $R_{\text{DS(on)}}$  temperature dependency should be considered.

As an example let us calculate maximum load current at  $T_A = 70~^{\circ}\text{C}$  and input voltage of 1.8 V. At this input voltage the  $R_{DS(on)}$  at 25  $^{\circ}\text{C}$  43 m $\Omega$  (see specification table). The  $R_{DS(on)}$  at 125  $^{\circ}\text{C}$  can be extrapolated from this data using the following formula:

$$R_{DS(on)}_{125 \text{ °C}} = R_{DS(on)}_{25 \text{ °C}} x (1 + T_C x (T_{J \text{ max.}} - 25)/100)$$

Where  $T_C$  is the  $R_{DS(on)}$  temperature coefficient expressed in percent change per  $^\circ$  C.

For SiP32441 the approximated value is 0.31 %/°C.  $T_{J \text{ max.}}$  is the maximum allowed junction temperature (125 °C). Therefore,

$$R_{DS(on) (at 125 \, ^{\circ}C)} =$$

43 mΩ x (1 + 0.31 x (125 - 25)/100) ≈ 57 mΩ

The maximum current limit is then determined by

$$I_{LOAD}$$

(max.)  $<\sqrt{\frac{P \text{ (max.)}}{R_{DS(on)}}}$

Which in this case is 2.38 A.

www.vishay.com

# Due to device limitation the max switch DC current should not exceed 3 A in any condition.

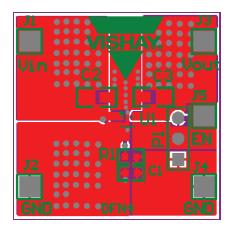

To obtain the highest power dissipation the power pad of the device should be connected to a heat sink on the printed circuit board. Fig. 4 shows a typical PCB layout. All copper traces and vias for the  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  pins should be sized adequately to carry the maximum continuous current.

#### **Negative Input Voltage**

The SiP32441 can withstand maximum negative 2 V at its input due to any spike from abnormal or fault condition of the system.

#### **Recommended Board Layout**

For improved performance, all traces should be as short as possible to minimize stray inductances and parasitic effects. The input and output capacitors should be kept as close as possible to the input and output pins respectively. Connecting the central exposed pad to GND, using wide traces for input, output, and GND help reducing the case to ambient thermal impedance. See fig. 4.

#### **BOARD LAYOUT**

Fig. 4 - Recommended Board Layout

#### TYPICAL APPLICATION SCHEMATIC

Fig. 5 - Application Schematic

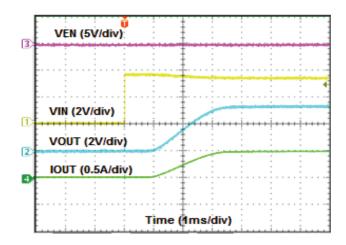

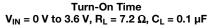

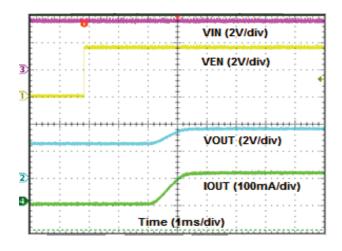

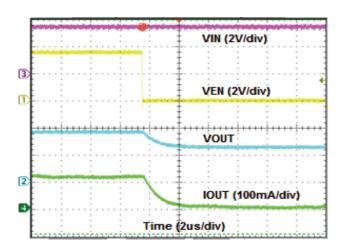

#### TYPICAL TURN-ON AND TURN-OFF WAVEFORMS

Turn-Off Time  $\label{eq:Vin} V_{IN} = 3.6~V~to~0~V,~R_L = 7.2~\Omega,~C_L = 0.1~\mu F$

Turn-On Time  $V_{IN} = 3.6 \text{ V, R}_L = 10 \ \Omega \text{ between OUT and } 2.5 \text{ V, C}_L = 0.1 \ \mu\text{F}$

Turn-Off Time  $V_{IN} = 3.6 \text{ V, R}_L = 10 \ \Omega \text{ between OUT and } 2.5 \text{ V, C}_L = 0.1 \ \mu\text{F}$

## TYPICAL CHARACTERISTICS (internally regulated, 25 °C, unless otherwise noted)

Fig. 6 - Quiescent Current vs. Input Voltage

Fig. 7 - Off Supply Current vs. Input Voltage

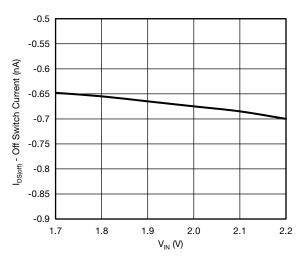

Fig. 8 - Off Switch Current vs. Input Voltage

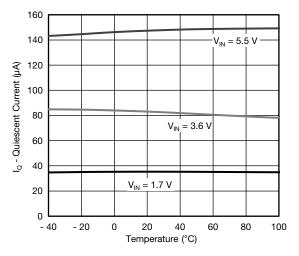

Fig. 9 - Quiescent Current vs. Temperature

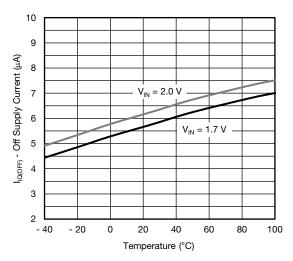

Fig. 10 - Off Supply Current vs. Temperature

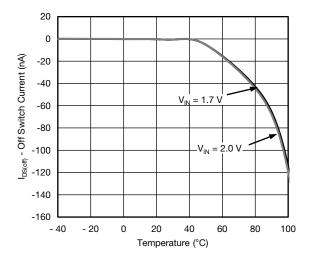

Fig. 11 - Off Switch Current vs. Temperature

## TYPICAL CHARACTERISTICS (internally regulated, 25 °C, unless otherwise noted)

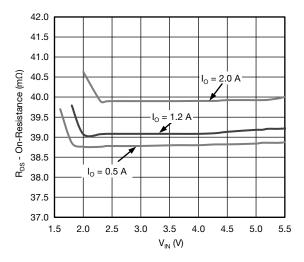

Fig. 12 - On-Resistance vs. Input Voltage

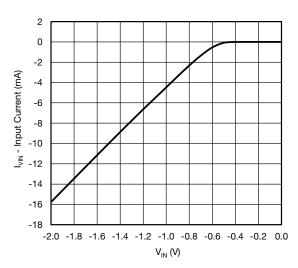

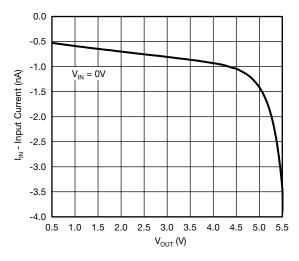

Fig. 13 - Input Current vs. Negative Input Voltage

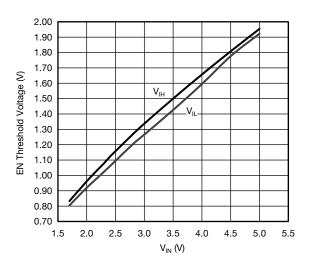

Fig. 14 - Threshold Voltage vs. Input Voltage

Fig. 15 - On-Resistance vs. Temperature

Fig. 16 - Reverse Blocking Current vs. Output Voltage

Fig. 17 - Rise Time vs. Temperature

www.vishay.com

## TYPICAL CHARACTERISTICS (internally regulated, 25 °C, unless otherwise noted)

Fig. 18 - Turn-On Delay Time vs. Temperature

Fig. 19 - Turn-Off Delay Time vs. Temperature

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see www.vishay.com/ppg?65763.

# **Legal Disclaimer Notice**

Vishay

# **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

Revision: 13-Jun-16 1 Document Number: 91000

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Vishay:

SIP32441DNP-T1-GE4