## PGA970 LVDT Sensor Signal Conditioner

### 1 Features

- Analog Features

- Programmable-Gain Analog Front End for LVDT Sensors

- Excitation Waveform Generator and Amplifier

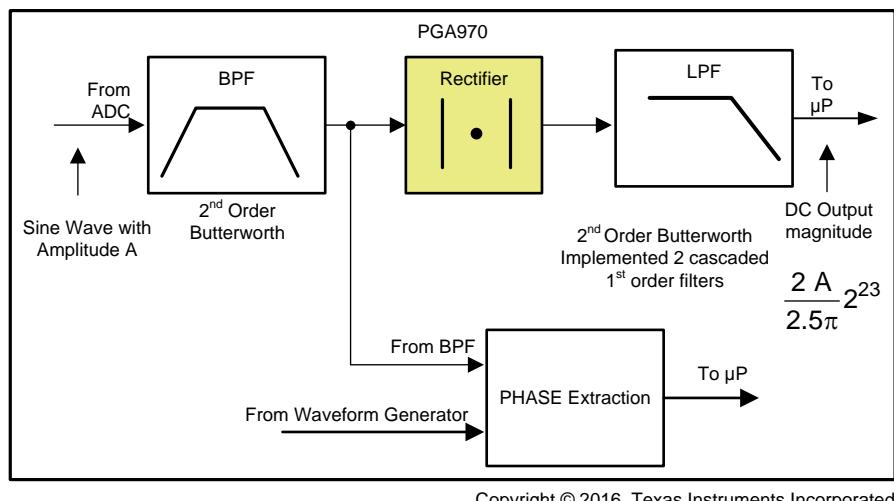

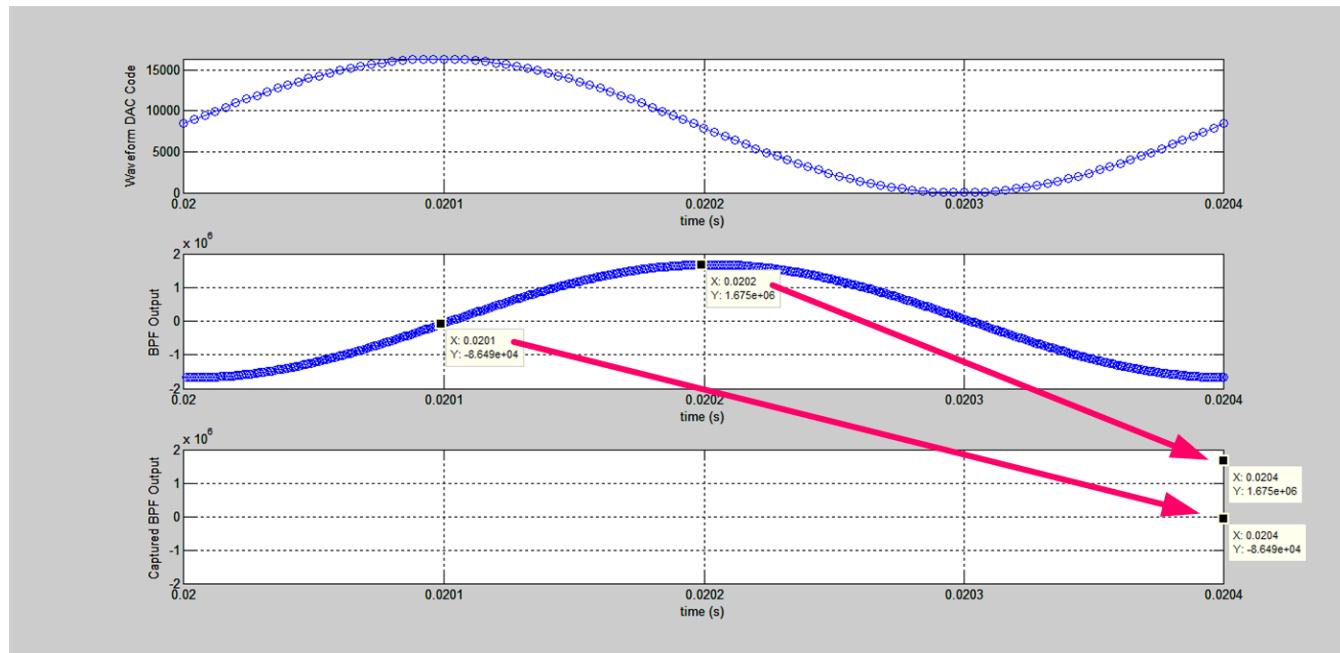

- Dual 24-Bit ADC With Amplitude and Phase Demodulators

- 24-Bit Auxiliary ADC

- On-Chip Internal Temperature Sensor

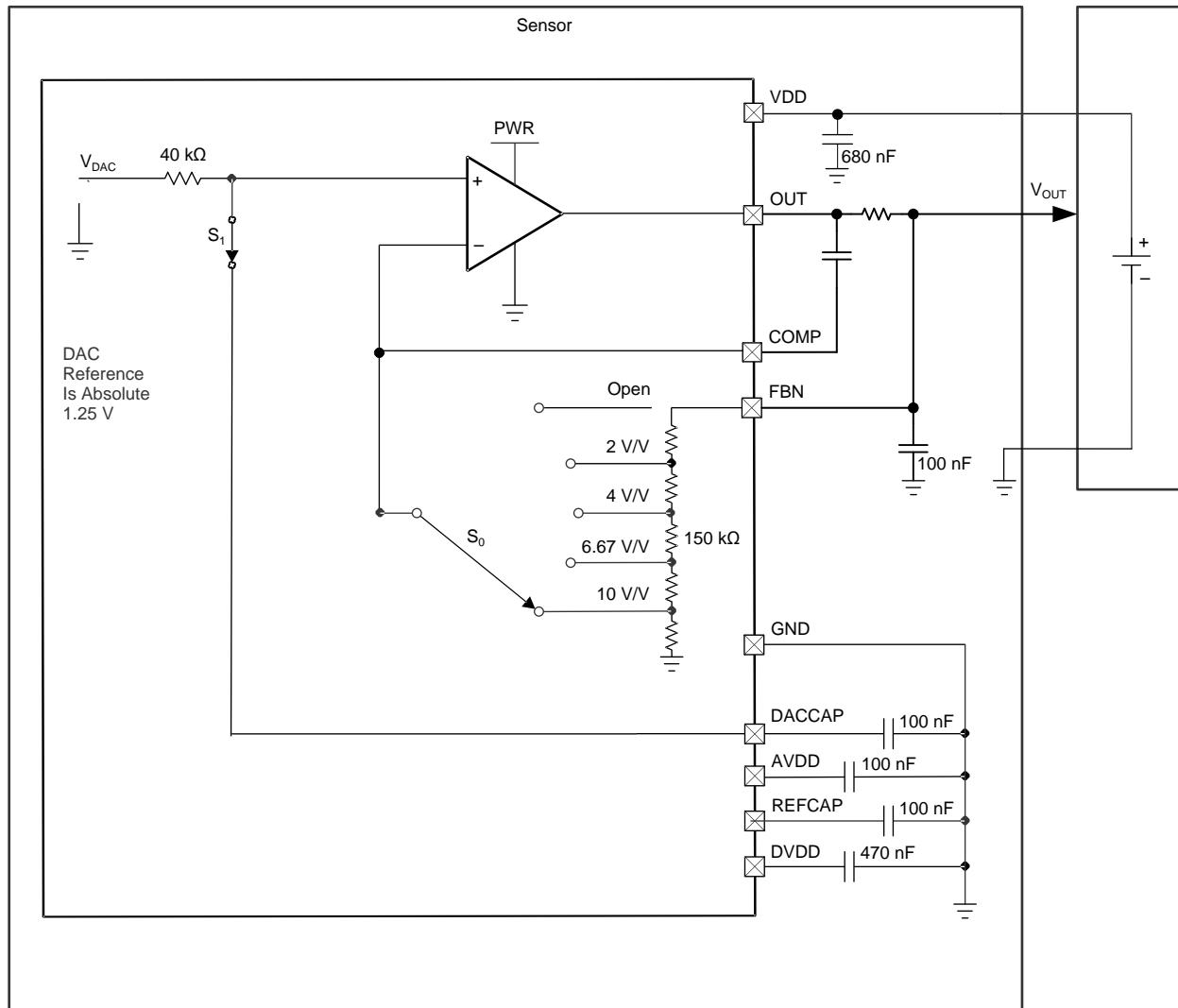

- 14-Bit Output DAC With Programmable Gain

- Built-In Diagnostics

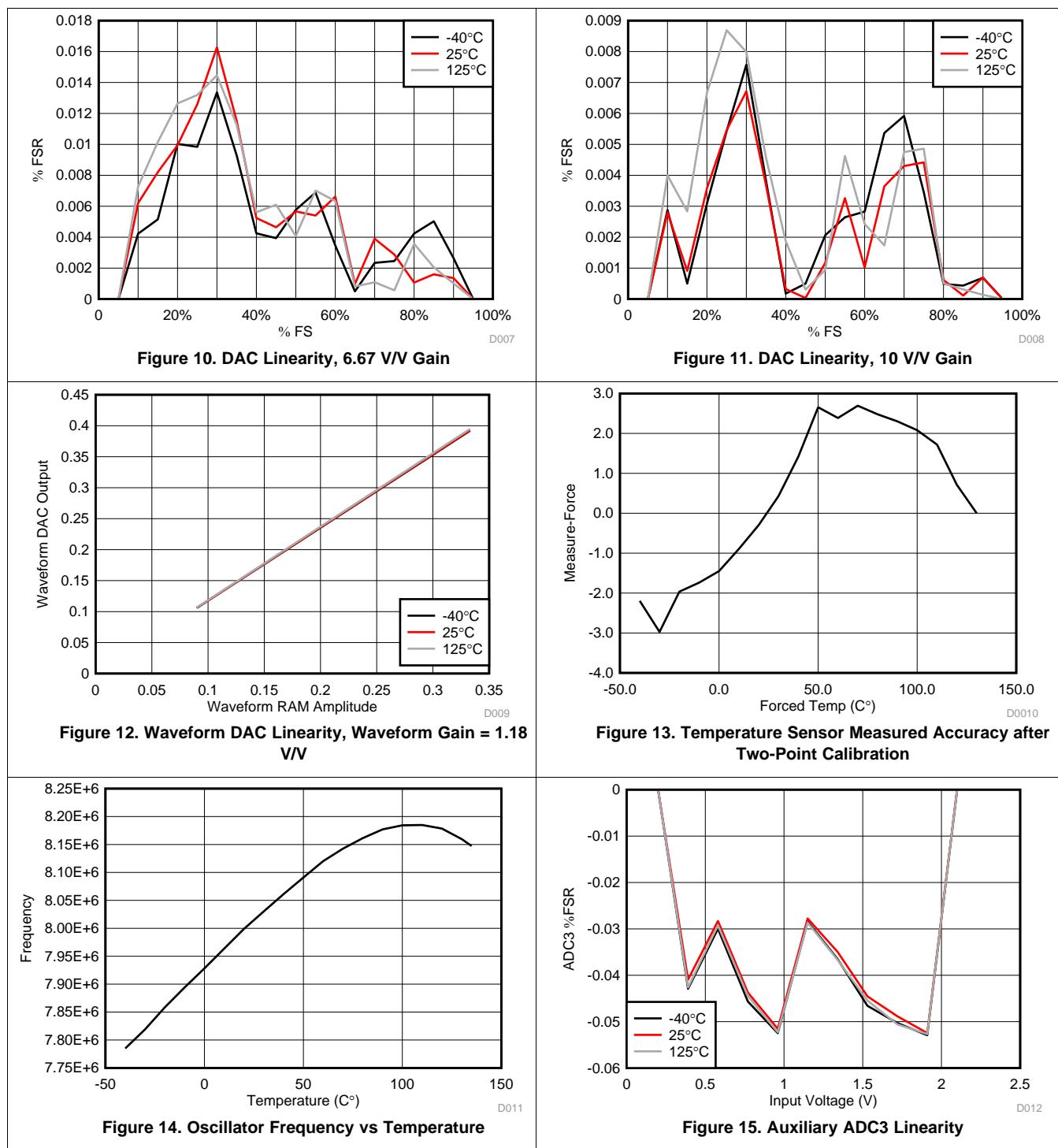

- Digital Features

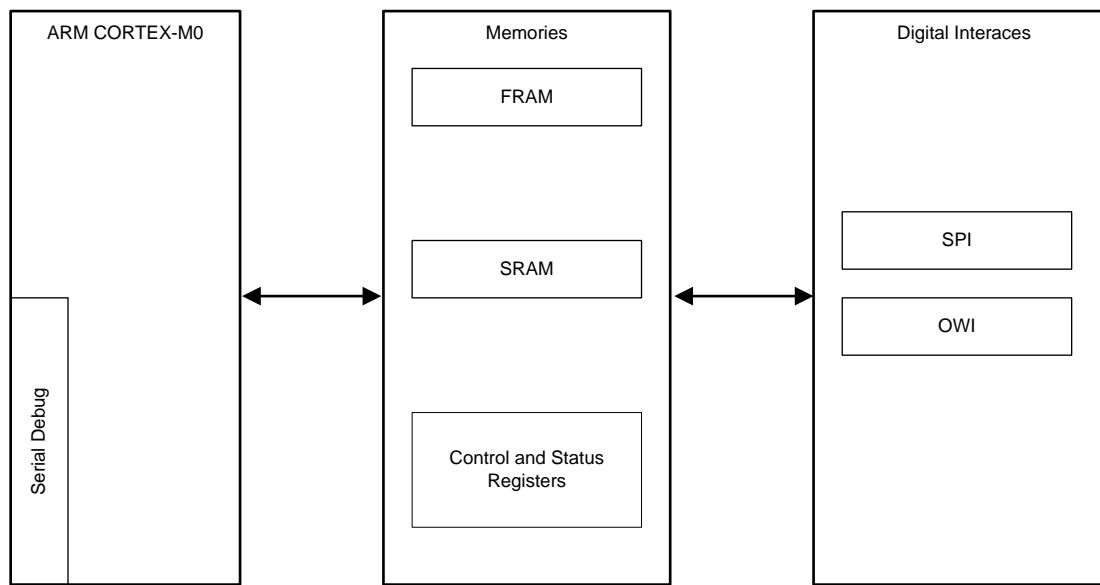

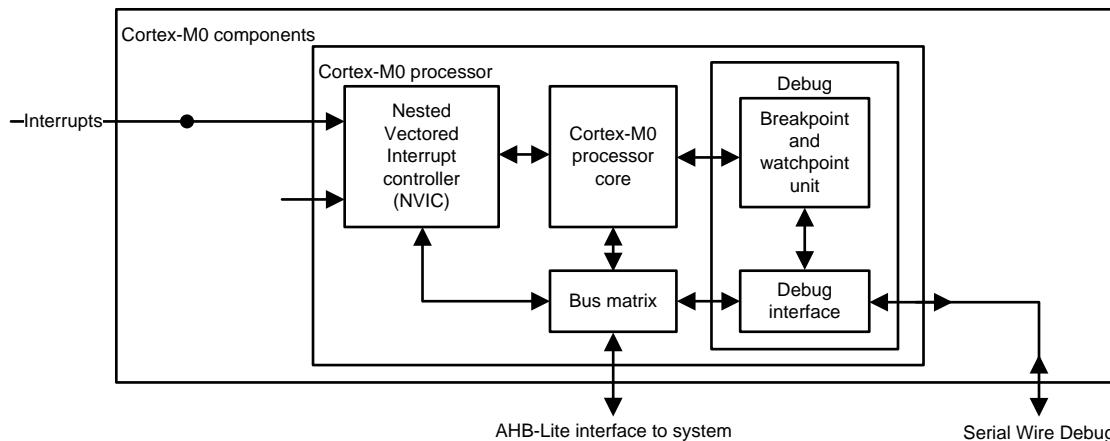

- ARM® Cortex®-M0 Microcontroller

- 16KB Ferroelectric RAM (FRAM) Program Memory

- 2KB General-Purpose RAM

- 512B RAM Waveform-Generator Look-Up Table

- 8-MHz On-Chip Oscillator

- Peripheral Features

- Serial Peripheral Interface (SPI)

- One-Wire Interface (OWI)

- Ratiometric and Absolute Voltage Output

- General Features

- Operational Supply Range: 3.5 V to 30 V

- Ambient Temperature Range: –40°C to +125°C

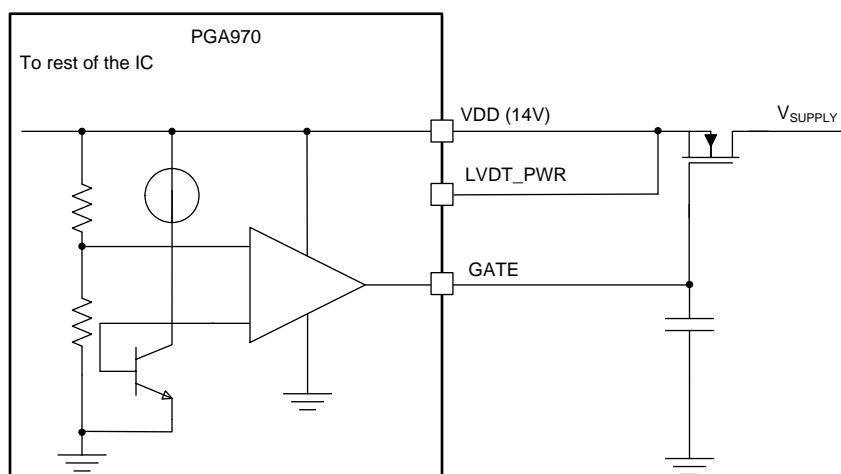

- DMOS Gate Controller for Extended Supply Range >30 V

### 2 Applications

- Position Sensor Signal Conditioning

- Linear Variable Differential Transformer (LVDT)

- Rotational Variable Differential Transformer (RVDT)

- Resolver

- RLC Measurement

### 3 Description

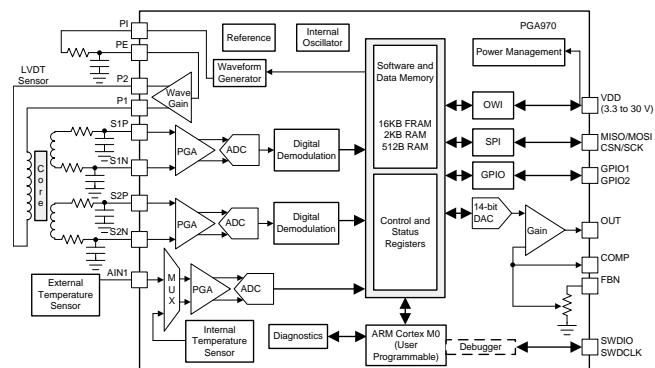

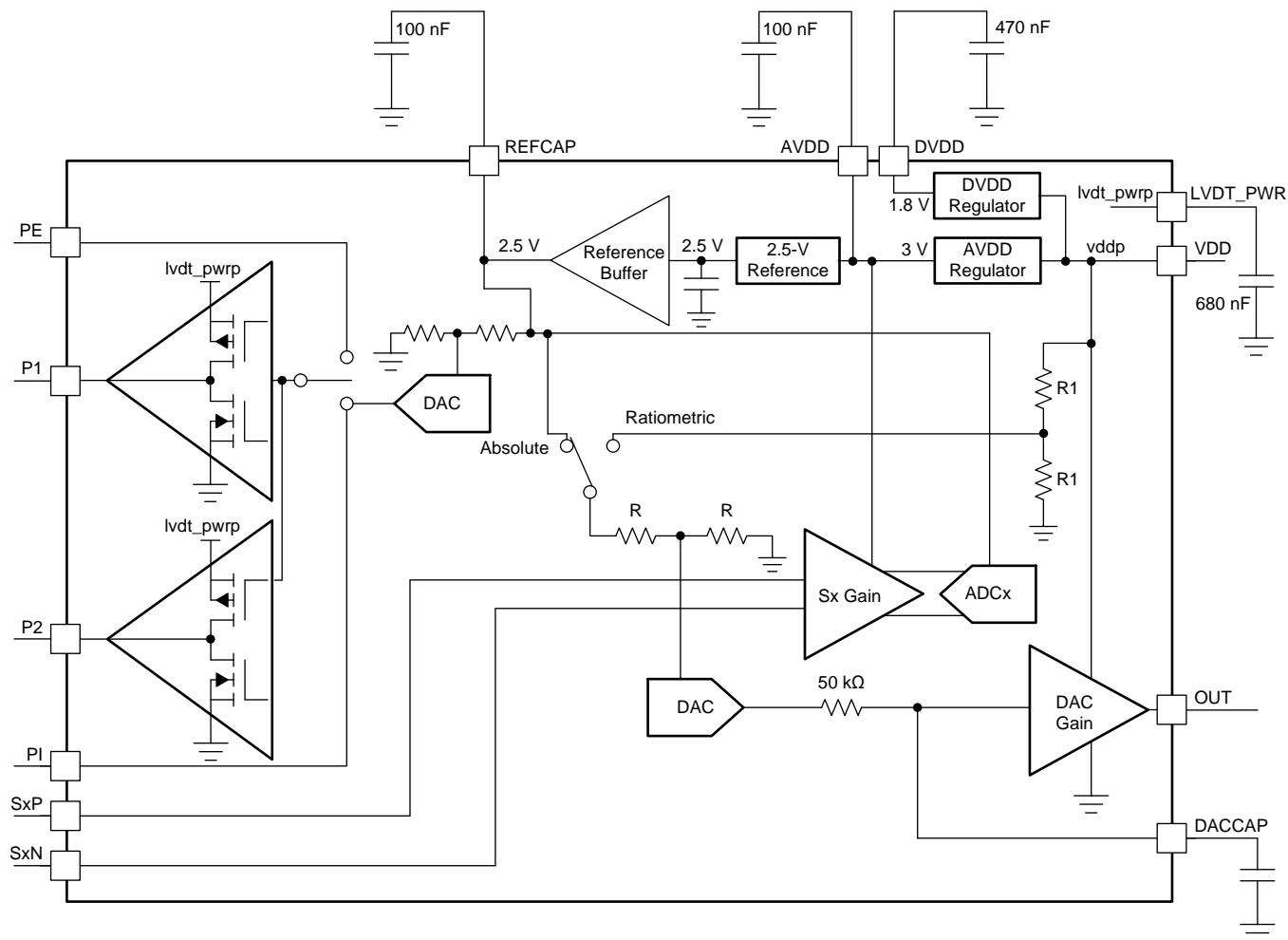

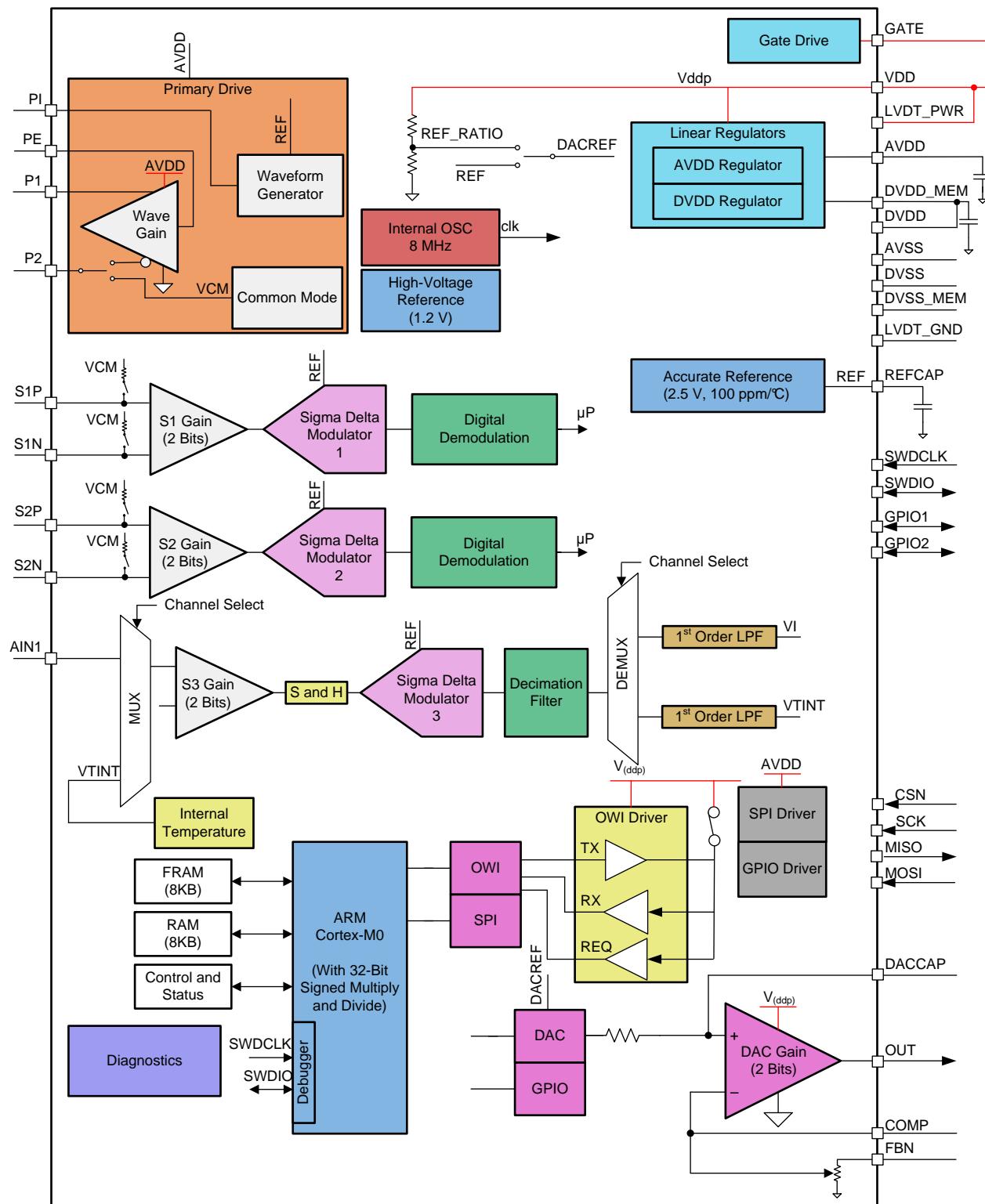

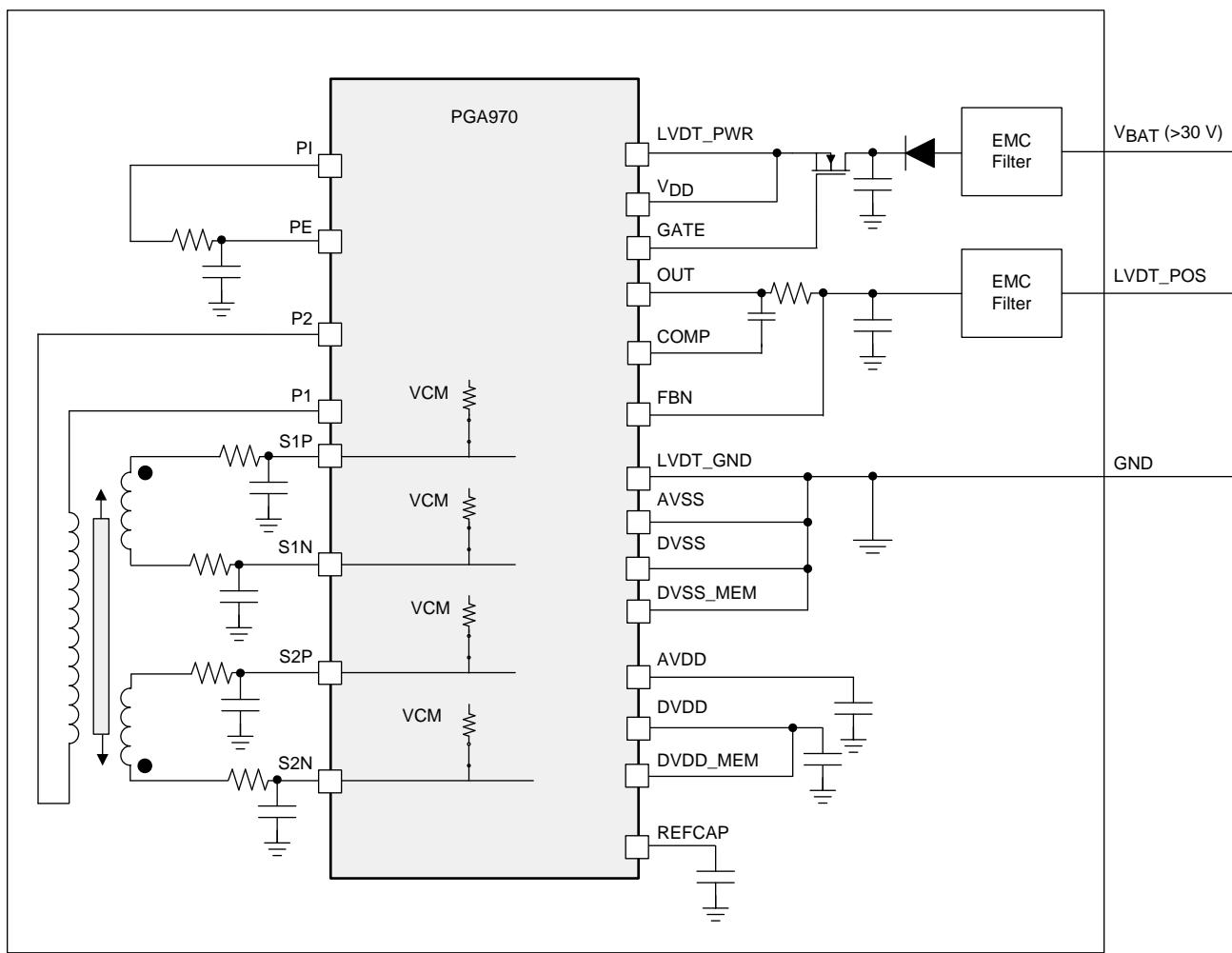

The PGA970 device is a highly integrated system-on-chip LVDT sensor-signal conditioner with advanced signal-processing capabilities. It contains a three-channel, low-noise, programmable-gain, analog front end that allows direct connection to the sense element, followed by three independent 24-bit delta-sigma ADCs.

Further, the device contains a digital signal-demodulation block that interfaces to an integrated ARM-Cortex M0 MCU, allowing implementation of custom sensor-compensation algorithms stored in the device nonvolatile memory. External system communication is achieved by using any of the SPI, OWI, GPIO, or PWM digital interfaces. Analog output is supported through a 14-bit DAC and programmable-gain amplifier offering reference or absolute-voltage output. Sensing-element excitation is achieved by the use of an integrated waveform generator and waveform amplifier. The waveform signal data is user-defined and stored in a designated RAM memory area.

Besides the primary functional components, the PGA970 device is equipped with additional support circuitry. The device diagnostics, sensor diagnostics, and integrated temperature sensor provide protection and information about the integrity of the overall system and sensing element. The device also includes a gate-controller circuit which when used with an external depletion MOSFET can regulate the device supply voltage in systems where the supply voltage exceeds 30 V.

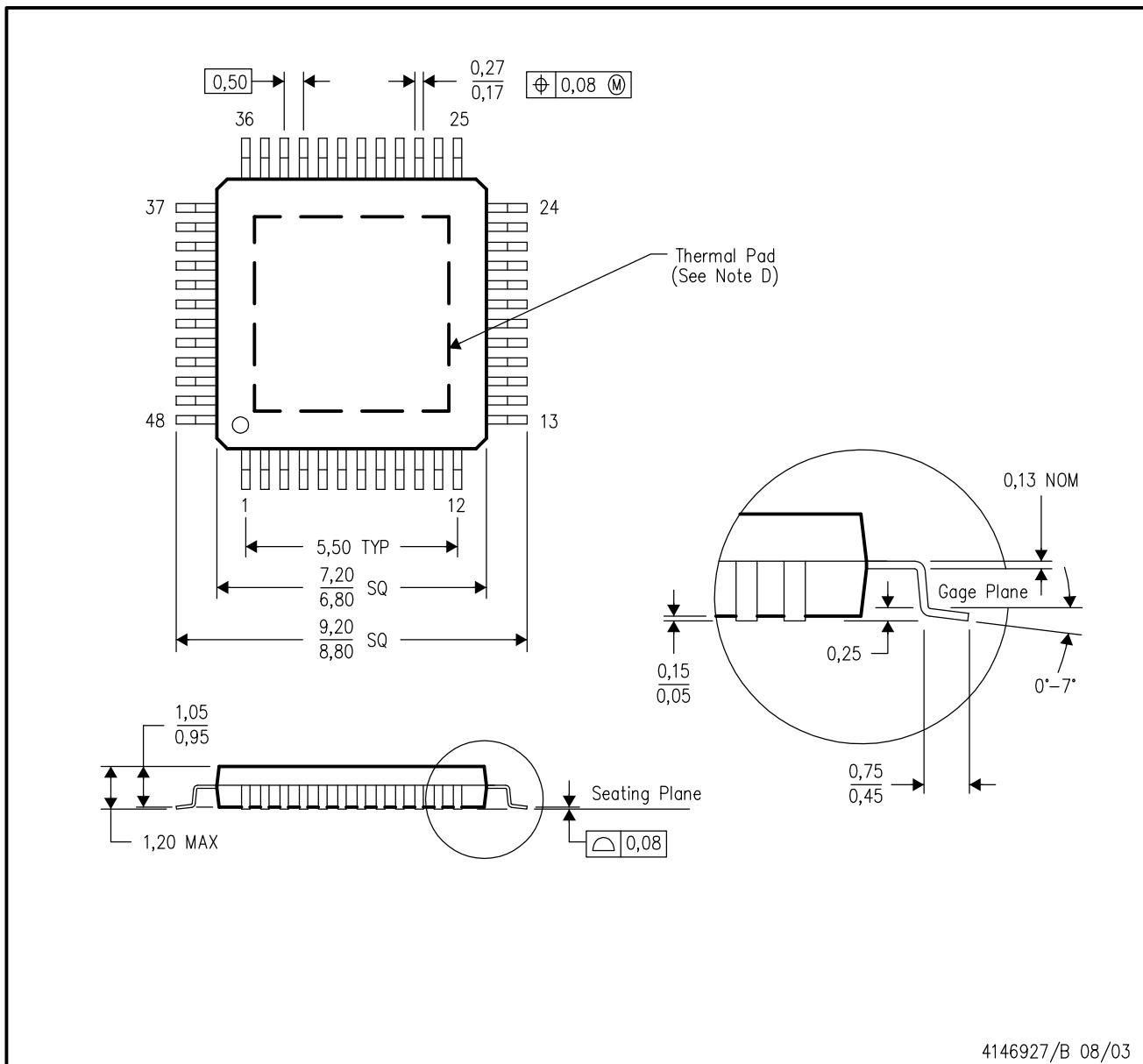

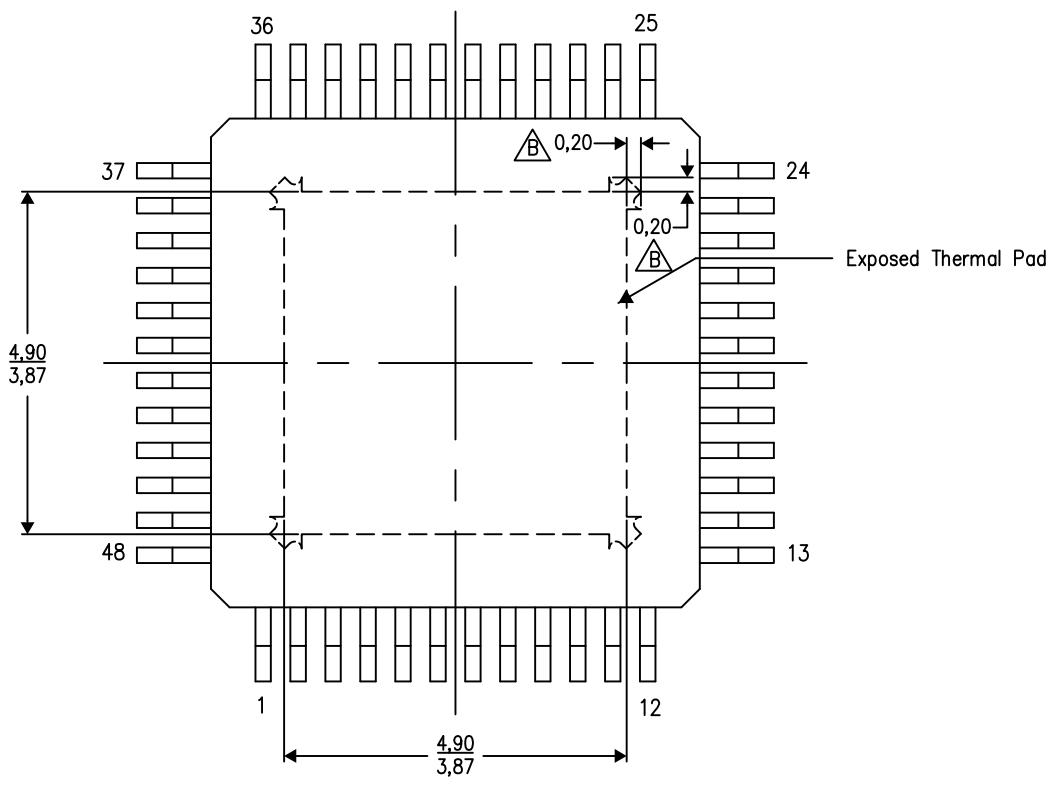

### Device Information<sup>(1)</sup>

| ORDER NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|--------------|------------|-------------------|

| PGA970QPHPR  | HTQFP (48) | 7.00 mm × 7.00 mm |

| PGA970QPHPT  |            |                   |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### Simplified Diagram

Copyright © 2016, Texas Instruments Incorporated

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|          |                                                                                      |          |           |                                                          |            |

|----------|--------------------------------------------------------------------------------------|----------|-----------|----------------------------------------------------------|------------|

| <b>1</b> | <b>Features</b> .....                                                                | <b>1</b> | 6.20      | GPIO, Digital Test-In and Test-Out Buffers .....         | <b>13</b>  |

| <b>2</b> | <b>Applications</b> .....                                                            | <b>1</b> | 6.21      | Non-Volatile Memory.....                                 | <b>13</b>  |

| <b>3</b> | <b>Description</b> .....                                                             | <b>1</b> | 6.22      | Diagnostics.....                                         | <b>13</b>  |

| <b>4</b> | <b>Revision History</b> .....                                                        | <b>2</b> | 6.23      | M0 .....                                                 | <b>14</b>  |

| <b>5</b> | <b>Pin Configuration and Functions</b> .....                                         | <b>3</b> | 6.24      | Digital Demodulation .....                               | <b>14</b>  |

| <b>6</b> | <b>Specifications</b> .....                                                          | <b>5</b> | 6.25      | SPI Timing Requirements .....                            | <b>15</b>  |

| 6.1      | Absolute Maximum Ratings .....                                                       | 5        | 6.26      | Typical Characteristics .....                            | <b>18</b>  |

| 6.2      | ESD Ratings.....                                                                     | 5        | <b>7</b>  | <b>Detailed Description</b> .....                        | <b>20</b>  |

| 6.3      | Recommended Operating Conditions .....                                               | 5        | 7.1       | Overview .....                                           | <b>20</b>  |

| 6.4      | Thermal Information .....                                                            | 5        | 7.2       | Functional Block Diagram .....                           | <b>21</b>  |

| 6.5      | Electrical Characteristics – External N-Channel<br>Depletion MOSFET Gate Drive ..... | 6        | 7.3       | Feature Description .....                                | <b>22</b>  |

| 6.6      | Electrical Characteristics - Regulators .....                                        | 6        | 7.4       | Device Functional Modes.....                             | <b>55</b>  |

| 6.7      | Electrical Characteristics – Internal Reference .....                                | 6        | 7.5       | Programming Tips .....                                   | <b>57</b>  |

| 6.8      | Electrical Characteristics – Internal Oscillator .....                               | 6        | 7.6       | Register Maps .....                                      | <b>60</b>  |

| 6.9      | Electrical Characteristics – LVDT Primary Supply<br>Waveform Generator .....         | 7        | <b>8</b>  | <b>Application and Implementation</b> .....              | <b>109</b> |

| 6.10     | Electrical Characteristics – LVDT Primary Supply<br>Waveform Gain .....              | 7        | 8.1       | Application Information.....                             | <b>109</b> |

| 6.11     | Electrical Characteristics – Internal Temperature<br>Sensor.....                     | 8        | 8.2       | Typical Application .....                                | <b>109</b> |

| 6.12     | Electrical Characteristics – S1 and S2 Gain .....                                    | 8        | <b>9</b>  | <b>Power Supply Recommendations</b> .....                | <b>110</b> |

| 6.13     | Electrical Characteristics – S3 Gain Stage .....                                     | 8        | <b>10</b> | <b>Layout</b> .....                                      | <b>111</b> |

| 6.14     | Electrical Characteristics – Digital Demodulators 1<br>and 2 .....                   | 9        | 10.1      | Layout Guidelines .....                                  | <b>111</b> |

| 6.15     | Electrical Characteristics – Analog-to-Digital<br>Converter 3 .....                  | 10       | 10.2      | Layout Example .....                                     | <b>111</b> |

| 6.16     | Electrical Characteristics – One-Wire Interface ....                                 | 11       | <b>11</b> | <b>Device and Documentation Support</b> .....            | <b>112</b> |

| 6.17     | Electrical Characteristics – SPI.....                                                | 11       | 11.1      | Documentation Support .....                              | <b>112</b> |

| 6.18     | DAC Output.....                                                                      | 11       | 11.2      | Receiving Notification of Documentation<br>Updates ..... | <b>112</b> |

| 6.19     | DAC Gain.....                                                                        | 12       | 11.3      | Community Resources.....                                 | <b>112</b> |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (January 2016) to Revision A                                      | Page     |

|-----------------------------------------------------------------------------------------|----------|

| • Changed the device status from <i>Product Preview</i> to <i>Production Data</i> ..... | <b>1</b> |

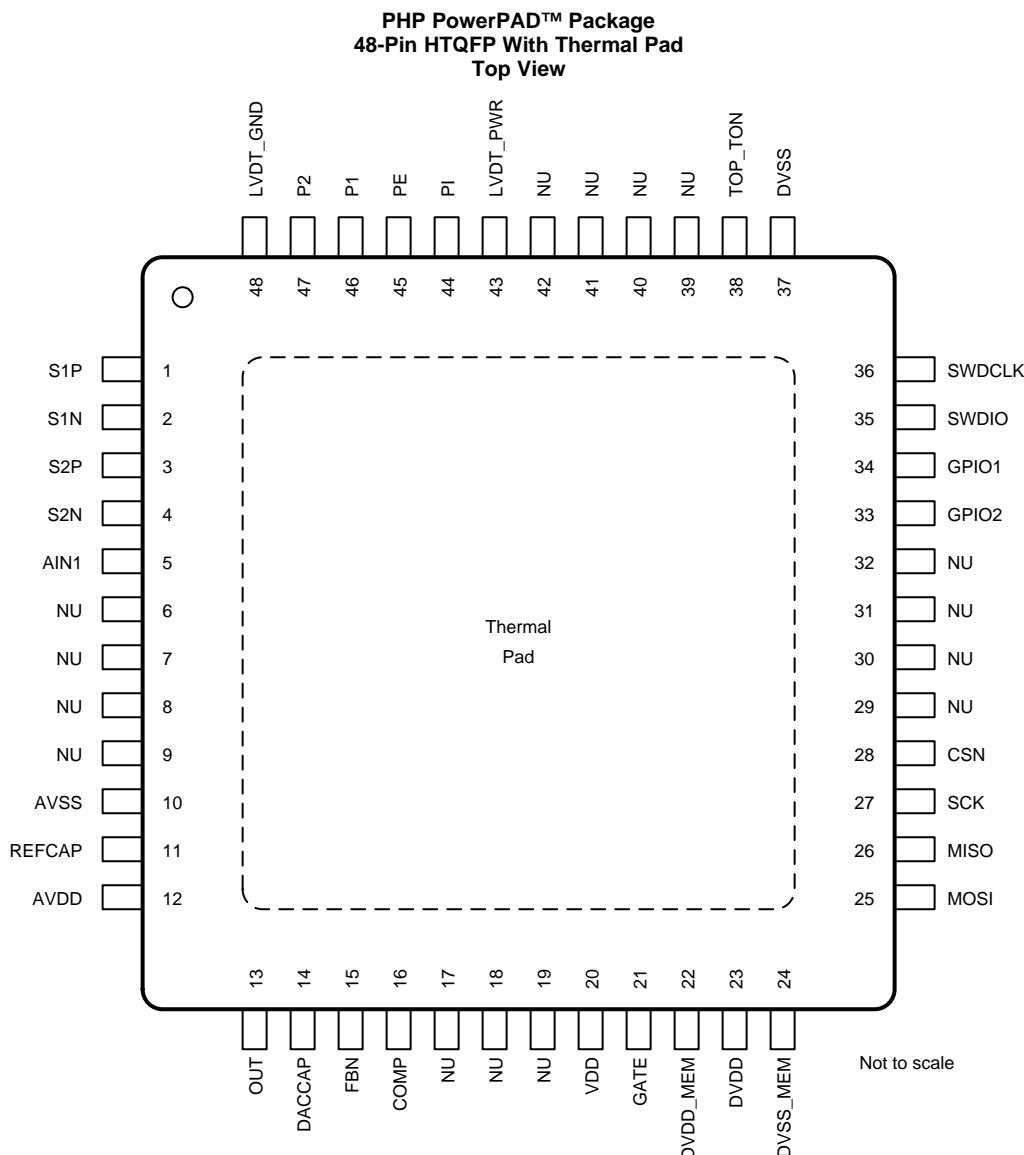

## 5 Pin Configuration and Functions

NU – Make no external connection.

**PGA970 Pin Functions**

| PIN             |                                                                    | I/O | DESCRIPTION                                                                                                         |

|-----------------|--------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.                                                                |     |                                                                                                                     |

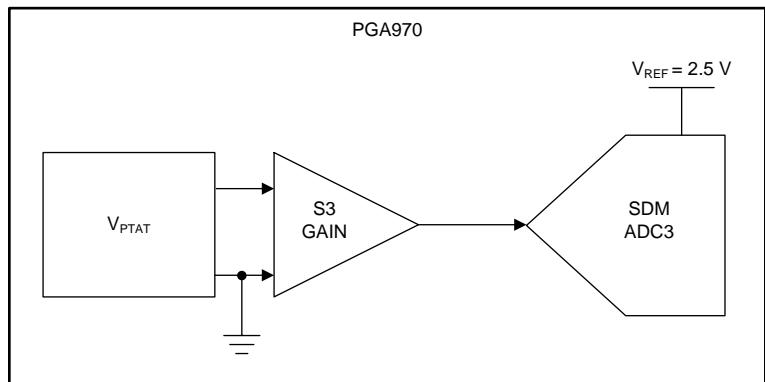

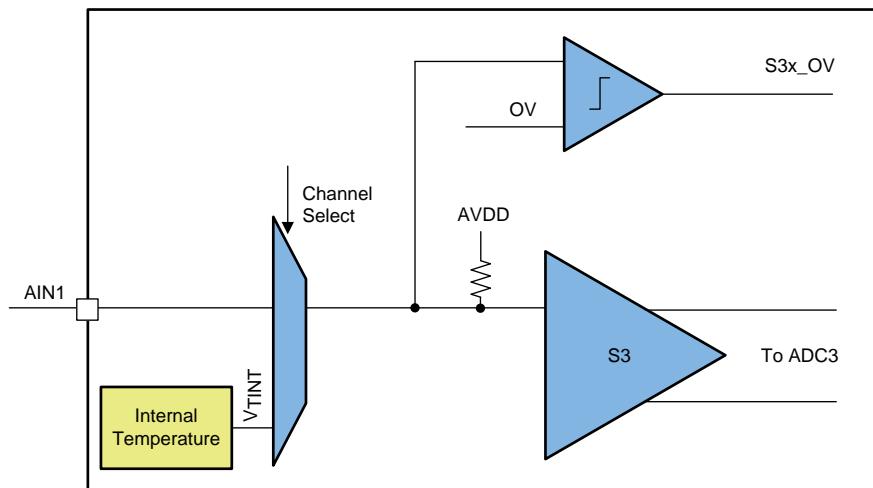

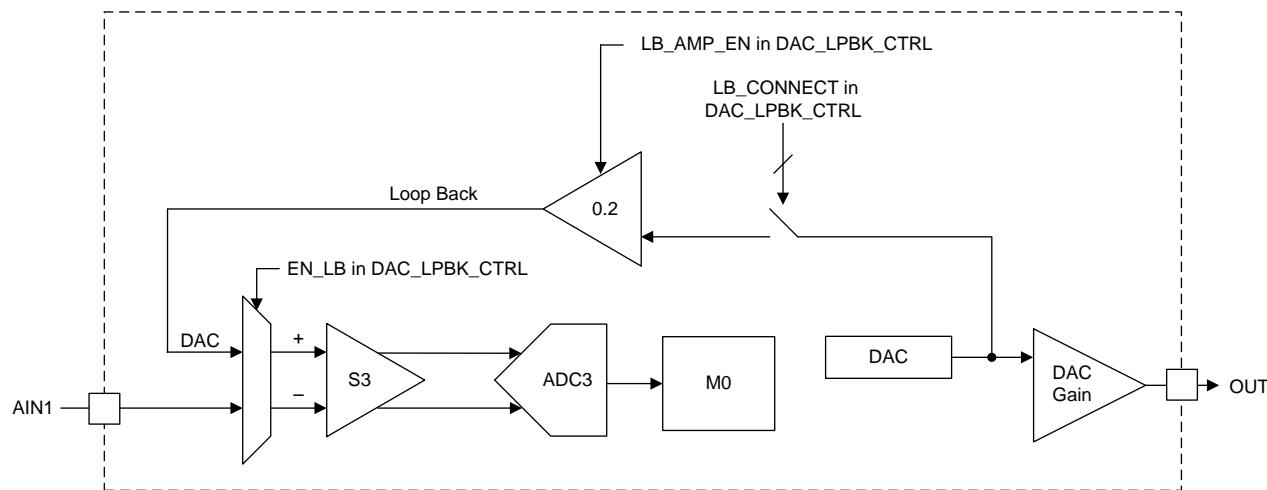

| AIN1            | 5                                                                  | I   | General-purpose ADC S3 Input. Multiplexed with the internal temperature sensor and output in an alternating format. |

| AVDD            | 12                                                                 | O   | Internal 3-V analog regulator output. Connect a 100-nF decoupling capacitor to ground.                              |

| AVSS            | 10                                                                 | —   | Analog ground. Tie to system ground.                                                                                |

| COMP            | 16                                                                 | I   | Output amplifier stability compensation                                                                             |

| CSN             | 28                                                                 | I   | SPI chip select                                                                                                     |

| DACCAP          | 14                                                                 | O   | DAC output filtering access. Connect a 100-nF capacitor to system ground for increased noise filtering.             |

| DVDD            | 23                                                                 | O   | Internal 1.8-V digital regulator output. Connect a 100-nF decoupling capacitor to ground                            |

| DVDD_MEM        | 22                                                                 | O   | FRAM power supply                                                                                                   |

| DVSS            | 37                                                                 | —   | Digital ground                                                                                                      |

| DVSS_MEM        | 24                                                                 | —   | FRAM power-supply ground                                                                                            |

| FBN             | 15                                                                 | I   | Output negative feedback                                                                                            |

| GATE            | 21                                                                 | O   | N-channel depletion MOSFET gate drive                                                                               |

| GPIO1           | 34                                                                 | I/O | General-purpose input or output. Function defined in user-generated firmware.                                       |

| GPIO2           | 33                                                                 | I/O | General-purpose input or output. Function defined in user-generated firmware.                                       |

| LVDT_GND        | 48                                                                 | —   | LVDT primary power ground. Tie to system ground.                                                                    |

| LVDT_PWR        | 43                                                                 | I   | LVDT primary power                                                                                                  |

| MISO            | 26                                                                 | O   | SPI slave data out                                                                                                  |

| MOSI            | 25                                                                 | I   | SPI slave data in                                                                                                   |

| NU              | 6, 7, 8, 9,<br>17, 18, 19,<br>29, 30, 31,<br>32, 39, 40,<br>41, 42 | —   | Not used                                                                                                            |

| OUT             | 13                                                                 | O   | 14-bit DAC amplifier output                                                                                         |

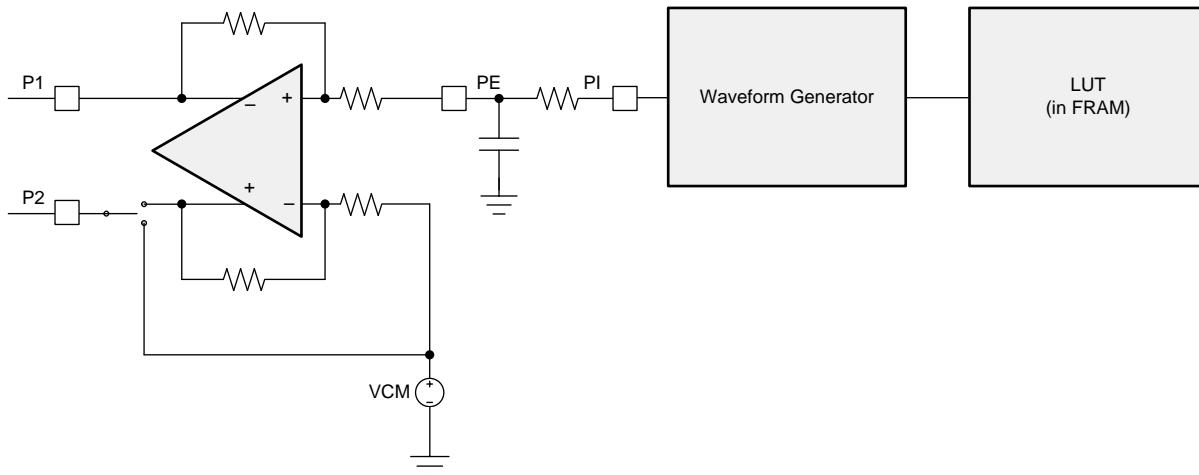

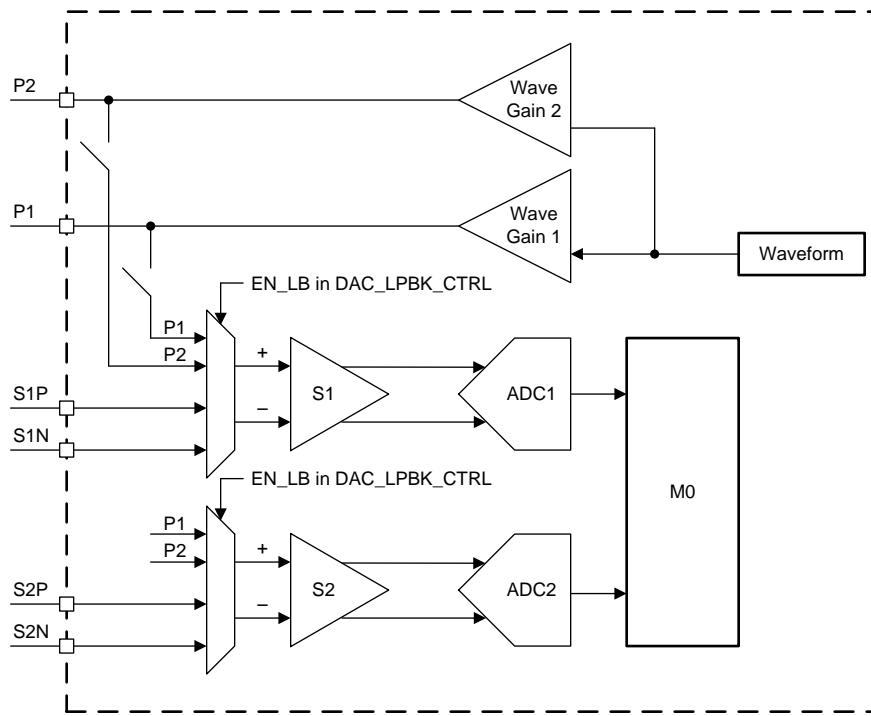

| P1              | 46                                                                 | O   | Primary-side LVDT excitation 1 for waveform amplifier single-ended or differential output                           |

| P2              | 47                                                                 | O   | Primary-side LVDT excitation 2 for waveform amplifier differential output                                           |

| PE              | 45                                                                 | I   | Waveform DAC output                                                                                                 |

| PI              | 44                                                                 | O   | Waveform GAIN input                                                                                                 |

| REFCAP          | 11                                                                 | O   | Reference capacitor                                                                                                 |

| S1N             | 2                                                                  | I   | Secondary 1 negative. Connected to S1 input stage and demodulator                                                   |

| S1P             | 1                                                                  | I   | Secondary 1 positive. Connected to S1 input stage and demodulator                                                   |

| S2N             | 4                                                                  | I   | Secondary 2 negative. Connected to S2 input stage and demodulator                                                   |

| S2P             | 3                                                                  | I   | Secondary 2 positive. Connected to S2 input stage and demodulator                                                   |

| SCK             | 27                                                                 | I   | SPI clock                                                                                                           |

| SWDCLK          | 36                                                                 | I   | Serial wire debug clock                                                                                             |

| SWDIO           | 35                                                                 | I/O | Serial wire debug input and output                                                                                  |

| TOP_TON         | 38                                                                 | O   | Test output positive or negative                                                                                    |

| V <sub>DD</sub> | 20                                                                 | I   | Supply voltage. 3.3-V to 30-V operating range                                                                       |

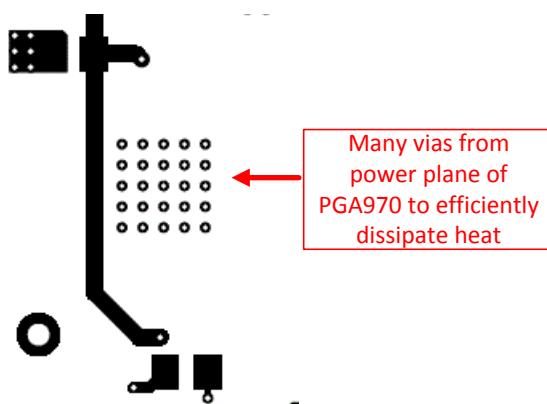

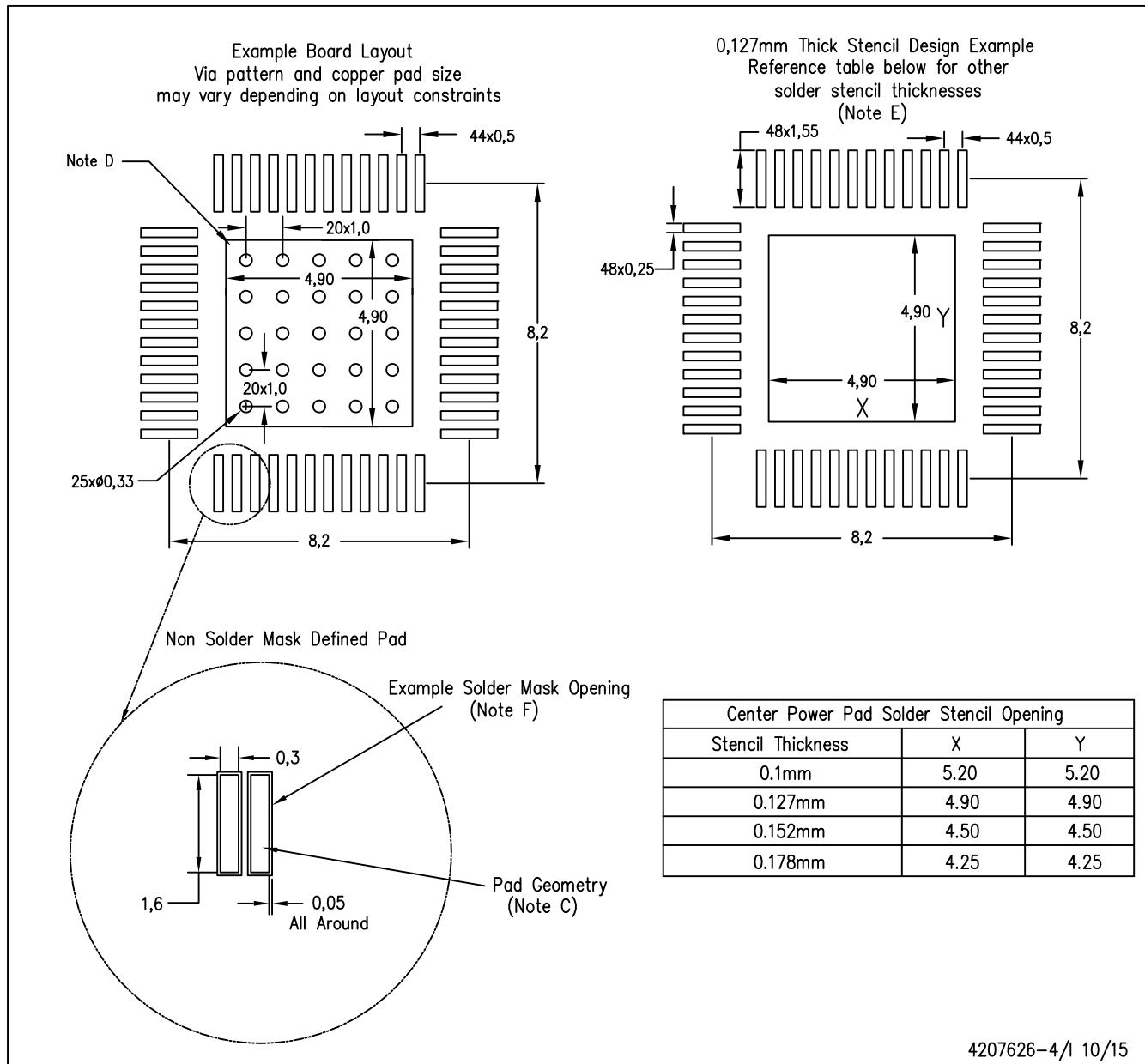

| Thermal pad     | —                                                                  | —   | Connect to ground and solder to ground plane. Thermal vias allow for additional heat dispersion.                    |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

See <sup>(1)</sup>.

|           |                                                                       | MIN           | MAX            | UNIT |

|-----------|-----------------------------------------------------------------------|---------------|----------------|------|

| $V_{DD}$  | $V_{DD}$ voltage                                                      | -0.3          | 33             | V    |

|           | GATE voltage                                                          | -0.3          | 33             | V    |

|           | Voltage at sensor input and drive pins P1, P2, S1P, S1N, S2P, and S2N | -0.3          | 3.45           | V    |

|           | Voltage at any I/O pin                                                | -0.3          | 3.45           | V    |

|           | Voltage at FBN pin                                                    | -0.3          | $V_{DD} + 0.3$ | V    |

| $I_{DD}$  | Supply current                                                        | Short on OUT  | 40             | mA   |

|           |                                                                       | Short on LVDT | 40             | mA   |

| $T_J$     | Maximum junction temperature                                          |               | 155            | °C   |

| $T_{stg}$ | Storage temperature                                                   | -65           | 150            | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* are not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|             |                         | VALUE                                                                 | UNIT       |

|-------------|-------------------------|-----------------------------------------------------------------------|------------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM) – EIA/JESD22-A114 <sup>(1)</sup>               | $\pm 2000$ |

|             |                         | Field-induced charged-device model (CDM) – JESD22-C101 <sup>(2)</sup> |            |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as  $\pm 2000$  V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as  $\pm 500$  V may actually have higher performance.

### 6.3 Recommended Operating Conditions

over operating ambient temperature range at  $V_{DD} = 5$  V (unless otherwise noted)

|          |                                        | MIN                                                                                                                     | NOM | MAX  | UNIT |

|----------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| $V_{DD}$ | Power supply voltage                   | 3.5                                                                                                                     | 30  | 30   | V    |

|          | Slew rate                              | $V_{DD} = 0$ to 30 V                                                                                                    |     | 0.5  | V/μs |

| $I_{DD}$ | Power supply current, normal operation | $V_{DD} = 14$ V, waveform generator at 5 kHz, S1, S2 enabled, no LVDT primary load, no load on OUT, M0 running at 8 MHz |     | 12.5 | mA   |

| $T_J$    | Operating junction temperature         | -40                                                                                                                     | 125 | 125  | °C   |

|          | Programming temperature                | FRAM                                                                                                                    | -40 | 125  | °C   |

|          | Capacitor on $V_{DD}$ pin              | 470                                                                                                                     | 680 | 680  | nF   |

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> | PGA970      | UNIT |

|-------------------------------|-------------|------|

|                               | PHP (HTQFP) |      |

|                               | 48 PINS     |      |

| $R_{\theta JA}$               | 25.8        | °C/W |

| $R_{\theta JC(\text{top})}$   | 12          | °C/W |

| $R_{\theta JB}$               | 7.7         | °C/W |

| $\psi_{JT}$                   | 0.2         | °C/W |

| $\psi_{JB}$                   | 7.6         | °C/W |

| $R_{\theta JC(\text{bot})}$   | 0.6         | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report (SPRA953).

## 6.5 Electrical Characteristics – External N-Channel Depletion MOSFET Gate Drive

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                                | TEST CONDITIONS       | MIN | TYP  | MAX | UNIT |

|------------------------------------------|-----------------------|-----|------|-----|------|

| $V_{DD}$ voltage when using GATE control | Gate control bit is 0 |     | 3.75 |     | V    |

| PSRR while in regulation                 |                       |     | 110  |     | dB   |

| Capacitor on GATE pin                    |                       |     | 330  |     | pF   |

| N-channel depletion MOSFET $V_{GS(th)}$  |                       |     | -1.5 |     | V    |

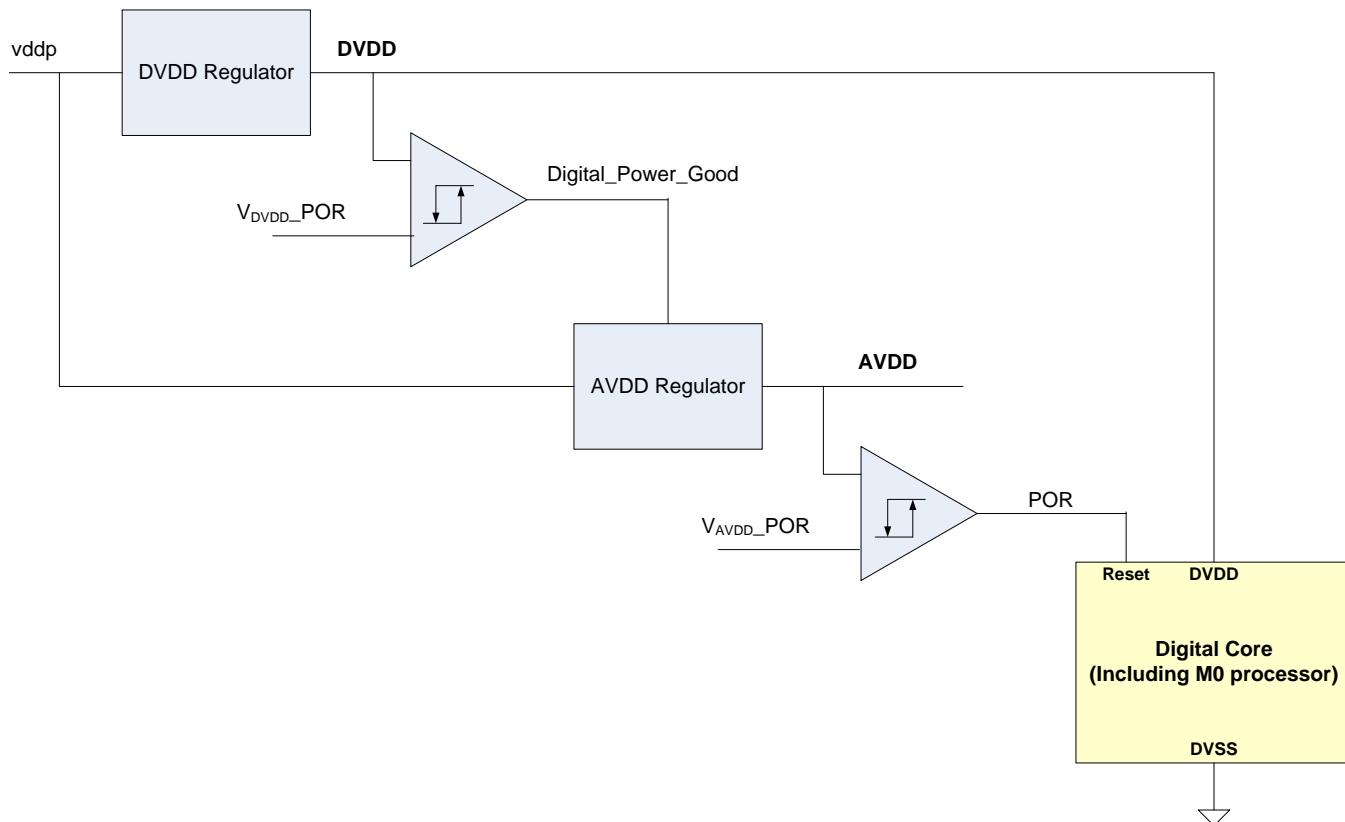

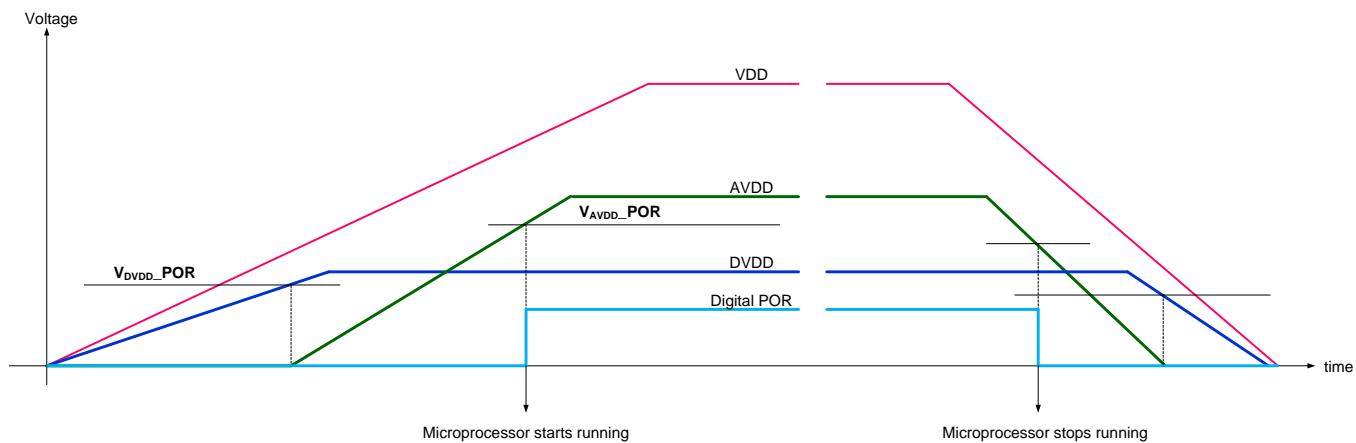

## 6.6 Electrical Characteristics - Regulators

| PARAMETER               | TEST CONDITIONS                   | MIN                                                                                                                                       | TYP  | MAX | UNIT |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

| $V_{AVDD}$              | $C_{AVDD} = 100 \text{ nF}$       |                                                                                                                                           | 3    |     | V    |

| $I_{AVDD}$              | External load on AVDD pin         |                                                                                                                                           | 5    |     | mA   |

| $V_{DVDD}$              | $DVDD$ voltage – operating        | $C_{DVDD} = 470 \text{ nF}$                                                                                                               | 1.85 |     | V    |

| $V_{DVDD(POR)}$         | $DVDD$ voltage – digital POR      |                                                                                                                                           | 1.65 |     | V    |

| $I_{(VDD + LVDT\_PWR)}$ | $V_{DD}$ constant current control | $EN\_CCS$ bit in CCS_CTRL = 1 (only CCS enabled, M0 not running, waveform generator not running, ADCs not enabled)<br>$ADJ\_CCS = 0b0000$ | 13.6 |     | mA   |

|                         |                                   | $ADJ\_CCS = 0b0001$                                                                                                                       | 14.6 |     |      |

|                         |                                   | $ADJ\_CCS = 0b0010$                                                                                                                       | 15.7 |     |      |

|                         |                                   | $ADJ\_CCS = 0b0011$                                                                                                                       | 16.7 |     |      |

|                         |                                   | $ADJ\_CCS = 0b0100$                                                                                                                       | 17.8 |     |      |

|                         |                                   | $ADJ\_CCS = 0b0101$                                                                                                                       | 18.8 |     |      |

|                         |                                   | $ADJ\_CCS = 0b0110$                                                                                                                       | 19.8 |     |      |

|                         |                                   | $ADJ\_CCS = 0b0111$                                                                                                                       | 20.8 |     |      |

|                         |                                   | $ADJ\_CCS = 0b1000$                                                                                                                       | 21.8 |     |      |

|                         |                                   | $ADJ\_CCS = 0b1001$                                                                                                                       | 22.9 |     |      |

|                         |                                   | $ADJ\_CCS = 0b1010$                                                                                                                       | 23.9 |     |      |

|                         |                                   | $ADJ\_CCS = 0b1011$                                                                                                                       | 24.9 |     |      |

|                         |                                   | $ADJ\_CCS = 0b1100$                                                                                                                       | 26   |     |      |

|                         |                                   | $ADJ\_CCS = 0b1101$                                                                                                                       | 27   |     |      |

|                         |                                   | $ADJ\_CCS = 0b1110$                                                                                                                       | 28   |     |      |

|                         |                                   | $ADJ\_CCS = 0b1111$                                                                                                                       | 29   |     |      |

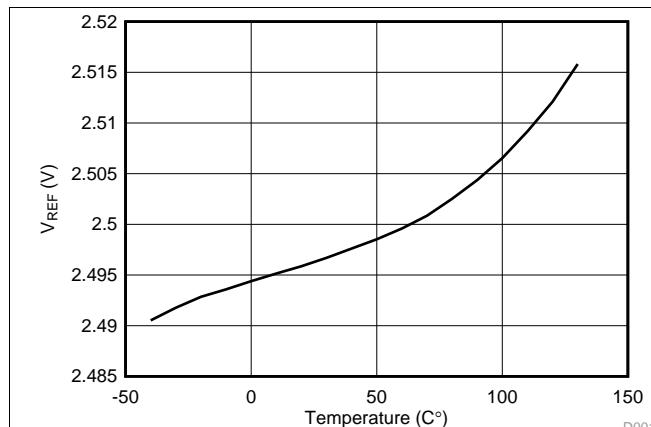

## 6.7 Electrical Characteristics – Internal Reference

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                        | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT   |

|----------------------------------|-----------------|------|-----|------|--------|

| High-voltage reference voltage   |                 |      | 1.2 |      | V      |

| Accurate reference voltage       |                 |      | 2.5 |      | V      |

| Accurate reference initial error |                 | -1%  |     | 1%   |        |

| Accurate reference voltage TC    |                 | -185 | 25  | 185  | ppm/°C |

| Capacitor value on REFCAP pin    |                 | 100  | 200 | 1000 | nF     |

## 6.8 Electrical Characteristics – Internal Oscillator

| PARAMETER                               | TEST CONDITIONS                | MIN | TYP | MAX | UNIT |

|-----------------------------------------|--------------------------------|-----|-----|-----|------|

| Internal oscillator frequency           | $T_A = 25^\circ\text{C}$       |     | 8   |     | MHz  |

| Internal oscillator frequency variation | Drift across temperature range | -3% |     | 7%  |      |

## 6.9 Electrical Characteristics – LVDT Primary Supply Waveform Generator

| PARAMETER                     | TEST CONDITIONS | MIN  | TYP | MAX | UNIT           |

|-------------------------------|-----------------|------|-----|-----|----------------|

| DAC resolution                |                 | 14   |     |     | Bits           |

| DAC range                     |                 | 1.25 |     |     | V              |

| DAC sample rate               |                 | 1    |     |     | MHz            |

| Waveform generator FIFO depth |                 |      | 256 |     | 14-bit samples |

## 6.10 Electrical Characteristics – LVDT Primary Supply Waveform Gain

| PARAMETER                                                                                                                              | TEST CONDITIONS                                                                                                                                                                                                             | MIN  | TYP  | MAX | UNIT   |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|--------|

| <b>POWER AMPLIFIER</b>                                                                                                                 |                                                                                                                                                                                                                             |      |      |     |        |

| Gain settling                                                                                                                          | DAC gain control bits = 0b00                                                                                                                                                                                                | 1    |      |     | V/V    |

|                                                                                                                                        | DAC gain control bits = 0b01                                                                                                                                                                                                | 1.18 |      |     |        |

|                                                                                                                                        | DAC gain control bits = 0b10                                                                                                                                                                                                | 1.4  |      |     |        |

|                                                                                                                                        | DAC gain control bits = 0b11                                                                                                                                                                                                | 1.67 |      |     |        |

| Gain error (end-point line)                                                                                                            | At 25°C, single-ended<br>Includes DAC gain error, waveform<br>gain = 1.67 V/V, 5-kHz<br>DAC waveform amplitude from<br>100 mV to 400 mV                                                                                     |      | 0.8% |     |        |

| Gain linearity (end-point line)                                                                                                        | At 25°C, single-ended<br>Includes DAC linearity, waveform gain<br>= 1.67V/V, 5 kHz<br>DAC waveform amplitude from 100<br>mV to 400 mV                                                                                       |      | 0.02 |     | %FSR   |

| Total temperature drift                                                                                                                | Pullup disabled<br>Differential sine voltage between P1<br>and P2 pins 100 mVrms to<br>390 mVrms<br>Drift formula: [(Amplitude (at T) –<br>Amplitude (at 25°C)) / [(T – 25°C)] ×<br>(Amplitude (at 25°C)] × 10 <sup>6</sup> |      | 200  |     | ppm/°C |

| LVDT supply voltage THD                                                                                                                | At 5 kHz, 25°C                                                                                                                                                                                                              | –60  |      |     | dB     |

| I <sub>LVDT_P</sub>                                                                                                                    | Current supply to LVDT primary                                                                                                                                                                                              |      | 20   |     | mA     |

| Short-circuit current                                                                                                                  |                                                                                                                                                                                                                             | 25   |      |     | mA     |

| Differential-mode output common<br>mode<br>(Common mode voltage at P1 or P2<br>when LVDT drive is configured for<br>differential mode) | DIFF_VOCM_CTRL = 0b00                                                                                                                                                                                                       | 0.75 |      |     | V      |

|                                                                                                                                        | DIFF_VOCM_CTRL = 0b01                                                                                                                                                                                                       | 1    |      |     |        |

|                                                                                                                                        | DIFF_VOCM_CTRL = 0b10                                                                                                                                                                                                       | 1.25 |      |     |        |

|                                                                                                                                        | DIFF_VOCM_CTRL = 0b11                                                                                                                                                                                                       | 1.5  |      |     |        |

| Differential offset adjustment <sup>(1)</sup>                                                                                          | DACVCM_CTRL = 0b00                                                                                                                                                                                                          | 0.82 |      |     | V      |

|                                                                                                                                        | DACVCM_CTRL = 0b01                                                                                                                                                                                                          | 0.84 |      |     |        |

|                                                                                                                                        | DACVCM_CTRL = 0b10                                                                                                                                                                                                          | 0.86 |      |     |        |

|                                                                                                                                        | DACVCM_CTRL = 0b11                                                                                                                                                                                                          | 0.88 |      |     |        |

| Unity-gain bandwidth <sup>(2)</sup>                                                                                                    |                                                                                                                                                                                                                             | 6    |      |     | MHz    |

(1) See [LVDT Primary Supply Waveform Gain](#) for a detailed description of the DACVCM\_CTRL code stored in FRAM.

(2) Specified by Design

## 6.11 Electrical Characteristics – Internal Temperature Sensor

| PARAMETER                            | TEST CONDITIONS            | MIN                                                            | TYP    | MAX | UNIT   |

|--------------------------------------|----------------------------|----------------------------------------------------------------|--------|-----|--------|

| Temperature range                    |                            | –40                                                            |        | 125 | °C     |

| Gain under 25°C                      | 24-bit ADC, –40°C to +25°C |                                                                | 6950.8 |     | LSB/°C |

| Gain above 25°C                      | 25°C to 125°C              | See the available 25°C and 125°C values in FRAM <sup>(1)</sup> |        |     | LSB/°C |

| Offset                               |                            | See the 25°C value in FRAM <sup>(1)</sup>                      |        |     | LSB    |

| Internal temperature sensor accuracy | –40°C to +25°C             |                                                                | ±2.8   |     | °C     |

(1) See [Internal Temperature Sensor](#) for a detailed description of the temperature code stored in FRAM.

## 6.12 Electrical Characteristics – S1 and S2 Gain

| PARAMETER                                                         | TEST CONDITIONS                      | MIN  | TYP  | MAX | UNIT |

|-------------------------------------------------------------------|--------------------------------------|------|------|-----|------|

| Gain steps (2 bits)                                               | Gain control bits = 00b at dc        |      | 1    |     | V/V  |

|                                                                   | Gain control bits = 01b              |      | 1.33 |     |      |

|                                                                   | Gain control bits = 10b              |      | 1.67 |     |      |

|                                                                   | Gain control bits = 11b              |      | 2.00 |     |      |

| Gain bandwidth product <sup>(1)</sup>                             |                                      |      | 350  |     | kHz  |

| Input bias current                                                |                                      |      | 5    |     | nA   |

| Input voltage at each pin                                         |                                      | 0.05 |      | 2   | V    |

| Common-mode voltage control (for ac-coupled secondary connection) | BIAS_VCM_CTRL = 00b, pullup disabled |      | 1.25 |     | V    |

|                                                                   | BIAS_VCM_CTRL = 01b; pullup disabled |      | 0.5  |     |      |

|                                                                   | BIAS_VCM_CTRL = 10b; pullup disabled |      | 0.75 |     |      |

|                                                                   | BIAS_VCM_CTRL = 11b; pullup disabled |      | 1    |     |      |

| Input impedance <sup>(1)</sup>                                    | Fault diagnostics resistors disabled | 500  |      |     | kΩ   |

(1) Defined in design, not tested by manufacturer

## 6.13 Electrical Characteristics – S3 Gain Stage

| PARAMETER                             | TEST CONDITIONS               | MIN  | TYP  | MAX | UNIT |

|---------------------------------------|-------------------------------|------|------|-----|------|

| Gain steps (2 bits)                   | Gain control bits = 00b at dc |      | 1    |     | V/V  |

|                                       | Gain control bits = 01b       |      | 1.33 |     |      |

|                                       | Gain control bits = 10b       |      | 2    |     |      |

|                                       | Gain control bits = 11b       |      | 5    |     |      |

| Gain bandwidth product <sup>(1)</sup> |                               |      | 350  |     | kHz  |

| Input bias current                    |                               |      | 5    |     | nA   |

| Input voltage at pin                  |                               | 0.01 |      | 2.1 | V    |

| Input impedance                       | Fault resistor disabled       | 50   |      |     | MΩ   |

## 6.14 Electrical Characteristics – Digital Demodulators 1 and 2

| PARAMETER                                                                                 | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MIN                    | TYP   | MAX | UNIT   |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|-----|--------|

| Sampling frequency                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        | 1     |     | MHz    |

| Demodulator voltage input range                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                      |       | 2.5 | V      |

| Number of bits                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        | 24    |     | bits   |

| Demodulator code for sinusoid input voltage of amplitude 0 V                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00 0000 <sub>hex</sub> |       |     | LSB    |

| Demodulator code for sinusoid input voltage of amplitude 2.4 V at output of S1 or S2 gain |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27 1D29 <sub>hex</sub> |       |     | LSB    |

| 24-bit peak-to-peak noise                                                                 | at <ul style="list-style-type: none"> <li>25°C</li> <li>5-kHz LVDT excitation</li> <li>Input signal amplitude = 0.8 V</li> <li>Common-mode voltage = 0.86 V</li> <li>S1 or S2 gain = 1 V/V</li> <li>Output rate = 256 µs</li> <li>Pullup disabled</li> <li>LPF cutoff frequency = 20 Hz</li> </ul> Includes gain noise, reference noise, and SDM thermal noise and quantization noise                                                                                                                                                                                                                             |                        | 50    |     | LSBs   |

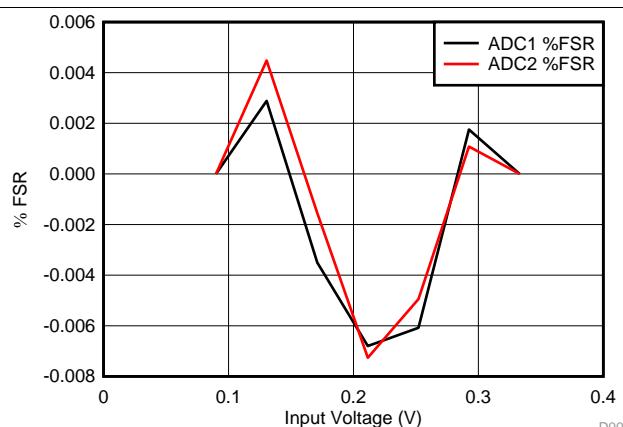

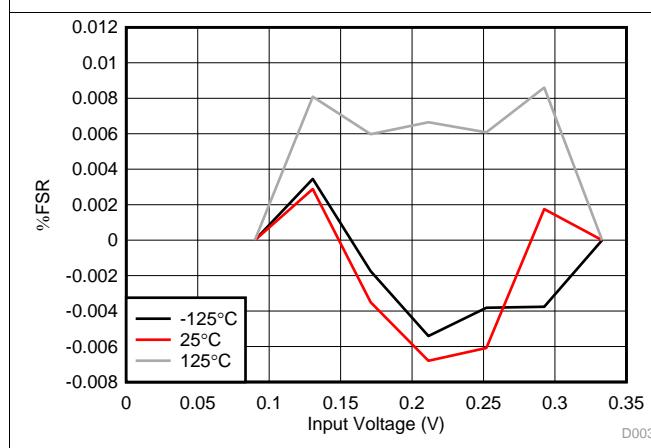

| Effective number of bits (ENOB) <sup>(1)</sup>                                            | at 25°C<br>at 5-kHz carrier frequency, LPF cutoff frequency = 250 Hz, gain = 1.33 V/V<br>Includes nonlinearity of gain, reference, and SDM<br>Method to calculate linearity: <ul style="list-style-type: none"> <li>Disable pullup</li> <li>Sweep input sine amplitude from 63 mVrms to 236 mVrms</li> <li>End-point fit a straight line between the demodulator output at these amplitudes</li> <li>Calculate linearity using the formula: [(max. deviation from straight line) / (max. demod – min. demod)] × 100</li> </ul> Includes gain noise, reference noise, and SDM thermal noise and quantization noise |                        | 15    |     | bits   |

| Demodulator-1, -2 nonlinearity                                                            | At 25°C<br>at 5-kHz carrier frequency, LPF cutoff frequency = 250 Hz, gain = 1.33 V/V<br>Includes nonlinearity of gain, reference, and SDM<br>Method to calculate linearity: <ul style="list-style-type: none"> <li>Disable pullup</li> <li>Sweep input sine amplitude from 63 mVrms to 236 mVrms</li> <li>End-point fit a straight line between the demodulator output at these amplitudes</li> <li>Calculate linearity using the formula: [(max. deviation from straight line) / (max. demod – min. demod)] × 100</li> </ul>                                                                                    |                        | ±0.01 |     | %FSO   |

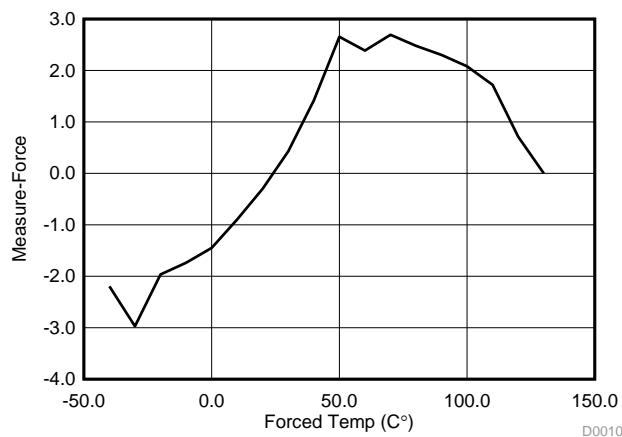

| Demodulator-1, -2 output total temperature drift                                          | 5-kHz carrier frequency, LPF cutoff frequency = 250 Hz, gain = 1.33 V/V<br>Includes drift of gain, reference, and SDM<br>Method to calculate drift: <ul style="list-style-type: none"> <li>Disable pullup</li> <li>Sweep input sine amplitude from 63 mVrms to 236 mVrms at temperature</li> <li>At each amplitude and temperature setting, record demodulator output</li> <li>Calculate drift using the formula:<br/>Drift formula: [demod (at T) – demod (at 25°C)] / [(T – 25°C) × demod (at 25)] × 10<sup>6</sup></li> </ul>                                                                                  |                        | ±9    | 50  | ppm/°C |

| Ratiometric (DEMOD1 – DEMOD2) / (DEMOD1 + DEMOD2) total temperature drift                 | At <ul style="list-style-type: none"> <li>Pullup disabled</li> <li>5-kHz carrier frequency</li> <li>DEMOD1 input signal amplitude = 157 mVrms</li> <li>DEMOD2 input signal amplitude = 116 mVrms</li> <li>Common-mode voltage = 0.86 V</li> <li>S1 or S2 gain = 1.33 V/V</li> <li>Output rate = 256 µs</li> <li>LPF cutoff frequency = 20 Hz</li> </ul> Drift formula: {[ratio (at T) – ratio (at 30°C)] / 1.4792} × 100                                                                                                                                                                                          |                        | 0.05  |     | %FS    |

| PSRR                                                                                      | $V_{DD} = 14 \text{ V}$ , ripple = 5%, frequency = 10 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        | 115   |     | dB     |

(1) ENOB =  $\ln[(\text{Full-Scale Range}) / (\text{Peak-to-Peak Noise})] / \ln(2)$

## 6.15 Electrical Characteristics – Analog-to-Digital Converter 3

| PARAMETER                                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MIN | TYP                    | MAX | UNIT   |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|-----|--------|

| Sampling frequency                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 4                      |     | MHz    |

| ADC voltage input range                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0   |                        | 2.5 | V      |

| Number of bits                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 24                     |     | bits   |

| ADC code for 0 V                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 00 0000 <sub>hex</sub> |     |        |

| ADC code for 2.5 V                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 7F FFFF <sub>hex</sub> |     |        |

| 16-bit peak-to-peak noise for the AIN1 input                    | At <ul style="list-style-type: none"> <li>• 25°C</li> <li>• DC</li> <li>• S3 gain = 1 V/V</li> <li>• Output period = 192 µs</li> <li>• LPF cutoff frequency = 20 Hz</li> </ul> Includes gain noise, ADC reference noise, ADC thermal noise, and ADC quantization noise                                                                                                                                                                                                                                                                                                                                    |     | 7                      |     | LSBs   |

| Effective number of bits (ENOB) for the AIN1 input              | At <ul style="list-style-type: none"> <li>• 25°C</li> <li>• DC</li> <li>• S3 gain = 1 V/V</li> <li>• Output period = 192 µs</li> <li>• LPF cutoff frequency = 20 Hz</li> </ul> Includes gain noise, ADC reference noise, ADC thermal noise, and ADC quantization noise                                                                                                                                                                                                                                                                                                                                    |     | 12.2                   |     | bits   |

| Minimum Input voltage for linearity (input-referred at S3 gain) | At <ul style="list-style-type: none"> <li>• 25°C</li> <li>• DC</li> <li>• S3 gain = 1 V/V</li> <li>• Output period = 192 µs</li> <li>• LPF cutoff frequency = 20 Hz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                            | 10  |                        |     | mV     |

| GAIN + ADC offset                                               | At <ul style="list-style-type: none"> <li>• 25°C</li> <li>• DC</li> <li>• Output period = 192 µs</li> <li>• LPF cutoff frequency = 20 Hz</li> </ul> Method to calculate linearity for each S3 gain setting: <ul style="list-style-type: none"> <li>• Sweep input from 200 mV to 2 V (divided by S3 gain)</li> <li>• End-point fit a straight line between the demodulator output at these amplitudes</li> <li>• Calculate linearity using the formula: [(max. deviation from straight line) / (max. ADC3 – min. ADC3)] × 100</li> <li>• Offset determined by Y-intercept of linearity equation</li> </ul> |     | 5                      |     | mV     |

| GAIN + ADC nonlinearity                                         | At <ul style="list-style-type: none"> <li>• 25°C</li> <li>• DC</li> <li>• Output period = 192 µs</li> <li>• LPF cutoff frequency = 20 Hz</li> </ul> Method to calculate linearity for each S3 gain setting: <ul style="list-style-type: none"> <li>• Sweep input from 200 mV to 2 V (divided by S3 gain)</li> <li>• End-point fit a straight line between the demodulator output at these amplitudes</li> <li>• Calculate linearity using the formula: [(max. deviation from straight line) / (max. ADC3 – min. ADC3)] × 100</li> </ul>                                                                   |     | 0.15                   |     | %FSO   |

| GAIN + ADC total temperature drift                              | At <ul style="list-style-type: none"> <li>• DC</li> <li>• Output period = 192 µs</li> <li>• LPF cutoff frequency = 20 Hz</li> </ul> Method to calculate temperature drift: <ul style="list-style-type: none"> <li>• Sweep input voltage from 200 mV to 2 V (divided by S3 gain) at 25°C and at temperature</li> <li>• Drift formula: {[ADC3 (at T) – ADC3 (at 25°C)] / [(T – 25°C) × ADC3 (at 25°C)]} × 10<sup>6</sup></li> </ul>                                                                                                                                                                         |     | 125                    |     | ppm/°C |

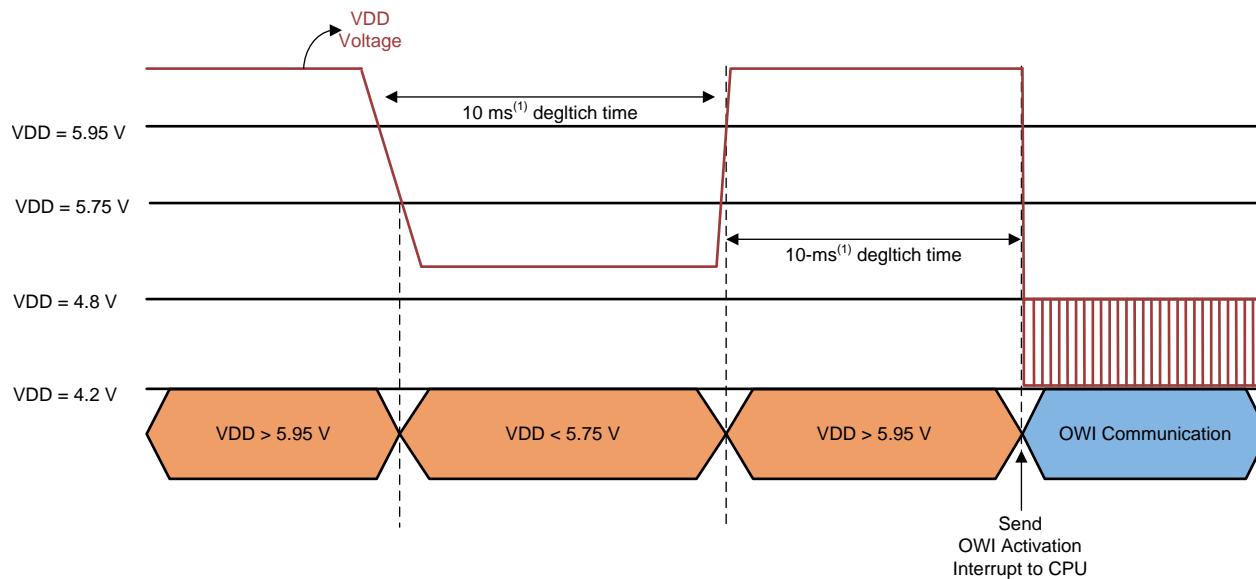

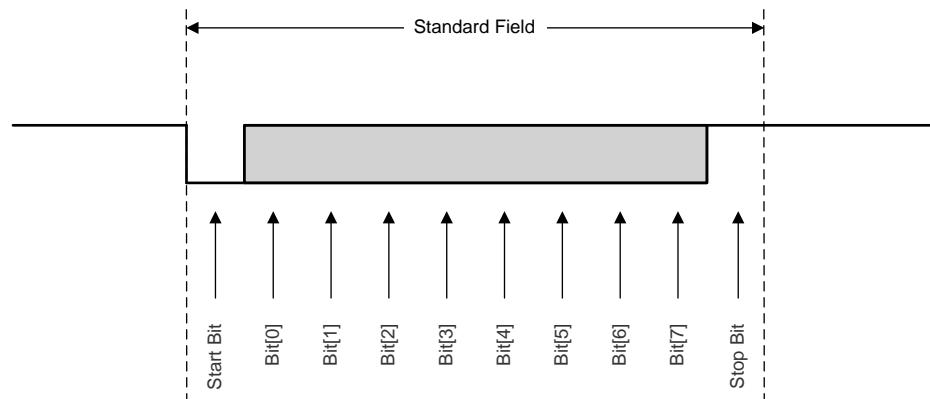

## 6.16 Electrical Characteristics – One-Wire Interface

| PARAMETER                              | TEST CONDITIONS                       | MIN     | TYP | MAX  | UNIT            |

|----------------------------------------|---------------------------------------|---------|-----|------|-----------------|

| Communication baud rate <sup>(1)</sup> |                                       | 320     |     | 9600 | Bits per second |

| $V_{(OWI\_ENH)}$                       | OWI activation high                   | 5.95    |     |      | V               |

| $V_{(OWI\_ENL)}$                       | OWI activation low                    |         |     | 5.75 | V               |

|                                        | Low time of activation-signal pulse   | 1<br>10 |     |      | ms              |

|                                        | High time of activation-signal pulse  | 1<br>10 |     |      | ms              |

| $V_{IH(OWI)}$                          | OWI transceiver Rx threshold for high | 4.8     |     | 5.1  | V               |

| $V_{IL(OWI)}$                          | OWI transceiver Rx threshold for low  | 3.9     |     | 4.2  | V               |

| $I_{OH(OWI)}$                          | OWI transceiver Tx threshold for high | 500     |     | 1379 | $\mu$ A         |

| $I_{OL(OWI)}$                          | OWI transceiver Tx threshold for low  | 2       |     | 5    | $\mu$ A         |

(1) OWI over power line does not work if there is an LDO between the supply to the sensor and the  $V_{DD}$  pin, and if the OWI high and low voltages are greater than the regulated voltage.

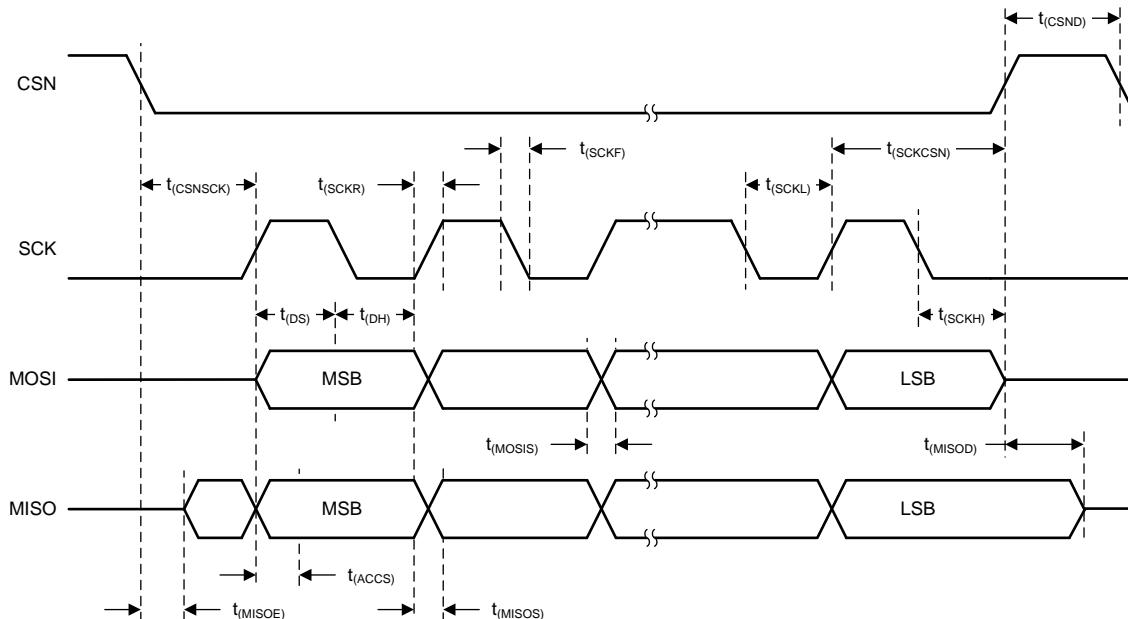

## 6.17 Electrical Characteristics – SPI

Over operating ambient temperature range (unless otherwise noted)

| PARAMETER     | TEST CONDITIONS                                                     | MIN  | TYP | MAX          | UNIT |

|---------------|---------------------------------------------------------------------|------|-----|--------------|------|

| $V_{IH}$      | High-level voltage (CSN, SCK, M <sub>OSI</sub> , M <sub>ISO</sub> ) | 2    |     | $AVDD + 0.3$ | V    |

| $V_{IL}$      | Low-level voltage (CSN, SCK, M <sub>OSI</sub> , M <sub>ISO</sub> )  | -0.3 |     | 0.8          | V    |

| $V_{OH}$      | High-level output voltage                                           | 2.4  |     |              | V    |

| $V_{OL}$      | Low-level output voltage                                            |      |     | 0.4          | V    |

| $f_{SCK}$     | SPI frequency                                                       |      |     | 1            | MHz  |

| $C_{L(MISO)}$ | Capacitive load for data output (M <sub>ISO</sub> )                 |      | 10  |              | pF   |

## 6.18 DAC Output

over operating ambient temperature range at  $V_{DD} = 5$  V (unless otherwise noted)

| PARAMETER             | TEST CONDITIONS                 | MIN | TYP                     | MAX | UNIT |

|-----------------------|---------------------------------|-----|-------------------------|-----|------|

| DAC reference voltage | Reference bit = 1               |     | 1.25                    |     | V    |

|                       | Reference bit = 0 (ratiometric) |     | $0.25 \times V_{(ddp)}$ |     |      |

| DAC resolution        |                                 |     | 14                      |     | bits |

## 6.19 DAC Gain

over operating ambient temperature range at  $V_{DD} = 5$  V (unless otherwise noted)

| PARAMETER                                                                                 | TEST CONDITIONS                                                                                                        | MIN                           | TYP   | MAX  | UNIT   |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------|------|--------|

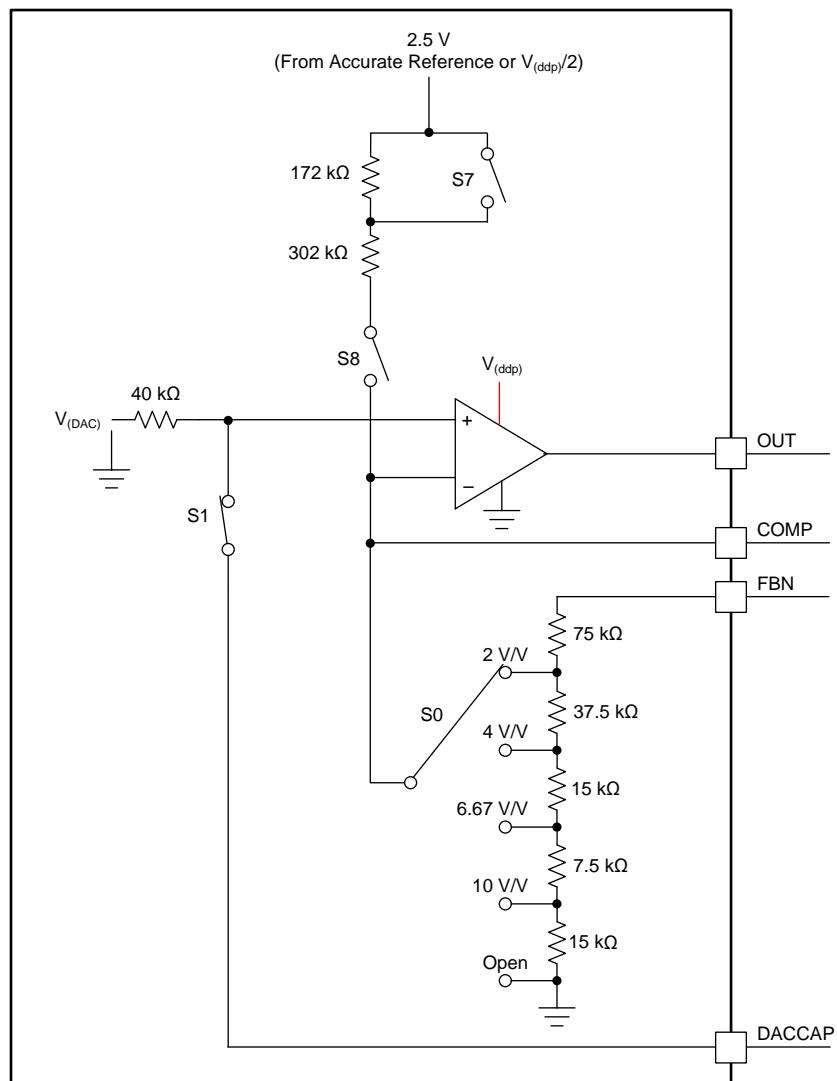

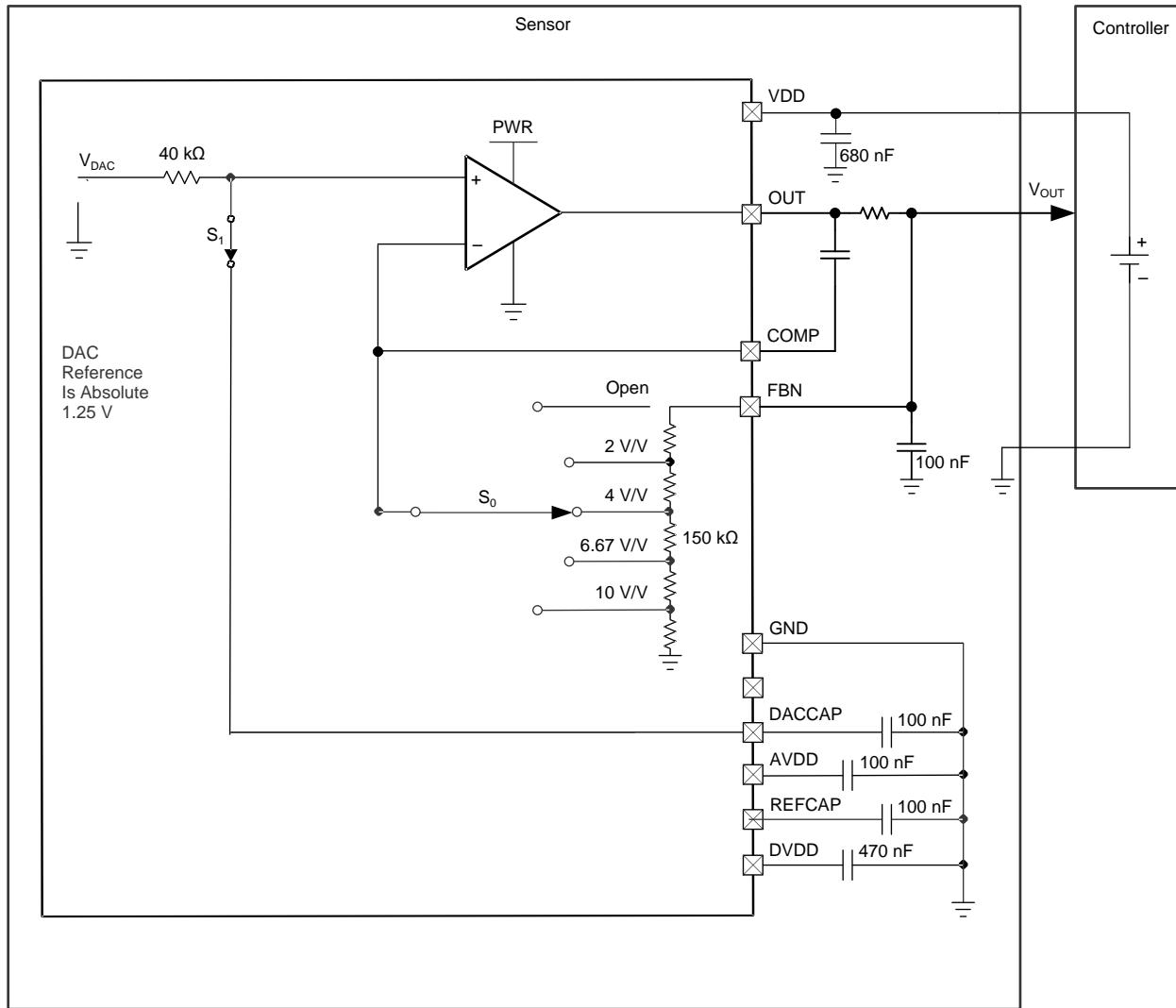

| Buffer gain (see Figure 3)                                                                | DAC_GAIN = 0b100, absolute                                                                                             | 2                             |       |      | V/V    |

|                                                                                           | DAC_GAIN = 0b010, absolute                                                                                             | 4                             |       |      |        |

|                                                                                           | DAC_GAIN = 0b110, absolute                                                                                             | 6.67                          |       |      |        |

|                                                                                           | DAC_GAIN = 0b001, absolute                                                                                             | 10                            |       |      |        |

|                                                                                           | DAC_GAIN = 0b010, ratiometric                                                                                          | 4                             |       |      |        |

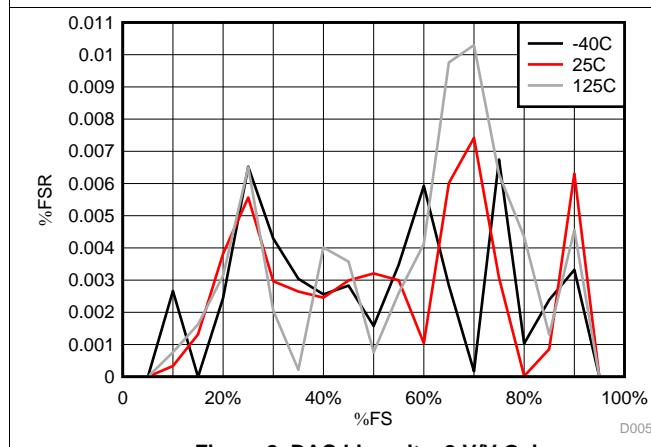

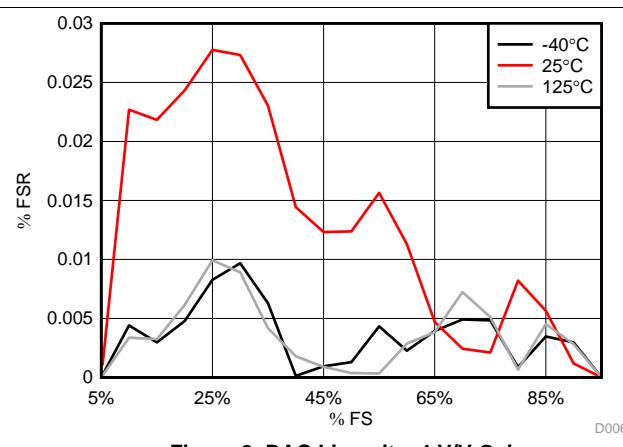

| Linearity                                                                                 | Calculation of linearity at each gain:<br>At 25 °C                                                                     | DAC_GAIN = 0b100, absolute    | 0.02  |      | %FSR   |

|                                                                                           | 1. Set OUT to drive a 100-nF capacitive load with appropriate compensation circuit. No DACCAP                          | DAC_GAIN = 0b010, absolute    | 0.025 |      |        |

|                                                                                           | 2. Sweep DAC code from 819d to 15 565d and measure OUT voltage.                                                        | DAC_GAIN = 0b110, absolute    | 0.04  |      |        |

|                                                                                           | 3. Fit a straight line using the end-point method.                                                                     | DAC_GAIN = 0b001, absolute    | 0.05  |      |        |

|                                                                                           | 4. Calculate linearity using the formula:<br>[(max. deviation from straight line) / (max. OUT – min. OUT)] × 100       | DAC_GAIN = 0b010, ratiometric | 0.025 |      |        |

|                                                                                           |                                                                                                                        |                               |       |      |        |

| Total temperature drift                                                                   | Calculation of temperature drift:                                                                                      | DAC_GAIN = 0b100, absolute    | 235   |      | ppm/°C |

|                                                                                           | 1. Set OUT to drive a 100-nF capacitive load with appropriate compensation circuit. No DACCAP                          | DAC_GAIN = 0b010, absolute    | 235   |      |        |

|                                                                                           | 2. Set DAC mid-code (8192d) and measure OUT voltage.                                                                   | DAC_GAIN = 0b110, absolute    | 235   |      |        |

|                                                                                           | 3. Measure OUT at 25°C and at temperature.                                                                             | DAC_GAIN = 0b001, absolute    | 235   |      |        |

|                                                                                           | 4. Calculate drift using the formula:<br>{[OUT (at T) – OUT (at 25°C)] / [OUT (at 25°C) × (T – 25)]} × 10 <sup>6</sup> |                               |       |      |        |

| Ratiometric error due to change in temperature and load current for DAC mid-code (8192d). | Calculate ratiometric error at $V_{DD} = 5$ V and at DAC codes as follows:                                             |                               |       |      | mV     |

|                                                                                           | 1. Apply DAC Code at 25°C and 0-mA load, and measure voltage at OUT.                                                   |                               |       |      |        |

|                                                                                           | 2. Change temperature between –40°C and 125°C, and measure voltage at OUT.                                             |                               | 19    |      |        |

|                                                                                           | 3. Change load current between 0 mA and 0.5 mA, and measure voltage at OUT.                                            |                               |       |      |        |

| Ratiometric error due to change in $V_{DD}$ for DAC mid-code (8192d).                     | 4. Ratiometric error = [(OUT at TEMPERATURE and LOAD) – (OUT at 25°C and 0 mA)]                                        |                               |       |      | mV     |

|                                                                                           | Calculate ratiometric error at DAC codes as follows:                                                                   |                               |       |      |        |

|                                                                                           | 1. Apply DAC code at 25°C and 0-mA load, and measure voltage at OUT.                                                   |                               |       |      |        |

|                                                                                           | 2. Change $V_{DD}$ between 4.5 V and 5.5 V, and measure voltage at OUT.                                                |                               | 25    | 50   |        |

| DAC gain noise                                                                            | 3. Change temperature between –40°C and 125°C, and measure voltage at OUT.                                             |                               |       |      | mV     |

|                                                                                           | 4. Ratiometric error = [(OUT at $V_{DD}$ and TEMPERATURE) – (OUT at 5 V and 25°C)] × $V_{DD}$ / 5 V                    |                               |       |      |        |

| DAC gain noise                                                                            | f = 10 Hz to 1 kHz, $V_{DD} = 4.5$ V, absolute mode, gain = 4 V/V, no capacitors for COMP or DACCAP pins, 25°C         | 95                            |       |      | µVpp   |

| Settling time (first-order response) <sup>(1)</sup>                                       | DAC code 819d to 15 564d step and $C_{LOAD} = 100$ nF. Output is 99% of final value.                                   |                               | 200   |      | µs     |

| Zero code voltage                                                                         | DAC code = 0000h, $I_{DAC\_GAIN} = -2.5$ mA, Gain = 4 V/V                                                              |                               | 20    |      | mV     |

| Full code voltage                                                                         | $V_{DD} = 14$ V, DAC code is 7FFFh, $I_{DAC\_GAIN} = 2.5$ mA, Gain = 4 V/V                                             | 4.8                           |       |      | V      |

| Output current                                                                            | DAC code = 7FFFh, DAC code = 0000h                                                                                     |                               |       | ±2.5 | mA     |

| Short-circuit source current                                                              | DAC code = 0000h                                                                                                       | 21                            |       |      | mA     |

| Short-circuit sink current                                                                | DAC code = 7FFFh                                                                                                       | 40                            |       |      | mA     |

| Gain bandwidth product <sup>(1)</sup>                                                     |                                                                                                                        | 1                             |       |      | MHz    |

| Maximum capacitance                                                                       | Without compensation                                                                                                   |                               | 100   |      | pF     |

| PSRR                                                                                      | $V_{DD} = 14$ V, ripple = 5%, frequency = 10 kHz                                                                       | –50                           |       |      | dB     |

(1) Specified by design

## 6.20 GPIO, Digital Test-In and Test-Out Buffers

| PARAMETER | TEST CONDITIONS           | MIN                                                        | TYP  | MAX          | UNIT |

|-----------|---------------------------|------------------------------------------------------------|------|--------------|------|

| $V_{IH}$  | High-level input voltage  | $R_{LOAD} \geq 10 \text{ k}\Omega$ to $V_{AVDD}$ or to 0 V | 2    | $AVDD + 0.3$ | V    |

| $V_{IL}$  | Low-level input voltage   |                                                            | -0.3 | 0.8          | V    |

| $V_{OH1}$ | High-level output voltage | $I_{OH} = -2 \text{ mA}$                                   | 2.4  |              | V    |

| $V_{OH2}$ | High-level output voltage | $I_{OH} = -0.2 \text{ mA}$                                 | 2.78 |              | V    |

| $V_{OL1}$ | Low-level output voltage  | $I_{OL} = 2 \text{ mA}$                                    |      | 0.4          | V    |

| $V_{OL2}$ | Low-level output voltage  | $I_{OL} = 0.2 \text{ mA}$                                  |      | 0.04         | V    |

| $I_{OH}$  | High-level output current | $V_{OH} = 2.4 \text{ V}$                                   | -2   |              | mA   |

| $I_{OL}$  | Low-level output current  | $V_{OL} = 0.8 \text{ V}$                                   |      | 2            | mA   |

## 6.21 Non-Volatile Memory

| PARAMETER              | TEST CONDITIONS | MIN | TYP | MAX       | UNIT   |

|------------------------|-----------------|-----|-----|-----------|--------|

| FRAM Size              |                 |     | 16  |           | KB     |

| Programming time       | Per word        |     | 250 |           | ns     |

| Data retention         |                 |     | 10  |           | years  |

| Erase and write cycles |                 |     |     | $10^{15}$ | cycles |

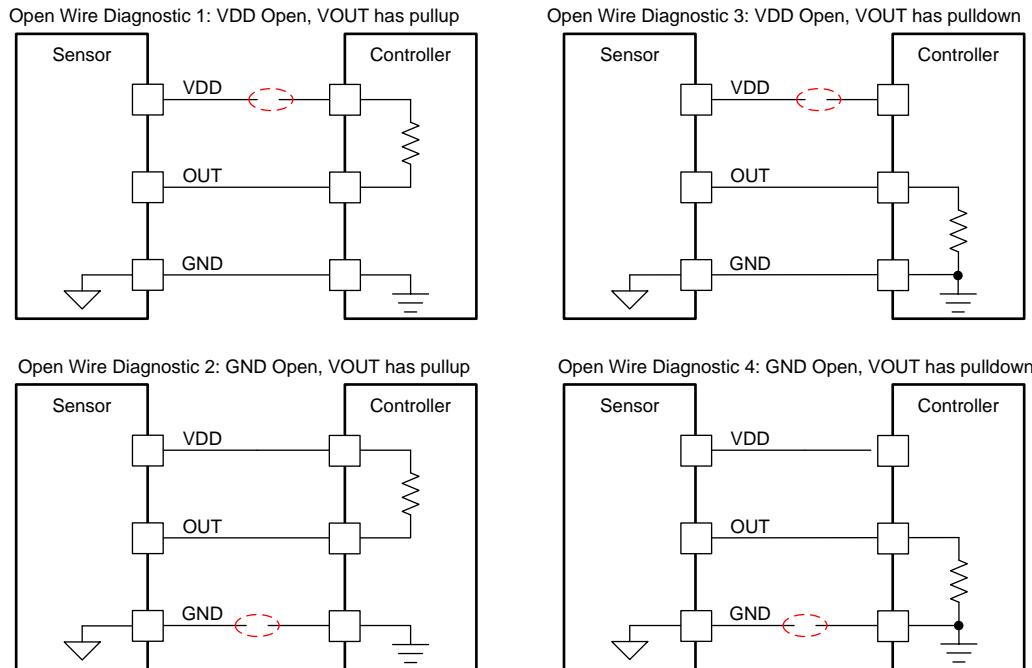

## 6.22 Diagnostics

| PARAMETER                          | TEST CONDITIONS                                         | MIN  | TYP        | MAX | UNIT |

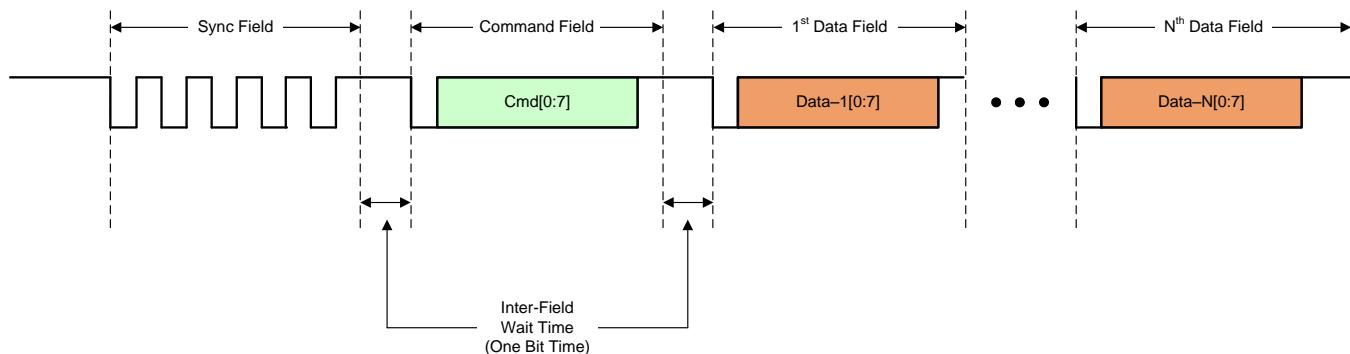

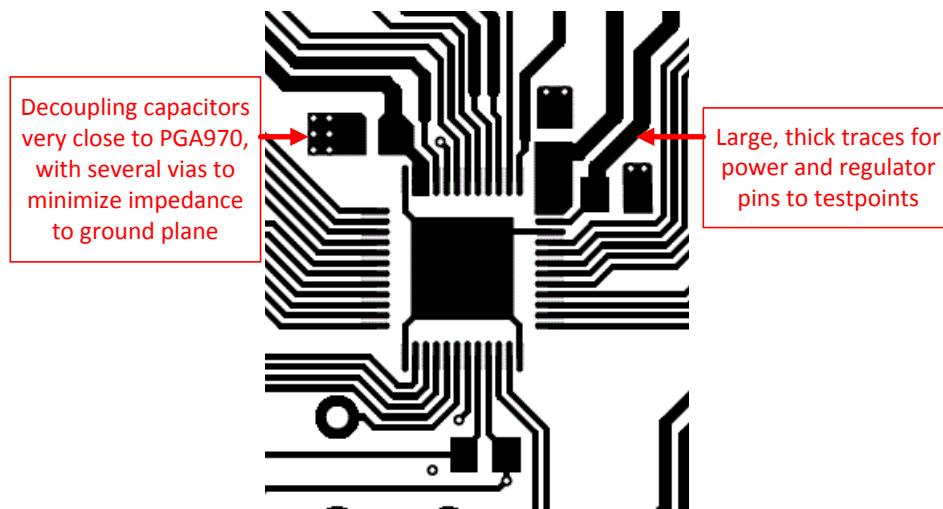

|------------------------------------|---------------------------------------------------------|------|------------|-----|------|