# XR82C684

CMOS Quad Channel UART (QUART)

September 1999-2

#### **FEATURES**

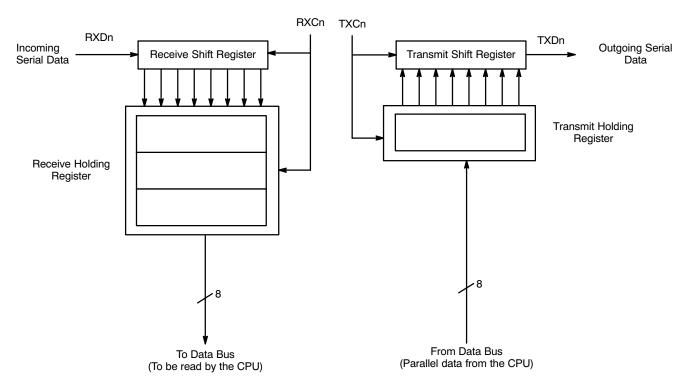

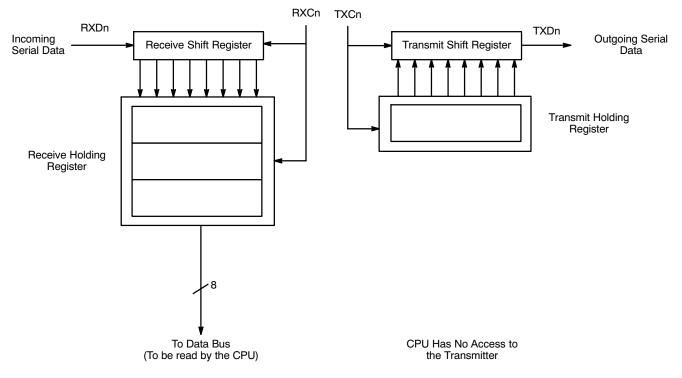

- Four Full-Duplex, Independent Channels

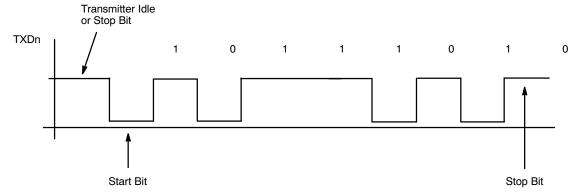

- Asynchronous Receiver and Transmitter

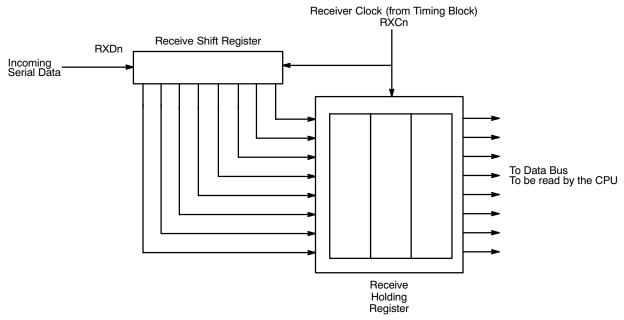

- Quadruple-Buffered Receivers and Transmitters

- Programmable Stop Bits in 1/16 bit increments

- Pin Selectable "88" and "68 Mode"

- Internal Bit Rate Generators with more than 33 Bit Bates

- Independent Bit Rate Selection for each Transmitter and Receiver

- External Clock Capability

- Maximum Bit Rate: 1X clock 1Mb/s, 16X clock -125 kb/s

- Normal, AUTOECHO, Local LOOPBACK and Remote LOOPBACK Modes

- Two Multi-function 16-bit Counter/Timers

- Interrupt Output with Sixteen Maskable Interrupt Conditions

- Interrupt Vector Output on Acknowledge

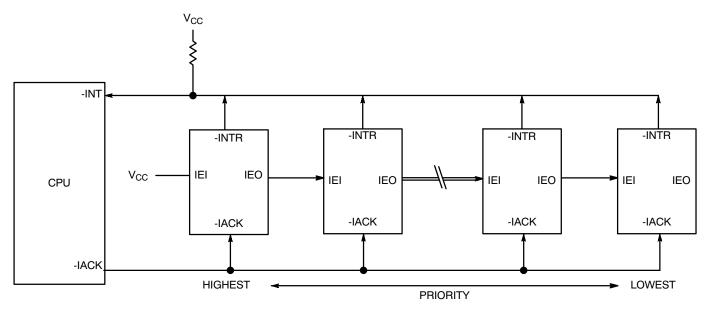

- Programmable Interrupt Daisy Chain (Z-Mode Operation only)

- 16 General Purpose Output pins

- 16 General Purpose Input pins with Change of States Detectors on 8 Inputs

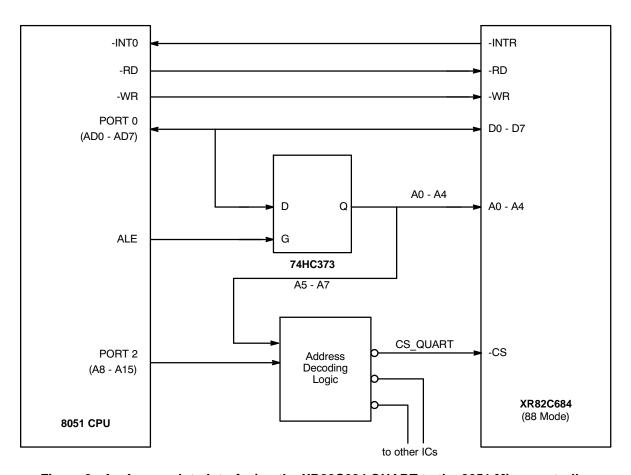

- Multi-drop Mode Compatible with 8051 Nine Bit Mode

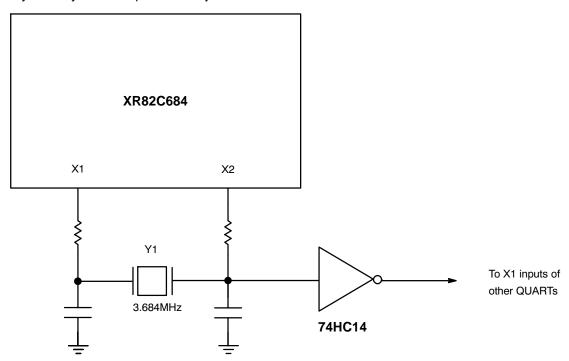

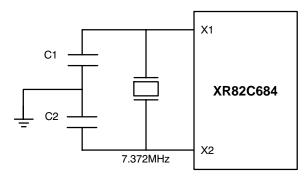

- On-chip Oscillator for Crystal

- Standby Mode to Reduce Operating Power

- Advanced CMOS Low Power Technology

#### **GENERAL DESCRIPTION**

The EXAR Quad Universal Asynchronous Receiver and Transmitter (QUART) is a data communications device that provides four fully independent full-duplex asynchronous communication channels in a single package. The QUART is designed for use in microprocessor based systems and may be used in a polled or interrupt-driven environment.

The XR82C684 device offers a single IC solution for various microprocessor families. The "88" and "68 modes" (for the 8800 and 68000 family of processors, respectively) can be selected by tying the SEL pin to  $V_{DD}$  or  $V_{SS}$ .

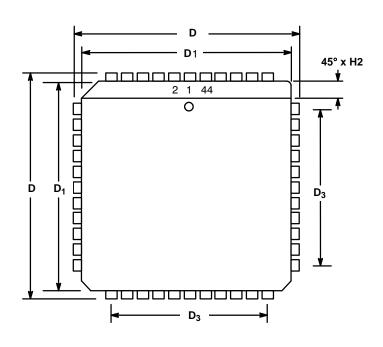

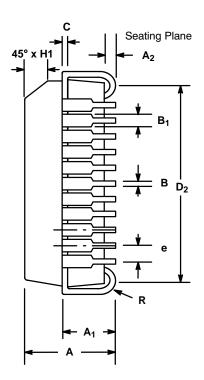

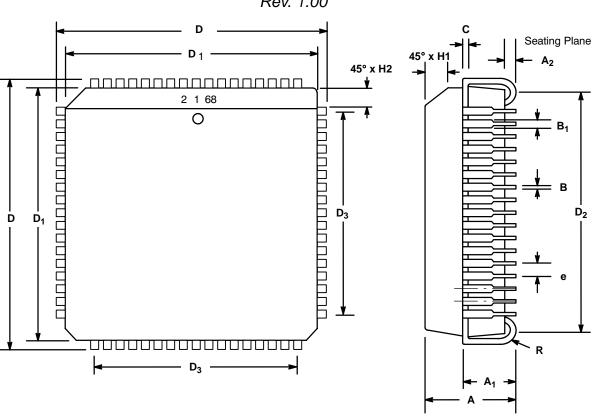

The QUART is fabricated using advanced two layer metal, with a high performance density EPI/CMOS 1.8• process to provide high performance and low power consumption, and is packaged in a 44 pin PLCC and a 68 pin PLCC.

### ORDERING INFORMATION

| Part No.      | Package     | Operating<br>Temperature Range |

|---------------|-------------|--------------------------------|

| XR82C684CJ/44 | 44 pin PLCC | 0°C to 70°C                    |

| XR82C684CJ    | 68 pin PLCC | 0°C to 70°C                    |

| XR82C684J/44  | 44 pin PLCC | -40°C to 85°C                  |

| XR82C684J     | 68 pin PLCC | -40°C to 85°C                  |

### PRINCIPLES OF OPERATION

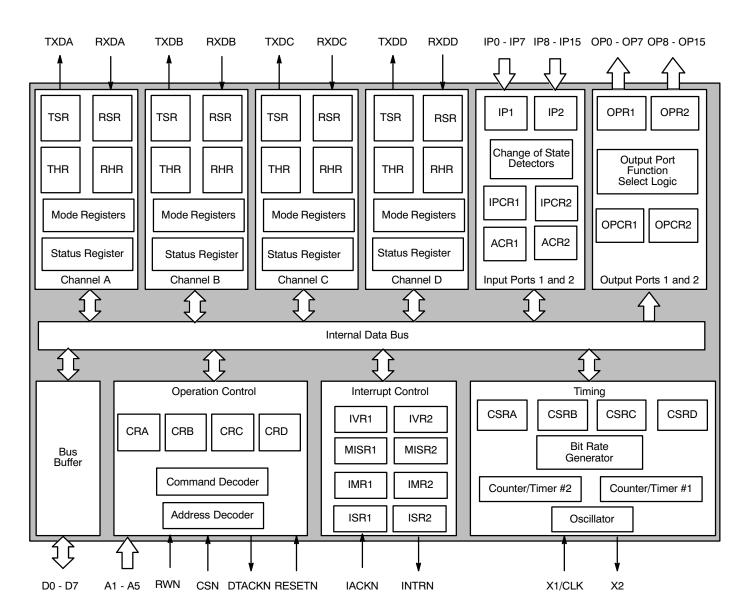

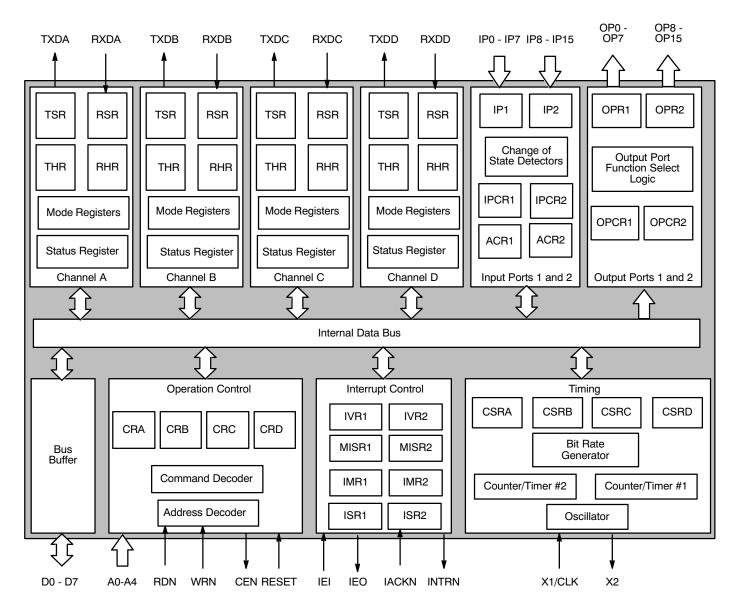

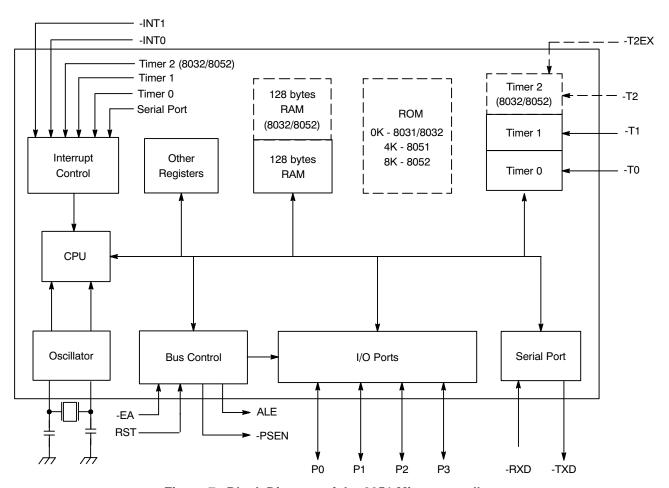

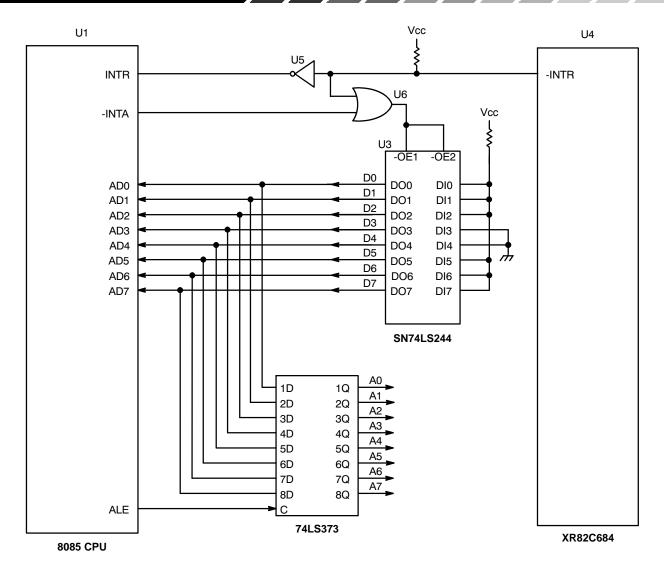

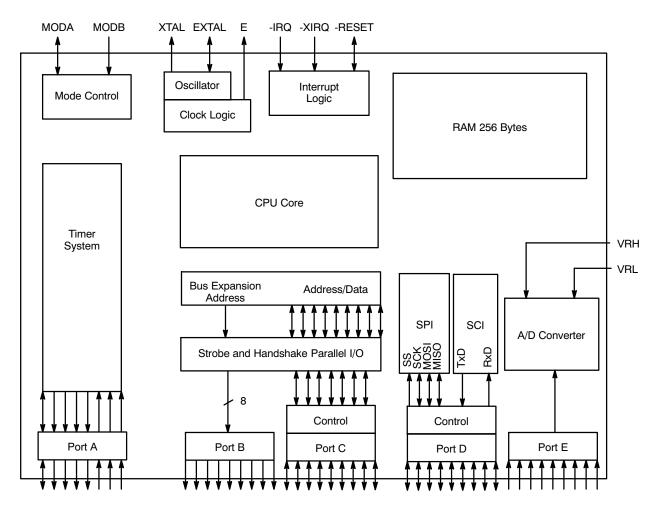

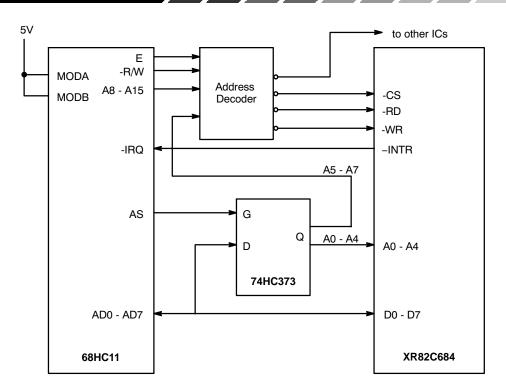

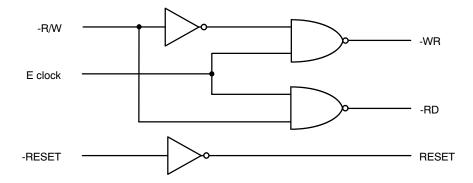

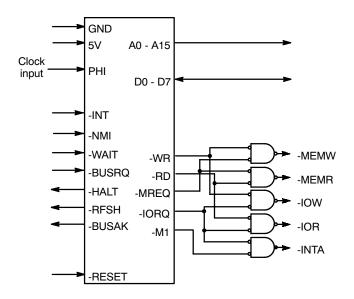

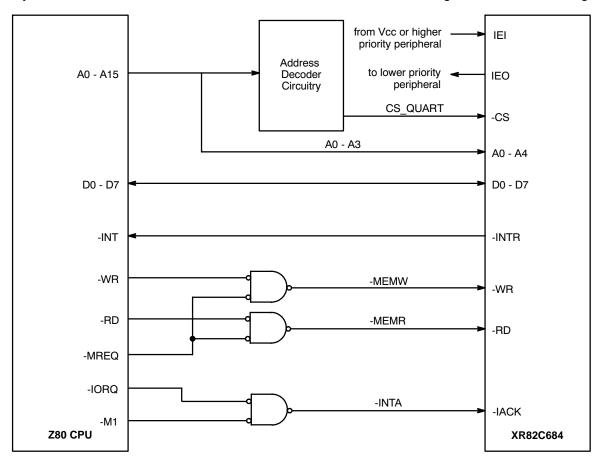

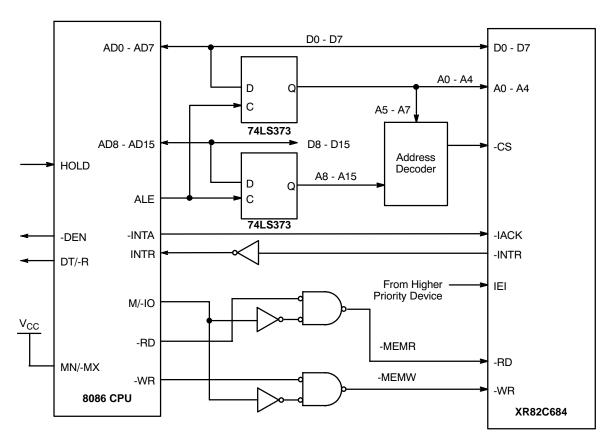

Figure 1 and Figure 2 present an overall block diagram of the QUART when operating in the 68 and 88 Modes, respectively. As illustrated in these block diagrams, the QUART consists of the following major functional blocks:

- Data Bus Buffer

- Interrupt Control

- Input Port

- Serial Communication Channels A, B, C, and D

- Operation Control

- Timing Control

- Output Port

Figure 1. Block Diagram of the XR82C684 in the 68 Mode

Figure 2. Block Diagram of the XR82C684 in the 88 Mode

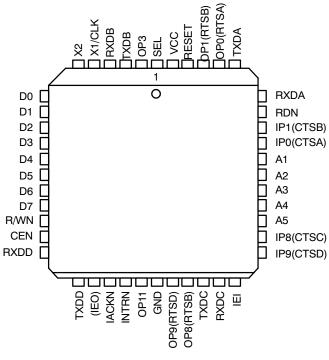

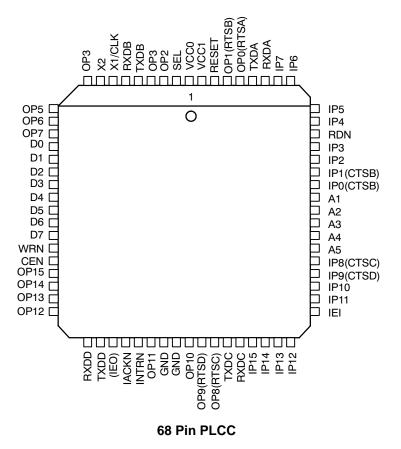

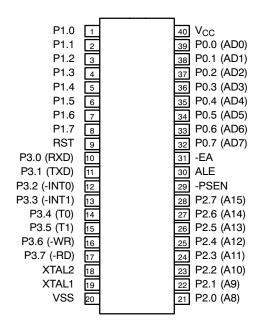

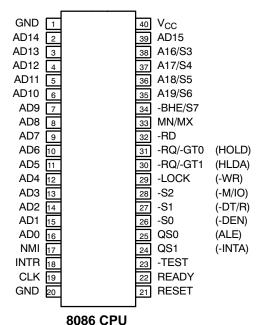

44 Pin PLCC

## **PIN DESCRIPTION**

| Pin #<br>68 Pin PLCC | Pin #<br>44 Pin PLCC | Symbol                                       | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|----------------------|----------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    |                      | V <sub>CC</sub> 0                            |        | Power Supply Pin.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2                    | 1                    | SEL                                          | I      | <b>Mode Select.</b> "88 mode" can be selected by tying this pin to GND; connecting this pin to V <sub>CC</sub> will select the "68 mode."                                                                                                                                                                                                                                                                                                   |

| 3                    |                      | OP2<br>(TXCA_16X)<br>(TXCA_1X)<br>(RXCA_1X)  | 0      | Output Port 2 (General Purpose Output). This pin can also be configured to function as the "Channel A Transmitter 16x or 1x clock" output, or the "Channel A Receiver 1X clock" output.                                                                                                                                                                                                                                                     |

| 4                    | 2                    | OP3<br>(TXCB_1X)<br>(RXCB_1X)<br>(C/T_1_RDY) | 0      | Output 3 (Active low). Can be programmed as a general purpose output, the "Channel B transmitter 1x clock" output, the "Channel B receiver 1x clock" output, or an open drain "Counter/Timer 1 ready" output.                                                                                                                                                                                                                               |

| 5                    | 3                    | TXDB                                         | O      | Transmitter Serial Data Output (Channel B). The least significant bit of the character is transmitted first. This output is held in the "high" (marking state) when the transmitter is idle, disabled, or when the channel is operating in the local LOOPBACK mode. If an external transmitter clock is specified, TXCB, the transmitted data is shifted out of the TSR (Transmitter Shift Register) on the falling the edge of this clock. |

| 6                    | 4                    | RXDB                                         | I      | Receiver Serial Data Input (Channel B). The least significant bit of the character is received first. If the external receiver clock, RXCB, is specified, then the serial input data is sampled on the rising edge of this clock.                                                                                                                                                                                                           |

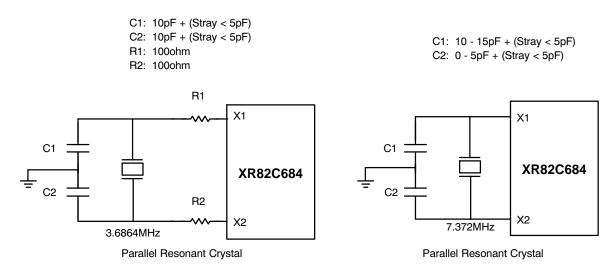

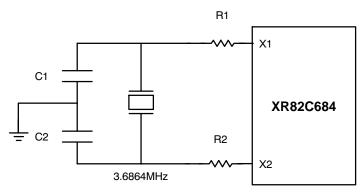

| 7                    | 5                    | X1/CLK                                       | I or O | Crystal Output or External Clock Input. This pin is the connection for one side of the crystal and a capacitor to ground when the internal oscillator is used. If the oscillator is not used, an external clock signal must be supplied at this input.                                                                                                                                                                                      |

|                      |                      |                                              |        | In order for the XR82C684 device to function properly, the user must supply a signal with frequencies between 2.0 MHz and 8.0 MHz. This requirement can be met by either a crystal oscillator or by the external TTL-compatible clock signal.                                                                                                                                                                                               |

| 8                    | 6                    | X2                                           | I      | Crystal Input. Connection for one side of the crystal (opposite of X1/CLK). If the oscillator is used, a capacitor must also be connected from this pin to ground. This pin must be left open if an external clock is supplied at the X1/CLK pin.                                                                                                                                                                                           |

| 9                    |                      | OP4<br>(RXRDY/<br>-FFULL_A)                  | 0      | Output 4 (General Purpose Output). This output pin can also be configured to function as the active-low "Receiver-Ready/FIFO Full" indicator for Channel A (RXRDY/-FFULL_A).                                                                                                                                                                                                                                                                |

| 10                   |                      | OP5<br>(RXRDY/<br>-FFULL_B)                  | 0      | Output 5 (General Purpose Output). This output pin can be configured to function as the active-low "Receiver-Ready/FIFO Full" indicator for Channel B (RXRDY/-FFULL_B).                                                                                                                                                                                                                                                                     |

| Pin #<br>68 Pin PLCC | Pin #<br>44 Pin PLCC | Symbol                       | Туре | Description                                                                                                                                                                                                                                       |

|----------------------|----------------------|------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                   |                      | OP6                          | 0    | Output 6 (General Purpose Output).                                                                                                                                                                                                                |

|                      |                      | (TXRDY_A)                    |      | This output pin can be configured to function as the active-low "Transmitter-Ready" indicator for Channel A (-TXRDY_A).                                                                                                                           |

| 12                   |                      | OP7<br>(TXRDY_B)             | 0    | Output 7 (General Purpose Output). This output pin can be configured to function as the active-low "Transmitter-Ready" indicator for Channel B (-TXRDY_B).                                                                                        |

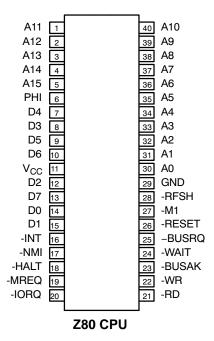

| 13                   | 7                    | D0                           | I/O  | LSB of the Eight Bit Bi-Directional Data Bus. All transfers between the CPU and the QUART take place over this bus (consisting of pins D0 - D7). The bus is tri-stated when the -CS input is "high", except during an IACK cycle (in the Z-Mode). |

| 14                   | 8                    | D1                           | I/O  | Bi-Directional Data Bus.                                                                                                                                                                                                                          |

| 15                   | 9                    | D2                           | I/O  | Bi-Directional Data Bus.                                                                                                                                                                                                                          |

| 16                   | 10                   | D3                           | I/O  | Bi-Directional Data Bus.                                                                                                                                                                                                                          |

| 17                   | 11                   | D4                           | I/O  | Bi-Directional Data Bus.                                                                                                                                                                                                                          |

| 18                   | 12                   | D5                           | I/O  | Bi-Directional Data Bus.                                                                                                                                                                                                                          |

| 19                   | 13                   | D6                           | I/O  | Bi-Directional Data Bus.                                                                                                                                                                                                                          |

| 20                   | 14                   | D7                           | I/O  | MSB of the Eight Bit Bi-Directional Data Bus. All transfers between the CPU and the QUART take place over this bus (consisting of pins D0 - D7). The bus is tri-stated when the -CS input is "high", except during an IACK cycle (in the Z-Mode). |

| 21                   | 15                   | R/-W<br>(68 Mode)            | I    | Read/-Write (Input). If this input is high while -CS is low, then the CPU is performing a READ cycle with the QUART. If this input is low, while -CS is low, then the CPU is performing a WRITE cycle with the QUART.                             |

| 21                   | 15                   | WRN<br>(88 Mode)             | ı    | Write Strobe (Active Low). A "low" on this input while -CS is also "low" writes the contents of the Data Bus into the addressed register, within the QUART. The transfer occurs on the rising edge of -WR.                                        |

| 22                   | 16                   | -CS                          | I    | Chip Select (Active Low). The data bus is tri-stated when -CS is high. Data transfers between the CPU and the QUART via D0 - D7 are enabled when -CS is low.                                                                                      |

| 23                   |                      | OP15<br>(-TXRDY_D)           | 0    | Output 15 (General Purpose Output). This output port pin can be configured to function as the open-drain, active-low "Transmitter Ready" indicator for Channel D (-TXRDY_D).                                                                      |

| 24                   |                      | OP14<br>(-TXRDY_C)           | 0    | Output 14 (General Purpose Output). This output port pin can be configured to function as the open-drain. active-low "Transmitter Ready" indicator for Channel C (-TXRDY_C).                                                                      |

| 25                   |                      | OP13<br>(RXRDY/<br>-FFULL_D) | I/O  | Output 13 (General Purpose Output). This output port pin can be configured to function as the open-drain, active low "Receiver Ready" or "FIFO Full" indicator for Channel D (RXRDY/-FFULL_D).                                                    |

| 26                   |                      | OP12<br>(RXRDY/<br>-FFULL_C) | 0    | Output 12 (General Purpose Output). This output port pin can be configured to function as the open-drain, active-low "Receiver Ready" or "FIFO Full" indicator for Channel C (RXRDY/-FFULL_C).                                                    |

| Pin #<br>68 Pin PLCC | Pin #<br>44 Pin PLCC | Symbol                  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|----------------------|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27                   | 17                   | RXDD                    | I    | Receiver Serial Data Input (Channel D). The least significant bit of the character is received first. If the external receiver clock, RXCD, is specified, then the serial input data is sampled on the rising edge of this clock.                                                                                                                                                                                                                                              |

| 28                   | 18                   | TXDD                    | 0    | Transmitter Serial Data Output (Channel D). The least significant bit of the character is transmitted first. This output is held in the high (marking state) when the transmitter is idle, disabled, or when the channel is operating in the local LOOPBACK mode. If an external transmitter clock is specified, TXCD, the transmitted data is shifted out of the TSR (Transmitter Shift Register) on the falling the edge of this clock.                                      |

| 29                   | 19                   | DTACKN<br>(68 mode)     | 0    | Data Transfer Acknowledge (Three-State, Active-Low). The QUART asserts -DTACK in order to inform the CPU that the present READ or WRITE operation is nearly complete. The 68000 Family of CPUs requires this signal from its peripheral devices in order to quickly and properly complete a READ or WRITE cycle.                                                                                                                                                               |

|                      |                      |                         |      | If the QUART asserts -DTACK during a READ operation, it indicates (to the CPU) that the requested data is on the databus. If -DTACK is asserted during an Interrupt Acknowledge cycle, the QUART is informing the CPU that the contents of the IVR (Interrupt Vector Register) are available on the data bus.                                                                                                                                                                  |

|                      |                      |                         |      | If the QUART asserts the -DTACK during a WRITE cycle, it is informing the CPU that the data, on the data bus, has been latched into the data bus buffer of the QUART device.                                                                                                                                                                                                                                                                                                   |

| 29                   | 19                   | IEO<br>(88 mode)        | 0    | Interrupt Enable Output (Z Mode; Active High). This output pin is normally "high". However, either one of the following two conditions can cause this output pin to be negated (toggle "low".)                                                                                                                                                                                                                                                                                 |

|                      |                      |                         |      | If the IEI (Interrupt Enable Input) pin is "low". If IEO is "low" because of the IEI pin, IEO will toggle "high" once the IEI pin has toggled "high".                                                                                                                                                                                                                                                                                                                          |

|                      |                      |                         |      | 2. The QUART has issued an Interrupt Request to the CPU (-INTR pin is toggled "low"). If IEO is "low" because the QUART has requested an Interrupt, then IEO will remain "low", throughout the Interrupt Service Routine, until the CPU has invoked the "RESET IUS" Command.                                                                                                                                                                                                   |

| 30                   | 20                   | IACKN<br>(68 or Z-Mode) | I    | Interrupt Acknowledge (Active Low). This input is the CPU's response to the interrupt request issued by the QUART device. When the CPU asserts this input, it indicates that the QUART's interrupt request is about to be serviced, and that the very next bus cycle will be an interrupt acknowledge (IACK) cycle. The QUART will respond to the CPU's interrupt acknowledge signal by placing the contents of the Interrupt Vector Register (IVR) on the data bus (D0 - D7). |

| Pin #<br>68 Pin PLCC | Pin #<br>44 Pin PLCC | Symbol                                         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|----------------------|------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31                   | 21                   | -INTRN                                         | O    | Interrupt Request Output (Active Low, Open-Drain)INTR is asserted upon the occurrence of one or more of the chip's maskable interrupting conditions. This signal will remain asserted throughout the Interrupt Service Routine and will be negated once the condition(s) causing the Interrupt Request has been eliminated.                                                                                                               |

| 32                   | 22                   | OP11<br>(TXCD_1X)<br>(RXCD_1X)<br>(-C/T_2_RDY) | 0    | Output 11 (General Purpose Output). This output port pin can also be configured to function as the "Channel D Transmitter 1X clock" output (TXCD_1X), the "Channel D Receiver 1X clock" output, or the active-low "Counter/Timer #2 Ready" Output (-C/T_2_RDY)                                                                                                                                                                            |

| 33                   | 23                   | GND                                            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 34                   |                      | GND                                            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 35                   |                      | OP10<br>(TXCC_1X)<br>(TXCC_16X)<br>(RXCC_1X)   | 0    | Output 10 (General Purpose Output). This output port pin can be configured to function as the "Channel C Transmitter 1X or 16X clock" output; or as the "Channel C Receiver clock" output.                                                                                                                                                                                                                                                |

| 36                   | 24                   | OP9 (-RTSD)                                    | 0    | Output 9 (General Purpose Output). This output port pin can be configured to function as the active-low, open-drain "Channel D, Request-to-Send" output (-RTSD).                                                                                                                                                                                                                                                                          |

| 37                   | 25                   | OP8 (-RTSC)                                    | 0    | Output 8 (General Purpose Output). This output port pin can be configured to function as the active-low, open-drain "Channel C Request-to-Send" output (-RTSC).                                                                                                                                                                                                                                                                           |

| 38                   | 26                   | TXDC                                           | O    | Transmitter Serial Data Output (Channel D). The least significant bit of the character is transmitted first. This output is held in the high (marking state) when the transmitter is idle, disabled, or when the channel is operating in the local LOOPBACK mode. If an external transmitter clock is specified, TXCD, the transmitted data is shifted out of the TSR (Transmitter Shift Register) on the falling the edge of this clock. |

| 39                   | 27                   | RXDC                                           | I    | Receive Serial Data Input (Channel D). The least significant bit is received first. If external receiver clock is specified, the data is sampled on the rising edge of the clock.                                                                                                                                                                                                                                                         |

| 40                   |                      | IP15                                           | I    | Input 15 (General Purpose Input).                                                                                                                                                                                                                                                                                                                                                                                                         |

| 41                   |                      | IP14<br>(RXCD_EX)                              | I    | Input 14 (General Purpose Input). This input pin can also be configured to function as the external clock input for the Receiver of Channel D (RXCD_EX).                                                                                                                                                                                                                                                                                  |

| 42                   |                      | IP13<br>(TXCD_EX)                              | I    | Input 13 (General Purpose Input). This input pin can also be configured to function as the external clock input for the Transmitter of Channel D (TXCD_EX).                                                                                                                                                                                                                                                                               |

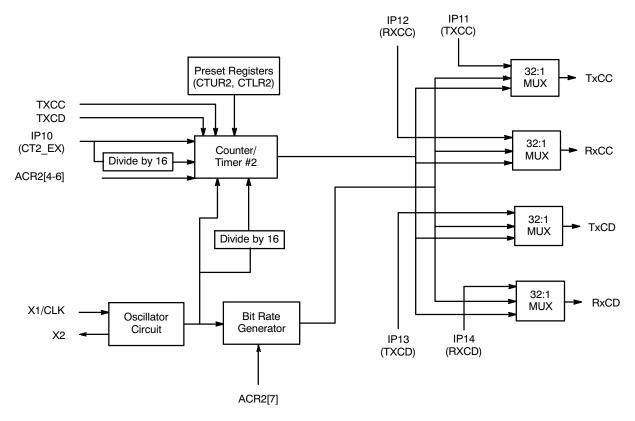

| 43                   |                      | IP12<br>(RXCC_EX)                              | I    | Input 12 (General Purpose Input). This input pin can also be configured to function as the external clock input for the Receiver of Channel C (RXCC_EX).                                                                                                                                                                                                                                                                                  |

| Pin #<br>68 Pin PLCC | Pin #<br>44 Pin PLCC | Symbol            | Туре | Description                                                                                                                                                                                                                                                                                 |

|----------------------|----------------------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44                   | 28                   | IEI<br>(Z-Mode)   | I    | Interrupt Enable Input (Z-Mode; Active High). If this active-high input is at a logic "high", the QUART is capable of generating all non-masked Interrupt Requests to the CPU. If this input is at a logic "low", the QUART is inhibited from generating any Interrupt Requests to the CPU. |

|                      |                      |                   |      | <b>Note:</b> if the user is operating this device in the "68 Mode" or in the "88 I-Mode," then this pin should be tied to V <sub>CC</sub> .                                                                                                                                                 |

| 45                   |                      | IP11<br>(TXCC_EX) | I    | Input 11 (General Purpose Input). This input pin can also be configured to function as the external clock input for the Transmitter of Channel C (TXCC_EX).                                                                                                                                 |

| 46                   |                      | IP10<br>(CT2_EX)  | I    | Input 10 (General Purpose Input). This input pin can be configured to function as the external clock input for Counter/Timer # 2.                                                                                                                                                           |

| 47                   | 29                   | IP9<br>(-CTSD)    | I    | Input 9 (General Purpose Input). This input pin can be configured to function as the active-low, "Channel D Clear-to-Send" input (-CTSD).                                                                                                                                                   |

| 48                   | 30                   | IP8<br>(-CTSC)    | I    | Input 8 (General Purpose Input). This input pin can be configured to function as the active-low, "Channel C Clear-to-Send" input (-CTSC).                                                                                                                                                   |

| 49                   | 31                   | A5                | I    | MSB of Address Input. This input, along with address inputs, A1 - A5 are used to select certain registers within the QUART device during read and write operations with the CPU.                                                                                                            |

| 50                   | 32                   | A4                | 1    | Address Input.                                                                                                                                                                                                                                                                              |

| 51                   | 33                   | A3                | ı    | Address Input.                                                                                                                                                                                                                                                                              |

| 52                   | 34                   | A2                | 1    | Address Input.                                                                                                                                                                                                                                                                              |

| 53                   | 35                   | A1                | 1    | LSB of Address Input.                                                                                                                                                                                                                                                                       |

| 54                   | 36                   | IP0<br>(-CTSA)    | I    | Input 0 (General Purpose Input). This input can be configured to function as the active-low "Clear-to-Send" input for Channel A (-CTSA).                                                                                                                                                    |

| 55                   | 37                   | IP1<br>(-CTSB)    | I    | Input 1 (General Purpose Input). This input can be configured to function as the active-low "Clear-to-Send" input for Channel B (-CTSB).                                                                                                                                                    |

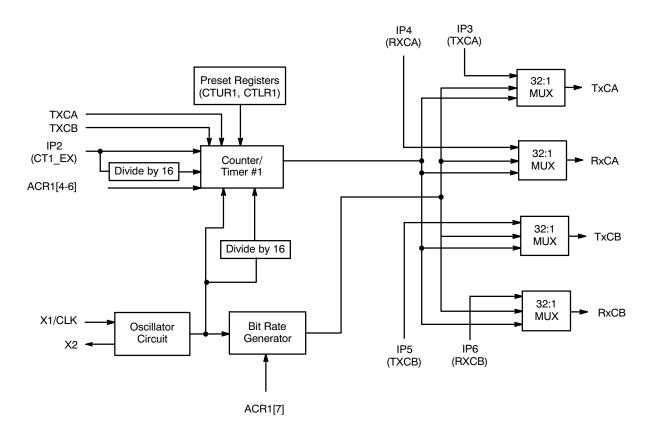

| 56                   |                      | IP2<br>(CT1_EX)   | I    | Input 2 (General Purpose Input). This input can be configured to function as the external clock input for Counter/Timer # 1.                                                                                                                                                                |

| 57                   |                      | IP3<br>(TXCA_EX)  | I    | Input 3 (General Purpose Input). This input can be configured to function as the external clock input for the Channel A Transmitter.                                                                                                                                                        |

| 58                   | 38                   | -RD<br>(88 Mode)  |      | Read Strobe ("88 Mode"; Active Low). A "low" on this input while -CS is also "low" places the contents of the addressed QUART register, on the Data Bus.                                                                                                                                    |

|                      |                      |                   |      | <b>Note:</b> If the user is operating this device in the "68-Mode" then this input should be tied to V <sub>CC</sub> .                                                                                                                                                                      |

| 59                   |                      | IP4<br>(RXCA_EX)  | I    | Input 4 (General Purpose Input). This input can be configured to function as the external clock input for the Channel A Receiver.                                                                                                                                                           |

.01 9

| Pin #<br>68 Pin PLCC | Pin #<br>44 Pin PLCC | Symbol            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|----------------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60                   |                      | IP5<br>(TXCB_EX)  | I    | Input 5 (General Purpose Input). This input can be configured to function as the external clock input for the Channel B Transmitter.                                                                                                                                                                                                                                                                                                      |

| 61                   |                      | IP6<br>(RXCB_EX)  | ı    | Input 6 (General Purpose Input). This input can be configured to function as the external clock input for the Channel B Receiver.                                                                                                                                                                                                                                                                                                         |

| 62                   |                      | IP7               | I    | Input 7 (General Purpose Input).                                                                                                                                                                                                                                                                                                                                                                                                          |

| 63                   | 39                   | RXDA              | I    | Reveive Serial Data Input (Channel A). The least significant bit of the character is received first. If external receiver clock, RXCA, is specified, the data is sampled on the rising edge of this clock.                                                                                                                                                                                                                                |

| 64                   | 40                   | TXDA              | O    | Transmitter Serial Data Output (Channel A). The least significant bit of the character is transmitted first. This output is held in the high (marking state) when the transmitter is idle, disabled, or when the channel is operating in the local LOOPBACK mode. If an external transmitter clock is specified, TXCA, the transmitted data is shifted out of the TSR (Transmitter Shift Register) on the falling the edge of this clock. |

| 65                   | 41                   | OP0<br>(-RTSA)    | 0    | Output 0 (General Purpose Output). This output port pin can also be configured to function as the active-low, open-drain Request-to-Send output for Channel A (-RTSA).                                                                                                                                                                                                                                                                    |

| 66                   | 42                   | OP1<br>(-RTSB)    | 0    | Output 1 (General Purpose Output). This output port pin can also be configured to function as the active-low, open-drain Request-to-Send output for Channel B (-RTSB).                                                                                                                                                                                                                                                                    |

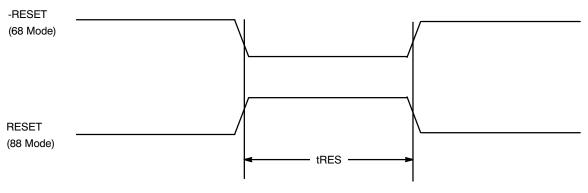

| 67                   | 43                   | RESET             | I    | Master Reset (Active High for the "88 Mode", and Active Low for the "68 Mode"). Asserting this input clears the following internal registers: SRn, ISRn, IMRn, OPRn, OPCRn, and initializes the IVRn to 0Fh, stops both of the Counter/Timers, puts 0P0 - OP15 in the high state, and places all four serial channels in the inactive state with the TXDA, TXDB, TXDC, and TXDD output marking (high).                                    |

| 68                   | 44                   | V <sub>CC</sub> 1 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## DC ELECTRICAL CHARACTERISTICS 1,2

**Test Conditions:**  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$  unless otherwise specified.

| Symbol             | Parameter                             | Min. | Тур. | Max.     | Unit | Conditions                 |

|--------------------|---------------------------------------|------|------|----------|------|----------------------------|

| V <sub>IL</sub>    | Input Low Voltage                     | 0.5  |      | 8.0      | V    |                            |

| $V_{IH}$           | Input High Voltage                    | 2.0  |      | $V_{CC}$ | V    |                            |

| $V_{IHX1}$         | Input High Voltage (X1/CLK)           | 4.0  |      | $V_{CC}$ | V    |                            |

| $V_{OL}$           | Output Low Voltage                    |      |      | 0.4      | V    | IOL = 2.4mA                |

| $V_{OH}$           | Output High Voltage                   | 2.4  |      |          | V    | IOH = -400• A              |

| I <sub>IL</sub>    | Input Leakage Current                 | -25  |      | 25       | • A  | VIN = 0 to V <sub>CC</sub> |

| I <sub>ILSEL</sub> | Select Pin Leakage Current            | -30  |      | 30       | • A  | VIN = 0 to V <sub>CC</sub> |

| I <sub>X1L</sub>   | X1 Input Low Current                  |      | -20  |          | • A  | VIN = 0                    |

| I <sub>X2L</sub>   | X2 Input Low Current                  |      | -7   |          | mA   |                            |

| I <sub>XIH</sub>   | X1 Input High Current                 |      | 20   |          | • A  | VIN = V <sub>CC</sub>      |

| I <sub>X2H</sub>   | X2 Input High Current                 |      | 20   |          | • A  | VIN = V <sub>CC</sub>      |

| I <sub>LL</sub>    | Data Bus Tri-State Leakage<br>Current | -10  |      | 10       | •A   | VO = 0 to V <sub>CC</sub>  |

| l <sub>oc</sub>    | Open Drain Output Leakage<br>Current  | -10  |      | 10       | •A   | VO = 0 to V <sub>CC</sub>  |

| I <sub>CCA</sub>   | Power Supply Current <sup>3</sup>     |      | 6    | 15       | mA   | Active Mode                |

| I <sub>ccs</sub>   | Power Supply Current <sup>3</sup>     |      | 3    | 10       | mA   | Standby Mode               |

#### Notes

<sup>&</sup>lt;sup>1</sup> Parameters are valid over the specified temperature and operating supply ranges. Typical values are 25°C, V<sub>CC</sub> = 5V and typical processing parameters.

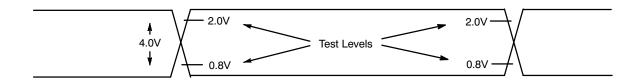

<sup>&</sup>lt;sup>2</sup> All voltages are referenced to ground (GND). For testing, input signal levels are 0.4V and 2.4V with a transition time of 20ns maximum. All time measurements are referenced at input voltages of 0.8V and 2.0V as appropriate. See NO TAG.

<sup>&</sup>lt;sup>3</sup> Measured operating with a 3.6864 MHz crystal and with all outputs open.

<sup>&</sup>lt;sup>4</sup> The minimum high time must be at least 1.5 times the X1/CLK period and the minimum low time must be at least equal to the X1/CLK period if either channel's Receiver is operating in external 1X clock mode.

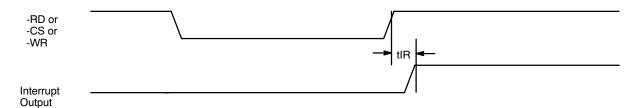

# AC ELECTRICAL CHARACTERISTICS 1, 2, 3

**Test Conditions:**  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$  unless otherwise specified.

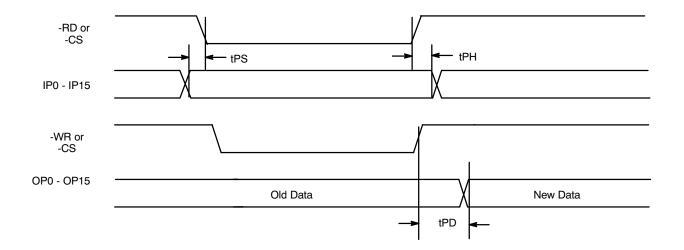

| Symbol           | Parameter                                                 | Min.             | Тур.                  | Max.      | Unit        | Conditions    |

|------------------|-----------------------------------------------------------|------------------|-----------------------|-----------|-------------|---------------|

| Reset Timin      | g (See <i>Figure 56</i> )                                 |                  |                       |           |             |               |

| tRES             | RESET Pulse Width                                         | 1.0              |                       |           | •s          |               |

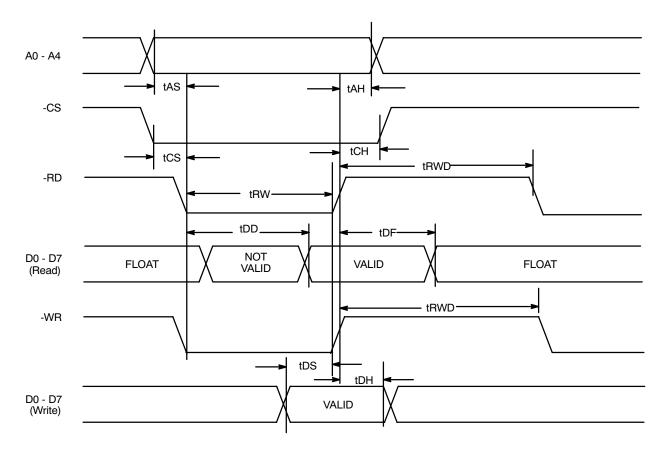

| XR82C684 R       | ead and Write Cycle Timing - 88 N                         | lode ( <i>Fi</i> | gure 57) <sup>7</sup> |           |             |               |

| t <sub>AS</sub>  | A0-A4 Setup Time to RD, WR<br>Low                         | 10               |                       |           | ns          |               |

| t <sub>AH</sub>  | A0-A4 Hold Time from RD, WR<br>Low                        | 0                |                       |           | ns          |               |

| t <sub>CS</sub>  | -CS Setup Time to RD, WR Low                              | 0                |                       |           | ns          |               |

| t <sub>CH</sub>  | -CS Hold Time from -RD, -WR<br>High                       | 0                |                       |           | ns          |               |

| $t_{RW}$         | -RD, -WR Pulse Width                                      | 225              |                       |           | ns          |               |

| t <sub>DD</sub>  | Data Valid from -RD Low                                   |                  | 60                    | 175       | ns          |               |

| t <sub>DF</sub>  | Data Bus Floating from -RD High                           | 10               |                       | 100       | ns          |               |

| t <sub>DS</sub>  | Data Setup Time to -WR High                               | 100              |                       |           | ns          |               |

| t <sub>DH</sub>  | Data Hold Time from -WR High                              | 5                |                       |           | ns          |               |

| t <sub>RWD</sub> | High Time between Reads and/<br>or Writes <sup>8, 9</sup> |                  | 100                   |           | ns          |               |

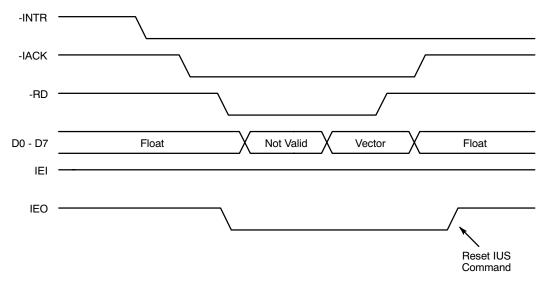

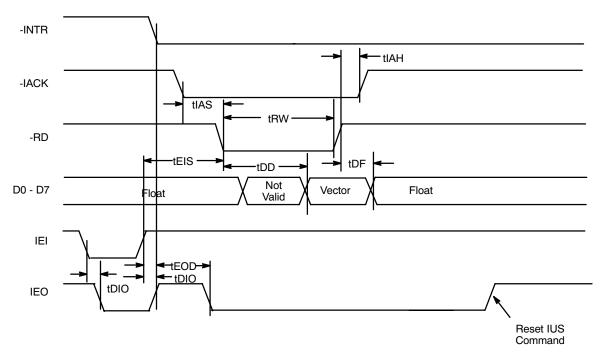

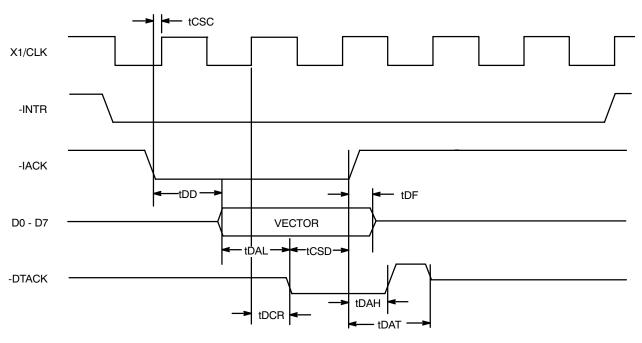

| Z-Mode Inte      | rrupt Cycle Timing (Figure 58)                            |                  |                       |           |             |               |

| t <sub>DIO</sub> | IEO Delay Time from IEI                                   |                  |                       | 100       | ns          |               |

| t <sub>IAS</sub> | IACK Setup Time to RD Low <sup>10</sup>                   |                  | Note 10               |           | ns          |               |

| t <sub>IAH</sub> | IACK Hold Time from RD High                               |                  | 0                     |           | ns          |               |

| t <sub>EIS</sub> | IEI Setup Time to RD Low                                  |                  | 50                    |           | ns          |               |

| t <sub>EOD</sub> | IEO Delay Time from INTR Low                              |                  |                       | 100       | ns          |               |

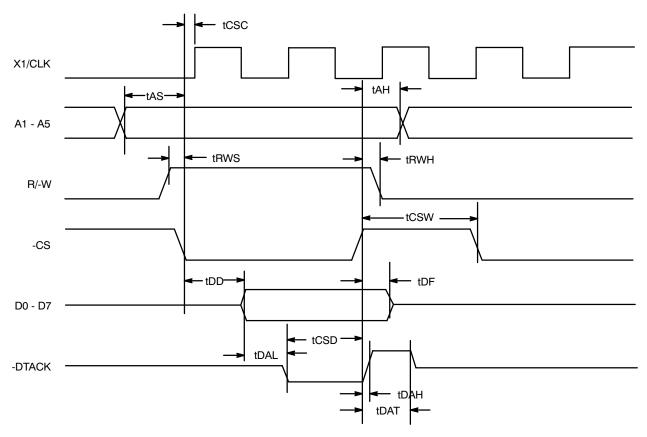

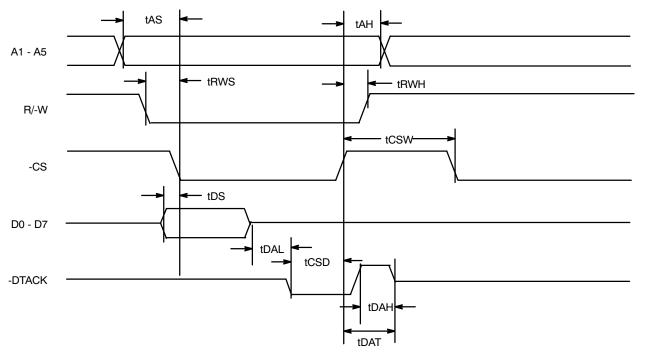

| XR82C684 R       | ead, Write and Interrupt Cycle Tin                        | ning -68 l       | Mode ( <i>Fi</i> g    | ure 59, F | igure 60 aı | nd Figure 61) |

| t <sub>AS</sub>  | A1-A5 Setup Time to -CS Low                               | 10               |                       |           | ns          |               |

| t <sub>AH</sub>  | A1-A5 Hold Time from -CS High                             | 0                |                       |           | ns          |               |

| t <sub>RWS</sub> | R/-W Setup Time to -CS Low                                | 0                |                       |           | ns          |               |

| t <sub>RWH</sub> | R/-W Setup Time from -CS High                             | 0                |                       |           | ns          |               |

| t <sub>CSW</sub> | -CS High Pulse Width 9, 11                                | 90               |                       |           | ns          |               |

| t <sub>CSD</sub> | -CS or -IACK High from -DTACK<br>Low                      | 20               |                       |           | ns          |               |

| t <sub>DD</sub>  | Data Valid from -CS or -IACK<br>Low                       |                  |                       | 175       | ns          |               |

| t <sub>DF</sub>  | Data Bus Floating from -CS or -IACK High                  | 10               |                       | 100       | ns          |               |

| t <sub>DS</sub>  | Data Setup Time to -CS Low                                | 0                |                       |           | ns          |               |

| t <sub>DH</sub>  | Data Hold Time from -CS Low                               | 125              |                       |           | ns          |               |

| t <sub>DAL</sub> | -DTACK Low from Read Data<br>Valid                        | 0                |                       |           | ns          |               |

# AC ELECTRICAL CHARACTERISTICS 1, 2, 3 (CONT'D)

| Parameter                                              | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Тур.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lead, Write and Interrupt Cycle Tir                    | ning -68 l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mode ( <i>Fig</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ure 59, F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | igure 60 a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nd Figure 61) (Cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

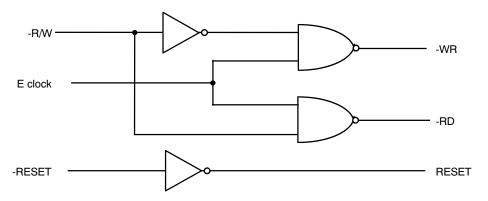

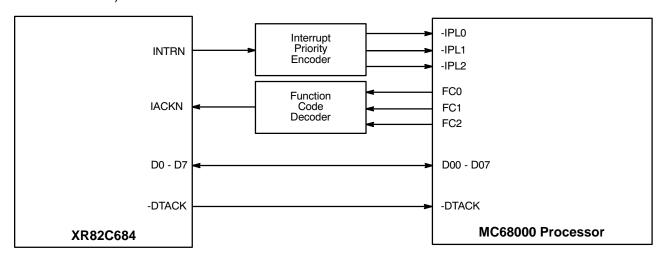

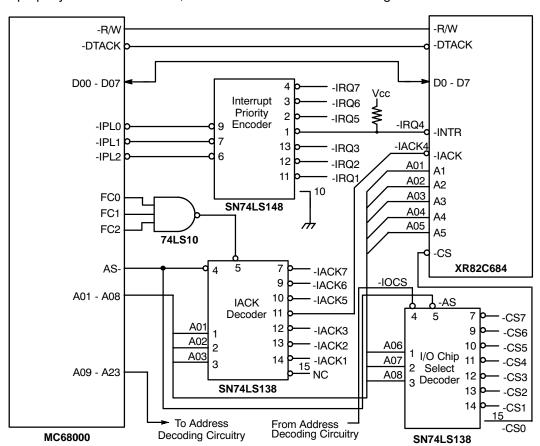

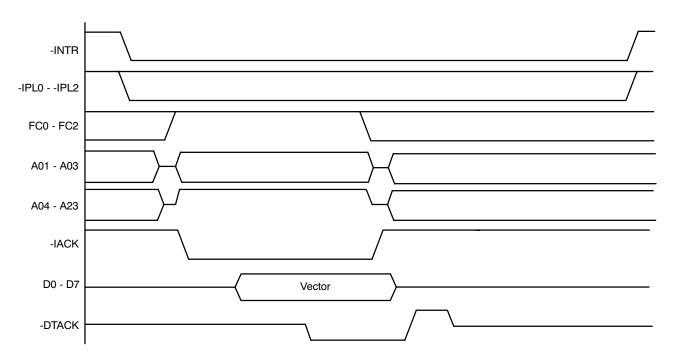

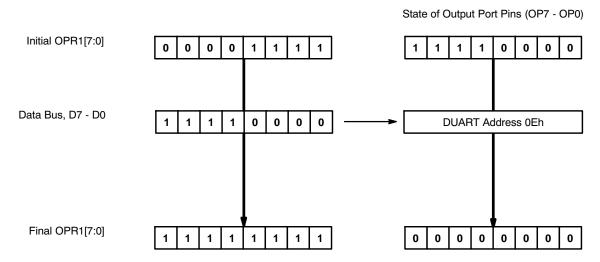

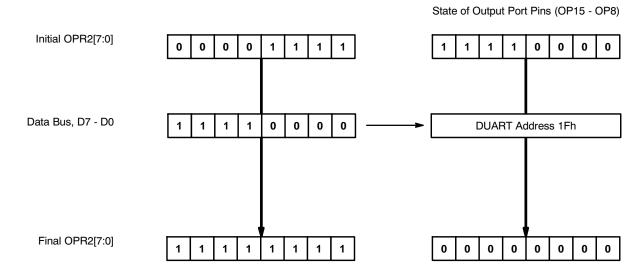

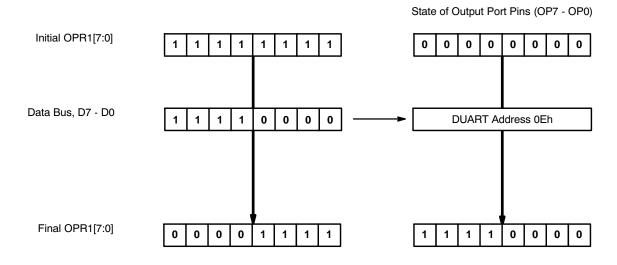

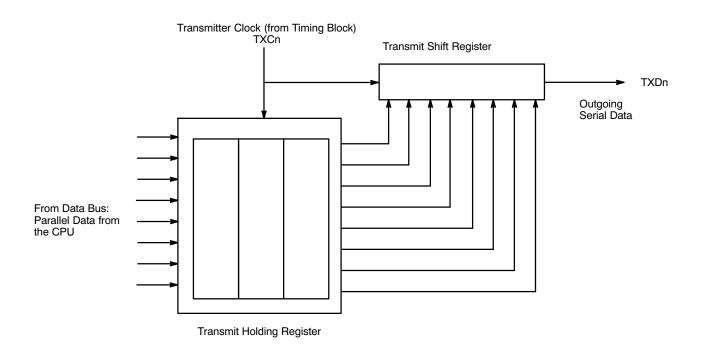

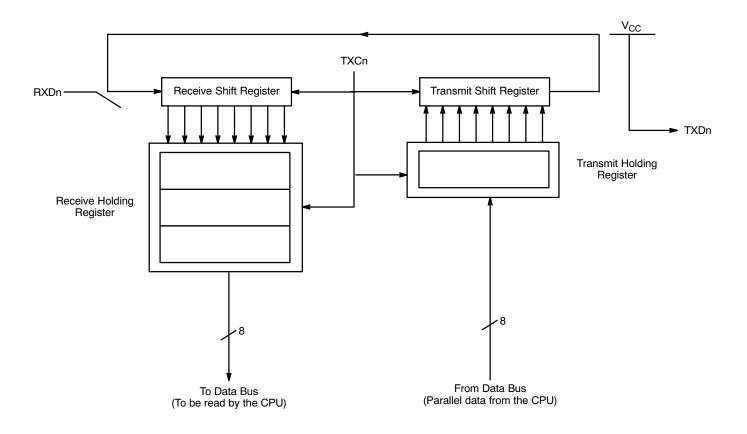

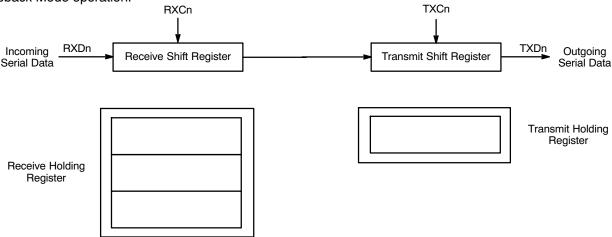

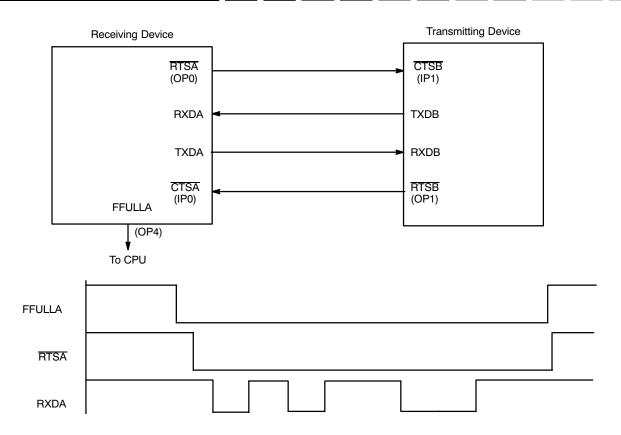

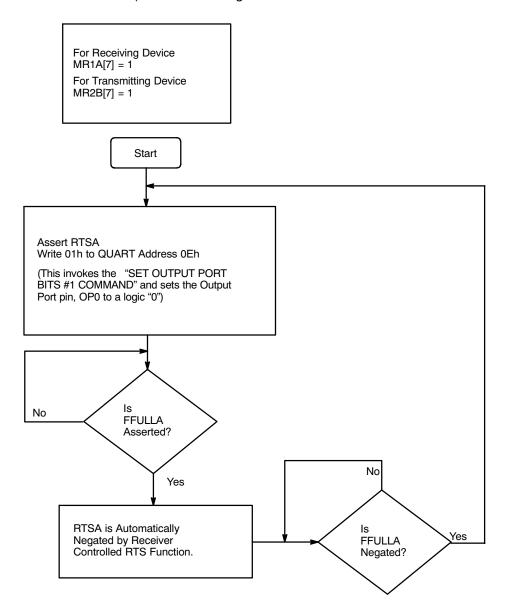

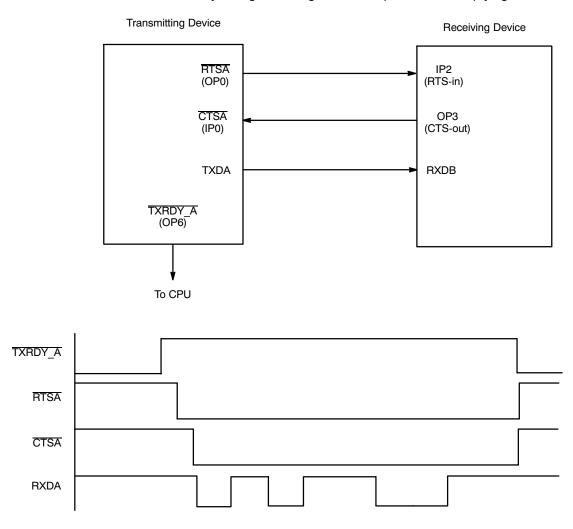

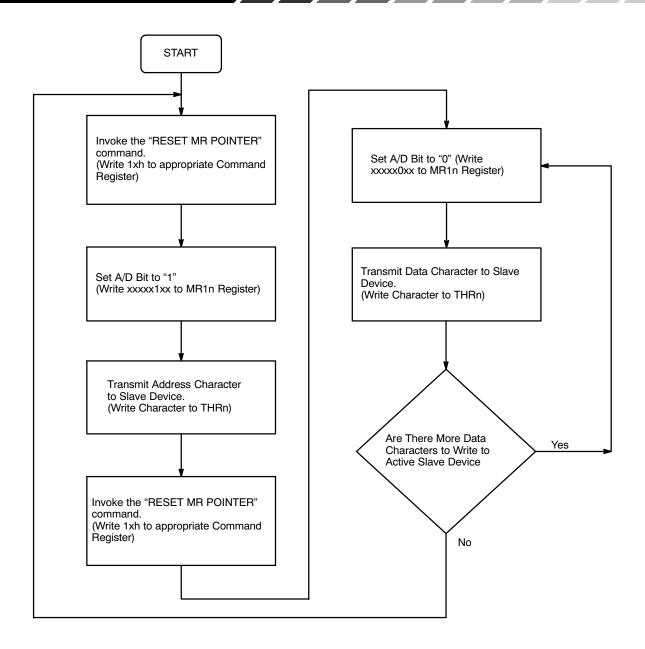

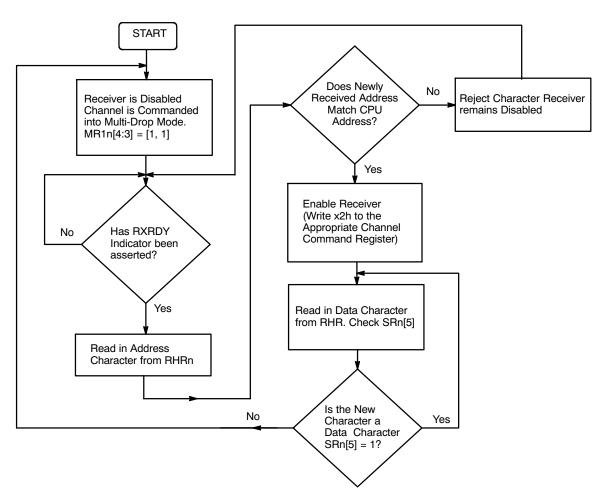

| -DTACK High from -CS or -IACK<br>High                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |