Z80382/Z8L382

# Z80382 Data Communications Processor

**Preliminary Product Specification**

PS006702-1201

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### **ZiLOG Worldwide Headquarters**

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

©2001 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

#### **Manual Conventions**

The following conventions have been adopted to provide clarity and ease of use:

- Courier Regular 10-point highlights the following items

- Bit

- Software code

- File names and paths

- Hexadecimal value

PS006701-0800 Conventions

#### Z80382/Z8L382 Z382 Data Communications Processor

#

PS006701-0800 Conventions

# **Table of Contents**

| 200302, 20L302 high-renormance Data Communications Processors |

|---------------------------------------------------------------|

| Features                                                      |

| General Description                                           |

| Z80382 Pin Description                                        |

| Absolute Maximum Ratings                                      |

| Standard Test Conditions                                      |

| DC Characteristics                                            |

| AC Characteristics                                            |

| Pin Functions                                                 |

| Functional Description                                        |

| Central Processing Unit                                       |

| Modes of Operation                                            |

| CPU Address Spaces                                            |

| Data Types                                                    |

| Addressing Modes                                              |

| Instruction Set 54                                            |

| Host Interface                                                |

| 16550 MIMIC                                                   |

| Host DMA Mailbox                                              |

| Plug-and-Play Interface 6 <sup>2</sup>                        |

| PCMCIA Interface                                              |

| DMA Channels 67                                               |

| DMA Channel/Device Interface                                  |

| DMA Operation                                                 |

| Per-Channel Registers                                         |

| Centralized DMA Registers                                     |

| Serial Communication Channels                                 |

| Asynchronous Serial Communications Interface (ASCI)           |

| HDLC Serial Channels77                                        |

| GCI/SCIT Interface 82                                         |

| Clocked Serial I/O (CSIO)                                     |

#### Z80382/Z8L382 |

#### **Z80382 Data Communications Processor**

| Counters, Timers and Other Miscellaneous Logic | 89 |

|------------------------------------------------|----|

| Programmable Reload Timer                      | 89 |

| Watch-Dog Timer                                | 91 |

| Parallel Ports                                 | 92 |

| I/O Chip Selects                               | 93 |

| Interrupt Logic                                | 95 |

| Z380-Compatible Peripheral Functions           | 98 |

| Device Configuration                           | 01 |

| Programmable Low-Noise Drivers 1               | 02 |

| Z382 I/O Register Maps                         | 02 |

| Package Information                            | 11 |

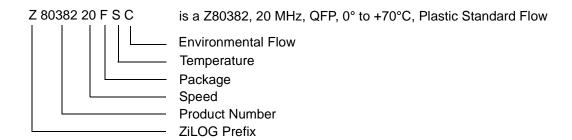

| Ordering Information                           | 13 |

| Device Errata                                  | 14 |

| Index                                          | 15 |

# List of Figures

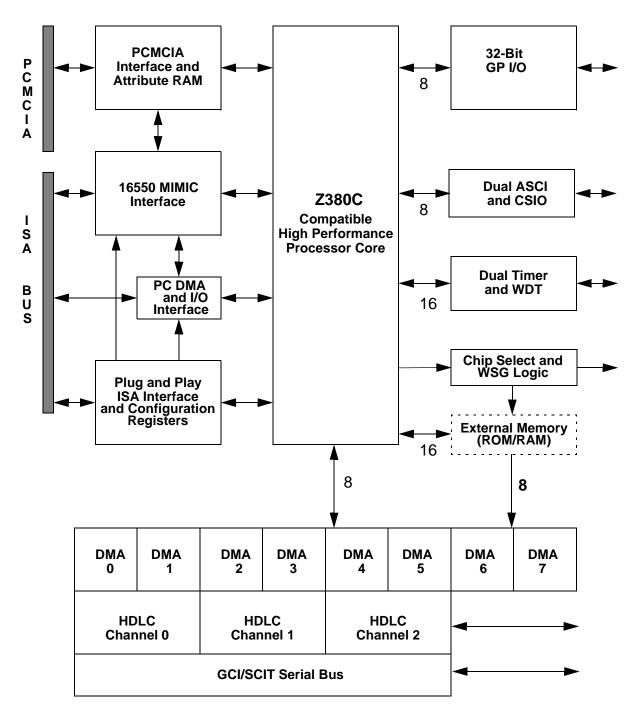

| Figure 1.  | Z80382 Block Diagram                                                                          | . 5 |

|------------|-----------------------------------------------------------------------------------------------|-----|

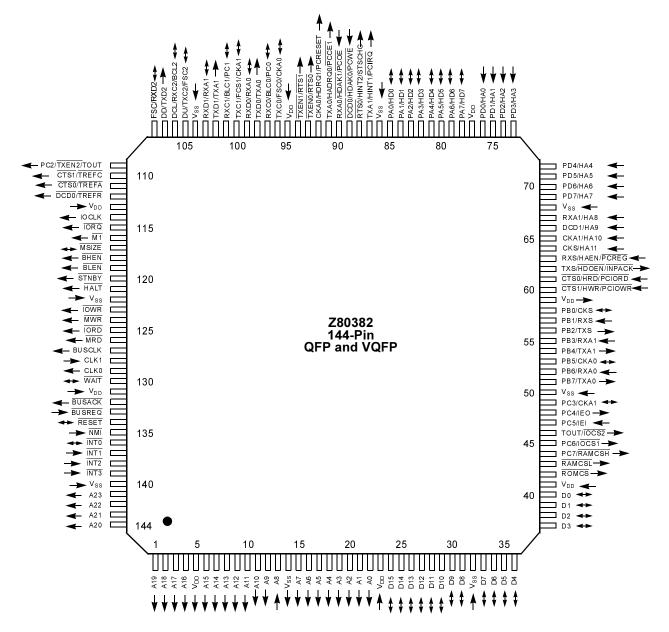

| Figure 2.  | Z80382 144-Pin QFP and VQFP Pin Description                                                   | . 6 |

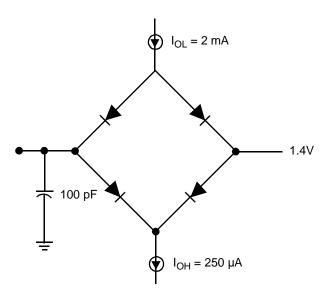

| Figure 3.  | Test Load Diagram                                                                             | . 8 |

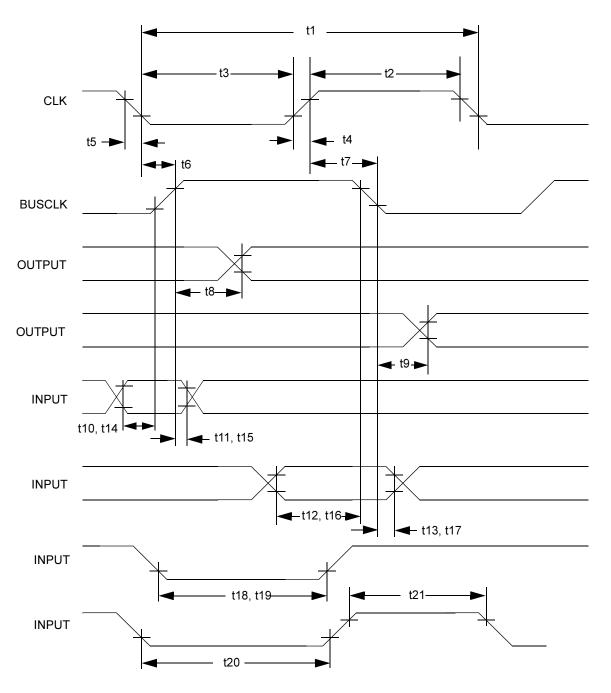

| Figure 4.  | 380C Processor Timing Diagram                                                                 | 16  |

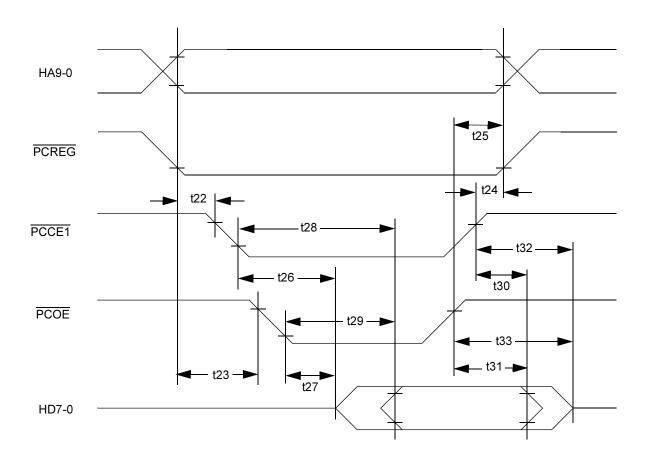

| Figure 5.  | Host - PCMCIA Attribute Memory Read Timing Diagram                                            | 18  |

| Figure 6.  | Host - PCMCIA Attribute Memory Write Timing Diagram                                           | 19  |

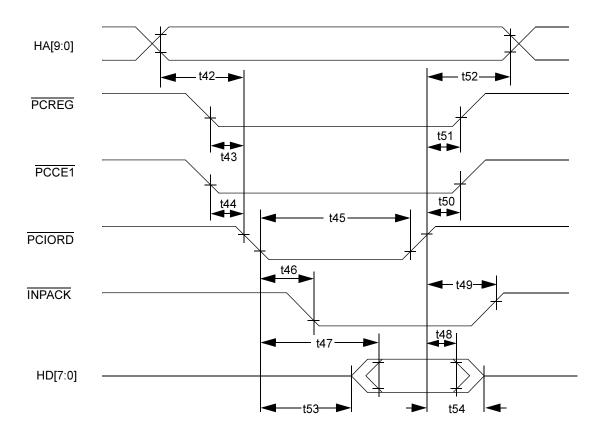

| Figure 7.  | Host - PCMCIA I/O Read Timing Diagram                                                         | 21  |

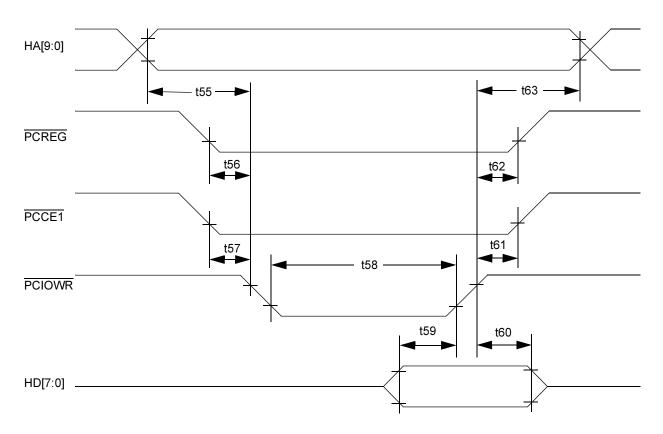

| Figure 8.  | Host - PCMCIA I/O Write Timing Diagram                                                        | 23  |

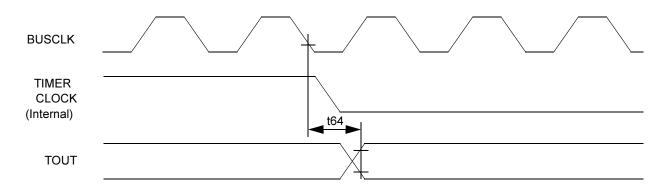

| Figure 9.  | Timer Output Timing Diagram                                                                   | 24  |

| Figure 10. | CSIO Receive/Transmit Timing Diagram                                                          | 25  |

| Figure 11. | ASCI Transmitter Timing Diagram                                                               | 26  |

| Figure 12. | ASCI Receiver Timing Diagram                                                                  | 27  |

| Figure 13. | Baud Rate Generator Timing Diagram                                                            | 28  |

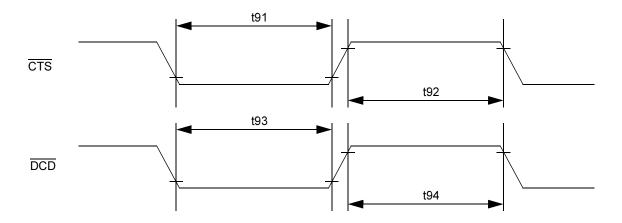

| Figure 14. | CTSA and DCDA Timing Diagram                                                                  | 29  |

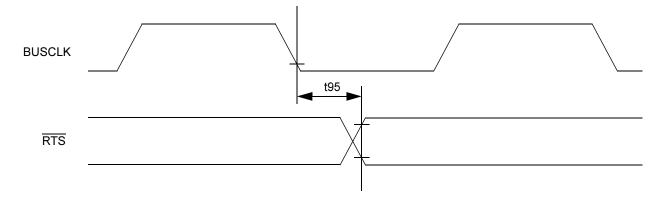

| Figure 15. | RTSA Timing Diagram                                                                           | 29  |

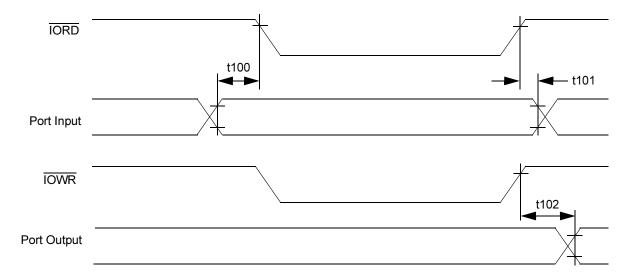

| Figure 16. | General-Purpose I/O Port Timing Diagram                                                       | 30  |

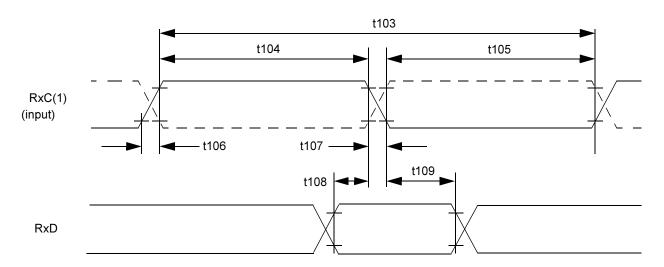

| Figure 17. | HDLC Receive Timing Diagram (Full Time HDLC, RxC Input) $\ldots$                              | 32  |

| Figure 18. | HDLC Receive Timing (Full Time HDLC, RxC Output)                                              | 32  |

| Figure 19. | HDLC Transmit Timing Diagram (Full Time HDLC)                                                 | 33  |

| Figure 20. | HDLC Timing Diagram - Non-GCI TDM Mode (for Start = 3, Length = 2, Negative Edge RxD Sampling | 35  |

| Figure 21. | GCI/SCIT Slave and Master Timing Diagram                                                      | 37  |

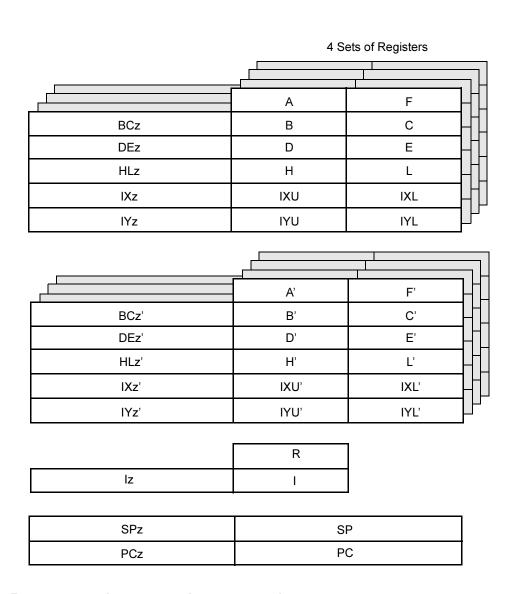

| Figure 22. | 380C Processor Core Register Set                                                              | 50  |

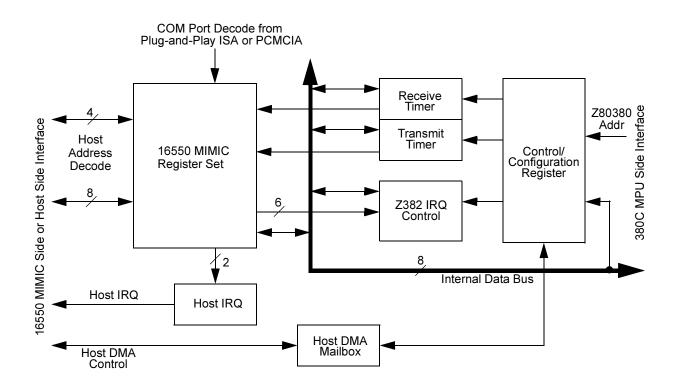

| Figure 23. | 16550 MIMIC Block Diagram                                                                     | 56  |

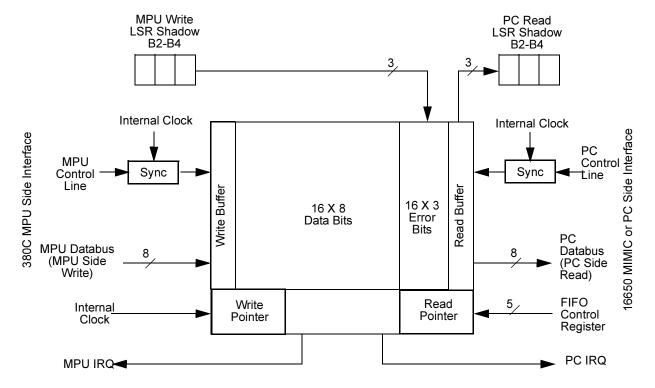

| Figure 24. | 16550 MIMIC Receiver FIFO Block Diagram                                                       | 57  |

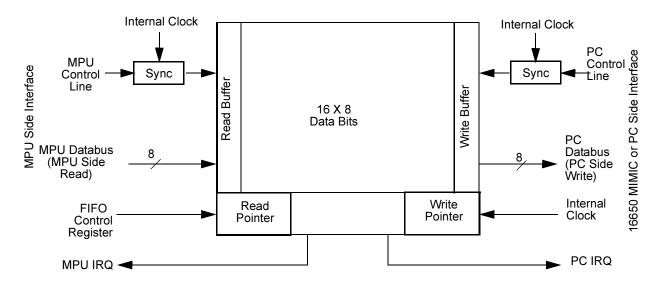

| Figure 25. | 16550 MIMIC Transmitter FIFO Block Diagram                                                    | 58  |

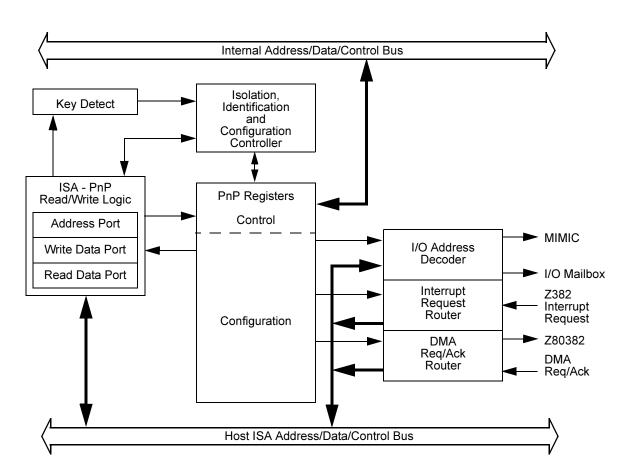

| Figure 26. | Plug-and-Play Interface Block Diagram                                                         | 62  |

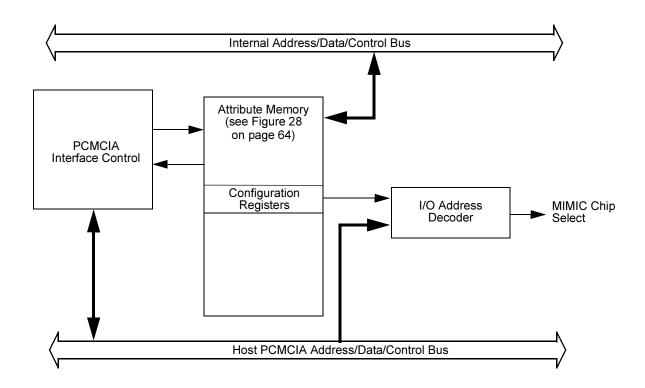

| Figure 27. | PCMCIA Interface Block Diagram                                                                | 65  |

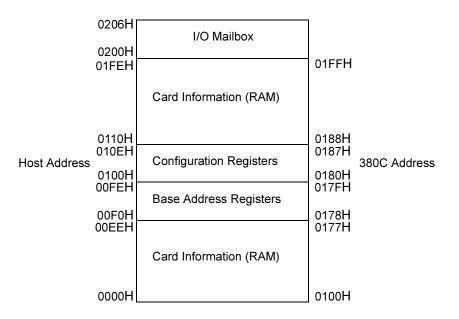

| Figure 28. | PCMCIA Attribute Memory Organization                                                          | 66  |

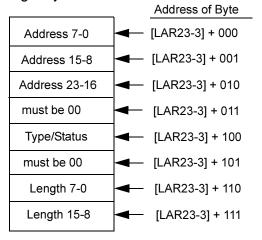

| Figure 29. | General Format of a DMA List Entry                                                            | 68  |

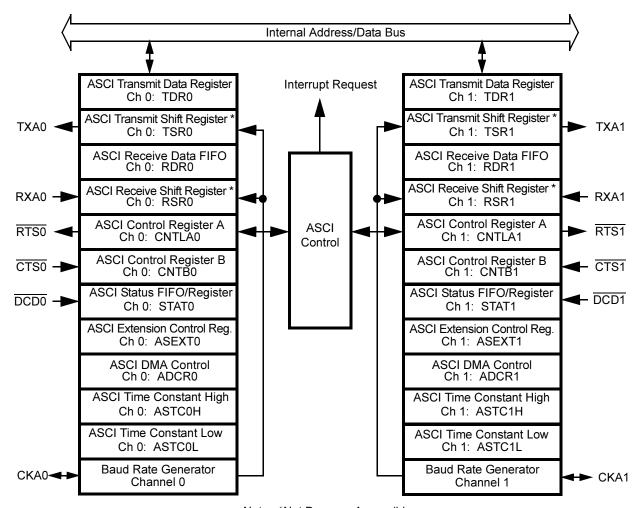

| Figure 30. | Asynchronous Serial Communications Interface (ASCI) Block Diagram                             | 74  |

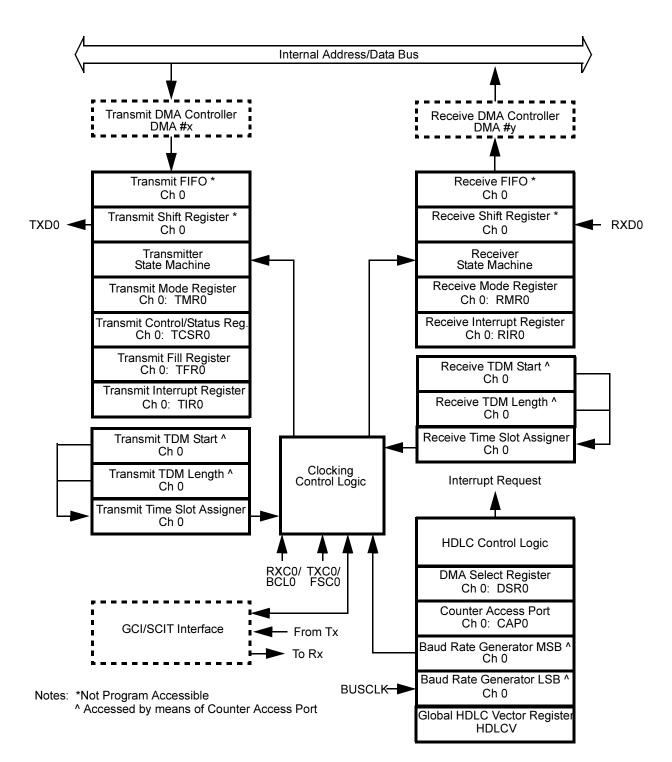

| Figure 31. | HDLC Channel Block Diagram (One of Three Channels Illustrated)                                | 78  |

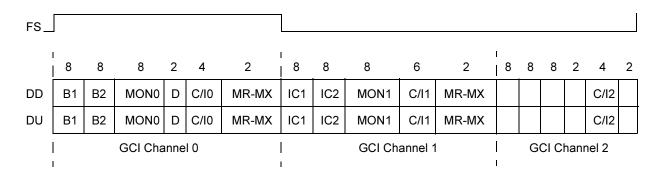

| Figure 32  | GCI/SCIT Frame Structure                                                                      | 83  |

#### Z80382/Z8L382

### **Z80382 Data Communications Processor**

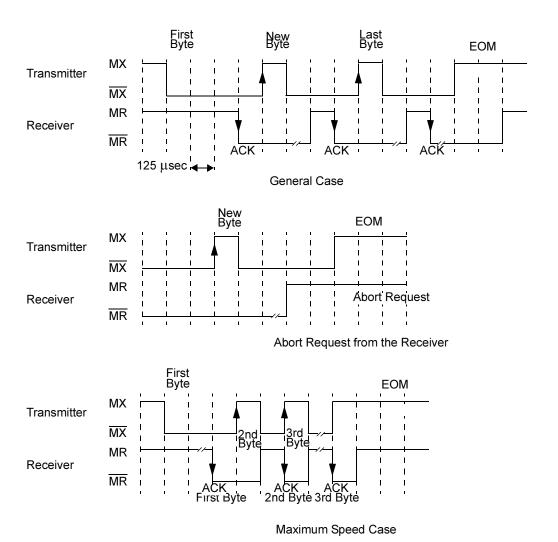

| Figure 33. | Monitor Handshake Timing Diagram                  | 86  |

|------------|---------------------------------------------------|-----|

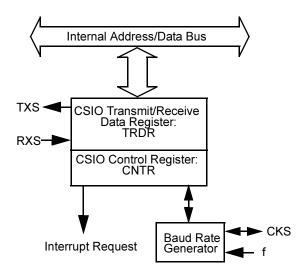

| Figure 34. | CSIO Block Diagram                                | 88  |

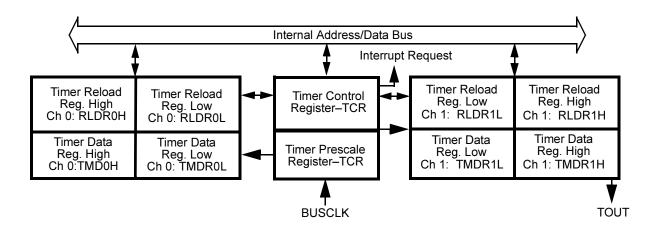

| Figure 35. | Programmable Reload Timer Block Diagram           | 90  |

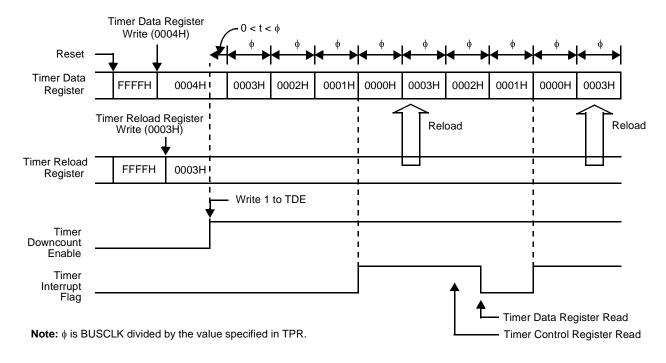

| Figure 36. | PRT Operation Timing Diagram                      | 91  |

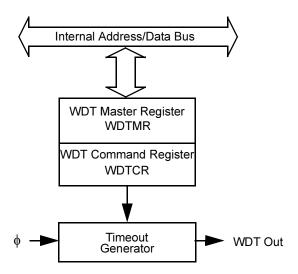

| Figure 37. | Watch-Dog Timer Block Diagram                     | 92  |

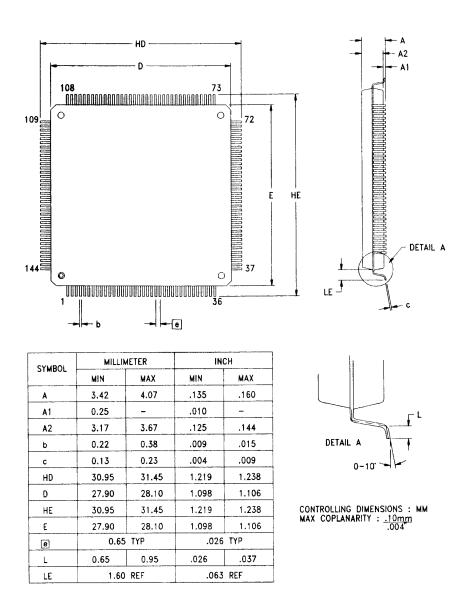

| Figure 38. | 144-Lead Plastic QFP Package Diagram 1            | 111 |

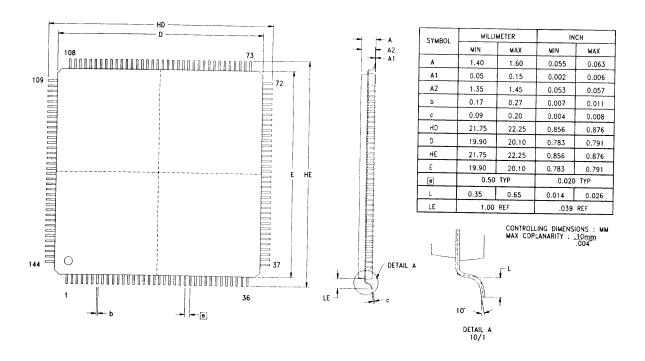

| Figure 39. | 144-Lead Plastic Low Profile VQFP Package Diagram | 112 |

# List of Tables

| Table 1.  | Pin Numbers and Input/Output Classifications   | 8    |

|-----------|------------------------------------------------|------|

| Table 2.  | Output Class Characteristics                   | . 11 |

| Table 3.  | Input Class Characteristics                    | . 12 |

| Table 4.  | DC Electrical Characteristics                  | . 13 |

| Table 5.  | AC Characteristics                             | 14   |

| Table 6.  | Host-PCMCIA Attribute Memory Read Timing       | . 17 |

| Table 7.  | Host-PCMCIA Attribute Memory Write Timing      | . 19 |

| Table 8.  | Host-PCMCIA I/O Read                           | 20   |

| Table 9.  | Host-PCMCIA I/O Write Timing                   | 22   |

| Table 10. | Timer Output Timing                            | 24   |

| Table 11. | CSIO Receive/Transmit Timing                   | 25   |

| Table 12. | ASCI Transmitter Timing                        | 26   |

| Table 13. | ASCI Receiver Timing                           | 27   |

| Table 14. | ASCI/CSIO Timing                               | 28   |

|           | General-Purpose I/O Port Timing                |      |

| Table 16. | HDLC Receive Timing                            | 31   |

| Table 17. | HDLC Transmit Timing                           | . 33 |

| Table 18. | HDLC Timing - Non-GCI TDM Mode                 | 34   |

| Table 19. | GCI/SCIT Timing - Slave Characteristics        | 35   |

| Table 20. | GCI/SCIT Timing - Master Characteristics       | 36   |

| Table 21. | Multiprocessor Unit (MPU) Signals              | . 38 |

| Table 22. | UART, Timer and CSIO Signals                   | 42   |

| Table 23. | ISA Bus Signals                                | 43   |

| Table 24. |                                                |      |

| Table 25. | Parallel Ports                                 | 44   |

| Table 26. | PCMCIA Interface Signals                       | 45   |

|           | Other Signals                                  |      |

| Table 28. | MIMIC Programming Registers                    |      |

| Table 29. | MIMIC-Host Registers                           | 60   |

| Table 30. | DMA Channel/Device Interface                   |      |

| Table 31. | Type/Status Definitions                        | 69   |

| Table 32. | Per-Channel Registers                          | . 72 |

| Table 33. | Pin Use Differences in TDM/Full Time Operation | . 77 |

| Table 34. | HDLC Channel/GCI/SCIT Interface                | . 79 |

#### Z80382/Z8L382

### **Z80382 Data Communications Processor**

| v |

|---|

|   |

| Table 35. | GCI Subchannel Start and Length Values | 79 |

|-----------|----------------------------------------|----|

| Table 36. | Interrupt Source Priorities            | 96 |

| Table 37. | Interrupt Sources and Assigned Vectors | 97 |

| Table 38. | Z80380-Compatible Registers            | 02 |

| Table 39. | Z80382 ASCI, PRT, CSIO, WDT Registers  | 03 |

| Table 40. | Port and New Z80382 Registers          | 04 |

| Table 41. | DMA Registers 1                        | 05 |

| Table 42. | HDLC Registers                         | 06 |

| Table 43. | GCI/SCIT Registers                     | 07 |

| Table 44. | Z80382 MIMIC Registers                 | 30 |

| Table 45. | PCNMCIA Memory and Registers           | 08 |

| Table 46. | Plug-and-Play ISA Registers            | 09 |

# Z80382, Z8L382 Data Communications Processor

#### **Features**

- Embedded Z380<sup>™</sup> Microprocessor

- Maintains Object Code Compatibility with Z80<sup>®</sup> and Z180<sup>™</sup> Microprocessors

- Enhanced Instruction Set for 16-Bit Operation

- 16 MB Linear Addressing

- Two Clock Cycle Instruction Execution Minimum

- Four On-Chip Register Banks

- BC/DE/HL/IX/IY Augmented to 32 Bits

- Clock Divide-by-Two and Multiply-by-Two Options

- Fully Static CMOS Design with Low-Power STANDBY Mode

- 16-Bit Internal Bus

- Dynamic Bus Sizing (8/16-Bit Inter-Operability)

- 16550 MIMIC with I/O Mailbox, DMA Mailbox, and 16 mA Bus Drive

- Three HDLC Synchronous Serial Channels

- Serial Data Rate of up to 10 Mbps

- GCI/SCIT Bus Interface

- Eight Advanced DMA Channels with 24-Bit Addressing

- Plug-and-Play ISA Interface

- PCMCIA Interface

- Two Enhanced ASCIs (UARTs) with 16-Bit Baud Rate Generators (BRG)

- Clocked Serial I/O Channel (CSIO) for Use with Serial Memory

- Two 16-Bit Timers with Flexible Prescalers

- Three Memory Chip Selects with Wait-State Generators

- Watch-Dog Timer (WDT)

- Up to 32 General-Purpose I/O Pins

- DC to 20 MHz Operating Frequency @ 5.0V

- DC to 10 MHz Operating Frequency @ 3.3V

- 144-Pin QFP and VQFP Style Packages

## **General Description**

The Z80382 (Z382) is designed to address high-end data communication applications such as digital modems (ISDN, GSM, Mobitex & Modacom), xDSL and analog modems (V.34 and beyond). The Z382 provides a performance upgrade to existing Z80- and Z18x-based designs by utilizing the increased bandwidth of the 380C processor. The Z8L382 is a low voltage version of the device.

Notes: In this document the notation 380C denotes the Z380-compatible CPU core which is embedded in the Z382.

An overline ( ) above a signal name indicates that the signal is asserted in the Low state and negated in the High state.

The 380C microprocessor is a high-performance processor with fast and efficient throughput and increased memory addressing capabilities. The 380C offers a continuing growth path for present Z80- or Z18x-based designs, while maintaining Z80 and Z180 object code compatibility. Its enhancements include added instructions, expanded 16 MB address space and flexible bus interface timing.

In the 380C, the basic addressing modes of the Z80 microprocessor have been augmented to include Stack Pointer Relative loads and stores, 16-bit and 24-bit indexed offsets, and more flexible Indirect Register addressing. Internally, all of the addressing modes allow up to 32-bit linear addressing; however, the Z382 has 24 address pins, therefore it can address a maximum of 16 MB of memory.

Other additions to the instruction set include a full complement of 16-bit arithmetic and logical operations, 16-bit I/O operations, multiply and divide, and a complete set of register-to-register loads and exchanges.

The 380C register file includes alternate versions of the IX and IY registers. There are four banks of registers in the 380C, along with instructions for switching among them. All of the 16-bit register pairs and index registers in the basic Z80 microprocessor register file are expanded to 32 bits.

The Z382 includes dynamic bus sizing to allow any mix of 8- and 16-bit memory, and I/O devices in a system. One application for this capability would be to copy code from a low-cost, slow 8-bit ROM to 16-bit RAM, from which it can be exe-

3

cuted at much higher speeds. Memory bus sizes can be configured internally by software to eliminate the need for external logic to drive MSIZE.

Some features that have traditionally been handled by external peripherals have been incorporated in the Z382. These on-chip peripherals reduce system chip count and interconnections on the external bus. These peripherals, illustrated in the Z382 Block Diagram in Figure 1, are summarized below.

**HDLC Synchronous Channels.** Three HDLC channels operate at serial data rates of up to 10 Mbps and feature 8-byte receive and transmit FIFOs. These can be used for modems, general data communications, and ISDN. The ISDN can be handled separately or through the GCI/SCIT bus interface. HDLC Channels always transfer data through the DMA channels. A transparent mode is selectable. Two of the HDLC cells can be pin multiplexed with the ASCIs (UARTs) to provide dynamically switchable (async-sync) DTE interfaces.

**DMA Channels**. The eight DMA channels provide 24-bit memory addressing and can transfer memory block sizes of up to 64 KB (16-bits) word. These DMA channels can be dynamically assigned to serve the HDLC ports, MIMIC COM port, Host DMA Mailbox, or ASCIs in any mixture. Linked list operation allows all HDLC transmitters and receivers to operate at or above T1/E1 rates simultaneously without loading the bus bandwidth.

**16550 MIMIC.** Provides connection to a PC ISA bus and emulation of the 16550 UART register set. Improvements include 16 mA output drivers and internal COM port address decoding to reduce external PC interface components.

**ASCI**. Two flexible asynchronous serial channels with baud rate generators, modem control and status.

**CSIO**. A clocked serial I/O channel which can be used for serial memory interface.

**Timers**. Two 16-bit counter/timers with flexible prescalers for wide-range timing applications.

**GCI/SCIT Bus Interface**. A common interface to ISDN interface devices. Internal signals from this module can be connected to the HDLC channels to provide two B-channels and one D-channel for ISDN.

**Plug-and-Play ISA Interface**. Provides auto-configuration in ISA (AT bus) applications.

**PCMCIA Interface**. Provides connectivity to a PCMCIA bus.

**32-Bit General-Purpose I/O**. For non-PC add-in applications, four 8-bit ports are provided for general- purpose I/O. In ISA or PCMCIA applications, the pins from two of the ports are reallocated to host bus signals and are not available. Pins from the other two ports are selectively multiplexed with on-chip peripheral functions (ASCIs, CSIO, PRT). These pins are individually programmable for input/output mode.

#### Z80382/Z8L382 Z80382 Data Communications Processor

**I/O Chip Selects.** Two I/O chip selects are provided to support I/O access of external peripherals. Each has a programmable base address and provides I/O decode sizes ranging from 8 to 512 bytes.

**ROM/RAM Chip Selects with Wait-State Generators**. Chip select outputs are provided to decode memory addresses and provide memory chip enables. Each chip select has its own Wait State Generator to allow use of memories with different speeds.

**Watch-Dog Timer**. A Watch-Dog Timer (WDT) with a wide range of time-constants prevents code runaway and possible resulting system damage. The RESET input can be forced as an output upon the terminal count of the WDT. This allows external peripherals to be reset along with the Z382

Figure 1. Z80382 Block Diagram

## **Z80382 Pin Description**

Figure 2. Z80382 144-Pin QFP and VQFP Pin Description

## **Absolute Maximum Ratings**

| Symbol           | Description    | Value                        |    |

|------------------|----------------|------------------------------|----|

| V <sub>DD</sub>  | Supply Voltage | -0.3 to +7.0                 | V  |

| V <sub>IN</sub>  | Input Voltage  | -0.3 to V <sub>DD</sub> +0.3 | V  |

| T <sub>OPR</sub> | Operating Temp | 0 to +70                     | °C |

| T <sub>STG</sub> | Storage Temp   | -55 to +150                  | °C |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This rating is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Standard Test Conditions**

The DC Characteristics which follow apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND (0V). Positive current flows into the referenced pin (Figure 3, Test Load Diagram).

- Operating temperature range:

- Standard: 0°C to 70°C

- Voltage Supply Range:

- +4.5V  $\leq$  V<sub>DD</sub>  $\leq$  +5.5V (Z80382 versions)

- +3.0V  $\leq$  V<sub>DD</sub>  $\leq$  +3.6V (Z8L382 versions)

All AC parameters assume a load capacitance of 50 pF. Add 10 ns delay for each 50 pF increase in load up to a maximum of 150 pF for the data bus and 100 pF for address and control lines. AC timing measurements are referenced to 1.5 volts (except for clock, which is referenced to the 10% and 90% points). Maximum capacitive load for PHI is 125 pF.

Figure 3. Test Load Diagram

## **DC Characteristics**

Pin Numbers and Input/Output Classifications

Table 1. Pin Numbers and Input/Output Classifications

| Pin             | Input Class <sup>1</sup> | Output Class <sup>1</sup> | Pin Number(s) |

|-----------------|--------------------------|---------------------------|---------------|

| BHEN            |                          | 0                         | 118           |

| BLEN            |                          | 0                         | 119           |

| BUSACK          |                          | 0                         | 132           |

| BUSREQ          | I                        |                           | 133           |

| CTS0/HRD/PCIORD | I                        |                           | 61            |

| CTS0/TREFA      | I                        | 0                         | 111           |

| CTS1/HWR/PCIOWR | I                        |                           | 60            |

| CTS1/TREFC      | I                        | 0                         | 110           |

| DCD0/HDAK0/PCWE | I                        |                           | 89            |

| DCD0/TREFR      | I                        | 0                         | 112           |

| DCD1/HA9        | I                        |                           | 66            |

| HALT            |                          | 0                         | 121           |

Table 1. Pin Numbers and Input/Output Classifications (Continued)

| Pin                | Input Class <sup>1</sup> | Output Class <sup>1</sup> | Pin Number(s)                        |

|--------------------|--------------------------|---------------------------|--------------------------------------|

| ĪNT0-3             | R                        |                           | 136 - 139                            |

| ĪORD               | ļ                        | 3                         | 125                                  |

| ĪORQ               | I                        | 3                         | 115                                  |

| ĪOWR               | I                        | 3                         | 123                                  |

| M1                 |                          | 3                         | 116                                  |

| MRD                | I                        | 3                         | 126                                  |

| MSIZE              | I                        | D                         | 117                                  |

| MWR                | I                        | 3                         | 124                                  |

| NMI                | R                        |                           | 135                                  |

| RAMCSL             |                          | 0                         | 43                                   |

| RESET              | R                        | D                         | 134                                  |

| ROMCS              | 0                        |                           | 42                                   |

| RTS0/HINT2/STSCHG  |                          | Н                         | 88                                   |

| STNBY              |                          | 0                         | 120                                  |

| TXEN1-0/RTS1-0     |                          | 0                         | 94 -93                               |

| WAIT               | I                        | D                         | 130                                  |

| A23-0              | I                        | 3                         | 141 - 144, 1 - 4, 6 - 13,<br>15 - 22 |

| BUSCLK             |                          | Н                         | 127                                  |

| CKA0/HDRQ1/PCRESET |                          | Н                         | 92                                   |

| CKA1/HA10          |                          | 3                         | 65                                   |

| CKS/HA11           |                          | 3                         | 64                                   |

| CLKI               | R                        |                           | 128                                  |

| CLKO               |                          | 0                         | 129                                  |

| D15-0              | I                        | 3                         | 24 - 31, 33 - 40                     |

| DCL/RXC2/BCL2      | I                        |                           | 106                                  |

| DD/TXD2            | I                        | D (DD)<br>O (TXD2)        | 107                                  |

| DU/TXC2/FSC2       | I                        | D (DU)<br>O (TXC2, FSC2)  | 105                                  |

| FSC/RXD2           | 1                        |                           | 108                                  |

Table 1. Pin Numbers and Input/Output Classifications (Continued)

| Pin                  | Input Class <sup>1</sup> | Output Class <sup>1</sup> | Pin Number(s) |

|----------------------|--------------------------|---------------------------|---------------|

| IOCLK                | I                        | 0                         | 114           |

| PA7-0/HD7-0          | I                        | Н                         | 78 -85        |

| PB0/CKS              | ļ                        | 3                         | 58            |

| PB1/RXS              | i                        | 3                         | 57            |

| PB2/TXS              |                          | 3                         | 56            |

| PB3/RXA1             |                          | 3                         | 55            |

| PB4/TXA1             |                          | 3                         | 54            |

| PB5/CKA0             |                          | 3                         | 53            |

| PB6/RXA0             |                          | 3                         | 52            |

| PB7/TXA0             | I                        | 3                         | 51            |

| PC2/TXEN2/TOUT       |                          | 3                         | 109           |

| PC3/CKA1             |                          | 3                         | 49            |

| PC4/IEO              |                          | 3                         | 48            |

| PC5/IEI              |                          | 3                         | 47            |

| PC6/IOCS1            |                          | 3                         | 45            |

| PC7/RAMCSH           |                          | 3                         | 44            |

| PD7-0/HA7-0          |                          | 3                         | 69 - 76       |

| RXA0/HDAK1/PCOE      |                          | D                         | 90            |

| RXA1/HA8             |                          | 3                         | 67            |

| RXC1-0/BCL1-0/PC1-0  |                          | 3                         | 101, 97       |

| RXD1-0/RXA1-0        |                          | 0                         | 103, 99       |

| RXS/HAEN/PCREG       |                          | D                         | 63            |

| TOUT/IOCS2           |                          | 3                         | 46            |

| TXA0/HDRQ0/PCCE1     | I                        | Н                         | 91            |

| TXA1/HINT1/PCIRQ     |                          | Н                         | 87            |

| TXC1-0/FSC1-0/CKA1-0 | I                        | 3                         | 100, 96       |

| TXD1-0/TXA1-0        |                          | 0                         | 102, 98       |

| TXS/HDOEN/INPACK     |                          | 0                         | 62            |

Table 1. Pin Numbers and Input/Output Classifications (Continued)

| Pin             | Input Class <sup>1</sup> | Output Class <sup>1</sup> | Pin Number(s)                        |

|-----------------|--------------------------|---------------------------|--------------------------------------|

| $V_{DD}$        |                          |                           | 5, 23, 41, 59, 77, 95, 113,<br>131   |

| V <sub>SS</sub> |                          |                           | 14, 32, 50, 68, 86, 104,<br>122, 140 |

Note: 1. Characteristics of each pin are listed in terms of the classifications in the DC Characteristics Table 2 and Table 3 which follow.

Specifications apply over Standard Operating Conditions unless otherwise noted.

**Table 2. Output Class Characteristics**

| Output<br>Class <sup>(1)</sup> | Туре                  | V <sub>OL</sub> Max.                                        | V <sub>OH</sub> Min.                                      | C <sub>OUT</sub><br>Max. <sup>(2)</sup> |

|--------------------------------|-----------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------|

| 0                              | Totem Pole            | 0.4V @ I <sub>OL</sub> = 2.0 mA                             | V <sub>DD</sub> - 1.2V @ I <sub>OH</sub> = 200 μA         | 15 pF                                   |

|                                |                       | Slew Rate = 0.33 V/ns min @                                 | © C <sub>LOAD</sub> = 50 pF                               |                                         |

| 3                              | 3-State               | 0.4V @ I <sub>OL</sub> = 2.0 ma                             | V <sub>DD</sub> - 1.2V @ I <sub>OH</sub> = 200 μA         |                                         |

|                                |                       | Slew Rate = 0.33 V/ns min @                                 | © C <sub>LOAD</sub> = 50 pF                               |                                         |

| Н                              | High Drive<br>3-State | 0.4V max @ I <sub>OL</sub> = 16 mA,<br>V <sub>DD</sub> = 5V | 2.4V min @ I <sub>OH</sub> = 5mA,<br>V <sub>DD</sub> = 5V | 15 pF                                   |

|                                |                       | Slew Rate = 0.33 V/ns min @                                 | © C <sub>LOAD</sub> = 50 pF                               |                                         |

| D                              | Open-Drain            | 0.4V max @ I <sub>OL</sub> = 16 mA                          |                                                           | 15 pF                                   |

#### Notes:

<sup>1.</sup> The Pin Numbers and Input/Output Classifications described in Table 1 identifies the specific output pins in each

<sup>2.</sup> Applies to Output only or I/O.

**Table 3. Input Class Characteristics**

| Input                | V <sub>IL</sub> Max. | V <sub>IL</sub> Max. | V <sub>IH</sub> Min. | V <sub>IH</sub> Min. | Minimum    |

|----------------------|----------------------|----------------------|----------------------|----------------------|------------|

| Class <sup>(1)</sup> | (Z80382)             | (Z8L382)             | (Z80382)             | (Z8L382)             | Hysteresis |

| I                    | 0.8V                 | 0.6V                 | 2.0V                 | 2.0V                 | 0.4V       |

$I_{\parallel}$  = ±10 µA max,  $V_{\parallel}$  = 0 to 5V (includes leakage if I/O)  $C_{\parallel N}$  = 5 pF max (if input only, see output type if I/O)

Note: Inputs of this type include a weak-latch circuit, except that a register bit can disable those for pins PB7-0

R 0.4V 0.4V

$$V_{DD}$$

- 0.6V  $V_{DD}$  - 0.3V 0.4V

$$I_{\parallel} = \pm 10 \; \mu A \; max, \; V_{\parallel} = 0 \; to \; 5V$$

$$C_{\parallel N} = 5 \; pF \; max$$

Note: Inputs of this type except CLKI include a weak-latch circuit.

Note: The Pin Numbers and Input/Output Classifications described in Table 1 identifies the specific input pins in each class.

**Table 4. DC Electrical Characteristics**

| Symbol           | Item                                                                 | Condition                                      | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------------------|------------------------------------------------|------|------|------|------|

| V <sub>IH</sub>  | Input High Voltage                                                   | See Table 3                                    |      |      |      | V    |

| $V_{IL}$         | Input Low Voltage                                                    | See Table 3                                    |      |      |      | V    |

| V <sub>OH</sub>  | Output High Voltage                                                  | See Table 2                                    |      |      |      | V    |

| V <sub>OL</sub>  | Output Low Voltage                                                   | See Table 2                                    |      |      |      | V    |

| I <sub>IL</sub>  | Input Leakage<br>Current, All Inputs<br>Except CLKI, CLKO            | $V_{IN} = 0.5V \text{ to} $<br>$V_{DD} - 0.5V$ |      |      | 1.0  | μА   |

| I <sub>TL</sub>  | Tristate Leakage<br>Current                                          | $V_{IN} = 0.5 \text{ to}$<br>$V_{DD} - 0.5$    |      |      | 1.0  | μΑ   |

| I <sub>DD</sub>  | V <sub>DD</sub> Supply Current <sup>(1, 3)</sup><br>Normal Operation | BUSCLK = 10 MHz<br>V <sub>DD</sub> = 3.3V      |      |      | 75   | mA   |

|                  |                                                                      | BUSCLK = 10 MHz<br>V <sub>DD</sub> = 5V        |      |      | 90   | mA   |

|                  |                                                                      | BUSCLK = 20 MHz<br>V <sub>DD</sub> = 5V        |      |      | 150  | mA   |

| I <sub>DDS</sub> | V <sub>DD</sub> Supply Current<br>Standby Mode <sup>(1, 2, 3)</sup>  | BUSCLK = 10 MHz<br>V <sub>DD</sub> = 3.3V      |      |      | 50   | μΑ   |

|                  |                                                                      | BUSCLK = 10 MHz<br>V <sub>DD</sub> = 5V        |      |      | 50   | μΑ   |

|                  |                                                                      | BUSCLK = 20 MHz<br>V <sub>DD</sub> = 5V        |      |      | 50   | μΑ   |

- 1.  $V_{IH}$  min =  $V_{DD}$ -1.0V,  $V_{IL}$  max = 0.8V. All output terminals are at no load. 2. On-chip peripherals with independent clocks are inactive (not being clocked).

- 3. BUSCLK is the internal processor clock frequency.

### **AC Characteristics**

### 380C Processor Timing (See Figure 4.)

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L$  = 50 pF for outputs.

**Table 5. AC Characteristics**

|        |                                          | Z80  | 382  | Z8L  | .382 |      |

|--------|------------------------------------------|------|------|------|------|------|

| Symbol | Parameter                                | Min. | Max. | Min. | Max. | Unit |

| t1     | Clock Cycle Time <sup>1</sup>            | 25   | DC   | 50   | DC   | ns   |

| t2     | Clock High Time <sup>1</sup>             | 10   |      | 20   |      | ns   |

| t3     | Clock Low Time <sup>1</sup>              | 10   |      | 20   |      | ns   |

| t4     | Clock Rise Time <sup>1</sup>             |      | 3    |      | 5    | ns   |

| t5     | Clock Fall Time <sup>1</sup>             |      | 3    |      | 5    | ns   |

| t6     | CLKI Low to BUSCLK High Delay            |      | 25   |      | 35   | ns   |

| t7     | CLKI High to BUSCLK Low Delay            |      | 25   |      | 35   | ns   |

| t8     | BUSCLK High to Output Valid <sup>2</sup> |      | 10   |      | 10   | ns   |

| t9     | BUSCLK Low to Output Valid <sup>3</sup>  |      | 10   |      | 10   | ns   |

| t10    | Input Setup to BUSCLK Rise <sup>4</sup>  | 10   |      | 15   |      | ns   |

| t11    | Input Hold from BUSCLK High <sup>4</sup> | 0    |      | 0    |      | ns   |

| t12    | BUSREQ Setup to BUSCLK Fall <sup>5</sup> | 10   |      | 15   |      | ns   |

| t13    | BUSREQ Hold from BUSCLK Low <sup>5</sup> | 0    |      | 0    |      | ns   |

| t14    | WAIT Setup to BUSCLK Rise <sup>6</sup>   | 10   |      | 15   |      | ns   |

| t15    | WAIT Hold from BUSCLK High <sup>6</sup>  | 0    |      | 0    |      | ns   |

| t16    | WAIT Setup to BUSCLK Fall <sup>6</sup>   | 15   |      | 15   |      | ns   |

| t17    | WAIT Hold from BUSCLK Low <sup>6</sup>   | 0    |      | 0    |      | ns   |

| t18    | NMI Width Low                            | 15   |      | 15   |      | ns   |

| t19    | RESET Width Low                          | 10   |      | 10   |      | t1   |

| t20    | ĪNT1, ĪNT2, ĪNT3 Low Width <sup>7</sup>  | 15   |      | 15   |      | ns   |

| t21    | INT1, INT2, INT3 High Width <sup>7</sup> | 15   |      | 15   |      | ns   |

15

#### Table 5. AC Characteristics (Continued)

|                  | Z80  | Z80382 |      | Z8L382 |      |

|------------------|------|--------|------|--------|------|

| Symbol Parameter | Min. | Max.   | Min. | Max.   | Unit |

#### Notes:

- 1. Applies to the oscillator or external clock input. The maximum internal clock frequency (BUSCLK) is limited to 20 MHz for the Z80382 and 10 MHz for the Z8L382. Input clock frequencies greater than these values must use the CLKI/2 mode for creating BUSCLK. This is the default state after Reset.

- 2. Applies to A23-0, BHEN, BLEN, IOCLK, IOCS1, IOCS2, ROMCS, RAMCSL, RAMCSH, M1, BUSACK, MRD, MWR, TREFA, TREFC, TREFR

3. Applies to D15-0, HALT, STNBY, IORQ, IORD, IOWR, MSIZE, BUSACK, MRD, MWR, TREFC, TREFR

- 4. Applicable for Data Bus and MSIZE inputs.

- 5. BUSREQ can also be asserted/deasserted asynchronously.

- 6. External waits asserted at WAIT input.

- 7. In edge-triggered mode.

Figure 4. 380C Processor Timing Diagram

#### **Host-PCMCIA Attribute Memory Read Timing (See Figure 5)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

Table 6. Host-PCMCIA Attribute Memory Read Timing

|               |                                                          | Z80382     |          | Z8L  | .382 |      |

|---------------|----------------------------------------------------------|------------|----------|------|------|------|

| Symbol        | Parameter                                                | Min.       | Max.     | Min. | Max. | Unit |

| t22           | Address Setup to PCCE1 Fall                              | 15         |          | 20   |      | ns   |

| t23           | Address Setup to PCOE Fall                               | 15         |          | 20   |      | ns   |

| t24           | Address Hold from PCCE1 High                             | 5          |          | 5    |      | ns   |

| t25           | Address Hold from PCOE High                              | 5          |          | 5    |      | ns   |

| t26           | PCCE1 Low to Data Active                                 | 0          |          | 0    |      | ns   |

| t27           | PCOE Low to Data Active                                  | 0          |          | 0    |      | ns   |

| t28           | PCCE1 Low to Data Valid                                  |            | 60       |      | 60   | ns   |

| t29           | PCOE Low to Data Valid                                   |            | 60       |      | 60   | ns   |

| t30           | Data Invalid from PCCE1 High                             | 5          |          | 5    |      | ns   |

| t31           | Data Invalid from PCOE High                              | 5          |          | 5    |      | ns   |

| t32           | Data 3-state from PCCE1 High                             |            | 20       |      | 20   | ns   |

| t33           | Data 3-state from PCOE High                              |            | 20       |      | 20   | ns   |

| Note: Timings | also apply for reads from registers located in the attri | bute memor | y space. |      |      |      |

18

Figure 5. Host - PCMCIA Attribute Memory Read Timing Diagram

#### **Host-PCMCIA Attribute Memory Write Timing (See Figure 6.)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

Table 7. Host-PCMCIA Attribute Memory Write Timing

|        |                              | Z80  | Z80382 |      | Z8L382 |      |

|--------|------------------------------|------|--------|------|--------|------|

| Symbol | Parameter                    | Min. | Max.   | Min. | Max.   | Unit |

| t34    | Address Setup to PCCE1 Fall  | 30   |        | 35   |        | ns   |

| t35    | Address Setup to PCWE Fall   | 30   |        | 35   |        | ns   |

| t36    | Address Hold from PCCE1 High | 10   |        | 10   |        | ns   |

| t37    | Address Hold from PCWE High  | 10   |        | 10   |        | ns   |

| t38    | Data Setup to PCCE1 Rise     | 20   |        | 20   |        | ns   |

| t39    | Data Setup to PCWE Rise      | 20   |        | 20   |        | ns   |

| t40    | Data Hold from PCCE1 High    | 10   |        | 10   |        | ns   |

| t41    | Data Hold from PCWE High     | 10   |        | 10   |        | ns   |

PCREG

PCCE1

PCWE

HD7-0

Figure 6. Host - PCMCIA Attribute Memory Write Timing Diagram

#### Host-PCMCIA I/O Read Timing (See Figure 7)

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

Table 8. Host-PCMCIA I/O Read

|        |                               | Z80382 |      | Z8L382 |      |       |  |

|--------|-------------------------------|--------|------|--------|------|-------|--|

| Symbol | Parameter                     | Min.   | Max. | Min.   | Max. | Units |  |

| t42    | Address Setup to PCIORD Fall  | 50     |      | 50     |      | ns    |  |

| t43    | PCREG Setup to PCIORD Fall    | 5      |      | 5      |      | ns    |  |

| t44    | PCCE1 Setup to PCIORD Fall    | 5      |      | 5      |      | ns    |  |

| t45    | PCIORD Low Width              | 125    |      | 125    |      | ns    |  |

| t46    | INPACK Low from PCIORD Low    |        | 10   |        | 10   | ns    |  |

| t47    | Data Valid from PCIORD Low    |        | 50   |        | 50   | ns    |  |

| t48    | Data Invalid from PCIORD High | 5      |      | 5      |      | ns    |  |

| t49    | INPACK High from PCIORD High  |        | 10   |        | 10   | ns    |  |

| t50    | PCCE1 Hold from PCIORD High   | 10     |      | 10     |      | ns    |  |

| t51    | PCREG Hold from PCIORD High   | 10     |      | 10     |      | ns    |  |

| t52    | Address Hold from PCIORD High | 10     |      | 10     |      | ns    |  |

| t53    | PCIORD Low to Data Active     | 0      |      | 0      |      | ns    |  |

| t54    | Data 3-state from PCIORD High |        | 20   |        | 20   | ns    |  |

Figure 7. Host - PCMCIA I/O Read Timing Diagram

#### Host-PCMCIA I/O Write Timing (See Figure 8)

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF for outputs.}$

Table 9. Host-PCMCIA I/O Write Timing

|        |                               | Z80382 |      | Z8L382 |      |       |

|--------|-------------------------------|--------|------|--------|------|-------|

| Symbol | Parameter                     | Min.   | Max. | Min.   | Max. | Units |

| t55    | Address Setup to PCIOWR Fall  | 50     |      | 50     |      | ns    |

| t56    | PCREG Setup to PCIOWR Fall    | 5      |      | 5      |      | ns    |

| t57    | PCCE1 Setup to PCIOWR Fall    | 5      |      | 5      |      | ns    |

| t58    | PCIOWR Low Width              | 125    |      | 125    |      | ns    |

| t59    | Data Setup to PCIOWR Rise     | 35     |      | 35     |      | ns    |

| t60    | Data Hold from PCIOWR High    | 20     |      | 20     |      | ns    |

| t61    | PCCE1 Hold from PCIOWR High   | 10     |      | 10     |      | ns    |

| t62    | PCREG Hold from PCIOWR High   | 10     |      | 10     |      | ns    |

| t63    | Address Hold from PCIOWR High | 10     |      | 10     |      | ns    |

Figure 8. Host - PCMCIA I/O Write Timing Diagram

#### **Timer Output Timing (See Figure 9)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF for outputs.}$

**Table 10. Timer Output Timing**

|        |                          | Z80382 |      | Z8L  | .382 |       |

|--------|--------------------------|--------|------|------|------|-------|

| Symbol | Parameter                | Min.   | Max. | Min. | Max. | Units |

| t64    | BUSCLK Low to TOUT Valid |        | 20   |      | 20   | ns    |

Figure 9. Timer Output Timing Diagram

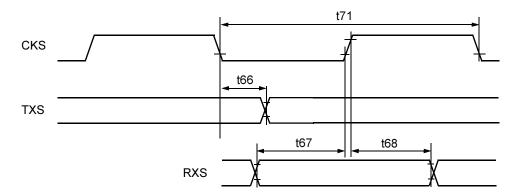

#### **CSIO Receive/Transmit Timing (See Figure 10)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

Table 11. CSIO Receive/Transmit Timing

|        |                           | Z80382 |      | Z8L382 |      |       |  |

|--------|---------------------------|--------|------|--------|------|-------|--|

| Symbol | Parameter                 | Min.   | Max. | Min.   | Max. | Units |  |

| t66    | CKS Low to TXS Valid      |        | 40   |        | 40   | ns    |  |

| t67    | RXS Setup to CKS Rise     | 20     |      | 20     |      | ns    |  |

| t68    | RXS Hold from CKS High    | 5      |      | 5      |      | ns    |  |

| t71    | CKS External Clock Period | 50     |      | 50     |      | ns    |  |

Figure 10. CSIO Receive/Transmit Timing Diagram

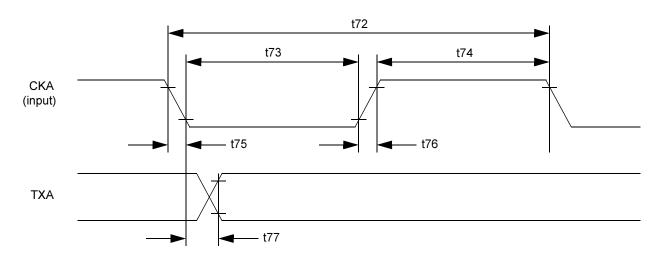

#### **ASCI Transmitter Timing (See Figure 11)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

**Table 12. ASCI Transmitter Timing**

|        |                                    | Z80382 |      | Z8L382 |      |       |  |

|--------|------------------------------------|--------|------|--------|------|-------|--|

| Symbol | Parameter                          | Min.   | Max. | Min.   | Max. | Units |  |

| t72    | External Transmit Clock Period     | 50     |      | 50     |      | ns    |  |

| t73    | External Transmit Clock Low Width  | 30     |      | 30     |      | ns    |  |

| t74    | External Transmit Clock High Width | 30     |      | 30     |      | ns    |  |

| t75    | External Transmit Clock Fall Time  |        | 5    |        | 10   | ns    |  |

| t76    | External Transmit Clock Rise Time  |        | 5    |        | 10   | ns    |  |

| t77    | CKA Low to TXA Data Valid          |        | 20   |        | 30   | ns    |  |

Figure 11. ASCI Transmitter Timing Diagram

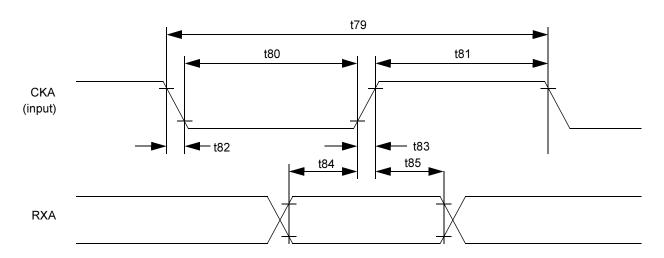

# **ASCI Receiver Timing (See Figure 12)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

Table 13. ASCI Receiver Timing

|        |                                  | Z80382 |      | Z8L382 |      |       |  |

|--------|----------------------------------|--------|------|--------|------|-------|--|

| Symbol | Parameter                        | Min.   | Max. | Min.   | Max. | Units |  |

| t79    | External Receive Clock Period    | 50     |      | 50     |      | ns    |  |

| t80    | External Receive Clock Low Time  | 30 30  |      |        |      | ns    |  |

| t81    | External Receive Clock High Time | 30     |      | 30     |      | ns    |  |

| t82    | External Receive Clock Fall Time |        | 5    |        | 10   | ns    |  |

| t83    | External Receive Clock Rise Time |        | 5    |        | 10   | ns    |  |

| t84    | RXA Setup to CKA Rise            | 20     |      | 25     |      | ns    |  |

| t85    | RXA Hold from CKA High           | 5      |      | 5      |      | ns    |  |

Figure 12. ASCI Receiver Timing Diagram

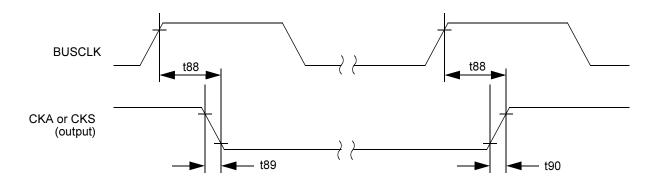

# ASCI/CSIO Timing-Baud Rate Generator, CTSA, DCDA, and RTSA Timing (See Figures 13 through 15)

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_1 = 50 \text{ pF}$  for outputs.

Table 14. ASCI/CSIO Timing

|        | Parameter                       | Z80     | Z80382 |      | Z8L382 |       |

|--------|---------------------------------|---------|--------|------|--------|-------|

| Symbol |                                 | Min.    | Max.   | Min. | Max.   | Units |

| t88    | BUSCLK High to BRG Output Delay |         | 30     |      | 40     | ns    |

| t89    | BRG Output Fall Time            | 10      |        |      | 15     | ns    |

| t90    | BRG Output Rise Time            |         | 10     |      | 15     | ns    |

| t91    | CTS Low Time                    | 100     |        | 100  |        | ns    |

| t92    | CTS High Time                   | 100     |        | 100  |        | ns    |

| t93    | DCD Low Time                    | 100 100 |        |      | ns     |       |

| t94    | DCD High Time                   | 100     |        | 100  |        | ns    |

| t95    | BUSCLK Low to RTS Valid         |         | 20     |      | 20     | ns    |

Figure 13. Baud Rate Generator Timing Diagram

Figure 14. CTSA and DCDA Timing Diagram

Figure 15. RTSA Timing Diagram

# **General-Purpose I/O Port Timing. (See Figure 16)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

Table 15. General-Purpose I/O Port Timing

|        |                                    | Z80382 |      | Z8L382 |      |       |  |

|--------|------------------------------------|--------|------|--------|------|-------|--|

| Symbol | Parameter                          | Min.   | Max. | Min.   | Max. | Units |  |

| t100   | I/O Port Data Setup to IORD Fall   | 10     |      | 10     |      | ns    |  |

| t101   | I/O Port Data Hold from IORD High  | 5      |      | 5      |      | ns    |  |

| t102   | I/O Port Data Valid from IOWR High |        | 20   |        | 20   | ns    |  |

Figure 16. General-Purpose I/O Port Timing Diagram

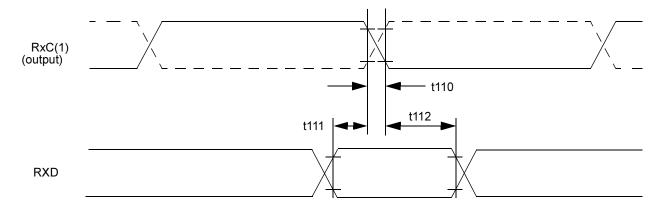

# HDLC Receive Timing- Full Time HDLC Mode (See Figures 17 and 18)

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs.

Table 16. HDLC Receive Timing

|      |                                                        | Z80382 |      | Z8L382 |      |       |  |

|------|--------------------------------------------------------|--------|------|--------|------|-------|--|

| No   | Parameter                                              | Min.   | Max. | Min.   | Max. | Units |  |

| t103 | External Receive Clock Period <sup>1</sup>             | 50     |      | 50     |      | ns    |  |

| t104 | External Receive Clock Low Time                        | 15     |      | 15     |      | ns    |  |

| t105 | External Receive Clock High Time                       | 15     |      | 15     |      | ns    |  |

| t106 | External Receive Clock Rise Time                       |        | 5    |        | 10   | ns    |  |

| t107 | External Receive Clock Fall Time                       |        | 5    |        | 10   | ns    |  |

| t108 | RxD Setup to RxC Edge (External RxC) <sup>1</sup>      | 20 20  |      |        | ns   |       |  |

| t109 | RxD Hold from RxC Low/High (External RxC) <sup>1</sup> | 5 5    |      |        | ns   |       |  |

| t110 | RxC rise/fall time (Internal RxC) <sup>1</sup>         |        | 5    |        | 10   | ns    |  |

| t111 | RxD Setup to RxC Edge (Internal RxC) <sup>1</sup>      | 20     |      | 25     |      | ns    |  |

| t112 | RxD Hold from RxC Low/High (Internal RxC) <sup>1</sup> | 5      |      | 10     |      | ns    |  |

Note: 1. Receive clock sampling edge is configurable by means of RIRn[6]. See Z80382 User Manual.

Note 1. HDLC clock triggering polarity is configurable by means of RIRn[6]. See Z80382 User Manual.

Figure 17. HDLC Receive Timing Diagram (Full Time HDLC, RxC Input)

Note 1. Receive clock sampling edge is configurable by means of RIRn[6]. See Z80382 User Manual.

Figure 18. HDLC Receive Timing (Full Time HDLC, RxC Output)

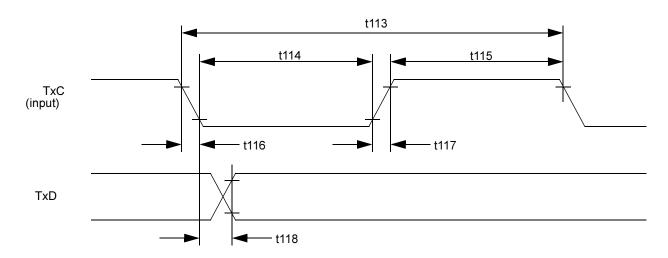

# **HDLC Transmit Timing- Full Time HDLC Mode (See Figure 19)**

Table 17. HDLC Transmit Timing

|        |                                             | Z80  | Z80382 |      | Z8L382 |       |

|--------|---------------------------------------------|------|--------|------|--------|-------|

| Symbol | Parameter                                   | Min. | Max.   | Min. | Max.   | Units |

| t113   | External Transmit Clock Period <sup>1</sup> | 50   |        | 50   |        | ns    |

| t114   | External Transmit Clock High Time           | 15   |        | 15   |        | ns    |

| t115   | External Transmit Clock Low Time            | 15   |        | 15   |        | ns    |

| t116   | External Transmit Clock Fall Time           |      | 5      |      | 10     | ns    |

| t117   | External Transmit Clock Rise Time           |      | 5      |      | 10     | ns    |

| t118   | TxC Low to TxD Data Valid                   |      | 20     |      | 25     | ns    |

Figure 19. HDLC Transmit Timing Diagram (Full Time HDLC)

34

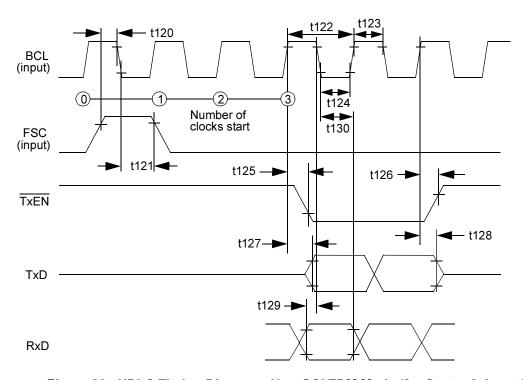

# HDLC Timing - Non-GCI TDM mode (See Figure 20)

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs

Table 18. HDLC Timing - Non-GCI TDM Mode

|             |                                                                                                   | Z80   | Z80382 |      | Z8L382 |       |  |

|-------------|---------------------------------------------------------------------------------------------------|-------|--------|------|--------|-------|--|

| Symbol      | Parameter                                                                                         | Min.  | Max.   | Min. | Max.   | Units |  |

| t120        | FSC Setup to BCL Fall                                                                             | 30    |        | 50   |        | ns    |  |

| t121        | FSC Hold from BCL Low                                                                             | 20    |        | 30   |        | ns    |  |

| t122        | BCL Period                                                                                        | 50    | 50 50  |      |        | ns    |  |

| t123        | BCL High Time                                                                                     | 15 15 |        |      | ns     |       |  |

| t124        | BCL Low Time                                                                                      | 15 15 |        |      | ns     |       |  |

| t125        | BCL High to TxEN Low                                                                              |       | 15     |      | 20     | ns    |  |

| t126        | BCL High to TxEN High                                                                             |       | 15     |      | 20     | ns    |  |

| t127        | BCL High to TxD Valid                                                                             |       | 15     |      | 20     | ns    |  |

| t128        | BCL High to TxD Invalid                                                                           | 15    |        | 20   |        | ns    |  |

| t129        | RxD Setup to BCL Fall (Rise) <sup>1</sup>                                                         | 15 20 |        | ns   |        |       |  |

| t130        | RxD Hold from BCL Low (High) <sup>1</sup>                                                         | 5     |        | 5    |        | ns    |  |

| Note: 1. Re | Note: 1. Receive clock sampling edge is configurable by means of RIRn[6]. See Z80382 User Manual. |       |        |      |        |       |  |

Figure 20. HDLC Timing Diagram - Non-GCI TDM Mode (for Start = 3, Length = 2, Negative Edge RxD Sampling

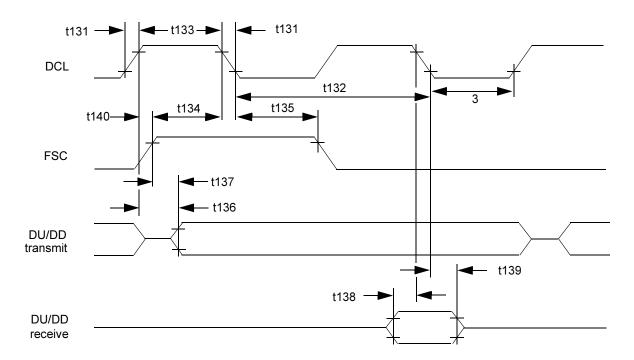

# **GCI/SCIT Timing-Slave Characteristics (See Figure 21)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_1 = 50 \text{ pF}$  for outputs.

Table 19. GCI/SCIT Timing - Slave Characteristics

|        | _                                     | Z80382 |      | Z8L382 |      |       |

|--------|---------------------------------------|--------|------|--------|------|-------|

| Symbol | Parameter                             | Min.   | Max. | Min.   | Max. | Units |

| t131   | DCL Data Clock Rise/Fall Time         |        | 5    |        | 10   | ns    |

| t132   | DCL Clock Period                      | 50     |      | 50     |      | ns    |

| t133   | DCL Pulse Width High                  | 15 15  |      |        |      | ns    |

| t134   | FSC Setup to DCL Fall                 | 30     |      | 30     |      | ns    |

| t135   | FSC Hold from DCL Low                 | 5      |      | 10     |      | ns    |

| t136   | DCL High to DU/DD Transmit Data Valid |        | 15   |        | 20   | ns    |

Table 19. GCI/SCIT Timing - Slave Characteristics (Continued)

|        |                                         | Z80382 |      | Z8L382 |      |       |  |

|--------|-----------------------------------------|--------|------|--------|------|-------|--|

| Symbol | Parameter                               | Min.   | Max. | Min.   | Max. | Units |  |

| t137   | FSC High to DU/DD Transmit Data Valid   |        | 15   |        | 20   | ns    |  |

| t138   | DU/DD Receive Data Setup to DCL Fall    | 15     |      | 20     |      |       |  |

| t139   | DU/DD Receive Data Hold from DCL<br>Low | 0      |      | 0      |      | ns    |  |

# **GCI/SCIT Timing - Master Characteristics (See Figure 21)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF for outputs.}$

Table 20. GCI/SCIT Timing - Master Characteristics

|        | _                                       | Z80382 |      | Z8L382 |      | <u></u> |

|--------|-----------------------------------------|--------|------|--------|------|---------|

| Symbol | Parameter                               | Min.   | Max. | Min.   | Max. | Units   |

| t131   | DCL Data Clock Rise/Fall Time           |        | 5    |        | 10   | ns      |

| t132   | DCL Clock Period                        | 50 50  |      |        |      | ns      |

| t133   | DCL Pulse Width High                    | 15 15  |      |        |      | ns      |

| t134   | FSC Setup to DCL Fall                   | 30 30  |      |        |      | ns      |

| t135   | FSC Hold from DCL Low                   | 5      |      | 10     |      | ns      |

| t136   | DCL High to DU/DD Transmit Data Valid   |        | 15   |        | 20   | ns      |

| t137   | FSC High to DU/DD Transmit Data Valid   |        | 15   |        | 20   | ns      |

| t138   | DU/DD Receive Data Setup to DCL Fall    | 15     | 20   |        |      | ns      |

| t139   | DU/DD Receive Data Hold from DCL<br>Low | 0 0    |      |        | ns   |         |

| t140   | FSC High from DCL High                  | 0 0    |      |        | ns   |         |

Figure 21. GCI/SCIT Slave and Master Timing Diagram

# **Pin Functions**

Tables 21 through 11 describe the input and output signals of the Z382. Signals are normally asserted in the High state and negated in the Low state. An overline ( ) above the signal name indicates that the signal is asserted in the Low state and negated in the High state.

Many pins have multiple functions, and thus may appear more than once in the pin description tables. In each table, such pins are described using their function in that mode. Likewise, some signals may be output on alternate pins depending on the mode under which the Z382 is operating. The notation xx/yy in the Pin Number column indicates that the signal may be assigned to pin xx or pin yy.

Table 21. Multiprocessor Unit (MPU) Signals

| Pin Name | Pin<br>Number(s)                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A23 - 0  | 141 - 144,<br>1 - 4, 6 - 13,<br>15 - 22 | Address Bus (outputs, active High, 3-state): These non-multiplexed address signals provide a linear memory address space of 16 MB. The address signals are also used to access I/O devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BUSACK   | 132                                     | Bus Acknowledge (output, active Low, 3-state): This signal, when asserted, indicates that the 380C has accepted an external bus request and has 3-stated its output drivers for the address bus, databus and the bus control signals TREFR, TREFA, TREFC, BHEN, BLEN, MRD, MWR, IORQ, IORD, and IOWR.  The 380C cannot provide any DRAM refresh transactions while it is in the bus acknowledge state.                                                                                                                                                                                                                                                                                                                                             |

| BHEN     | 118                                     | Byte High Enable (output, active Low, 3-state): This signal is asserted at the beginning of a memory or refresh transaction, to request an operation on D15-8. If software initiates a 16-bit memory operation, but MSIZE is asserted indicating a byte-wide memory, only the data on D7-0 is transferred in the current transaction, and another transaction is performed to transfer the other data byte, also on D7-0. See note in the next paragraph under BLEN pin description.                                                                                                                                                                                                                                                               |

| BLEN     | 119                                     | Byte Low Enable (output, active Low, 3-state): This signal is asserted at the beginning of a memory or refresh transaction, to request an operation on D7-0. If software initiates a 16-bit memory transaction, but MSIZE is asserted indicating a byte-wide memory, only the data on D7-0 is transferred in the current transaction, and another transaction is performed to transfer the other data byte, also on D7-0.  Note: To align Z382 documentation and terminology with historical Z80 and industry practice, the names of the BHEN and BLEN pins, as well as the D15-8 and D7-0 pins, have been swapped on the Z382 compared to the Z380. This fact should be significant only for those using a Z380 Emulator in a Z382-based project. |

| BUSREQ   | 133                                     | Bus Request (input, active Low): When this signal is asserted, an external bus master is requesting control of the bus. BREQ has higher priority than all nonmaskable and maskable interrupt requests.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BUSCLK   | 127                                     | <b>Bus Clock</b> (output, active High, 3-state): This signal is the reference edge for the majority of other signals generated by the 380C. Its frequency may be that of the CLKI pin, or CLKI divided by two or times two.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 21. Multiprocessor Unit (MPU) Signals (Continued)

|                      |                    | . , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name             | Pin<br>Number(s)   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D15-0                | 24 - 31<br>33 - 40 | <b>D15-0 Data Bus</b> (input/output, active High, 3-state): This bidirectional 16-bit data bus is used for data transfer between the 380C and memory or I/O devices. In a memory word transfer, the even-addressed (A0=0) byte is transferred on D7-0, and the odd-addressed (A0=1) byte on D15-8. 8-bit memories should be connected to D7-0, while 8-bit I/O devices should be attached to D15-8 (this difference tends to equalize electrical loading). (See note under BLEN pin description on page 38.)                                                     |

| HALT<br>STNBY        | 121<br>120         | <b>HALT, STANDBY Status</b> (outputs, active Low): These two outputs indicate the status of the Z382 as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      |                    | STNBY HALT Mode H H Normal instruction execution H L HALT instruction L H SLEEP Mode: clock runs but is blocked from most of the chip L L STANDBY Mode: oscillator is stopped                                                                                                                                                                                                                                                                                                                                                                                    |

| INT3<br>INT2<br>INT1 | 139<br>138<br>137  | Interrupt Requests (inputs, active Low): Asynchronous maskable interrupt inputs. Can be selected as low- or high-level sensitive, or as falling- or rising-edge triggered.                                                                                                                                                                                                                                                                                                                                                                                       |

| ĪNT0                 | 136                | Interrupt Request (input, active Low): INT0 is logically ORed (positive-logic ANDed) with the interrupt requests from the on-chip MIMIC, DMAs, and HDLC controllers, to create the processor's INT0 input.                                                                                                                                                                                                                                                                                                                                                       |

| IOCLK                | 114                | Input/Output Clock (output, active High, 3-state): This signal is a program controlled divided-down version of BUSCLK. The division factor can be two, four, six or eight with I/O transactions and interrupt-acknowledge transactions occurring relative to IOCLK. IOCLK can be disabled, in which case BUSCLK is the timing reference for I/O transactions. Note: The INTACK output of the Z380 has been omitted on the Z382 for pinning reasons. A similar signal can be easily obtained by low-active-ANDing (positive-logic ORing) the M1 and IORQ outputs. |

| IORQ                 | 115                | <b>Input/Output Request</b> (output, active Low, 3-state): This signal is active during all I/O read and write transactions and interrupt acknowledge transactions.                                                                                                                                                                                                                                                                                                                                                                                              |

| IORD                 | 125                | Input/Output Read Strobe (output, active Low, 3-state): This signal is used to strobe data from the peripherals during I/O read transactions.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| IOWR                 | 123                | Input/Output Write Strobe (output, active Low, 3-state): This signal is used to strobe data into the peripherals during I/O write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IOCS1<br>IOCS2       | 45<br>46           | <b>Input/Output Chip Select</b> (output, active Low): These outputs may be used to access external I/O devices. The base I/O address and range are programmable.                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 21. Multiprocessor Unit (MPU) Signals (Continued)

| Pin Name | Pin<br>Number(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |