#### I2C Bus/SMBus Repeater

### **Features**

- 2 channel, bidirectional buffer

- I<sup>2</sup>C-bus and SMBus compatible

- Operating supply voltage range of 2.3 V to 3.6 V

- Active HIGH repeater enable input

- Open-drain input/outputs

- Lock-up free operation

- Supports arbitration and clock stretching across the repeater

- Accommodates Standard-mode and Fast-mode I<sup>2</sup>Cbus devices and multiple masters

- Powered-off high-impedance I<sup>2</sup>C-bus pins

- 5.5 V tolerant I<sup>2</sup>C-bus and enable pins

- 0 Hz to 400 kHz clock frequency (the maximum system operating frequency may be less than 400 kHz because of the delays added by the repeater)

- ESD protection exceeds 4KV HBM per JESD22-A114

- Package: MSOP-8, SOIC-8 and DFN2x3-8L

### **Description**

The PI6ULS5V9515A is a CMOS integrated circuit intended for  $I^2C$  bus and SMBus systems applications. The device contains two identical bidirectional opendrain buffer circuits that enable  $I^2C$  and similar bus systems to be extended without degradation of system performance.

The PI6ULS5V9515A enables the system designer to isolate two halves of a bus for both voltage and capacitance, accommodating more I<sup>2</sup>C devices or longer trace length. It also permits extension of the I<sup>2</sup>C-bus by providing bidirectional buffering for both the data (SDA) and the clock (SCL) lines, thus allowing two buses of 400 pF to be connected in an I<sup>2</sup>C application.

The PI6ULS5V9515A has an EN pin to turn the

drivers on and off. This can be used to isolate a badly behaved slave on power-up until after the system power-up reset. It should never change state during an I<sup>2</sup>C-bus operation because disabling during a bus operation will hang the bus and enabling part way through a bus cycle could confuse the I<sup>2</sup>C-bus parts being enabled. The enable pin should only change state when the global bus and the repeater port are in an idle state to prevent system failures.

The output low levels for sides are approximately 0.5 V, but the input voltage of each internal buffer must be 70 mV lower (0.43V) or even more lower. When the output internally is driven low the low is not recognized as a low by the input. This prevents a lockup condition from occurring when the input low condition is released.

Two or more PI6ULS5V9515A devices can't be used in series. The PI6ULS5V9515A design does not allow this configuration. Since there is no direction pin, slightly different valid low-voltage levels are used to avoid lockup conditions between the input and the output of each repeater. A valid low applied at the input of a PI6ULS5V9515A will be propagated as a buffered low with a slightly higher value on the output. When this buffered low is applied to another PI6ULS5V9515A-type device in series, the second device does not recognize it as a valid low and will not propagate it as a buffered low again.

The device contains a power-up control circuit that sets an internal latch to prevent the output circuits from becoming active until Vcc is at a valid level (Vcc = 2.3 V).

As with the standard I<sup>2</sup>C system, pull-up resistors are required to provide the logic-high levels on the buffered bus. The PI6ULS5V9515A has standard open-collector configuration of the I<sup>2</sup>C bus. The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. The device is designed to work with Standard mode and Fast mode I<sup>2</sup>C devices in addition to SMBus devices. Standard mode I<sup>2</sup>C devices only specify 3mA in a generic I<sup>2</sup>C system, where Standard mode devices and multiple masters are possible. Under certain conditions, higher termination currents can be used.

## **Pin Configuration**

**Pin Description**

| Pin No | Name            | Description                       |

|--------|-----------------|-----------------------------------|

| 1      | n.c.            | Not connected                     |

| 2      | SCL0            | serial clock port 0 bus           |

| 3      | SDA0            | serial data port 0 bus            |

| 4      | GND             | supply ground (0 V)               |

| 5      | EN              | active HIGH repeater enable input |

| 6      | SDA1            | serial data port 1 bus            |

| 7      | SCL1            | serial clock port 1 bus           |

| 8      | V <sub>CC</sub> | supply voltage (2.3 V to 3.6 V)   |

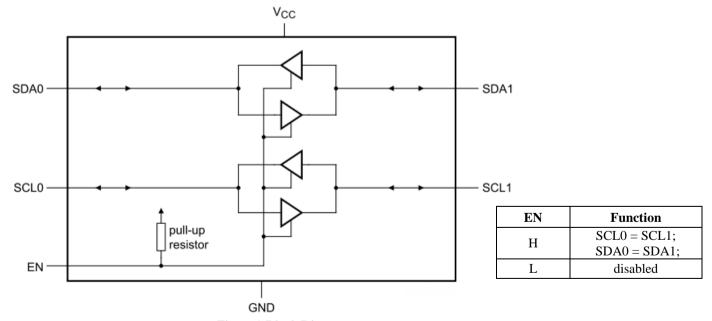

### **Block Diagram**

Figure 1:Block Diagram

### **Maximum Ratings**

| -55°C to +125°C |

|-----------------|

| -0.5V to +6.0V  |

| -0.5V to+6.0V   |

| 100mA           |

| 50mA            |

| 50mA            |

| 4000V           |

|                 |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended operation conditions**

$Vcc = 2.3 \text{ V to } 3.6 \text{ V}; \overline{GND} = 0 \text{ V}; T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}; \text{ unless otherwise specified}$

| Symbo<br>1                                 | Parameter                                                                              | Test Conditions                                                                                 | Min. | Тур. | Max. | Unit |

|--------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| Vcc                                        | supply voltage port                                                                    | -                                                                                               | 2.3  | -    | 3.6  | V    |

| I <sub>CCH</sub> HIGH-level supply current | both channels HIGH;; SDAn = SCLn = $V_{CC}$<br>$V_{CC}$ = 2.7 V                        | -                                                                                               | 0.5  | 5    | mA   |      |

|                                            | current                                                                                | both channels HIGH;; SDAn = SCLn = $V_{CC}$<br>$V_{CC} = 3.6 \text{ V}$                         | -    | 0.5  | 5    | mA   |

| I <sub>CCL</sub> LOW-level supply current  | both channels LOW; $V_{CC} = 2.7$ V; one SDA and one SCL = GND; other SDA and SCL open | -                                                                                               | 1.6  | 5    | mA   |      |

|                                            | current                                                                                | both channels LOW; $V_{CC} = 3.6 \text{ V}$ ; one SDA and one SCL = GND; other SDA and SCL open | -    | 1.7  | 5    | mA   |

| $I_{CCLC}$                                 | contention port A supply current                                                       | $V_{CC} = 2.7V$ or $3.6V$ ; $SDAn = SCLn = GND$                                                 | -    | 1.6  | 5    | mA   |

### **DC Electrical Characteristics**

VCC = 2.7 V to 5.5 V; GND = 0 V; Tamb = -40 °C to +85 °C; unless otherwise specified

| Parameter                                 | Description                                                                | Test Conditions <sup>(1)</sup>                    | Min.        | <b>Typ.</b> <sup>(2)</sup> | Max.    | Unit |  |

|-------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------|-------------|----------------------------|---------|------|--|

| Input and o                               | Input and output SDAn and SCLn                                             |                                                   |             |                            |         |      |  |

| $V_{\mathrm{IH}}$                         | HIGH-level input voltage                                                   | -                                                 | $0.7V_{CC}$ | -                          | 5.5     |      |  |

| $V_{\mathrm{IH}}$ $V_{\mathrm{IL}}^{(1)}$ | LOW-level input voltage                                                    | -                                                 | -0.5        | -                          | +0.3Vcc | V    |  |

| $V_{\rm ILc}$                             | Contention LOW-level input voltage                                         | -                                                 | -0.5        | 0.4                        | -       |      |  |

| $V_{IK}$                                  | Input clamping voltage                                                     | $I_I = -18 \text{ mA}$                            | -           | -                          | -1.2    | V    |  |

| ${ m I_{LI}}$                             | Input leakage current                                                      | $V_{I} = 3.6 \text{ V}$                           | -           | -                          | ±1      | μΑ   |  |

| I <sub>IL</sub> L                         | LOW-level input current                                                    | Vcc=2.3-2.7V;<br>SDA, SCL; V <sub>I</sub> = 0.2 V | -           | -                          | 10      | μΑ   |  |

|                                           |                                                                            | Vcc=3.0-3.6V;<br>SDA, SCL; V <sub>I</sub> = 0.2 V | -           | -                          | 5       | μΑ   |  |

| $V_{OL}$                                  | LOW-level output voltage                                                   | $I_{OL} = 20 \mu A \text{ or } 6 \text{ mA}$      | 0.47        | 0.52                       | 0.6     | V    |  |

| V <sub>OL</sub> -V <sub>ILc</sub>         | Difference between LOW-level output and LOW-level input voltage contention | guaranteed by design                              | -           | 70                         | -       | mV   |  |

| $I_{LOH}$                                 | HIGH-level output leakage current                                          | $V_0 = 3.6 \text{ V}$                             |             |                            | 10      | μΑ   |  |

| Cio                                       | input/output capacitance                                                   | $V_I = 3 \text{ V or } 0 \text{ V}$               | -           | 6                          | -       | pF   |  |

| Enable                                    |                                                                            |                                                   |             |                            |         |      |  |

| $V_{ m IH}$                               | HIGH-level input voltage                                                   | -                                                 | 2.0         | -                          | 5.5     | V    |  |

| $V_{\rm IL}$                              | LOW-level input voltage                                                    | -                                                 | -0.5        | -                          | +0.8    | V    |  |

| $I_{ m IL}$                               | LOW-level input current                                                    | $V_{I} = 0.2 \text{ V}$                           | -           | -10                        | -30     | μΑ   |  |

| $I_{LI}$                                  | Input leakage current                                                      | $V_I = Vcc$                                       | -1          | -                          | +1      | μΑ   |  |

| Ci                                        | Input capacitance                                                          | $V_{I} = 3.0 \text{ V or } 0 \text{ V}$           | -           | 6                          | -       | pF   |  |

**Notes:**

1 V<sub>IL</sub> specification is for the first LOW level seen by the SDAB/SCLB lines. V<sub>IL</sub>c is for the second and subsequent LOW levels seen by the SDAn/SCLn lines.

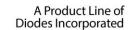

**Dynamic characteristics** GND = 0 V;  $T_{amb} = -40$  °C to +85 °C; unless otherwise specified. (1)(2)

| Symbol           | Parameter                     | Test Conditions | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------|-----------------|------|------|------|------|

| Vcc=2.3-2.7      | Vcc=2.3-2.7V                  |                 |      |      |      |      |

| t <sub>PLH</sub> | LOW-to-HIGH propagation delay | -               | 33   | 113  | 190  | ns   |

| t <sub>PHL</sub> | HIGH-to-LOW propagation delay | -               |      | 82   | 130  | ns   |

| $t_{TLH}$        | LOW-to-HIGH transition time   | -               | -    | 148  | -    | ns   |

| $t_{ m THL}$     | HIGH-to-LOW transition time   | -               | -    | 57   | -    | ns   |

| $t_{ m SU}$      | Set-up time                   | -               | 100  | -    | -    | ns   |

| t <sub>H</sub>   | Hold time                     | -               | 130  | -    | -    | ns   |

| Vcc=3.0-3.6V     |                               |                 |      |      |      |      |

| t <sub>PLH</sub> | LOW-to-HIGH propagation delay | -               | 33   | 102  | 180  | ns   |

| t <sub>PHL</sub> | HIGH-to-LOW propagation delay | -               |      | 68   | 120  | ns   |

| t <sub>TLH</sub> | LOW-to-HIGH transition time   | -               | -    | 147  | -    | ns   |

| t <sub>THL</sub> | HIGH-to-LOW transition time   | -               | -    | 58   | -    | ns   |

| $t_{ m SU}$      | Set-up time                   | -               | 100  | -    | -    | ns   |

| t <sub>H</sub>   | Hold time                     | -               | 100  | -    | -    | ns   |

#### Notes:

- (1) Typical values taken at VCC = 3.3 V and Tamb =  $25^{\circ}\text{C}$ .

- (2) Different load resistance and capacitance will alter the RC time constant, thereby changing the propagation delay and transition times.

Figure 2: Propagation Delay and Transition Times

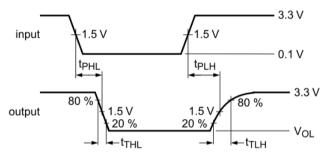

$R_L$  = load resistor; 1.35 k $\Omega$

C<sub>L</sub> = load capacitance includes jig and probe capacitance; 50 pF

$R_T$  = termination resistance should be equal to  $Z_o$  of pulse generators

Figure 3: Test Circuit

### **Functional Description**

The PI6ULS5V9515A is a CMOS integrated circuit intended for I<sup>2</sup>C bus and SMBus systems applications. The device contains two identical bidirectional open-drain buffer circuits that enable I<sup>2</sup>C and similar bus systems to be extended without degradation of system performance.

The PI6ULS5V9515A enables the system designer to isolate two halves of a bus for both voltage and capacitance., accommodating more  $I^2C$  devices or longer trace length. It also permits extension of the  $I^2C$ -bus by providing bidirectional buffering for both the data (SDA) and the clock (SCL) lines, thus allowing two buses of 400 pF to be connected in an  $I^2C$  application.

The PI6ULS5V9515A has an EN pin to turn the drivers on and off. This can be used to isolate a badly behaved slave on power-up until after the system power-up reset. It should never change state during an I<sup>2</sup>C-bus operation because disabling during a bus operation will hang the bus and enabling part way through a bus cycle could confuse the I<sup>2</sup>C-bus parts being enabled. The enable pin should only change state when the global bus and the repeater port are in an idle state to prevent system failures.

The output low levels for sides are approximately 0.5 V, but the input voltage of each internal buffer must be 70 mV lower (0.43V) or even more lower. When the output internally is driven low he low is not recognized as a low by the input. This prevents a lockup condition from occurring when the input low condition is released.

Two or more PI6ULS5V9515A devices can't be used in series. The PI6ULS5V9515A design does not allow this configuration. Since there is no direction pin, slightly different valid low-voltage levels are used to avoid lockup conditions between the input and the output of each repeater. A valid low applied at the input of a PI6ULS5V9515A will be propagated as a buffered low with a slightly higher value on the output. When this buffered low is applied to another PI6ULS5V9515A-type device in series, the second device does not recognize it as a valid low and will not propagate it as a buffered low again.

The device contains a power-up control circuit that sets an internal latch to prevent the output circuits from becoming active until Vcc is at a valid level (Vcc = 2.3 V).

As with the standard I<sup>2</sup>C system, pull-up resistors are required to provide the logic-high levels on the buffered bus. The PI6ULS5V9515A has standard open-collector configuration of the I<sup>2</sup>C bus. The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. The device is designed to work with Standard mode and Fast mode I<sup>2</sup>C devices in addition to SMBus devices. Standard mode I<sup>2</sup>C devices only specify 3 mA in a generic I<sup>2</sup>C system, where Standard mode devices and multiple masters are possible. Under certain conditions, higher termination currents can be used.

### **Application Information**

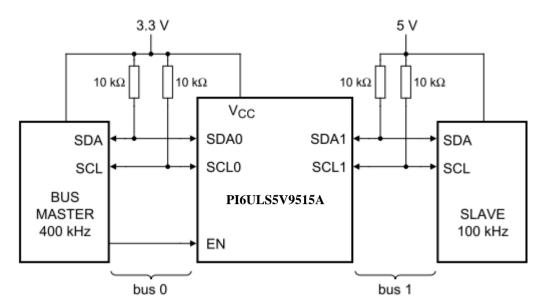

A typical application is shown in Figure 4. In this example, the system master is running on a 3.3 V I<sup>2</sup>C-bus while the slave is connected to a 5V bus. Both buses run at 400 kHz. Master devices can be placed on either bus.

The PI6ULS5V9515A is 5V tolerant, so it does not require any additional circuitry to translate between different bus voltages.

When one side of the PI6ULS5V9515A is pulled LOW by a device on the  $I^2C$ -bus, a CMOS hysteresis type input detects the falling edge and causes the internal driver on the other side to turn on, thus causing the other side to also go LOW. The side driven LOW by the PI6ULS5V9515A will typically be at  $V_{OL} = 0.5 \text{ V}$ .

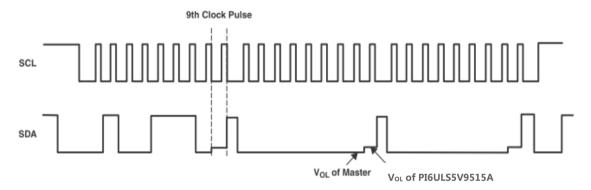

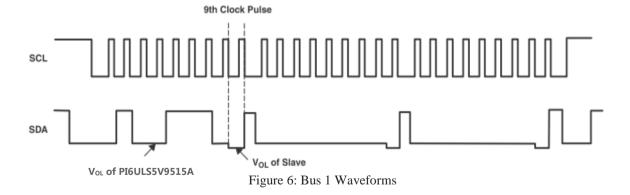

Figure 5 and Figure 6 show the waveforms that are seen in a typical application. If the bus master in Figure 4 writes to the slave through the PI6ULS5V9515A, Bus 0 has the waveform shown in Figure 5. This looks like a normal  $I^2C$  transmission until the falling edge of the eighth clock pulse. At that point, the master releases the data line (SDA) while the slave pulls it low through the PI6ULS5V9515A. Because the  $V_{OL}$  of the PI6ULS5V9515A typically is around 0.5V, a step in the SDA is seen. After the master has transmitted the ninth clock pulse, the slave releases the data line.

On the Bus 1 side of the PI6ULS5V9515A, the clock and data lines have a positive offset from ground equal to the  $V_{OL}$  of the PI6ULS5V9515A. After the eighth clock pulse, the data line is pulled to the  $V_{OL}$  of the slave device, which is very close to ground in the example.

It is important to note that any arbitration or clock-stretching events on Bus 1 require that the  $V_{OL}$  of the devices on Bus 1 be 70 mV below the  $V_{OL}$  of the PI6ULS5V9515A (see  $V_{OL}$  -  $V_{ILC}$  in Electrical Characteristics) to be recognized by the PI6ULS5V9515A and transmitted to Bus 0.

Figure 4: Typical Application

Figure 5: Bus 0 Waveforms

### **Mechanical Information**

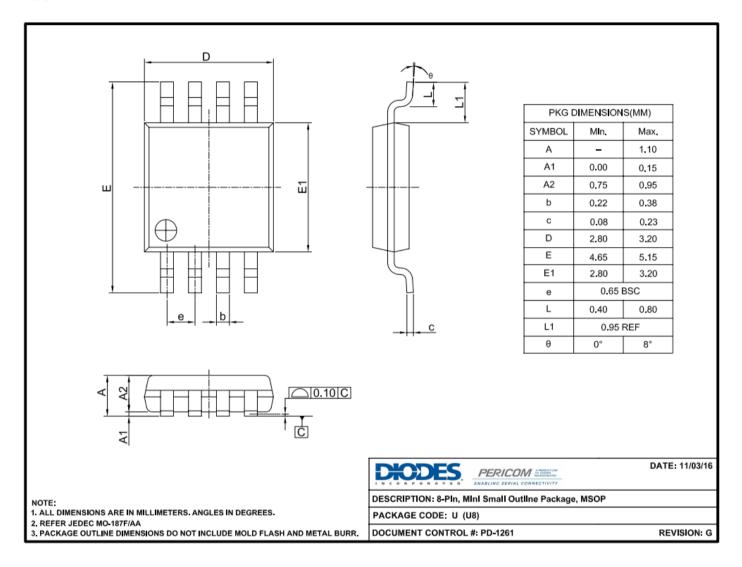

### MSOP-8

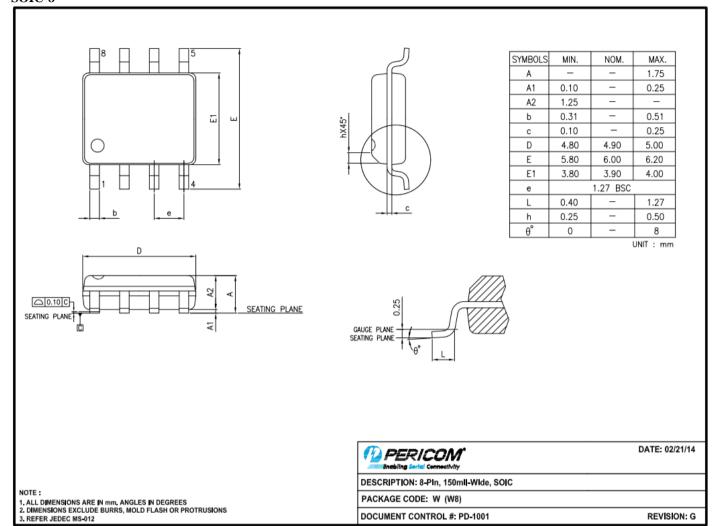

#### **SOIC-8**

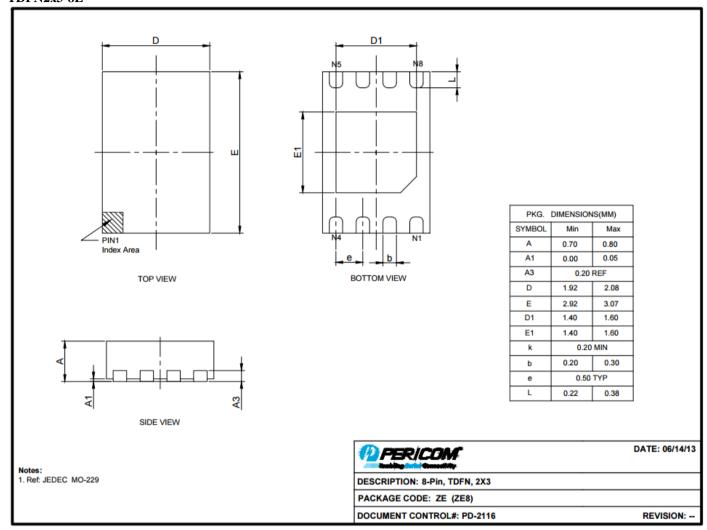

#### TDFN2x3-8L

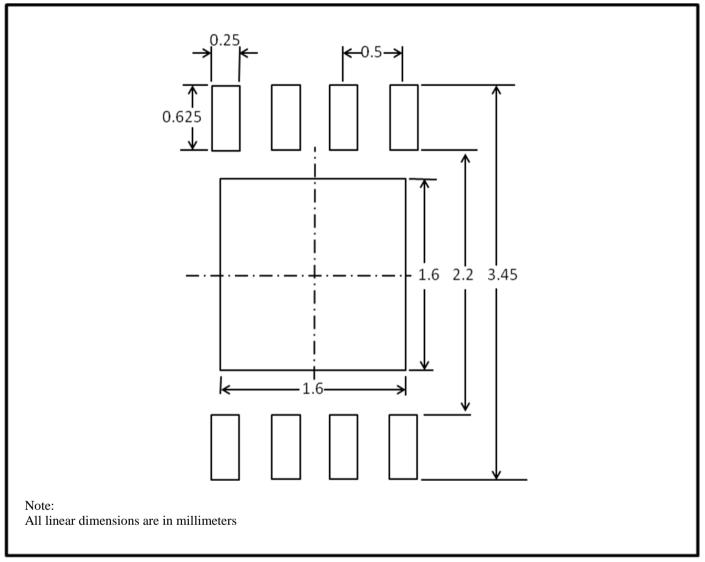

### Recommended Land pattern for TDFN2\*3-8L

## **Ordering Information**

| Part No.          | Package Code | Package                                                |

|-------------------|--------------|--------------------------------------------------------|

| PI6ULS5V9515AUE   | U            | 8-pin, Mini Small Outline Package ( MSOP)              |

| PI6ULS5V9515AUEX  | U            | 8-pin, Mini Small Outline Package ( MSOP), Tape & Reel |

| PI6ULS5V9515AWE   | W            | 8-pin, 150mil-Wide (SOIC)                              |

| PI6ULS5V9515AWEX  | W            | 8-pin, 150mil-Wide (SOIC), Tape & Reel                 |

| PI6ULS5V9515AZEEX | ZE           | 8-pin, 2x3 (TDFN), Tape & Reel                         |

#### Note:

- E = Pb-free

- Adding X Suffix= Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### **Diodes Incorporated:**

<u>PI6ULS5V9515AUEX</u> <u>PI6ULS5V9515AWEX</u> <u>PI6ULS5V9515AUE-2017</u> <u>PI6ULS5V9515AWE</u> <u>PI6ULS5V9515AUEX-2017</u>