### TC8511F

### Font Graphics Accelerator

#### 1 **GENERAL DESCRIPTION**

The Font Graphics Accelerator (FGA) is a high-speed LSI that enables hardware-based processing. Efficient commands are provided to convert display parameters to highquality characters. Possible output includes Bezier cubic curves, straight lines, arcs (circles), and elliptic arcs (ellipses).

#### 2 **FEATURES**

- ☐ Si-gate high speed CMOS technology

- □ +5V single power supply

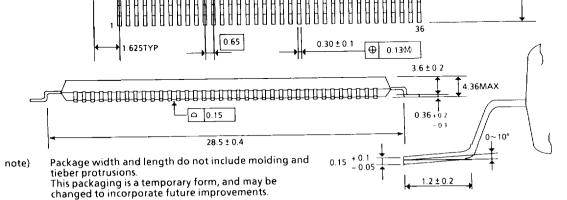

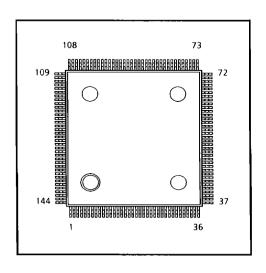

- ☐ 144 pin flat package

- 13 kinds of basic command

- Drawing function

Bezier curve, Line, Arc (Circle),

Elliptic arc (Ellipse)

☐ Filling function

Bezier curve dx, dy generation

DDA line dx, dy generation

Outline drawing

Filling

Command → Character generation

$(60 \times 60 \text{ dot})$

- Dividing fonts generation

- ☐ Buffer memory size

Maximum 32MB (Pair)

[] Host interface

32 bits or 16 bits selection

☐ Direct SRAM interface

DMA transfer function

400 ns/dot

100 ns/dot

400 ns/dot.

400 ns/byte (Clock cycle 10MHz)

1800~2000 character/second (Estimate value)

### 3. FGA and APPLICATION SYSTEM

### 3.1 INTERNAL ORGANIZATION

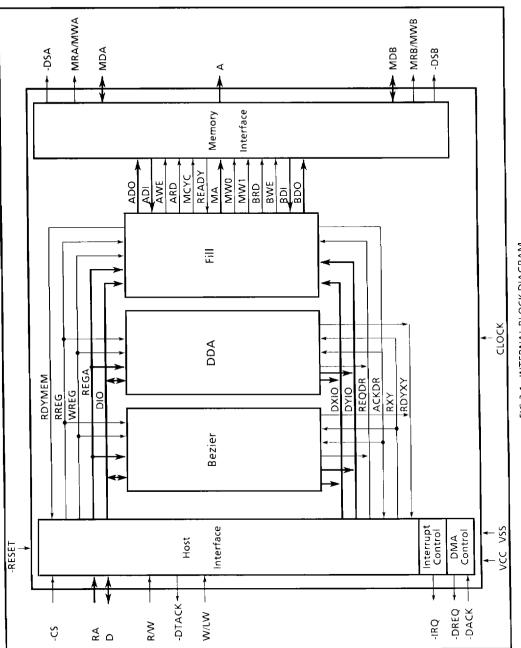

The FGA is composed mainly of the following 5 blocks:

#### (1) HOST BLOCK

The host block interfaces the host system and the FGA. It provides access to the control registers in the Bezier, DDA and Fill blocks, and to the buffer memory. It has the Host block for the transmission of address displacements between Bezier/DDA block and the host system.

An address displacement (dx, dy) may be generated by the Bezier block, DDA block or host system.

#### (2) BEZIER BLOCK

The Bezier block generates quantized displacements (dx, dy) to draw an approximated Bezier cubic curve. The approximation is based on 2 on-line points and 2 off-line points defined by the CPU. The Bezier block creates precise curves that will improve the quality of outline fonts. Displacements (dx, dy) are generated at an average speed of 400 ns/dot (Clock cycle = 10MHz).

#### (3) DDA BLOCK

The DDA block generates quantized displacements (dx, dy) to draw approximated straight lines. The approximation is based on 2 on-line points determined by the CPU.

### (4) FILL BLOCK

The Fill block has two major functions:

- 1) Draws in the buffer memory the outlines determined by the address displacements (dx, dy) provided from the Bezier block, DDA block and/or the host system. The buffer memory has a twofold structure; i.e. All outlines are generated in memory A, and outlines indicating special points (points on horizontal lines, vertexes, concaves, overlapped points, corners, etc.) are generated in memory B; and:

- 2) Fill areas enclosed by the outlines. The result of filling is stored into the buffer memory B.

Operating speed Outlining: 400 ns/dot

Filling: 400 ns/byte (Clock cycle = 10MHz clock)

#### (5) MEMORY BLOCK

The Memory block is connected with the Fill block to interface data exchange to and from the buffer memory (A and/or B).

FGA internal block diagram shown in FIG.3.1.

FIG.3.1 INTERNAL BLOCK DIAGRAM

2

TC8511F-3 250190 129

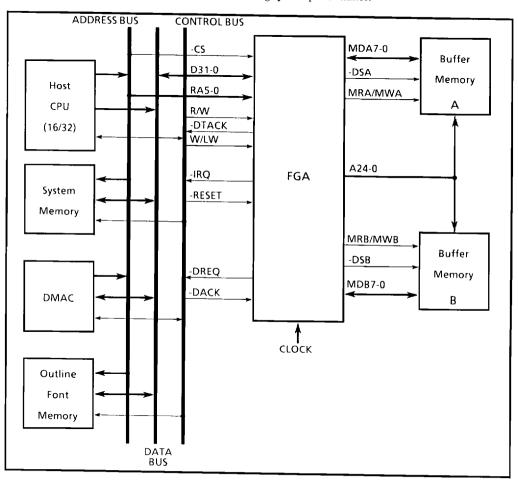

### 3.2 SYSTEM CONFIGURATION

FIG.3.2 illustrates a typical configuration of the FGA-linked system. The FGA is connected as a peripheral of the host system through the interface.

Commands from the CPU is interpreted by the FGA for converting approximated curves and lines to dot matrix outlines, storing these outlines into dedicated local memories A and B, and filling the outlined areas. To maximize the speed and performance, the buffer memories are separated from the CPU system bus so they operate on independent timing.

When transferring filled data to system memory, it can be done simultaneously with filling motion thus enabling transfer of data to the CPU without lowering system performance.

FIG.3.2 EXAMPLE of SYSTEM CONFIGURATION

# 2

## DISPLAY CONTROLLER

### 4. PIN DESCRIPTION

### 4.1 PIN CONNECTION

| NO. | ю  | PIN NAME | NO. | 10  | PIN NAME | NO. | Ю | PIN NAME | NO. | Ю   | PIN NAME |

|-----|----|----------|-----|-----|----------|-----|---|----------|-----|-----|----------|

| 1   | V  | VDD      | 37  | V   | VDD      | 73  | G | GND      | 109 | V   | VDD      |

| 2   | G  | GND      | 38  | G   | GND      | 74  | G | GND      | 110 | 0   | -D\$A    |

| 3   |    | -CS      | 39  | 10  | D13      | 75  | v | VDD      | 111 | 0   | MRA/MWA  |

| 4   | 1  | R/W      | 40  | Ю   | D14      | 76  | 0 | Α0       | 112 | G   | GND      |

| 5   |    | W/LW     | 41  | Ю   | D15      | 77  | 0 | A1       | 113 | V   | VDD      |

| 6   | О3 | -DTACK   | 42  | V   | VDD      | 78  | 0 | A2       | 114 | .10 | MDA0     |

| 7   | V  | VDD      | 43  | G   | GND      | 79  | 0 | А3       | 115 | 10  | MDA1     |

| 8   | G  | GND      | 44  | Ю   | D16      | 80  | 0 | A4       | 116 | 10  | MDA2     |

| 9   | 0  | -DREQ    | 45  | 10  | D17      | 81  | 0 | A5       | 117 | 10  | MDA3     |

| 10  | _  | -DACK    | 46  | 10  | D18      | 82  | G | GND      | 118 | G   | GND      |

| 11  | >  | VDD      | 47  | 0   | D19      | 83  | ٧ | VDD      | 119 | V   | VDD      |

| 12  | G  | GND      | 48  | 10  | D20      | 84  | 0 | A6       | 120 | Ю   | MDA4     |

| 13  | OD | -IRQ     | 49  | >   | VDD      | 85  | 0 | A7       | 121 | 10  | MDA5     |

| 14  | 1  | -RESET   | 50  | G   | GND      | 86  | 0 | A8       | 122 | 10  | MDA6     |

| 15  | <  | VDD      | 51  | 10  | D21      | 87  | 0 | Α9       | 123 | 10  | MDA7     |

| 16  | G  | GND      | 52  | 10  | D22      | 88  | 0 | A10      | 124 | G   | GND      |

| 17  | ı  | CLOCK    | 53  | 10  | D23      | 89  | O | A11      | 125 | V   | VDD      |

| 18  | V  | VDD      | 54  | 10  | D24      | 90  | G | GND      | 126 | G   | GND      |

| 19  | G  | GND      | 55  | 10  | D25      | 91  | > | VDD      | 127 | ٧   | VDD      |

| 20  | 10 | D0       | 56  | ν   | VDD      | 92  | 0 | A12      | 128 | 0   | -DSB     |

| 21  | 10 | D1       | 57  | G   | GND      | 93  | 0 | A13      | 129 | 0   | MRB/MWB  |

| 22  | Ю  | D2       | 58  | Ю   | D26      | 94  | 0 | A14      | 130 | G   | GND      |

| 23  | 10 | D3       | 59  | 10  | D27      | 95  | 0 | A15      | 131 | V   | VDD      |

| 24  | 10 | D4       | 60  | 10  | D28      | 96  | 0 | A16      | 132 | 10  | MDB0     |

| 25  | V  | VDD      | 61  | Ю   | D29      | 97  | 0 | A17      | 133 | 10  | MDB1     |

| 26  | G  | GND      | 62  | 10  | D30      | 98  | G | GND      | 134 | 10  | MDB2     |

| 27  | 10 | D5       | 63  | 10  | D31      | 99  | V | VDD      | 135 | Ю   | MD83     |

| 28  | 10 | D6       | 64  | V   | VDD      | 100 | 0 | A18      | 136 | G   | GND      |

| 29  | 10 | D7       | 65  | G   | GND      | 101 | 0 | A19      | 137 | V   | VDD      |

| 30  | 10 | D8       | 66  | 1   | RA0      | 102 | 0 | A20      | 138 | 10  | MDB4     |

| 31  | 10 | D9       | 67  |     | RA1      | 103 | 0 | A21      | 139 | 10  | MD85     |

| 32  | V  | VDD      | 68  | 1   | RA2      | 104 | 0 | A22      | 140 | 10  | MDB6     |

| 33  | G  | GND      | 69  | 1   | RA3      | 105 | 0 | A23      | 141 | 10  | MDB7     |

| 34  | 10 | D10      | 70  | - 1 | RA4      | 106 | 0 | A24      | 142 | G   | GND      |

| 35  | 10 | D11      | 71  | -   | RA5      | 107 | G | GND      | 143 | V   | VDD      |

| 36  | 10 | D12      | 72  | V   | VDD      | 108 | ٧ | VDD      | 144 | G   | GND      |

#### 4.2 PIN CONFIGURATION

### (1) Bidirectional Data Bus (D31-D0: I/O T)

The bidirectional data bus (D31-D0) is used to transfer data between the CPU and the FGA. The FGA uses either a 16-bit or 32-bit bus for data transfer. The data bus provides a 3-state buffer, and is kept at high impedance except for the reading by the CPU. The 16-bit structure should be composed of the bits D15 - D0, with the bits D31-D16 unused.

### (2) Read/Write (R/W: Input)

Read/Write (R/W) input signals control the data transfer to and from the CPU. Data are transferred to the CPU when the R/W is high, and to the FGA when the R/W is low.

The data direction is reversed in the DMA transfer.

### (3) Chip Select (-CS: Input)

The -CS input signal is used to address the FGA by the CPU. The FGA registers can be read/written only when the -CS signal is low.

### (4) Register Address Bus (RA5-RA0: Input)

The RA5-RA0 input signals are used to access the FGA registers (command register, mode registers, parameter registers, status registers and interrupt registers). Each of these register has a identified register number. A register can be read/written only when its register number is designated.

A separate memory access port is automatically selected for the DMA transfer. Therefore, any register number will be ignored if designated.

A register number (address) is composed of one word, but may be accessed by word (16 bits) or long word (32 bits) according to the width of the bidirectional data bus. In the 32-bit structure, reading an even address n results in the reading of n and n+1, and an odd address m results in the reading of m-1 and m.

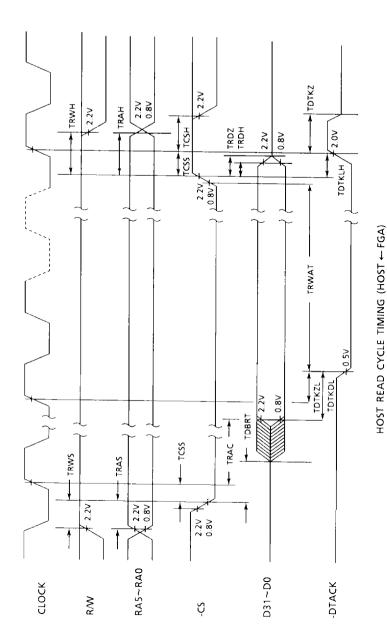

### (5) Data Transfer Acknowledge (-DTACK: Output T)

The DTACK signal indicates the end of a data transfer. The signal is based on the 3-state logic. When the CPU acknowledges a low -DTACK in the read cycle, it terminates the bus cycle after latching data on the bidirectional data bus. In the write cycle, it terminates the bus cycle immediately after it acknowledges a low -DTACK signal. The -DTACK signal is kept at high impedance in non-bus cycles.

### (6) Data Bus Width Select (W/LW: Input)

The W/LW signal selects either 32 bits or 16 bits for the bidirectional data bus (D31-D0) width. The 16-bit structure is selected when W/LW is high; only the D15-D0 lines are used, while D31-D16 are kept at high impedance. When W/LW is low, all lines are used for the 32-bit structure. Normally, the bus width is determined during the system configuration.

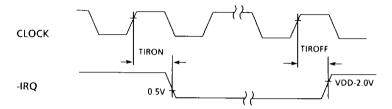

#### (7) Interrupt request (-IRO: Output OD.)

The -IRQ signal requests the CPU to interrupt the current operation. An interrupt may be requested to terminate a command, divide a line, process an overflow of the stack or check the clipping area.

-IRQ is an open-drain output terminal.

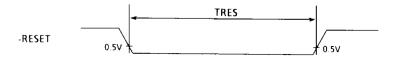

#### (8) Reset (-RESET: Input)

The -RESET signal resets the FGA state.

When a low -RESET signal is entered, the FGA will:

- · Reset the control flip-flop.

- · Clear the mode registers,

- · Reset a part of the parameter registers and set defaults.

- · Clear the interrupt register and the interrupt enable register.

### (9) DMA transfer request (-DREQ: Output)

The -DREQ signal is generated to the DMAC (direct memory access control) to request a data transfer in the DMA mode. The system must be set to the DMA mode and ready for a transfer before a -DREQ signal is generated.

Either single transfer or block transfer can be selected.

### (10) DMA transfer request acknowledge (-DACK: Input)

The -DACK signal is entered from the DMAC when it acknowledges a DMA transfer request (DREQ). When -DACK is low, data are transferred to the FGA if the R/W signal is high, and to the CPU if R/W is low. While -DACK is low, the -CS signal must be kept at a high level. In a non-DMA mode, -DACK must be pulled up to a high level.

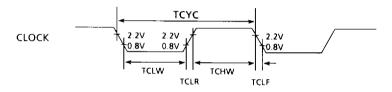

### (11) Clock (CLOCK: Input)

The clock signal determines the basic cycle of all the FGA operations.

### (12) Memory Data Bus A (MDA7-MDA0: I/O T)

This is a bidirectional data bus used to transfer data to and from the local buffer memory  $\Lambda$ . The bus serves as a 3-state buffer. It is kept at a high impedance when the memory is not accessed.

### (13) Memory Data Bus B (MDB7-MDB0: I/O T)

This is a bidirectional data bus used to transfer data to and from the local buffer memory B.

The bus serves as a 3-state buffer. It is kept at a high impedance when the memory is not accessed.

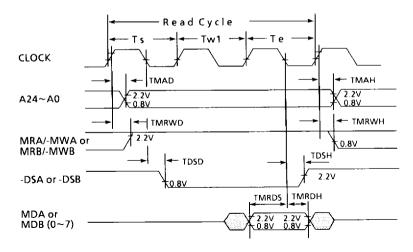

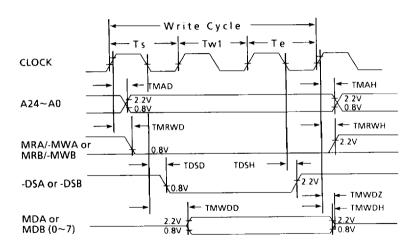

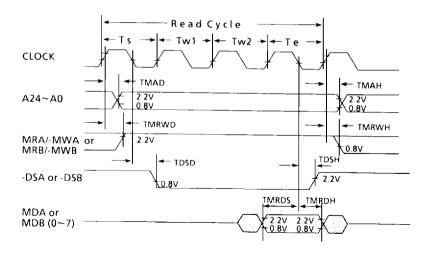

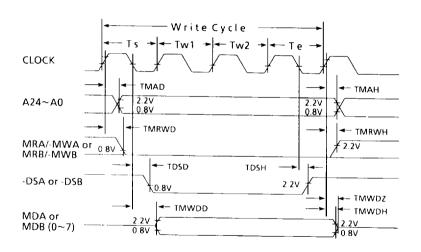

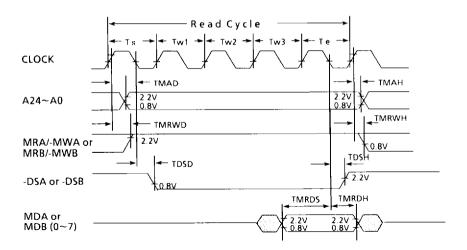

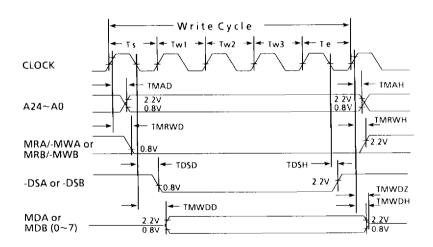

### (14) Memory Address Bus (A24-A0: Output)

The Memory Address Bus (A24-A0) is used to address the local buffer memories A and B.

#### (15) Data strobe A (-DSA: Output)

The -DSA signal defines the timing of reading/writing from/to the local buffer memory  $\Lambda$ . Data are latched to be read into the FGA from the local buffer memory  $\Lambda$  at the -DSA rising edge. Data can be written when -DSA is low.

### (16) Data strobe B (-DSB: Output)

The -DSB signal defines the timing of reading/writing from/to the local buffer memory B.

Data are latched to be read into the FGA from the local buffer memory B at the -DSB rising edge. Data can be written when -DSB is low.

### (17) Memory Read/Write A (MRA/MWA: Output)

The  $MR\Lambda/MW\Lambda$  signals determine the direction of data to be transferred between the FGA and the local buffer memory  $\Lambda$ .

Data are read from the local buffer memory  $\Lambda$  when MRA/MWA is high, and written to the memory when the signal is low.

### (18) Memory Read/Write B (MRB/MWB: Output)

The MRB/MWB signals determine the direction of data to be transferred between the FGA and the local buffer memory B.

Data are read from the local buffer memory B when MRB/MWB is high, and written to the memory when the signal is low.

### 5. FUNCTIONAL DESCRIPTION

### 5.1 GENERAL

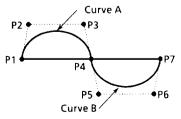

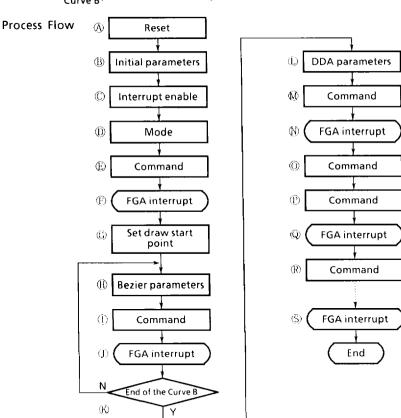

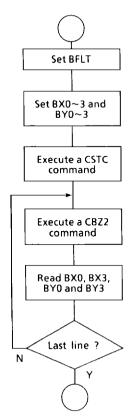

The Font Graphics Accelerator outlines and fills using various parameters, modes and commands provided from the CPU. This section describes the procedures required to achieve specific operations. Example

The following pattern can be generated to the CPU as described in the flow chart below.

- The curve A inside the points P1, P2, P3 and P4 is drawn by a Bezier command.

- The curve B inside the points P4, P5, P6 and P7 is drawn by a Bezier command.

- The line from the point P7 to the point P1 is drawn by a DDA command.

| NO.          | OPERATION                                                                                                                                                                                                                           | REGISTER(S) USED                            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| ( <b>A</b> ) | Initialize the FGA. The FGA is initialized by RESET signal or CRST command.                                                                                                                                                         | CMD                                         |

| (B)          | Set the following initial parameters for operating the FGA: Size of the local buffer memories Work areas Start point (P1)                                                                                                           | MAD<br>ASD,AED                              |

| (C)          | Set the interrupt enable bit if an interrupt is required to terminate each command.                                                                                                                                                 | IER                                         |

| (D)          | Select a mode for commands to be executed.                                                                                                                                                                                          | MOD1,MOD2                                   |

| (E)          | Execute a CMCL command to clear the local buffer memories A and B.                                                                                                                                                                  | CMD                                         |

| (J/)         | The FGA sets the interrupt bit (INTMB) and generates an interrupt request (-IRQ) to the CPU. The CPU reads the IR register to confirm that the local buffer memories are cleared.                                                   | IR                                          |

| (G)          | Set position value of P1 for drawing start point                                                                                                                                                                                    | DS                                          |

| QD.          | Set the coordinates of the points P1, P2, P3 and P4 on the parameter registers (for drawing the Bezier curve A in the local buffer memories).                                                                                       | BX0,BX1,<br>BX2,BX3,<br>BY0,BY1,<br>BY2,BY3 |

| (1)          | Execute a CBZ1 command to draw the Bezier curve A.                                                                                                                                                                                  | CMD                                         |

| ( <b>j</b> ) | The FGA sets the interrupt bit (INTB1), and generates an interrupt request (IRQ) to the CPU. The CPU reads the IR register to confirm that the Bezier curve A is drawn.                                                             | IR                                          |

| IÒ.          | The CPU checks if the Bezier curve B is drawn. If the curve is not drawn, it repeats the steps 7 through 9 for the points P4, P5, P6 and P7.                                                                                        |                                             |

| (l)          | The CPU calculates and set on the parameter registers the parameters used by the DDA block to draw the line from the point P7 to P1.                                                                                                | DDARO,<br>DDAR3,<br>DDAR4,<br>DDAC          |

| M            | Execute a CDDA1 command to draw the straight line.                                                                                                                                                                                  | CMD                                         |

| <b>(N)</b>   | Upon finishing the drawing of straight line, the FGA sets the interrupt bit (INTD) and generates an interrupt request (IRQ) to the CPU which reads the IR register to confirm that the drawing of straight line by DDA is finished. | IR                                          |

| (t t)        | Execute a CPTE command to close the outline.                                                                                                                                                                                        | CMD                                         |

| (P)          | Execute a CFIL1 command to fill the closed area.                                                                                                                                                                                    | CMD                                         |

| NO. | OPERATION                                                                                                                                                                                                                                                                    | REGISTER(S) USED |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Q   | The FGA sets the interrupt bit (INTMB) and generates an interrupt request (IRQ) to the CPU. The CPU reads the IR register to confirm that the filling is finished.  At this moment, the following patterns are stored in the buffer memories A and B:  Memory A  Memory B    | IR               |

| R   | Execute a CBLK command to transfer to the CPU the C filled pattern stored in the local buffer memory B.  The CPU continues reading the results of processing through handshaking communication.                                                                              | CMD              |

| (S) | When the last word (or long word) is read by the CPU, the FGA sets the interrupt bit (INTMB) and generates an interrupt request (IRQ) to the CPU. After the CPU reads the last word (or long word), it reads the IR register to confirm that the block transfer is finished. | IR               |

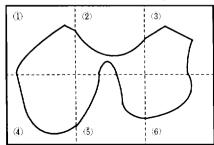

### 5.2 DIVIDING FONTS

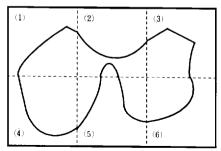

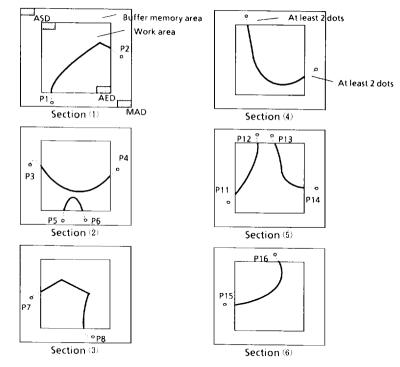

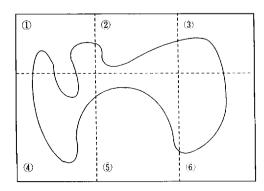

A font larger than the buffer memory area (MAD) can be created in a divided form. Very large fonts can be used because they can be divided into as many sections as desired.

To draw the left pattern, the CPU divides it into 6 sections that fit the size of the buffer memory. The CPU calculates the coordinates of the beginning and end of each outline. Each outline should begin and end at points at least 2 dots extended out of the work area.

The CPU provides parameters of all outlines contained in each divided section.

The work area should be sized smaller than the buffer memory area so that each out line can be extended over its boundary.

A divided pattern can be output to the CPU in the following procedure:

Set parameters → Outline → Fill → Block transfer → Clear the work area.

Divided sections should be processed in the order of  $(1) \rightarrow (2) \rightarrow (3) \rightarrow (4) \rightarrow (5) \rightarrow (6)$ . The following fill commands are used to fill the closed area:

CFIL3 command to fill the sections (1) and (4)

CFIL4 command to fill the sections (2) and (5)

CFIL2 command to fill the sections (3) and (6)

### 5.3 DESCRIPTION of the COMMANDS

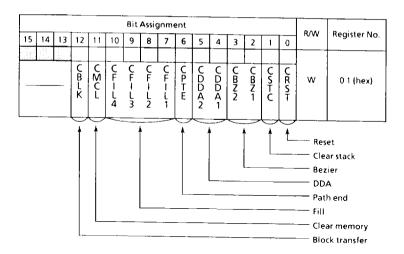

The FGA supports 13 commands, each of which is assigned to a specific bit in the command register (CMD). A command can be activated by writing "1" to the corresponding bit.

|    |    |    |                  |         |                       | Bita             | assig                 | nme              | nt               |                       |                       |                  |                  |                  |                  |                             |

|----|----|----|------------------|---------|-----------------------|------------------|-----------------------|------------------|------------------|-----------------------|-----------------------|------------------|------------------|------------------|------------------|-----------------------------|

| 15 | 14 | 13 | 12               | 11      | 10                    | 9_               | 8                     | 7                | 6                | 5                     | 4                     | 3                | 2                | 1                | 0                |                             |

| _  |    |    | C<br>B<br>L<br>K | C M C L | C<br>F<br>1<br>L<br>4 | C<br>F<br>L<br>3 | C<br>F<br>I<br>L<br>2 | C<br>F<br>I<br>L | C<br>P<br>T<br>E | C<br>D<br>D<br>A<br>2 | C<br>D<br>D<br>A<br>1 | C<br>B<br>Z<br>2 | C<br>B<br>Z<br>1 | C<br>S<br>T<br>C | C<br>R<br>S<br>T | Name of correspond command. |

Commands Assigned to the Command Register Bits

See Section 5.7 for restrictions involved in activating these commands.

### 5.3.1 RESET COMMAND [CRST]

A CRST command is executed to initialize the FGA. It has the same function as the -RESET signal. Executing a CRST command causes the following operations:

- 1. Reset the control flip-flop.

- 2. Clear the mode registers (MOD1 and MOD2).

- 3. Clear the parameter registers and set defaults.

- · Clear the Work Area Start (ASD) register.

- · Reset the Work Area End (AED) register (to XAE = 63 and YAE = 511).

- · Clear the Current Pointer (CP).

- · Clear the Drawing Start (DS) register.

- Reset the Buffer Memory Area Definition (MAD) register (to XMA = 6).

- · Clear the Stack Pointer (BSP).

- 4. Clear the following interrupt registers:

- · Interrupt register (IR).

- Interrupt enable register (IER).

### 5.3.2 CLEAR STACK [CSTC]

A CSTC command clears the Bezier Stack Pointer (BSP) used for the generation of Bezier curves. A CSTC command must precede a CBZ2 command that subdivides a Bezier curve into lines.

The stack pointer can be cleared by executing a CSTC command or writing "0".

A CSTC command is not necessary for executing a CBZ1 command (that generates a Bezier curve).

### 5.3.3 COMMAND to GENERATE a BEZIER CURVE [CBZ1]

A CBZ1 command generates a Bezier cubic curve.

When a CBZ1 command is executed, the Bezier block generates 4-bit quantized displacements (dx, dy) to draw an approximated Bezier cubic curve. A Bezier cubic curve is defined using 4 points, whose x-y coordinates are indicated by the parameter registers BX0-3 and BY0-3.

After a CBZ1 command is executed, the FGA sets the bit INTB1 of the interrupt register.

A CBZ1 command causes one of the following operations according to the mode specified by the MOD1 mode register:

- (a) Draw an outline in the local buffer memory A using the displacements (dx, dy).

- (b) Draw an outline in the local buffer memory A and the local buffer memory B using the displacements (dx, dy).

- (c) Transfer the displacements (dx, dy) to the CPU while doing the operation (a) or (b).

- (d) Transfer the displacements (dx, dy) to the CPU without doing the operation (a) or (b).

- (a) is selected to draw an outline. (b) is selected to draw an outline and fill. (c) and (d) are used if displacements should be processed by the CPU.

A CSTC command is not required before executing a CBZ1 command.

### 5.3.4 COMMAND to DIVIDE a BEZIER CURVE [CBZ2]

CBZ2 commands are used to subdivide a Bezier cubic curve into straight lines.

The number of lines is determined by a value set on the flatness register. A Bezier curve to be subdivided is specified by the parameter registers  $BX0\sim3$  and  $BY0\sim3$ .

The first CBZ2 command determines the first division point (or the end of the first line). To obtain the next division point, another CBZ2 command should be executed.

Each time a division point is determined by a CBZ2 command, the FGA sets the INTB2 bit of the interrupt register, and generates an interrupt request IRQ.

P1-P4 : Bezier parameters (coordinates of

the 4 points)

(P1 and Q1): Beginning and end of the line 1 (Q1 and Q2): Beginning and end of the line 2 (Q2 and P4): Beginning and end of the line 3 The coordinates of the beginning and end of each line are stored in the parameter registers (BX0, BY0) and (BX3, BY3), and read by the CPU.

When the last division is completed, the FGA sets the interrupt bits INTB1 and INTB2, and generates an interrupt request IRQ to inform the CPU of the end of division.

Only the ends (BX3, BY3) should be picked up each time to read subdivided lines continuously.

A CSTC command must be executed before the first CBZ2 command.

A CBZ2 command defines the beginning and end of a line for reading by the CPU. It can be coincided or paralleled with a CDDA1 command to draw this line in the local buffer memories A and R

The CPU reads the beginning (BX0, BY0) and end (BX3, BY3) of a line, and executes the next CBZ2 command if necessary. At the same time, it calculates and sets on the parameter registers DDAR0, DDAR3 and DDAR4 the parameters required to draw the line just determined. Then, a CDDA1 command can be executed to draw this line in the buffer memories.

The above steps are repeated until the last line is drawn in the local buffer memories A and B.

### 5.3.5 COMMAND to GENERATE a STRAIGHT LINE [CDDA1]

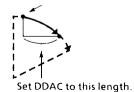

A CDDA1 command is used to generate a straight line.

When a CDDA1 is executed, the DDA block generates 4-bit quantized displacements (2 bits each for x and y coordinates), the number of which is designated by the DDAC register. A line is drawn based on these displacements and the parameters provided by the parameter registers DDAR0, DDAR3 and DDAR4. After a CDDA1 command is executed, the FGA sets the INTD bit of the interrupt register. A CDDA1 command causes one of the following operations according to a mode specified by the MOD1 mode register:

- (a) Draw an outline in the local buffer memory A using the displacements (dx, dy).

- (b) Draw an outline in the local buffer memories A and B using the displacements (dx, dy).

- (c) Transfer the displacements (dx, dy) to the CPU while doing the operation (a) or (b).

- (d) Transfer the displacements (dx, dy) to the CPU without doing the operations (a) or (b).

- (a) is selected to draw an outline pattern. (b) is selected to draw outline and filled patterns. (c) and (d) are used if the displacements need processing by the CPU.

### 5.3.6 COMMAND to GENERATE a CIRCLE, ARC or ELLIPSE [CDDA2]

CDDA2 commands are used to generate a circle, arc or ellipse.

When a CDDA2 command is executed, the DDA block generates 4-bit quantized displacements (2 bits each for x and y coordinates), the number of which is designated by the DDA counter register (DDAC). A 1/8 circle or ellipse is drawn using these displacements and the values of the parameter registers (DDAR0, DDAR1, DDAR2, DDAR3 and DDAR4) and the mode register MOD2. These parameters are preset to define the beginning of a circle/ellipse and its radius. After a CDDA2 command is executed, the FGA sets the INTD bit of the interrupt register.

The operation of a CDDA2 command is determined by the MOD1 mode register, as in the case of a CDDA1 command

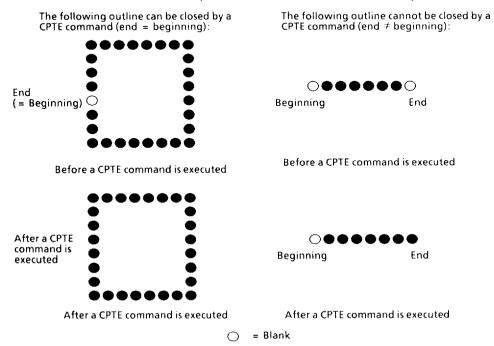

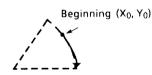

### 5.3.7 PATH END [CPTE]

A CPTE command is used to close an outline. An outline can be closed only if its end overlaps its beginning. This command should be executed after defining the x-y coordinates of the end (= beginning) of an outline to be closed. To fill a closed area, use the fill commands CFIL 1 to 4.

A CPTE Command example to Close An Outline in the Buffer Memory A

= Filled

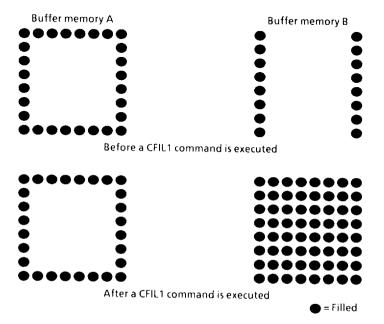

### 5.3.8 COMMAND to FILL a NON-DIVIDED FONT [CFIL1]

A CFIL1 command is used to fill the interior of a closed outline. Before executing this command, an outline must be drawn by CBZ1, CDDA1 and/or CDDA2 commands or the direct write access of the displacement from the CPU to the dx, dy port, and closed at a point specified by the CPU. A closed area can be filled by a CFIL1 command if it is drawn in both the local buffer memories A and B according to the mode specified by the MOD1 mode register.

After a CFIL1 command is executed, the FGA sets the INTMB bit of the interrupt register.

An Example of CFIL1 Command

A CFIL1 command causes one of the following operations as determined by the MOD1 mode register:

- (1) Transfer the filled pattern to the CPU.

- (2) Write the filled pattern in the buffer memory B.

- (3) Do (1) and (2) simultaneously.

- (4) While doing (1), clear the work areas of the buffer memories  $\boldsymbol{A}$  and  $\boldsymbol{B}$ .

The operation (1) provides the fastest output to the CPU. A block transfer (CBLK command) should be used to send the result of (2) to the CPU. (4) enables outlining and filling to be repeated without using a CMCL (clear memory) command.

#### 5.3.9 COMMANDS to FILL a DIVIDED FONT [CFIL2, CFIL3, CFIL4]

These commands fill a divided font as follows:

CFIL2 command fills the right sections of a divided font.

CFIL3 command fills the left sections of a divided font.

CFIL4 command fills the remaining sections of a divided font.

After a CFIL command is executed, the FGA sets the INTMB bit of the interrupt register.

A font larger than the buffer memory area can be divided into 6 sections as shown in the left figure. To fill this divided font, use the following commands:

CFIL3 command to fill the sections (1) and (4).

CFIL4 command to fill the sections (2) and (5).

CFIL2 command to fill the sections (3) and (6).

These sections must be filled in the order of  $(\underline{i}) \rightarrow (\underline{\tilde{z}}) \rightarrow (3) \rightarrow (\underline{\tilde{4}}) \rightarrow (5) \rightarrow (6)$ .

The operation of a CFIL command 2, 3 or 4 is determined by the MOD1 mode register, as in the case of a CFIL1 command.

#### 5.3.10 CLEAR MEMORY [CMCL]

A CMCL command clears a work area specified by the parameter registers ASD and AED.

To clear a work area, set the mode register (MOD1) to specify which memory (A or B) should be cleared, and if it should be cleared to "0" (blank) or "1" (filled). A CMCL command must be executed before any outline can be drawn and filled.

### 5.3.11 BLOCK TRANSFER [CBLK]

A CBLK command transfers data in a work area specified by the parameter registers ASD and AED. Data can be transferred between the CPU and the FGA, the mode of which is specified by the mode register MOD1 (DMA transfer or programmed transfer controlled by the -CS signal).

When a CBLK command is executed, data are transferred repeatedly and the handshake between CPU and FGA is controlled by the -CS or -DACK signal and -DTACK signal.

When the last piece of data is transferred, the FGA sets the interrupt bit INTMB, and generates an interrupt request to inform the CPU of the end of the transfer.

### 5.4 SETTING PARAMETERS

### 5.4.1 SETTING PARAMETERS for DRAWING a BEZIER CURVE

Command

CBZ1

Parameter registers :

BX0, BX1, BX2, BX3

BY0, BY1, BY2, BY3

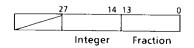

To draw a Bezier curve, set the parameter registers BX0~3 and BY0~3 to the following values:

BX0~3

: X coordinates of the reference points  $P0 \sim P3 + 0.5$

BY0~3

: Y coordinates of the reference points  $P0 \sim P3 + 0.5$

Each of these parameter registers is composed of a 14 bit integer part and a 14 bit fraction part.

Command

CBZ2

Parameter registers

BX0, BX1, BX2, BX3

BY0, BY1, BY2, BY3

BFLT

The parameter registers  $BX0\sim3$  and  $BY0\sim3$  should be set to the same values as for the CBZ1 command.

CBZ2 commands are used to divide a Bezier curve into several lines. A Bezier curve is approximated by these lines as determined by the flatness parameter. The flatness of a Bezier curve is specified by the parameter register BFLT as follows next page:

| FLATNESS | VALUE OF BFLT |

|----------|---------------|

| 1/2      | 11111         |

| 1        | 11110         |

| 2        | 11100         |

| 4        | 11000         |

| 8        | 10000         |

| 16       | 00000         |

A Bezier curve can be divided by a CBZ2 command in the following algorithm:

BX0 and BY0 (BX3 and BY3) indicate values equal to 0.5 plus the X or Y coordinate of the beginning (end) of each approximating line.

A line is defined to be the last line if:

- The STSE bit of the status register is set (stack is empty), or

- Both the INTB2 bit and the INTB1 bit of the interrupt register IR are set after a CBZ2 command is executed.

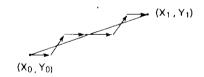

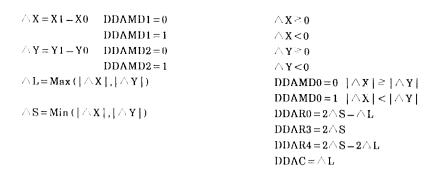

#### 5.4.2 SETTING PARAMETERS for DRAWING a LINE

Command : CDDA1

Parameter registers: DDAR0, DDAR3, DDAR4, DDAC

Mode register bits : DDAMD0, DDAMD1, DDAMD2, DDAMD4

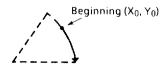

Beginning  $(X_0, Y_0)$ End  $(X_1, Y_1)$

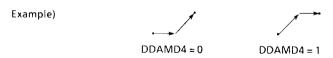

The DDAMD4 bit determines whether a coordinate with a fraction of 0.5 should be rounded upward or downward according to the axial direction of the shorter displacement; i.e., if DDMA4=0, a coordinate with a fraction of 0.5 will be rounded downward (upward) to the opposite direction to the shorter displacement, and if DDAMD4=1, it will be rounded upward (downward) to the same direction as the shorter displacement.

In the above description, the line begins and ends at integral coordinates. If the coordinates contain a fraction, dx, dy steps for the beginning and end points must be provided from the host processor.

#### 5.4.3 SETTING PARAMETERS for DRAWING a CIRCLE

Command

: CDDA2

Parameter registers: DDARO, DDAR1, DDAR2, DDAR3, DDAR4, DDAC

Mode register bits : DDAMD0, DDAMD1, DDAMD2, DDAMD3, DDAMD4, DDAMD7

Each CDDA2 command generates a 1/8 circle.

A 1/8 circle can be drawn in 16 forms as shown below, and defined by the mode register bits DDAMD0, DDAMD1, DDAMD2, and DDAMD3. A 1/8 circle may start or end at a given point on the x or y axis (based on its center as the origin). The former is categorized as a case I circle, and the latter a case II circle.

|              | NO.     |          | DDAMD0 | DDAMD1 | DDAMD2 | DDAMD3 | CASE |

|--------------|---------|----------|--------|--------|--------|--------|------|

| ↓ ×          | (s) -   | ,        | 0      | 0      | 0      | 0      | 1    |

| D. Q         | (B)     | 1        | 1      | 0      | 0      | 0      | Ш    |

|              | (C)     | 1        | 1      | 1      | 0      | 0      | l    |

| B 10         | (I)     |          | 0      | 1      | 0      | 0      | II   |

| (E)          | (E) N   | _        | 0      | 1      | 1      | 0      | i    |

|              | (F) (F) | 1        | 1      | 1      | 1      | 0      | II   |

|              | (G)     | 1        | 1      | 0      | 1      | 0      | 1    |

|              | (II)    | _        | 0      | 0      | 1      | 0      | Ш    |

|              | (i) r   |          | 0      | 1      | 0      | 1      | 1    |

| <b>D</b>     | [(D)] , | (        | 1      | 1      | 0      | 1      | Ħ    |

| D/ , 10      | Ŕ       |          | 1      | 0      | 0      | 1      | 1    |

| $\mathbb{R}$ | (D) \   | <u> </u> | 0      | 0      | 0      | 1      | 11   |

| (T) > (M)    | M) _    | 1        | 0      | 0      | 1      | 1      | 1    |

|              | Ø0      | <u>/</u> | 1      | 0      | 1      | 1      | H    |

|              | ((i))   | )        | 1      | 1      | 1      | 1      | I    |

|              | (P)     |          | o      | 1      | 1      | 1      | II   |

Set DDAMD4 and DDAMD7 to 0.

Set DDAC to the coordinates dx, dy.

Set DDAR3 to 4.

Set DDAR4 to 8.

Set DDAR0 - DDAR2 as follows according to the type of a 1/8 circle to be generated (case I or II):

Case I

Beginning (I<sub>0</sub>, s<sub>0</sub>)

Case II

Beginning  $(s_0, l_0)$

l<sub>0</sub> and s<sub>0</sub> indicate the x – y displacements from the beginning to the end of this 1/8 circle, based on its center as the origin.

R: Radius

In this case, the  $\boldsymbol{x}$  displacement is larger than the  $\boldsymbol{y}$  displacement.

DDAR0 =

$$2(I_0^2 + S_0^2 - R^2)$$

+  $4|I_0| - 2|S_0| + 3$

DDAR1 =  $4|I_0| + 2$

DDAR2 =  $4(|I_0| - |S_0|) + 2$

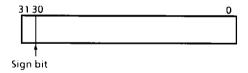

Each of the registers DDAR0~DDAR7 consists of 32 bits, and uses the representation of sign plus 2's complement.

$$\begin{aligned} \text{DDAR0} &= 2 \left( I_0^2 + S_0^2 - R^2 \right) \\ &- 4 \left| I_0 \right| + 2 \left| S_0 \right| + 3 \\ \text{DDAR1} &= -4 \left| I_0 \right| + 2 \\ \text{DDAR2} &= 4 \left( \left| S_0 \right| - \left| I_0 \right| \right) + 2 \end{aligned}$$

# 2

### 5.4.4 ARCS CONSISTING of MORE THAN ONE 1/8 CIRCLE

An arc can be drawn using several 1/8 circles. It should be composed of case I 1/8 circles and case II 1/8 circles that alternate with each other.

If a case I 1/8 circle is already drawn, the case II 1/8 circle that follows it can be drawn using the values remaining in the parameter registers DDAR0-DDAR2. Use the following formulas to calculate the initial parameters of the case II 1/8 circle:

DDAR0 = DDAR0 old + 1/2DDAR2 old - DDAR1 old + 1

DDAR1 = DDAR2 old - DDAR1 old + 2

DDAR2 = DDAR2 old

Similarly, if a case II 1/8 circle is already drawn, the case I 1/8 circle that follows it can be drawn using the values remaining in the parameter registers DDAR0-DDAR2.

The following formulas should be used to calculate the initial parameters of the case I 1/8 circle:

DDAR0 = DDAR0 old + DDAR1 old - DDAR2 old DDAR1 = DDAR1 old DDAR2 = 2DDAR1 old - DDAR2 old

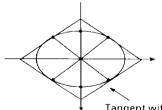

### 5.4.5 SETTING PARAMETERS for DRAWING an ELLIPSE (Ellipses parallel to the x and y axes)

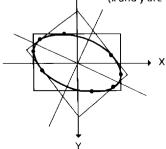

Each CDDA2 command generates a 1/8 ellipse. 1/8 ellipse is any of the following 8 sections of an ellipse:

An ellipse must satisfy the following relation:  $ax^2 + by^2 + c = 0$ (x and y are the x and y coordinates whose origin is the center of the ellipse).

Point of contact with a ± 1 gradient

$$x = \pm \sqrt{\frac{-cb}{a(a+b)}}$$

$$y = \frac{a}{b} x$$

Set the mode register bits DDAMD0 $\sim$ 4 and 7 and the parameter register DDAC in the same manner as in setting the parameters of a 1/8 circle.

DDAR0~4 should be set as follows according to the type of a 1/8 ellipse to be generated :

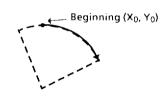

A case 11/8 elliptic arc that starts from the y axis:

Beginning (X<sub>0</sub>, Y<sub>0</sub>) / If the alli

If the ellipse starts from the x axis, the same formulas will apply, except that "a" should be read as "b" and " $X_0$ " as " $Y_0$ " and vice versa.  $a \leftrightarrow b$ ,  $X_0 \leftrightarrow Y_0$

$$\begin{array}{l} {\rm DDAR0} = 2\left( {a{x_0}^2 + b{y_0}^2 + c} \right) + 4a\left| \left| {x_0} \right| - 2b\left| \left| {y_0} \right| + 2a + b \right. \\ {\rm DDAR1} = 2a\left( {2\left| \left| {x_0} \right| + 1} \right) \\ {\rm DDAR2} = 2a\left( {2\left| \left| {x_0} \right| + 1} \right) - 4b\left| \left| {y_0} \right| \\ {\rm DDAR3} = 4a \end{array}$$

A case II1/8 elliptic arc that ends on the y axis:

DDAR4 = 4a + 4b

If the ellipse ends on the x axis, the same formulas will apply, except that "a" should be read as "b" and " $X_0$ " as " $Y_0$ ", and vice versa.  $a \leftrightarrow b$ ,  $X_0 \leftrightarrow Y_0$

```

\begin{aligned} & DDAR0 = 2\left(ax_0^2 + by_0^2 + c\right) + 2a \mid x_0 \mid -4b \mid y_0 \mid + 2a + b \\ & DDAR1 = 2b \left(-2 \mid y_0 \mid + 1\right) \\ & DDAR2 = 4a \mid x_0 \mid + 2b \left(-2 \mid y_0 \mid + 1\right) \\ & DDAR3 = 4b \\ & DDAR4 = 4a + 4b \end{aligned}

```

### 5.4.6 ELLIPSES NOT PARALLEL to X or Y AXIS (Ellipses not parallel to x or y axis)

Each CDDA2 command generates a 1/8 ellipse.

As shown below, an ellipse is divided into 8 sections as determined by the tangent lines parallel to the x and y axes and the  $\pm 1$  tangent lines.

Ellipses not parallel to x or y axis:  $ax^2 + 2bxy + cy^2 + d = 0$ (x and y are the x and y coordinates whose origin is the center of the ellipse)

Point of contact with horizontal

$$x = \pm b \sqrt{\frac{-d}{a (ac-b^2)}}$$

$$y = \mp a \sqrt{\frac{-d}{a (ac-b^2)}}$$

Point of contact with vertical

$$x = \pm c \sqrt{\frac{-d}{c (ac-b^2)}}$$

$$y = \mp b \sqrt{\frac{-d}{c (ac-b^2)}}$$

Point of contact with a -1 gradient

$$x = \pm (c - b) \sqrt{\frac{-d}{a(c-b)^2 + 2b(a-b)(c-b) + c(a-b)^2}}$$

$$y = \pm (a - b) \sqrt{\frac{-d}{a(c-b)^2 + 2b(a-b)(c-b) + c(a-b)^2}}$$

Point of contact with a + 1 gradient

$$x = \pm (c + b) \sqrt{\frac{-d}{a (b + c)^2 - 2b (a + b)(c + b) + c (a + b)^2}}$$

$$y = \pm (a + b) \sqrt{\frac{-d}{a (b + c)^2 - 2b (a + b)(c + b) + c (a + b)^2}}$$

Set the mode register bits DDAMD0~4 and the parameter register DDAC in the same manner as in setting the parameters of a 1/8 parallel ellipse. Set DDAMD7 to 1. DDAR0~5 should be set as follows according to the type of a 1/8 to be generated:

A case I 1/8 ellipses (1/8 ellipses are classified into 16 types. The classification is the same as that of 1/8 circles.)

### Type (A) in Case I

No. of

$$\Re \sim \mathbb{D}$$

defined as same as a 1/8 ellipse.

DDAR0 =

$$2(ax_0^2 + bx_0 y_0 + cy_0^2 + d)$$

+  $2a(2x_0 + 1) + b(x_0 + 2y_0 + 1) + c(2y_0 + 1)$

DDAR1 =  $2a(2x_0 + 1) + b(2y_0 + 1)$

DDAR2 =  $2a(2x_0 + 1) + b(2x_0 + 2y_0 + 1) - 4cy_0$

DDAR3 =  $4a$

DDAR4 =  $4a + 4b + 4c$

DDAR5 = 4a + 2b

Type ① Use the same formulas except the following changes:

$$\mathbf{x}_0 \to -\mathbf{x}_0$$

$$\mathbf{y}_0 \to -\mathbf{y}_0$$

Type (i) Use the same formulas except the following changes:

$$x_0 \rightarrow -x_0$$

$b \rightarrow -b$

Type № Use the same formulas except the following changes:

$$y_0 \rightarrow -y_0$$

$$b \rightarrow -b$$

Type ① Use the same formulas except the following changes:

$$x_0 \rightarrow y_0$$

$$y_0 \rightarrow -x_0$$

$$a \leftrightarrow c$$

$$b \rightarrow -b$$

Type (i) Use the same formulas except the following changes:

$$x_0 \rightarrow -y_0$$

$$y_0 \rightarrow x_0$$

$$a \leftrightarrow c$$

$$b \rightarrow -b$$

Type (i) Use the same formulas except the following changes:

$$x_0 \rightarrow y_0$$

$$y_0 \rightarrow x_0$$

$$a \leftrightarrow c$$

Type (i) Use the same formulas except the following changes:

$$\mathbf{x}_0 \rightarrow -\mathbf{y}_0$$

$$\mathbf{y}_0 \rightarrow -\mathbf{x}_0$$

$$\mathbf{a} \leftrightarrow \mathbf{c}$$

### Type (B) in Case II

$$\begin{split} DDAR0 &= 2 \left( ax_0^2 + bx_0 \ y_0 + cy_0^2 + d \right) \\ &\quad + a \left( 2x_0 + 1 \right) + b \left( 2x_0 + y_0 + 1 \right) + 2c \left( 2y_0 + 1 \right) \\ DDAR1 &= 2c \left( 2y_0 + 1 \right) + b \left( 2x_0 + 2y_0 + 1 \right) - 4ax_0 \\ DDAR2 &= 2c \left( 2y_0 + 1 \right) + b \left( 2x_0 + 2y_0 + 1 \right) - 4ax_0 \\ DDAR3 &= 4c \\ DDAR4 &= 4a + 4b + 4c \\ DDAR5 &= 2b + 4c \end{split}$$

Use the same formulas except the following changes:

$$\mathbf{x}_0 \rightarrow -\mathbf{x}_0$$

$$y_0 \rightarrow -y_0$$

Type ①

Use the same formulas except the following changes:

$$\mathbf{x}_0 \rightarrow -\mathbf{x}_0$$

Type (N)

Use the same formulas except the following changes:

$$y_0 \rightarrow -y_0$$

$$b \rightarrow -b$$

Use the same formulas except the following changes: Type ①

$$\mathbf{x}_0 \rightarrow \mathbf{y}_0$$

$$y_0 \rightarrow -x_0$$

$$\mathbf{a} \leftrightarrow \mathbf{c}$$

$$b \rightarrow -b$$

Type (1)

Use the same formulas except the following changes:

$$\mathbf{x}_0 \rightarrow -\mathbf{y}_0$$

$$\mathbf{y}_0 \to \mathbf{x}_0$$

$$a \leftrightarrow c$$

$$b \rightarrow -b$$

Type ①

Use the same formulas except the following changes:

$$\mathbf{x}_0 \rightarrow \mathbf{y}_0$$

$$y_0 \rightarrow x_0$$

$$a \leftrightarrow c$$

Type Q

Use the same formulas except the following changes:

$$\mathbf{x}_0 \rightarrow -\mathbf{y}_0$$

$$y_0 \rightarrow -x_0$$

### 5.5 MEMORY ORGANIZATION

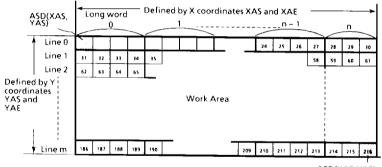

### 5.5.1 DATA ORGANIZATION of MEMORY

The FGA supports 2 buffer memories A and B, each of which has an 8-bit bus. As a result, the buffer memories are accessed by the FGA on a byte basis.

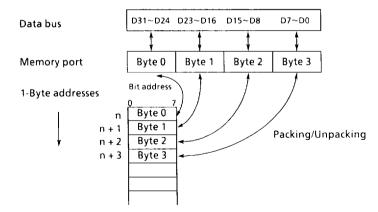

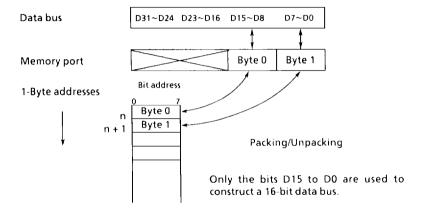

Data are transferred between the CPU and the FGA using a 32-bit or 16-bit bus. The buffer memories are accessed by the CPU either by dot (for dot-matrix drawing) or by byte (for random access, block transfer and transfer of the results of fill commands).

Data are transferred between the CPU and the buffer memories in words (over a 16-bit bus) or long words (32-bit bus) from a 1-byte memory address specified.

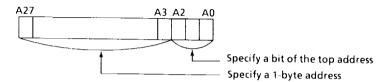

A pair of current pointers are used by the CPU to specify buffer memory addresses. The current pointer L indicates the x coordinates of memory addresses and the current pointer H indicates their y coordinates. The 3 bits A0 to A2 of the current pointer L are used to specify a particular bit of the top address.

### Address register

All bits from A0 through A27 are used for outlining and filling. In the data transfer, only the bits A3 to  $\Delta$ 27 (25 bits) are used to specify a 1-byte address.

The FGA converts words (or long words) to and from an equivalent number of bytes (this is called packing and unpacking).

### Bit assignment of 1-byte addresses

Each memory address is composed of 8 bits from bit 0 to bit 7. The bit 0 corresponds to the MSB of the data bus between the FGA and the CPU/buffer memories.

### 32-bit bus (W/-LW signal = low)

### 16-bit bus (W/-LW signal = high)

### 5.5.2 REGISTER ORGANIZATION

The FGA registers are accessed by the CPU using the register address terminals (RA5-RA0). A register can be accessed only if its number (address) is specified (except in the DMA transfer where a separate memory port is automatically selected). Each of these registers is assigned to a 1-word address, and can be accessed as determined by the width of the bus between the FGA and the CPU.

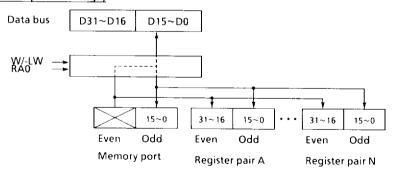

### 32-bit bus (W/-LW = low)

If the bus is composed of 32 bits, the CPU will access two 1-word addresses at the same time. As a result, two registers can be accessed if only one address is specified. If an even address n is specified, a pair of registers located in the addresses n and n+1 will be accessed. If an odd address m is specified, registers in the addresses m and m-1 will be accessed.

### 16-bit bus (W/-LW = high)

In the 16-bit configuration, the bus is composed of the bits D15-D0. This means that only one address can be accessed at one time. Either an even address or odd address must be specified to access each register.

Note however that the memory port is always assigned to an odd address in the 16-bit bus construction.

#### 5.6 BUFFER MEMORY and WORK AREA

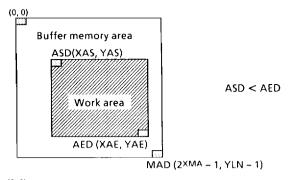

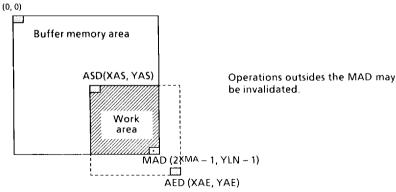

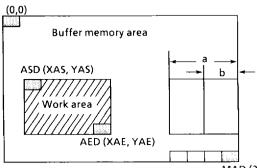

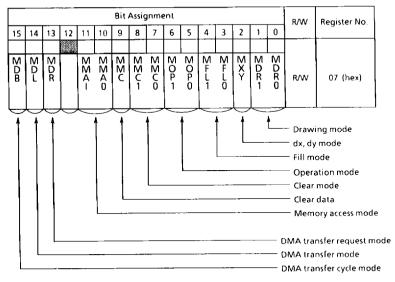

### 5.6.1 DEFINING the WORK AREA

The work area is the active field for all operations including outlining and filling. Also, this area defines data to be transferred or cleared from the buffer memories.

The work area is defined by the parameter registers ASD (Area Start Definition) and AED (Area End Definition).

The work area should be created within the buffer memory area defined by MAD. A work area that extends over the boundary is invalid. All operations outside the MAD may be also invalidated.

YLN: Y area width

See buffer memory area in

the item 4-5-5

### 5.6.2 WORK AREA for the DATA TRANSFER

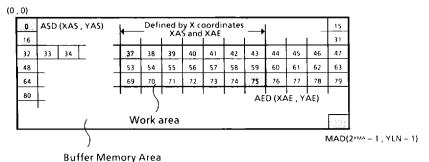

The horizontal range of the work area is defined on a byte basis by the ASD and AED registers. On the other hand, data are transferred to the CPU by word (over the 16-bit data bus) or long word (over the 32-bit data bus). This means that the size of the work area may not be divided by that of data accessible by the CPU. The discrepancy will be 1 byte in the word-based transfer, and 1 to 3 bytes in the long-word-based transfer.

To avoid this problem, the horizontal range of the work area should be defined so it consists of a number of bytes equal to a 4's multiple (or 2's multiple in the 16-bit transfer).

Objects are outlined and filled normally on a work area composed of odd bytes.

Caution should be exercised in attempting a programmed transfer using the chip select (CS) signal. If the work area is sized as shown below and the data bus is composed of 32 bits, the nth transfer cycle results in the transfer of the last 3 bytes on the line 0 28, 29 and 30 the 1st byte on the line 1 31. In this manner, 4 bytes of data will be transferred normally up to the bytes 211, 212, 213 and 214 on the last line m. However, the last cycle will cause the FGA to transfer the bytes 215 and 216, and 2 bytes' undefined data to the CPU.

If a block write transfer is executed under the same conditions, the FGA will write only the existing data of up to  $216\,$ .

AED(XAE,YAE)

Given conditions:

Bus width: 32 bits

Width of the work area: 4n + 3 bytes

#### 5.6.3 WORK AREA for the DMA TRANSFER

In the DMA transfer, the number of words to be transferred is specified by the DW register to define the active width. Normally, the active width should match the width of the work area specified by the x coordinates XAS and XAE. If the active width is smaller than the width of the work area, a specified number of words will be transferred normally. If the active area is wider than the work area, the shortage will be supplemented by undefined data as described below.

### Examples of DMA transfer)

### Example 1

- · Bus width: 16 bits (W/-LW = 1)

- · Number of words to be transferred: 3

- · Transfer mode: Line mode (Bit 14 of MOD1 = 1)

Result of a word-based transfer

37 38, 39 40, 41 42

### Example 2

- · Bus width: 16 bits (W/-LW = 1)

- · Number of words to be transferred: 4

- · Transfer mode: Line mode (Bit 14 of MOD1 = 1)

Result of a word-based transfer

37 38, 39 40, 41 42, 43 44

#### Example 3

- Bus width: 16 bits (W/-LW = 1)

- · Number of words to be transferred: 7

- · Transfer mode: Line mode (Bit 14 of MOD1 = 1)

Result of a word-based transfer

37 38, 39 40, 41 42, 43 44, 45 46, 47 32, 33 34

### Example 4

- · Bus width: 32 bits (W/-LW = 0)

- · Number of words to be transferred: 2

- · Transfer mode: Line mode (Bit 14 of MOD1 = 1)

Result of a word-based transfer

37 38, 39 40, 41 42 43 44

#### Example 5

- · Bus width: 32 bits (W/-LW = 0)

- · Number of words to be transferred: 3

- Transfer mode: Line mode (Bit 14 of MOD1 = 1)

Result of a long word-based transfer

37 38 39 40, 41 42 43 44, 45 46 47 32

#### Example 6

- Bus width: 16 bits (W/-LW = 1)

- · Number of words to be transferred: 4

- · Transfer mode: Block mode (Bit 14 of MOD1 = 0)

Result of a word-based transfer

37 38, 39 40, 41 42, 43 44

53 54, 55 56, 57 58, 59 60

69 70, 71 72, 73 74, 75 76

### Example 7

- · Bus width: 32 bits (W/-LW = 1)

- · Number of words to be transferred: 3

- Transfer mode: Block mode (Bit 14 of MOD1 = 0)

Result of a word-based transfer

37 38 39 40 ,41 42 43 44 ,45 46 47 32

53 54 55 56 ,57 58 59 60 ,61 62 63 48

69 70 71 72 ,73 74 75 76 ,77 78 79 64

The Undefined bytes are not written/read to/from the buffer memories for reading/writing. However, the FGA is accessed by the DMA controller for the number of words specified by the DW register.

#### 5.6.4 WORK AREA for a DIVIDED FONT

To fill a divided font using CFIL2-4 commands, the FGA requires an additional work area to be provided at the right end in the buffer memory area (MAD). This additional work area has the same height (defined by the y coordinates YAS and YAE) as the main work area, and a width of either a word (16 bits) or a long word (32 bits) as determined by the bus width. To process a divided font, the main work area must be located so it will not disturb the additional work area.

- Width of an additional work area in the 32bit configuration

- Width of an additional work area in the 16bit configuration

MAD (2XMA-1, YLN-1)

YLN: Y area width

See buffer memory area in

the item 5.8.5 (5).

The additional work area is created in the buffer memory A.

One additional work area is repeatedly used for all traverse sections of a divided font. Therefore, the top and the bottom of the main work areas must be unchanged for all of these sections. If the top or the bottom changes, the divided font may not be filled properly.

A font divided as shown on the left is filled in the order of  $(1) \rightarrow (2) \rightarrow (3) \rightarrow (4) \rightarrow (5) \rightarrow (6)$ . The sections (1), (2) and (3) are filled using the same additional work area, and so their main work areas must be identical in height. Similarly, the top and the bottom of the main work area must be unchanged for the sections (4), (5) and (6). The height of the main work area can be changed only after all traverse sections ((1), (2)) and (3) or (4), (5) and (6) in this case) are completed.

The left or the right edge of the main work area can be changed freely.

#### 5.6.5 RANDOM ACCESS and the BUFFER MEMORY AREA

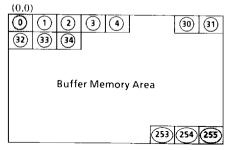

Data in the buffer memory area (MAD) can be randomly accessed by the CPU as specified by the current pointer (CP). Data are accessed either by word (2 bytes) or by long word (4 bytes) according to the bus width.

MAD (2×MA-1, YLN-1)

Over the 32-bit data bus, this buffer memory area can be randomly accessed as follows:

- When CP=0, the bytes 0, 1, 2 and 3 will be accessed. In the auto-increment mode, the access will increment the CP value to 4.

- When CP = 30, the bytes 30, 31, 32 and 33 will be accessed. In the auto-increment mode, the access will increment the CP value to 34.

- When CP = 253, the bytes 253, 254, 255 and 0 will be accessed. In the auto-increment mode, the access will increment the CP value to 0.

YLN: Y area width

See buffer memory area in

the item 5.8.5 (5).

#### 5.6.6 STRUCTURE of the RUFFER MEMORY ADDRESSES

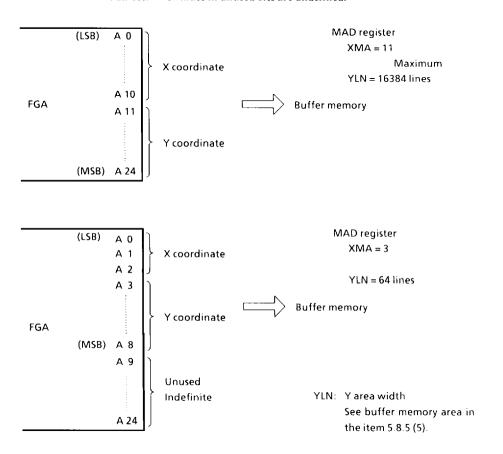

As mentioned earlier, buffer memory addresses are specified by their x-y coordinates, which are defined by the 25 bits of the current pointers. Up to 11 bits (A0 $\sim$ A10 in the figure below) can be used to indicate an X coordinate, and 14 bits (A11 $\sim$ A24) to indicate a Y coordinate.

The buffer memory area can be sized freely (to a 2's multiple in both the x and y direction) within the capacity of the memory used. The buffer memory area is specified by the parameter register MAD. If an address can be indicated without using the all bits, it will be barrel-shifted (compressed to the LSB), and converted to a linear address. The values in unused bits are undefined.

#### 5.7 RESTRICTIONS

#### 5.7.1 EXECUTION of MORE THAN 1 COMMAND

The FGA commands are located in the command register. A command can be accessed by setting a specific bit allocated to this command. Executing more than one command is disabled by the FGA to protect the internal circuits (except for CSTC and CBZ2 commands). If more than 1 bit are set, the less significant bit (bit of the smaller number) will be selected.

#### Command register

|    | Bit assignment |    |                  |                  |    |                       |                  |                  |                  |                       |           |                  |                  |                  |         |

|----|----------------|----|------------------|------------------|----|-----------------------|------------------|------------------|------------------|-----------------------|-----------|------------------|------------------|------------------|---------|

| 15 | 14             | 13 | 12               | 11               | 10 | 9                     | 8                | 7                | 6                | 5                     | 4         | 3                | 2                | 1                | 0       |

|    | 313            | 1  |                  |                  |    |                       |                  |                  |                  |                       |           |                  |                  |                  |         |

| _  |                | _  | C<br>B<br>L<br>K | C<br>M<br>C<br>L | L  | C<br>F<br>I<br>L<br>3 | F<br>I<br>L<br>2 | C<br>F<br>I<br>L | C<br>P<br>T<br>E | C<br>D<br>D<br>A<br>2 | C D D A 1 | C<br>B<br>Z<br>2 | C<br>B<br>Z<br>1 | C<br>S<br>T<br>C | C R S T |

**Priority increases**

Highest priority

- · The CRST bit has the highest priority. Any other bits will be ignored if set.

- · A CSTC command can be coincided with a command from CDDA1 to CBLK (bits 4 12).

- If the CSTC bit and the CBZ1 or CBZ2 bit are set at the same time, only the CSTC bit becomes

effective.

- · A CBLK (bits 4 12).

- In any other case where more than 1 bit are set at the same time, the FGA will select the smaller bit, and set the INTIL bit of the interrupt register.

## 2

#### 5.7.2 ACCESS by the CPU DURING COMMAND EXECUTION

When a command is being executed, the following access may be attempted by the CPU:

- (1) Access to another command

- (2) Access to other internal register

- (3) Access to the dx, dy port register

- (4) Access to the memory port register

- (1) Access to another command

If the access to another command is attempted,

- · A reset command will be always executed if accessed.

- · A CBZ2 or CSTC command will be executed if certain conditions are met.

- · Other command will be always executed if a CBZ2 command is currently executed.

In all other cases, the FGA disables the access and sets the INTIL bit of the interrupt register.

#### (2) Access to other internal register

- Mode registers (MOD1 and MOD2)

Writing to the mode registers will be disabled. If the writing is attempted, the data may be invalidated.

- · Parameter registers

#### PARAMETER REGISTERS

| COMMAN<br>EXECU                                                   |          | OPERATION MODE                                              | PARAMETER REGISTERS THAT CANNOT BE WRITTEN                                  | READ<br>OPERATION |

|-------------------------------------------------------------------|----------|-------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------|

|                                                                   | 6074     | Draw outlines in the buffer memory A/B (Bit 1 of MOD1 = 0)  | BSP, BX0, BX1, BX2, BX3, BY0, BY1, BY2, BY3, ASD, AED, CP, DS, MAD          | Possible          |

| CBZ1 or<br>CBZ2                                                   | CBZ1     | Draw noting in the buffer memory A/B<br>(Bit 1 of MOD1 = 1) | BX0, BX1, BX2, BX3, BY0, BY1, BY2, BY3<br>BSP                               | Possible          |

|                                                                   | CBZ2     |                                                             | BX0, BX1, BX2, BX3, BY0, BY1, BY2, BY3<br>BSP, BFLT                         | Possible          |

|                                                                   | CDDA1    | Draw outlines in the buffer memory A/B (Bit 1 of MOD1 = 0)  | DDARO, DDAR3, DDAR4, DDAC, ASD,<br>AED, CP, DS, MAD                         | Possible          |

| CDDA1 or                                                          |          | Draw nothing in the buffer memory A/B (Bit 1 of MOD1 = 1)   | DDARO, DDAR3, DDAR4, DDAC                                                   | Possible          |

| CDDA2                                                             | CDDA1    | Draw outlines in the buffer memory A/B (Bit 1 of MOD1 = 0)  | DDARO, DDAR1, DDAR2, DDAR3,<br>DDAR4, DDAR5, DDAC, ASD, AED, CP,<br>DS, MAD | Possible          |

|                                                                   |          | Draw nothing in the buffer memory A/B (Bit 1 of MOD1 = 1)   | DDARO, DDAR1, DDAR2,DDAR3,<br>DDAR4, DDAR5, DDAC                            | Possible          |

| G511.4.4                                                          | CD. I.C. | Request DMA transfer<br>(Bit 13 of MOD1 = 1)                | ASD, AED, CP, DS, MAD, DW                                                   | Possible          |

| CFIL1 – 4 or CBLK                                                 |          | Request no DMA transfer<br>(Bit 13 of MOD1 = 0)             | ASD, AED, CP, DS, MAD                                                       | Possible          |

| CMCL, CPTE or buffer<br>memory access<br>Bit 8 (STMBY) of SR1 = 1 |          |                                                             | ASD, AED, CP, DS, MAD                                                       | Possible          |

#### (3) Access to the dx, dy port register

If the access to the dx, dy port register is attempted.

- · Writing will be enabled only if the command being executed is CBZ2.

- · Reading will be enabled only if the command being executed is CBZ1, DDA1 or DDA2 and the mode register is set to enable the output to the CPU.

In all other cases, the FGA disables the access and sets the INTIL bit of the interrupt register.

- (4) Access to the memory port register

- · Reading/writing will be enabled if the command being executed is CBZ2.

In all other cases, the FGA disables the access and sets the INTIL bit of the interrupt register.

After setting the INTIL bit, the FGA generates the -DTACK signal to the CPU. This will terminate the bus cycle, and prevent the system from getting hung.

# 2

#### 5.7.3 ILLEGAL ACCESS

Access by the CPU

| Comm<br>Access by CPU | CBZ1      | CBZ2 | CDDA<br>1/2 | СРТЕ | CFIL1<br>~ 4 | CMCL   | CBLK       | When no<br>command<br>is being<br>executed |         |

|-----------------------|-----------|------|-------------|------|--------------|--------|------------|--------------------------------------------|---------|

|                       | CRST      | ()   | ()          | ()   | $\odot$      | ()     | ()         | $\bigcirc$                                 | ()      |

|                       | CSTC      | ×    | ×           | 0    | ()           | ()     | ()         | ()                                         | $\circ$ |

|                       | CBZ1      | ×    | ×           | ×    | ×            | ×      | ×          | ×                                          | $\circ$ |

| C                     | CBZ2      | ×    | ×           | ()   | ()           | ()     | $\bigcirc$ | $\odot$                                    | ()      |

| Command register      | CDDA1/2   | ×    | 0           | ×    | ×            | ×      | ×          | ×                                          | ()      |

|                       | CPTE      | ×    | 0           | ×    | ×            | ×      | ×          | ×                                          | 0       |

|                       | CFIL1 ~ 4 | ×    | ()          | ×    | ×            | ×      | ×          | ×                                          | 0       |

|                       | CMCL      | ×    | ()          | ×    | ×            | ×      | ×          | × _                                        | ()      |

|                       | CBLK      | ×    | ()          | ×    | ×            | ×      | ×          | ×                                          | ()      |

| Internal              | R         | 0    | ()          | ()   | $\odot$      | ()     | ()         | ()                                         | ()      |

| registers             | w         | 0    | ()          | ()   | ()           | $\cap$ | ()         | ()                                         | ()      |

| dx, dy port           | R         | - 11 | ×           | f l  | ×            | ×      | ×          | ×                                          | ×       |

| register              | w         | ×    | ()          | ×    | ×            | ×      | ×          | ×                                          | ( )     |

| Memory port           | R         | ×    | ()          | ×    | ×            | []     | ×          | []                                         | ()      |

| register              | w         | ×    | ()          | ×    | ×            | ×      | ×          | 1                                          | ()      |

- Enabled

- x Disabled (Illegal access)

- [ ] Enabled or disabled according to the mode selected

- If the access is disabled, the FGA will generate the -DTACK signal to the CPU and set the INTIL bit of the interrupt register. All commands (except RESET) will be ignored if accessed. Reading of an internal register, the memory port or dx, dy port register will result in the reading of undefined data. Writing will be disabled.

- · If no command is being executed, the memory port register can be accessed only in the random mode. DMA transfer is disabled.

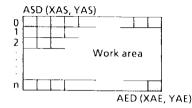

| 5.8   | REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.8.1 | DESCRIPTION of the REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | [] Command register (W)  The FGA supports 13 basic commands including CBZ, DDA and CFIL. To execute a command, set the bit assigned to this command.                                                                                                                                                                                                                                                                                                         |

|       | ☐ Mode registers (R/W)  The mode registers specify the mode of operation to be executed by a command. They must be set before a command is executed.                                                                                                                                                                                                                                                                                                         |

|       | ☐ Parameter registers (R/W)                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | Parameter registers are located in the Bezier block, DDA block and Fill block. They indicate parameters necessary to execute a command. They must be set before a command is executed.                                                                                                                                                                                                                                                                       |

|       | 10 parameter registers in the Bezier block  - BSP, BFLT, BX0, BX1, BX2, BX3, BY0, BY1, BY2, BY3                                                                                                                                                                                                                                                                                                                                                              |

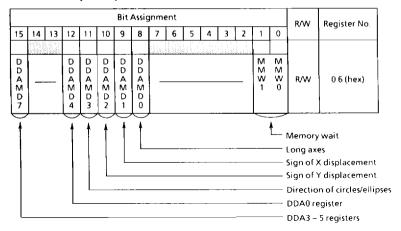

|       | 7 parameter registers in the DDA block - DDAR0, DDAR1, DDAR2, DDAR3, DDAR4, DDAR5, DDAC                                                                                                                                                                                                                                                                                                                                                                      |

|       | 6 parameter registers in the Fill block - ASD, AED, CP, DS, MAD, DW                                                                                                                                                                                                                                                                                                                                                                                          |

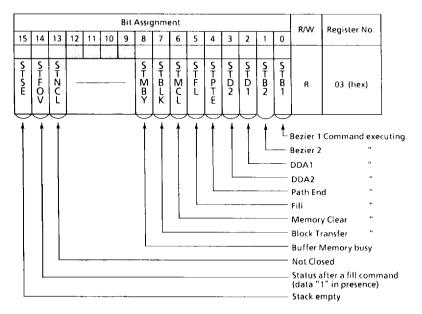

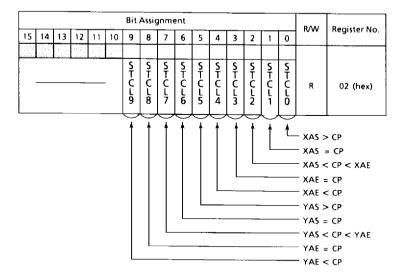

|       | ☐ Status registers (R)                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | The status registers serve as status flags that indicate the states of the Bezier, DDA and Fill blocks.<br>Up to 22 states can be indicated to help effective control by the CPU.                                                                                                                                                                                                                                                                            |

|       | ☐ Interrupt register (R)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

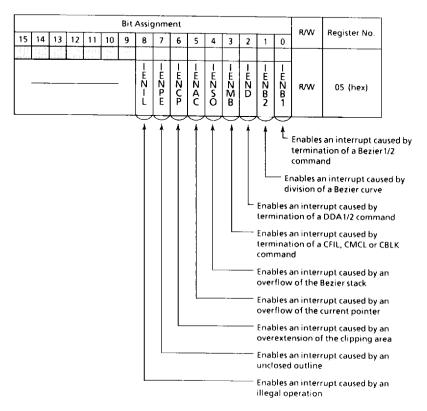

|       | It supports 9 types of interrupts to enable various operations such as ending the current command, dividing a line, processing an overflow of the stack, and checking the clipping area. An interrupt is requested when the applicable bit is set. If an interrupt bit is set, the register will generate an interrupt request (-IRQ) signal to allow the CPU to process the interrupt routine. An interrupt can be reset by reading the interrupt register. |

|       | ☐ Interrupt enable register (R/W)                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | This register enables interrupts on a selective basis. Each bit corresponds to a specific bit of the                                                                                                                                                                                                                                                                                                                                                         |

TC8511F-44 250190 170

interrupt register.

| Memory access port register (R/W)  The buffer memories are accessed by the CPU through the memory port. The buffer memories are |

|---------------------------------------------------------------------------------------------------------------------------------|

| accessed when:                                                                                                                  |

| (1) The result of a fill command is transferred to the CPU;                                                                     |

| (2) A block transfer is executed; or                                                                                            |

| (3) Random data access is selected.                                                                                             |

| dx, dy port register (R/W)                                                                                                      |

| This register is used by the CPU to read/write displacement data (dx, dy) from/to the buffer memories.                          |

| To access any of these registers, the CPU must specify its register number using the RA5 - RA0                                  |

| terminals.                                                                                                                      |

2

#### 5.8.3 LIST of the REGISTERS

| Register<br>NO | Register name                | Abbreviation | R/W | Τ                |                       |                       |                       |                       |                       | Ві                    | t Ass                 | ignm                  | ent                   |                        |                       |                         |                       |                  | _                      |

|----------------|------------------------------|--------------|-----|------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|-----------------------|-------------------------|-----------------------|------------------|------------------------|

|                |                              |              |     | 15               | 14                    | 1.3                   | 12                    | 11                    | 10                    | 9                     | В                     | 7                     | 6                     | 5                      | 4                     | 3                       | 2                     | 1                | 0                      |