# MPC962308

# **3.3 V Zero Delay Buffer**The MPC962308 is a 3.3 V Zero Delay Buffer designed to distribute

The MPC962308 is a 3.3 V Zero Delay Buffer designed to distribute high-speed clocks in PC, workstation, datacom, telecom and other high-performance applications. The MPC962308 uses an internal PLL and an external feedback path to lock its low-skew clock output phase to the reference clock phase, providing virtually zero propagation delay. The input-to-output skew is guaranteed to be less than 250 ps and output-to-output skew is guaranteed to be less than 200 ps.

#### **Features**

- 1:8 outputs LVCMOS zero-delay buffer

- Zero input-output propagation delay, adjustable by the capacitive load on FBK input

- Multiple Configurations, see Table 2. Available MPC962308 Configurations

- Multiple low-skew outputs

- 200 ps max output-output skew

- 700 ps max device-device skew

- · Two banks of four outputs, output tristate control by two select inputs

- Supports a clock I/O frequency range of 10 MHz to 133 MHz

- Low jitter, 200 ps max cycle-cycle (-1, -1H, -4, -5H)

- ±250 ps static phase offset (SPO)

- · 16-pin SOIC package or 16-pin TSSOP package

- Single 3.3 V supply

- Ambient temperature range: –40°C to +85°C

- Compatible with the CY2308 and CY23S08

- · Spread spectrum compatible

# REFERENCE PROPERTY OF THE PROP

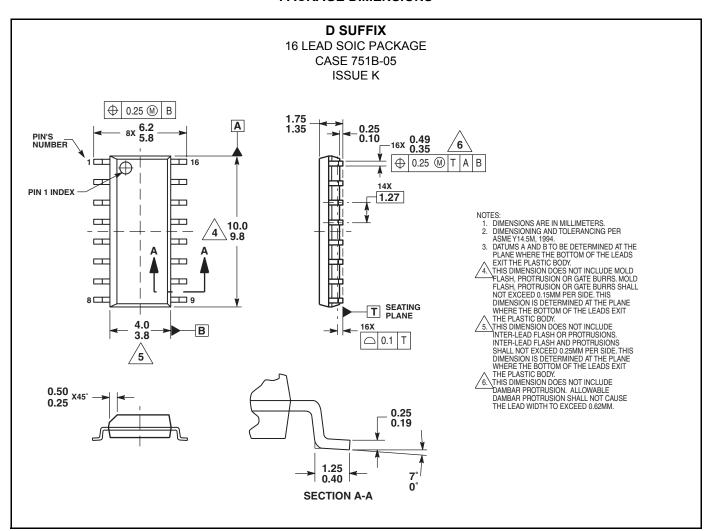

# **D SUFFIX** 16-LEAD SOIC PACKAGE CASE 751B-05

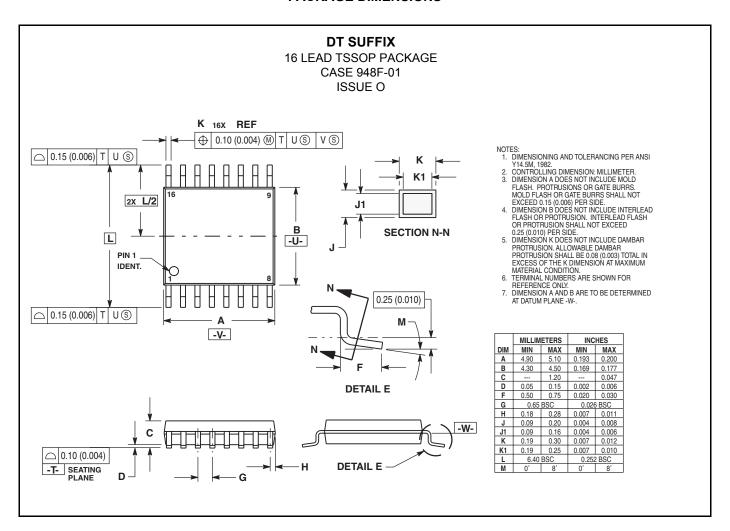

**DT SUFFIX** 16-LEAD TSSOP PACKAGE CASE 948F-01

### **Functional Description**

The MPC962308 has two banks of four outputs each which can be controlled by the select inputs as shown in **Table 1. Select Input Decoding**. Bank B can be tristated if all of the outputs are not required. The select inputs also allow the input clock to be directly applied to the output for chip and system testing purposes. The MPC962308 PLL enters a power down state when there are no rising edges on the REF input. During this state, all of the outputs are in tristate and there is less than 50  $\mu$ A of current draw. The PLL shuts down in two additional cases explained in **Table 1. Select Input Decoding**.

Multiple MPC962308 devices can accept and distribute the same input clock throughout the system. In this situation, the difference between the output skews of two devices will be less than 700 ps.

The MPC962308 is available in five different configurations as shown in **Table 2. Available MPC962308 Configurations**. In the MPC962308-1, the reference frequency is reproduced by the PLL and provided at the outputs. A high drive version of this configuration, the MPC962308-1H, is available to provide faster rise and fall times of the device.

The MPC962308-2 provides 2X and 1X the reference frequency at the output banks. In addition, the MPC962308-3 provides 4X and 2X the reference frequency at the output banks. The output banks driving the feedback will determine the different configurations of the above devices. The MPC962308-4 provides outputs 2X the reference frequency. The MPC962308-5H is a high drive version with outputs of REF/2.

The MPC962308 is fully 3.3 V compatible and requires no external components for the internal PLL. All inputs accept LVCMOS signals while the outputs provide LVCMOS compatible levels with the capability to drive terminated 50  $\Omega$  transmission lines on the incident edge. Depending on the configuration, the device is offered in a 16-lead SOIC or 16-lead TSSOP package.

Rev 3, 08/2004

Order number: MPC962308

# Semic

#### **Block Diagram ⊠** FBK PLL REF ⊠ MUX -⊠ CLKA1 ⊠ CLKA2 Extra Divider (-3, -4) -⊠ CLKA3 Extra Divider (-5H) ⊠ CLKA4 S2 🖾 Select Input Decoding S1 ⊠ /2 CLKB1 \_\_ CLKB2 CLKB3 \_ CLKB4 Extra Divider (-2, -3)

## Pin Configuration

**Table 1. Select Input Decoding**

| S2 | S1 | CLOCK A1—A4         | CLOCK B1—B4         | Output Source | PLL Shutdown |

|----|----|---------------------|---------------------|---------------|--------------|

| 0  | 0  | Three-State         | Three-State         | PLL           | Y            |

| 0  | 1  | Driven              | Three-State         | PLL           | N            |

| 1  | 0  | Driven <sup>1</sup> | Driven <sup>1</sup> | Reference     | Y            |

| 1  | 1  | Driven              | Driven              | PLL           | N            |

<sup>1.</sup> Outputs inverted on MPC962308-2 in bypass mode, S2=1 and S1=0.

Table 2. Available MPC962308 Configurations

| Device       | Feedback From    | Bank A Frequency | Bank B Frequency                      |

|--------------|------------------|------------------|---------------------------------------|

| MPC962308-1  | Bank A or Bank B | Reference        | Reference                             |

| MPC962308-1H | Bank A or Bank B | Reference        | Reference                             |

| MPC962308-2  | Bank A           | Reference        | Reference/2                           |

| MPC962308-2  | Bank B           | 2 X Reference    | Reference                             |

| MPC962308-3  | Bank A           | 2 X Reference    | Reference or Reference <sup>[1]</sup> |

| MPC962308-3  | Bank B           | 4 X Reference    | 2 X Reference                         |

| MPC962308-4  | Bank A or Bank B | 2 X Reference    | 2 X Reference                         |

| MPC962308-5H | Bank A or Bank B | Reference /2     | Reference /2                          |

<sup>1.</sup> Output phase is indeterminate (0° or 180° from input clock). If phase integrity is required, use the MPC962308-2.

# **Table 3. Pin Description**

| Pin | Signal             | Description                                   |

|-----|--------------------|-----------------------------------------------|

| 1   | REF <sup>1</sup>   | Input reference frequency, 5 V tolerant input |

| 2   | CLKA1 <sup>2</sup> | Clock output, Bank A                          |

| 3   | CLKA2 <sup>2</sup> | Clock output, Bank A                          |

| 4   | V <sub>DD</sub>    | 3.3 V supply                                  |

| 5   | GND                | Ground                                        |

| 6   | CLKB1 <sup>2</sup> | Clock output, Bank B                          |

| 7   | CLKB2 <sup>2</sup> | Clock output, Bank B                          |

| 8   | S2 <sup>3</sup>    | Select input, bit 2                           |

| 9   | S1 <sup>3</sup>    | Select input, bit 1                           |

| 10  | CLKB3 <sup>2</sup> | Clock output, Bank B                          |

| 11  | CLKB4 <sup>2</sup> | Clock output, Bank B                          |

| 12  | GND                | Ground                                        |

| 13  | V <sub>DD</sub>    | 3.3 V supply                                  |

| 14  | CLKA3 <sup>2</sup> | Clock output, Bank A                          |

| 15  | CLKA4 <sup>2</sup> | Clock output, Bank A                          |

| 16  | FBK                | PLL feedback input                            |

- 1. Weak pull-down.

- 2. Weak pull-down on all outputs.

- 3. Weak pull-ups on these inputs.

# **Table 4. Maximum Ratings**

| Characteristics                                         | Value                        | Unit |

|---------------------------------------------------------|------------------------------|------|

| Supply Voltage to Ground Potential                      | -0.5 to +3.9                 | V    |

| DC Input Voltage (Except REF)                           | –0.5 to V <sub>DD</sub> +0.5 | V    |

| DC Input Voltage REF                                    | -0.5 to 5.5                  | V    |

| Storage Temperature                                     | –65 to +150                  | °C   |

| Junction                                                | 150                          | °C   |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) | >2000                        | V    |

Table 5. Operating Conditions for MPC962308-X Industrial Temperature Devices

| Parameter       | Description                                 | Min | Max | Unit |

|-----------------|---------------------------------------------|-----|-----|------|

| $V_{DD}$        | Supply Voltage                              | 3.0 | 3.6 | V    |

| T <sub>A</sub>  | Operating Temperature (Ambient Temperature) | -40 | 85  | °C   |

| C <sub>L</sub>  | Load Capacitance, below 100 MHz             |     | 30  | pF   |

|                 | Load Capacitance, from 100 MHz to 133 MHz   |     | 15  | pF   |

| C <sub>IN</sub> | Input Capacitance <sup>1</sup>              |     | 7   | pF   |

<sup>1.</sup> Applies to both REF clock and FBK.

# Table 6. Electrical Characteristics for MPC962308-X Industrial Temperature Devices<sup>1</sup>

| 50.0         | V<br>V                               |

|--------------|--------------------------------------|

| 50.0         | _                                    |

| 50.0         | ^                                    |

|              | μΑ                                   |

| 100.0        | μА                                   |

| 0.4          | V                                    |

|              | V                                    |

| 25.0         | μА                                   |

| 45.0         | mA                                   |

| 70(-1H, -5H) | mA                                   |

| 35.0         | mA                                   |

| 20.0         | mA                                   |

|              | 25.0<br>45.0<br>70(-1H, -5H)<br>35.0 |

<sup>1.</sup> All parameters are specified with loaded outputs.

<sup>2.</sup> Parameter is guaranteed by design and characterization. Not 100% tested in production.

Table 7. Switching Characteristics for MPC962308-X Industrial Temperature Devices<sup>1</sup>

| Parameter         | Name                                                                                    | Test Conditions                                                            | Min  | Тур | Max   | Unit |

|-------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|-----|-------|------|

| t <sub>1</sub>    | Output Frequency                                                                        | 30-pF load, All devices                                                    | 10   |     | 100   | MHz  |

| t <sub>1</sub>    | Output Frequency <sup>2</sup>                                                           | 20-pF load, -1H, -5H devices                                               | 10   |     | 133.3 | MHz  |

| t <sub>1</sub>    | Output Frequency <sup>2</sup>                                                           | 15-pF load, -1, -2, -3, -4 devices                                         | 10   |     | 133.3 | MHz  |

|                   | Duty Cycle <sup>2</sup> = t <sub>2</sub> ÷ t <sub>1</sub><br>(-1, -2, -3, -4, -1H, -5H) | Measured at 1.4 V, FOUT =66.66 MHz<br>30-pF load                           | 40.0 |     | 60.0  | %    |

|                   | Duty Cycle <sup>2</sup> = $t_2 \div t_1$<br>(-1, -2, -3, -4, -1H, -5H)                  | Measured at 1.4 V, FOUT <50.0 MHz<br>15-pF load                            | 45.0 |     | 55.0  | %    |

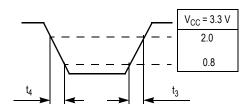

| t <sub>3</sub>    | Rise Time <sup>2</sup> (-1, -2, -3, -4)                                                 | Measured between 0.8 V and 2.0 V, 30-pF load                               |      |     | 2.50  | ns   |

|                   | Rise Time <sup>2</sup> (-1, -2, -3, -4)                                                 | Measured between 0.8 V and 2.0 V, 15-pF load                               |      |     | 1.50  | ns   |

|                   | Rise Time <sup>2</sup><br>(-1H, -5H)                                                    | Measured between 0.8 V and 2.0 V, 30-pF load                               |      |     | 1.50  | ns   |

| t <sub>4</sub>    | Fall Time <sup>2</sup> (-1, -2, -3, -4)                                                 | Measured between 0.8 V and 2.0 V, 30-pF load                               |      |     | 2.50  | ns   |

|                   | Fall Time <sup>2</sup> (-1, -2, -3, -4)                                                 | Measured between 0.8 V and 2.0 V,<br>15-pF load                            |      |     | 1.50  | ns   |

|                   | Fall Time <sup>2</sup><br>(-1H, -5H)                                                    | Measured between 0.8 V and 2.0 V, 30-pF load                               |      |     | 1.25  | ns   |

|                   | Output-to-Output Skew on same Bank (-1, -2, -3, -4) <sup>2</sup>                        | All outputs equally loaded                                                 |      |     | 200   | ps   |

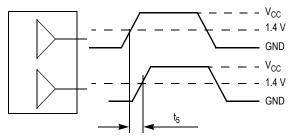

| t <sub>5</sub>    | Output-to-Output Skew (-1H, -5H)                                                        | All outputs equally loaded                                                 |      |     | 200   | ps   |

|                   | Output Bank A to Output<br>Bank B Skew (-1, -4, -5H)                                    | All outputs equally loaded                                                 |      |     | 200   | ps   |

|                   | Output Bank A to Output<br>Bank B Skew (-2, -3)                                         | All outputs equally loaded                                                 |      |     | 400   | ps   |

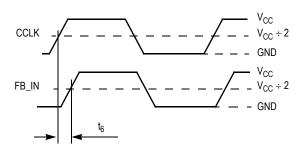

| t <sub>6</sub>    | Delay, REF Rising Edge to FBK Rising Edge <sup>2</sup>                                  | Measured at V <sub>DD</sub> /2                                             |      | 0   | ±250  | ps   |

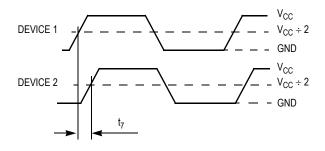

| t <sub>7</sub>    | Device-to-Device Skew <sup>2</sup>                                                      | Measured at V <sub>DD</sub> /2 on the FBK pins of devices                  |      | 0   | 700   | ps   |

| t <sub>8</sub>    | Output Slew Rate <sup>2</sup>                                                           | Measured between 0.8 V and 2.0 V on -1H, -5H device using Test Circuit # 2 | 1    |     |       | V/ns |

| tu                | Cycle-to-Cycle Jitter<br>(-1, -1H, -4, -5H) <sup>2</sup>                                | Measured at 66.67 MHz, loaded outputs, 15-pF load                          |      |     | 200   | ps   |

|                   |                                                                                         | Measured at 66.67 MHz, loaded outputs, 30-pF load                          |      |     | 200   | ps   |

|                   |                                                                                         | Measured at 133.3 MHz, loaded outputs, 15 pF load                          |      |     | 100   | ps   |

| t <sub>J</sub>    | Cycle-to-Cycle Jitter (-2, -3) <sup>2</sup>                                             | Measured at 66.67 MHz, loaded outputs 30-pF load                           |      |     | 400   | ps   |

|                   |                                                                                         | Measured at 66.67 MHz, loaded outputs<br>15-pF load                        |      |     | 400   | ps   |

| t <sub>LOCK</sub> | PLL Lock Time <sup>2</sup>                                                              | Stable power supply, valid clocks presented on REF and FBK pins            |      |     | 1.0   | ms   |

<sup>1.</sup> All parameters are specified with loaded outputs.

<sup>2.</sup> Parameter is guaranteed by design and characterization. Not 100% tested in production.

# **APPLICATIONS INFORMATION**

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device

Figure 1. Output-to-Output Skew t<sub>SK(O)</sub>

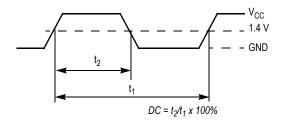

The time from the PLL controlled edge to the non-controlled edge, divided by the time between PLL controlled edges, expressed as a percentage

Figure 3. Output Duty Cycle (DC)

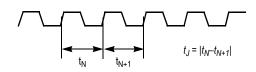

The variation in cycle time of a signal between adjacent cycles, over a random sample of adjacent cycle pairs

Figure 5. Cycle-to-Cycle Jitter

Figure 2. Static Phase Offset Test Reference

Figure 4. Device-to-Device Skew

**Figure 6. Output Transition Time Test Reference**

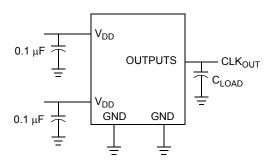

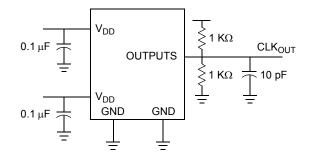

# Test Circuit #1

Test Circuit for all parameters except t<sub>8</sub>

## Test Circuit #2

Test Circuit for t<sub>8</sub>, Output slew rate on -1H, -5 device

# Ordering Information (Available)

| Ordering Code    | Package Name | Package Type                         |

|------------------|--------------|--------------------------------------|

| MPC962308D-1     | D16          | 16-pin 150-mil SOIC                  |

| MPC962308D-1R2   | D16          | 16-pin 150-mil SOIC — Tape and Reel  |

| MPC962308D-1H    | D16          | 16-pin 150-mil SOIC                  |

| MPC962308D-1HR2  | D16          | 16-pin 150-mil SOIC — Tape and Reel  |

| MPC962308DT-1H   | DT16         | 16-pin 150-mil TSSOP                 |

| MPC962308DT-1HR2 | DT16         | 16-pin 150-mil TSSOP — Tape and Reel |

| MPC962308D-2     | D16          | 16-pin 150-mil SOIC                  |

| MPC962308D-2R2   | D16          | 16-pin 150-mil SOIC — Tape and Reel  |

# **Ordering Information (Planned)**

| Ordering Code    | Package Name | Package Type                         |

|------------------|--------------|--------------------------------------|

| MPC962308D-3     | D16          | 16-pin 150-mil SOIC                  |

| MPC962308D-3R2   | D16          | 16-pin 150-mil SOIC — Tape and Reel  |

| MPC962308D-4     | D16          | 16-pin 150-mil SOIC                  |

| MPC962308D-4R2   | D16          | 16-pin 150-mil SOIC — Tape and Reel  |

| MPC962308D-5H    | D16          | 16-pin 150-mil SOIC                  |

| MPC962308D-5HR2  | D16          | 16-pin 150-mil SOIC — Tape and Reel  |

| MPC962308DT-5H   | DT16         | 16-pin 150-mil TSSOP                 |

| MPC962308DT-5HR2 | DT16         | 16-pin 150-mil TSSOP — Tape and Reel |

# **PACKAGE DIMENSIONS**

# **PACKAGE DIMENSIONS**

**NOTES**

**NOTES**

# Freescale Semiconductor, Inc.

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2004

### HOW TO REACH US:

USA/EUROPE/LOCATIONS NOT LISTED: Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130 JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

HOME PAGE: http://motorola.com/semiconductors