This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

# ISO-CMOS MT3070/71/74/75 Wide Dynamic Range DTMF Receiver

Preliminary Information

#### **Features**

- 45 dB dynamic range

- Simultaneous DTMF and supervisory tone detection (MT3070/MT3071)

- Powerdown mode

- 4-bit binary serial data output

- For use with microprocessor controlled guard time (MT3070/MT3074)

- Internal guard time circuitry (MT3071/MT3075)

## **Applications**

- Integrated telephone answering machine

- End-to-end signalling

# Description

The MT3070/MT3071/MT3074/MT3075 is a high performance DTMF Receiver which decodes all 16 DTMF tone pairs into a 4-bit binary code. The device incorporates an AGC for wide dynamic range which is suitable for end-to-end signalling. The MT3070/MT3071 also indicates the presence of all supervisory tones using internal detection circuitry. The MT3074/MT3075 does not detect the presence of supervisory tones. The powerdown function provides low standby current. The MT3070/MT3074 is useful in applications where DTMF validation period is determined by external control. The

MT3071/MT3075 uses internal counters to provide a preset DTMF validation period. The MT3070/MT3071/MT3074/MT3075 uses a crystal or a ceramic resonator to complete the oscillator circuit.

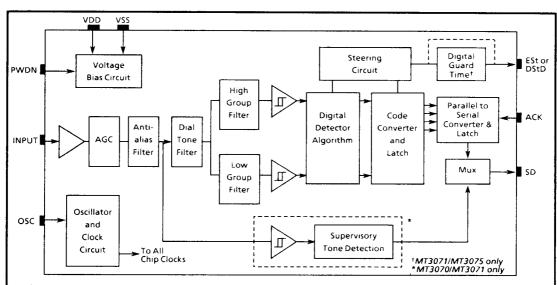

Figure 1 - Functional Block Diagram

# **Absolute Maximum Ratings**<sup>1</sup>

|   | Parameter                              | Symbol                           | Min                   | Max                   | Units |

|---|----------------------------------------|----------------------------------|-----------------------|-----------------------|-------|

| 1 | DC Power Supply Voltage                | V <sub>DD</sub> -V <sub>SS</sub> |                       | 6                     | V     |

| 2 | Voltage on any pin (other than supply) | V <sub>I/O</sub>                 | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V     |

| 3 | Current at any pin (other than supply) | I <sub>1/O</sub>                 |                       | 10                    | mA    |

| 4 | Storage temperature                    | T <sub>STG</sub>                 | - 65                  | + 150                 | °C    |

| 5 | Package power dissipation              | P <sub>D</sub>                   |                       | 500                   | mW    |

<sup>&</sup>lt;sup>†</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied. Derate above 85 °C at 9 mW / °C. All leads soldered to board.

# Recommended Operating Conditions - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated

|   | Parameter                      | Sym             | Min  | Тур      | Max  | Units | Test Conditions      |

|---|--------------------------------|-----------------|------|----------|------|-------|----------------------|

| 1 | Positive Power Supply          | V <sub>DD</sub> | 4.75 | 5.0      | 5.25 | V     | V <sub>SS</sub> = 0V |

| 2 | Oscillator Clock Frequency     | fc              |      | 4.194304 |      | MHz   |                      |

| 3 | Oscillator Frequency Tolerance | Δfc             |      | ± 0.1    |      | %     |                      |

| 4 | Operating temperature          | То              | -40  | 25       | + 85 | °C    |                      |

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing

# DC Electrical Characteristics- Over recommended operating conditions unless otherwise stated

|    | Characteristics                            | Sym             | Min                  | Тур≠ | Max                   | Units | Test Conditions                            |

|----|--------------------------------------------|-----------------|----------------------|------|-----------------------|-------|--------------------------------------------|

| 1  | Operating supply current                   | I <sub>DD</sub> |                      | 3.0  |                       | mA    |                                            |

| 2  | Standby supply current                     | IDDQ            |                      |      | 100                   | μΑ    | PWDN = V <sub>DD</sub>                     |

| 3  | Input High Voltage<br>(except OSC Input)   | V <sub>IH</sub> | V <sub>DD</sub> -1.5 |      |                       | ٧     |                                            |

| 4  | Input High Voltage<br>(for OSC Input only) | V <sub>1H</sub> | V <sub>DD</sub> -1.0 |      |                       | ٧     |                                            |

| 5  | Input Low Voltage                          | VIL             |                      |      | V <sub>SS</sub> + 1.5 | ٧     |                                            |

| 6  | Input Leakage Current<br>(Pins 2 & 6)      |                 |                      | 0.1  |                       | μΑ    |                                            |

| 7  | Input impedance (Pin 1)                    | R <sub>IN</sub> | 10                   |      |                       | kΩ    |                                            |

| 8  | Input impedance (Pin 3)                    | R <sub>IN</sub> |                      | 4    |                       | kΩ    |                                            |

| 9  | Output high (source) current               | Іон             | 0.4                  |      |                       | mA    | $V_{OUT} = V_{DD}$ -0.4V (SD,ESt,DStD)     |

| 10 | Output low (sink) current                  | loL             | 1.0                  |      |                       | mA    | $V_{OUT} = V_{SS} + 0.4V$<br>(SD,ESt,DStD) |

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

# AC Electrical Characteristics- over recommended operating conditions unless otherwise stated

|    | Characteristics                                      | Sym              | Min          | Typ‡ | Max                                     | Units | Test Conditions*      |

|----|------------------------------------------------------|------------------|--------------|------|-----------------------------------------|-------|-----------------------|

| 1  | Valid input signal level (each tone of composite     |                  | -45          |      | 0                                       | dBm   | 1,2,3,5,6,9           |

|    | signal).                                             |                  | 4.36         |      | 775                                     |       | 1,2,3,5,6,9           |

| 2  | Positive twist accept                                |                  |              |      | 6                                       | dB    | 1,2,3,4,9,14          |

| 3  | Negative twist accept                                |                  |              |      | 6                                       | dB    | 1,2,3,4,9,14          |

| 4  | Frequency deviation accept                           |                  | ± 1.5% ± 2Hz |      | ***                                     |       | 1,2,3, 5, 9           |

| 5  | Frequency deviation reject                           |                  | ± 3.5%       |      |                                         |       | 1,2,3, 5, 9           |

| 6  | Third tone tolerance                                 |                  |              | - 16 |                                         | dB    | 1,2,3,4,5,9, 12       |

| 7  | Noise tolerance                                      |                  |              | - 12 |                                         | dB    | 7,9, 10               |

| 8  | Dial tone tolerance                                  |                  |              | + 22 |                                         | dB    | 8, 9, 11              |

| 9  | Supervisory tones detect level (Total power)         |                  |              | -30  |                                         | dBm   | 13 for<br>MT3070/3071 |

| 10 | Supervisory tones non-<br>detect level (Total power) |                  |              | -35  | , , , , , , , , , , , , , , , , , , , , | dBm   | 13 for<br>MT3070/3071 |

| 11 | Supervisory tone integrator attack time              | t <sub>SA</sub>  |              | 1.0  |                                         | ms    | for<br>MT3070/3071    |

| 12 | Supervisory tones integrator decay time              | t <sub>SD</sub>  |              | 500  |                                         | ms    | for<br>MT3070/3071    |

| 13 | Tone present detect time (ESt)                       | t <sub>DP</sub>  | 3            |      | 20                                      | ms    | for<br>MT3070/3074    |

| 14 | Tone absent detect time (ESt)                        | t <sub>DA</sub>  | 0.5          |      | 20                                      | ms    | for<br>MT3070/3074    |

| 15 | Tone duration accept (DStD)                          | t <sub>REC</sub> |              |      | 40                                      | ms    | for<br>MT3071/3075    |

| 16 | Tone duration reject (DStD)                          | t <sub>RÉC</sub> | 20           |      |                                         | ms    | for<br>MT3071/3075    |

| 17 | Interdigit pause accept (DStD)                       | t <sub>iD</sub>  |              |      | 40                                      | ms    | for<br>MT3071/3075    |

| 18 | Interdigit pause reject<br>(DStD)                    | t <sub>DO</sub>  | 20           |      |                                         | ms    | for<br>MT3071/3075    |

| 19 | Data shift rate (ACK)<br>duty cycle 40%-60%          |                  |              |      | 1                                       | MHz   |                       |

| 20 | Propagation delay (ACK to Data)                      | t <sub>PAD</sub> |              | 100  |                                         | ns    |                       |

| 21 | Set-up time delay (ESt/DStD to ACK)                  | t <sub>DL</sub>  | 0            |      |                                         | ns    |                       |

| 22 | Data hold time (ACK to SD)                           | t <sub>DH</sub>  | 30           |      |                                         | ns    |                       |

<sup>\*</sup>Typical figures are at 25 °C and are for design aid only: not guaranteed and not subject to production testing

<sup>\*</sup> Test Conditions

<sup>1.</sup> dBm = decibels above or below a reference power of 1 mW into a 600 ohm load

<sup>2.</sup> Digit sequence consists of all DTMF tones.

<sup>3.</sup> Tone duration = 40 ms, tone pause = 40 ms

<sup>3.</sup> Tone duration = 40 ms, tone pause = 40 ms.

4. Signal condition consists of nominal DTMF frequencies.

5. Both tones in composite signal have an equal amplitude.

6. Tone pair is deviated by ±1.5 % ± 2 Hz.

7. Bandwidth limited (3 kHz) Gaussian noise.

8. The precise dial tone frequencies are 350 Hz and 440 Hz (± 2 %).

9. For an error rate of better than 1 in 10,000. External guard time for MT3070/MT3074 = 20 ms.

Referenced to lowest level frequency component in DTMF signal.

Referenced to the minimum valid accept level.

<sup>12.</sup> Worst case interfering frequency

13. For testing purposes a C-message filter is connected at the input

14. Both tones must be within valid input signal range.

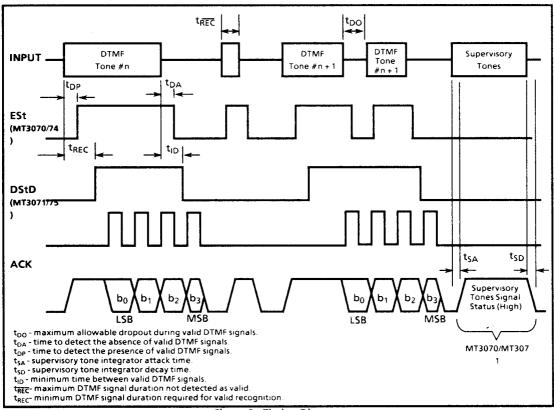

Figure 2 - Timing Diagram

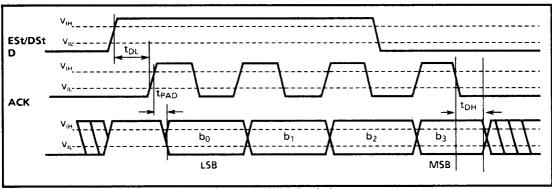

Figure 3 - ACK to SD Timing

**Pin Description**

| Pin<br># | Name                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

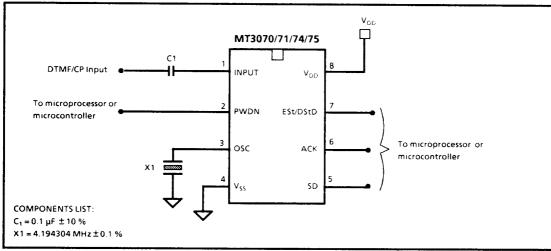

| 1        | INPUT                       | Audio Input. Input signal must be AC coupled as shown in Fig.4.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2        | PWDN                        | Power Down Input. A logic high on this pin will power down the device to reduce power consumption. The ACK pin must be logic low before a logic high is applied on this pin. For normal operation, PWDN pin must be logic low.                                                                                                                                                                                                                                                       |

| 3        | osc                         | <ol> <li>Oscillator Input. This pin can either be driven by:</li> <li>an external digital output with defined input logic levels. No coupling capacitor is required.</li> <li>connecting a crystal between OSC Input and V<sub>SS</sub>. No loading capacitor is required.</li> <li>connecting a ceramic resonator between OSC Input and V<sub>SS</sub>. No loading capacitor is required.</li> <li>Frequency of oscillation should be maintained at 4.194304 MHz ± 0.1%.</li> </ol> |

| 4        | Vss                         | Ground. (0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5        | SD                          | Serial Data Output. In the absence of ACK input signal, a logic high output indicates the presence of tones: DTMF or supervisory tones (MT3070/MT3071 only). If ESt is high and the ACK pulse sequence is applied, the SD output provides a 4-bit binary code representing the decoded DTMF digit. Refer to Fig. 3.                                                                                                                                                                  |

| 6        | ACK                         | Acknowledge Pulse Input. After ESt or DStD goes high, applying a sequence of four pulses on this pin will shift out four bits on the SD pin, representing the decoded DTMF digit. The rising edge of the first pulse will latch the data prior to shifting. Refer to Fig. 3.                                                                                                                                                                                                         |

| 7        | ESt<br>(MT3070/<br>MT3074)  | Early Steering Output. A logic high on ESt indicates that a DTMF signal is present.                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | DStD<br>(MT3071/<br>MT3075) | <b>Delayed Steering Output.</b> A logic high on DStD indicates that a valid DTMF digit has been detected.                                                                                                                                                                                                                                                                                                                                                                            |

| 8        | V <sub>DD</sub>             | <b>Positive Power Supply</b> . (5V Typ.) Performance of the device can be optimized by minimizing noise on the supply rails. Decoupling capacitors across $V_{DD}$ and $V_{SS}$ are therefore recommended.                                                                                                                                                                                                                                                                           |

Figure 4 - Application Circuit

## **Functional Description**

The MT3070/MT3071/MT3074/MT3075 is a high performance and low power consumption DTMF Receiver. The receiver provides a wide dynamic range and a serial data output port. The MT3070/MT3071 also provides a supervisory tone detection function. The input signal is applied to a DTMF tone detection circuit and a supervisory tone detection circuit (MT3070/MT3071) via an Automatic Gain Control (AGC). The device incorporates a bandsplit filter section to separate the input DTMF signal into high and low group tones and a digital counting section to verify that the incoming signal corresponds to standard DTMF frequencies. Following verification, the DTMF signal is decoded into a 4-bit code and shifted out in a serial format.

#### Automatic Gain Control (AGC)

The input signal is buffered by an internal op-amp, followed by an AGC circuit to provide a wide dynamic range. This signal is filtered by a lowpass filter to prevent aliasing distortion. This antialiasing filter also serves as the front end filter for the supervisory tone detection. The input signal is then routed to both the DTMF detection circuitry and the supervisory tone detection circuitry.

#### **Filter and Decoder Section**

Signals entering the DTMF detection circuitry are filtered by a notch filter at 350 and 440 Hz for dial tone rejection. This signal, still in its composite form, is then split into its individual high and low frequency components by two sixth order switched capacitor bandpass filters. Each component tone is then smoothed by an output filter and squared by high gain limiting comparators. The resulting squarewaves are applied to a digital detection circuit where a complex averaging algorithm is employed to determine the valid DTMF signal. Upon recognition of a valid frequency from each tone group, the Early Steering (ESt) output of MT3070/MT3074 will go high, indicating that a DTMF tone has been detected. Any subsequent loss of DTMF signal condition will cause ESt pin to go low. For MT3071/MT3075, an internal delayed steering counter validates the early steering signal for a predetermined guard time which requires no external components. The Delayed Steering (DStD) output will go high only when the validation period has elapsed. Once the DStD output is high, any subsequent loss of early steering signal due to DTMF signal dropout will activate the internal counter for a validation of tone absent guard time. The DStD output will go low only after this validation period.

#### Supervisory Tone Detection (MT3070/MT3071)

The output signal from the AGC circuit is also applied to the supervisory tone detection circuit. When the signal level is above the threshold of the internal comparator, the supervisory tone detection circuit produces a tone present indication on the SD output. The detector circuit incorporates an integrator such that in the presence of supervisory tones, the SD output will remain a continuous high. Since the DTMF signals are in the detection bandwidth, the presence of a DTMF signal will also cause the SD to go high. Therefore, the SD and ESt/DStD output pins should be monitored by a microprocessor in real time, so that various supervisory tones, presence of speech or DTMF signals can be identified. The supervisory tone detection circuit is enabled at all times except during the time between the rising edge of the first pulse and the falling edge of the fourth pulse on ACK pin (see Figure 2).

#### Serial Data (SD) Output

When a valid DTMF signal is present, ESt /DStD will go high. The application of four clock pulses on the ACK pin will provide a 4-bit serial binary code representing the decoded DTMF digit on the SD pin output. The rising edge of the first pulse applied on the ACK pin latches the data and the least significant bit of the decoded digit is also shifted out on the SD pin. The next three pulses on ACK pin will shift the remaining latched bits in a serial format (see Figure 3). If less than four pulses are applied to the ACK pin, new data cannot be latched even though ESt/DStD is valid. Clock pulses should be applied to shift out any remaining data bits and to resume normal operation. Any transition in excess of four pulses will be ignored until the next rising edge of the ESt/DStD. The 4-bit binary codes representing all 16 standard DTMF digits are shown in Table 1.

#### Powerdown Mode

The device has a powerdown function to reduce power consumption. To enter powerdown mode, the ACK pin must be logic low before a logic high is applied on the PWDN pin. See Table 2 for setup.

### Oscillator

The on-chip oscillator is completed by connecting a 4.194304 MHz crystal or ceramic resonator from OSC pin to ground. The oscillator circuit can also be driven by an external clock at 4.194304 MHz.

| F <sub>LOW</sub> | F <sub>HIGH</sub> | DIGIT | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

|------------------|-------------------|-------|----------------|----------------|----------------|----------------|

| 697              | 1209              | 1     | 0              | 0              | 0              | 1              |

| 697              | 1336              | 2     | 0              | 0              | 1              | 0              |

| 697              | 1477              | 3     | 0              | 0              | 1              | 1              |

| 770              | 1209              | 4     | 0              | 1              | 0              | 0              |

| 770              | 1336              | 5     | 0              | 1              | 0              | 1              |

| 770              | 1477              | 6     | 0              | 1              | 1              | 0              |

| 852              | 1209              | 7     | 0              | 1              | 1              | 1              |

| 852              | 1336              | 8     | 1              | 0              | 0              | 0              |

| 852              | 1477              | 9     | 1              | 0              | 0              | 1              |

| 941              | 1336              | 0     | 1              | 0              | 1              | 0              |

| 941              | 1209              | *     | 1              | 0              | 1              | 1              |

| 941              | 1477              | #     | 1              | 1              | 0              | 0              |

| 697              | 1633              | Α     | 1              | 1              | 0              | 1              |

| 770              | 1633              | В     | 1              | 1              | 1              | 0              |

| 852              | 1633              | С     | 1              | 1              | 1              | 1              |

| 941              | 1633              | D     | 0              | 0              | 0              | 0              |

0 = LOGIC LOW, 1 = LOGIC HIGH

Table 1 - Serial Decode Bit Table

| PWDN<br>(Input) | ACK<br>(Input) | ESt/DStD<br>(Output)            | SD<br>(Output)   | MT3070/71/<br>74/75<br>Status |  |  |

|-----------------|----------------|---------------------------------|------------------|-------------------------------|--|--|

| Low             | Refe<br>Tii    | r to Figs. 2 and<br>ming Wavefo | Normal operation |                               |  |  |

| High†           | Low            | Low                             | Low              | Powerdown<br>mode             |  |  |

| High            | High           | ×                               | ×                | Undefined                     |  |  |

t = enters powerdown mode on the rising edge

Table 2 - Powerdown Mode

# **Applications**

The circuit shown in Figure 4 illustrates the use of the MT3070/MT3071/MT3074/MT3075 in a typical receiver application. It requires only a coupling capacitor and a crystal or ceramic resonator.

The MT3070/MT3074 is designed for the user who wishes to tailor the guard time for specific applications. When a DTMF signal is present, the ESt pin will go high. An external microprocessor monitors ESt in real time for a period of time set by the user. A guard time algorithm must be implemented such that DTMF signals not meeting the timing requirements are rejected. The MT3071/MT3075 uses an internal counter to provide a preset DTMF validation period. It requires no external components. The DStD output high indicates that a valid DTMF digit has been detected.

The 4 194304 MHz frequency has a secondary advantage in some applications where a real time clock is required. A 22-bit counter will count 4194304 cycles to provide a one second time base.

X = don't care