## MQ-100/HD64464

## HITACHI

LCD/CRT 2D Graphics Subsystem

Data Book Version 1.09

August 1998

Preliminary Product Information

#### **Copyright Notice**

Copyright 1998 MediaQ, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by MediaQ, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means - electronic, mechanical, magnetic, optical, chemical, manual, or otherwise - any part of this publication without the express written permission of MediaQ, Inc.

#### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademark Acknowledgment**

MediaQ Logo is a registered trademark of MediaQ, Inc.

All other trademarks are the property of their respective holders.

#### **Disclaimer**

This document provides general information for the customer. MediaQ, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the document. MediaQ makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that many different parties hold patents on products, components, and processes within the personal computer industry. Customers should ensure that their use of the products does not infringe upon any patents. MediaQ respects the patent rights of third parties and shall not participate in direct or indirect patent infringement.

## **Revision History**

| Revision     | <u>Date</u>        | <u>By</u>    | Comment                                     |

|--------------|--------------------|--------------|---------------------------------------------|

| 1.07<br>1.08 | 7/20/98<br>7/29/98 | SRV/bb<br>MB | Frame Release. Revised all the Electricals. |

| 1.06         | 8/27/98            | SRV          | Include HD64464                             |

# MQ-100/HD64464 LCD/CRT 2D Graphics Subsystem Preliminary Product Information

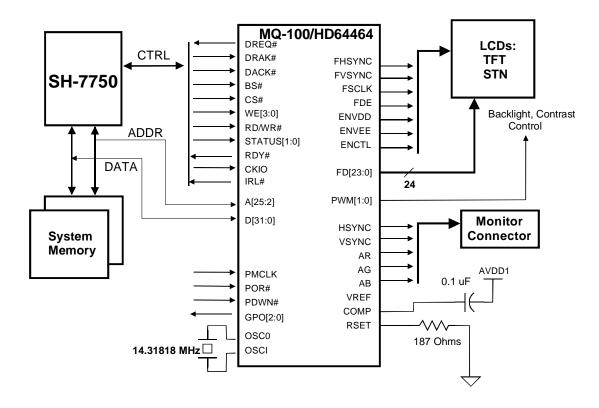

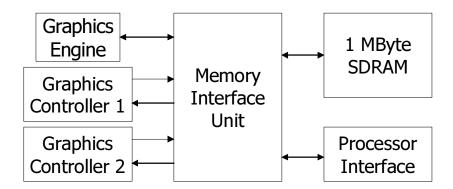

The MQ-100/HD64464 is a single-chip LCD/CRT 2D graphics subsystem with 1MByte embedded DRAM. The MQ-100/HD64464 is designed to provide direct, high performance interface to the Hitachi SH-family of RISC Processors. The target market segments for the MQ-100/HD64464 are subnotebooks based on the Windows<sup>®</sup> CE Operating System, Internet Appliances and Windows-based Terminals.

#### MQ-100/HD64464 Key Features:

- 64-Bit 2D Graphics Acceleration Engine

- Embedded 1-MByte SDRAM for Display Memory

- Bandwidth-Driven System Partitioning Reduces I/O Traffic and Saves Power

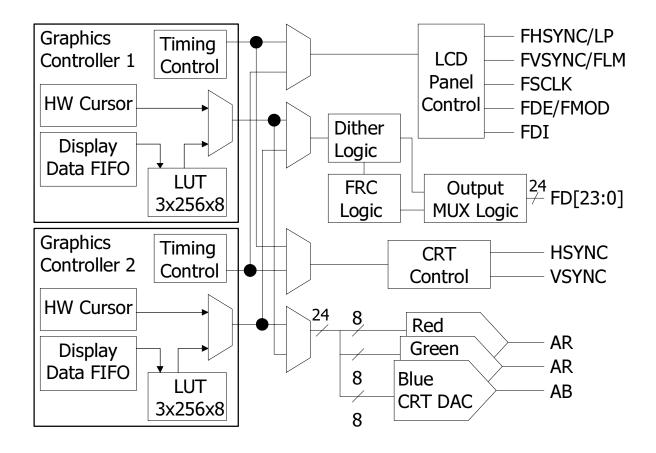

- Independent LCD and CRT Controllers

- Display Resolutions up to 1024x768; Pixel Depth up to 16-Bits per pixel

- Direct Interface to CRT monitors with On-Chip TrueColor DAC

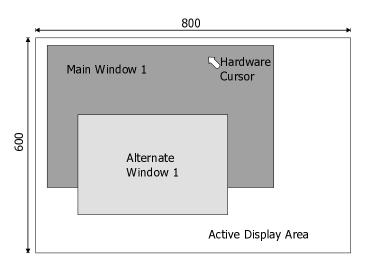

- QView<sup>TM</sup> Display Functionality Enables Simultaneous and Dual Image Views on LCD / CRT

- Two 64x64 Hardware Cursors

- Programmable PWM Outputs control LCD Contrast and Brightness

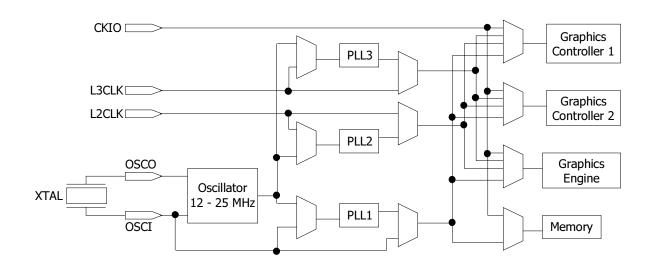

- 3 On-Chip PLL Frequency Synthesizers

- Advanced Power Management Features with DynamiQ<sup>TM</sup> and Windows CE Power

- Management Support

- Fully Static Design Fabricated in CMOS Process

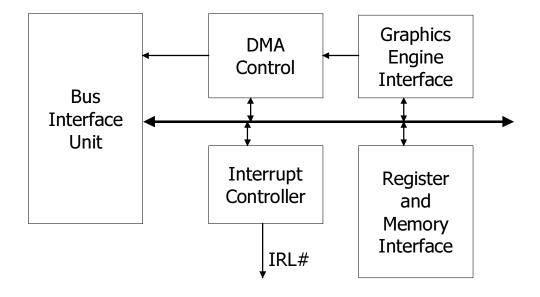

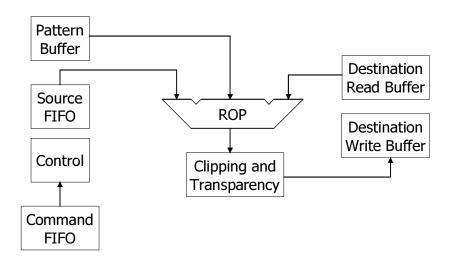

Figure 1: MQ-100/HD64464 System Implementation Diagram

#### 1 MQ-100/HD64464 Overview

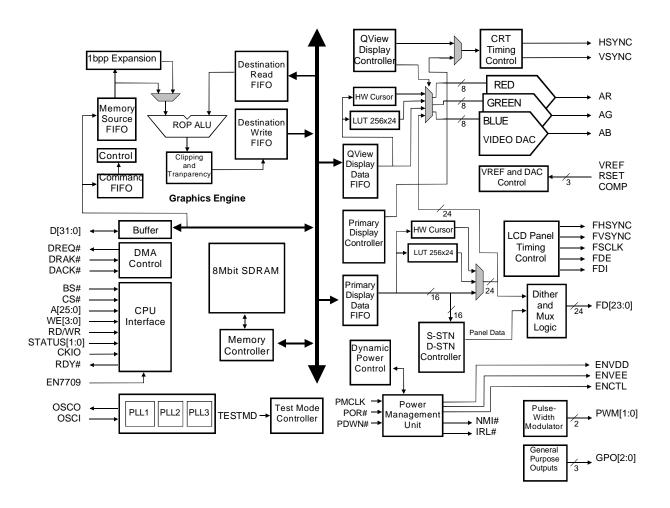

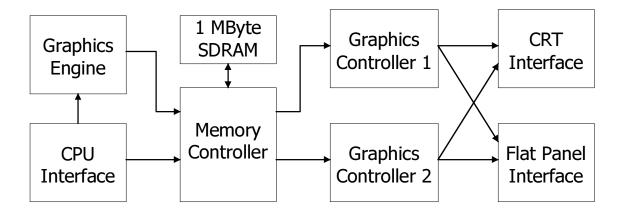

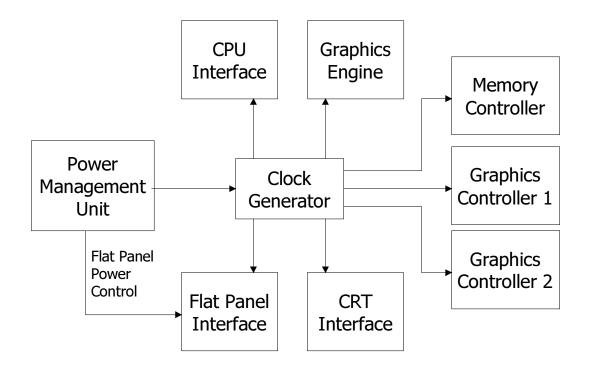

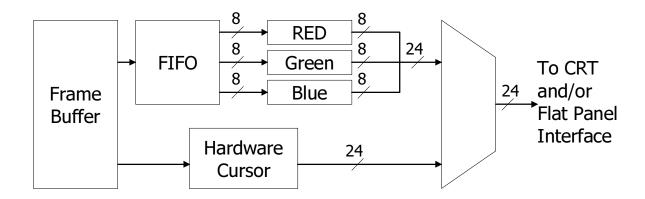

The MediaQ MQ-100/HD64464 is a high-performance single-chip accelerated 2D graphics display subsystem for Hitachi SH-7750 and SH-7709 based systems. An integrated 1-MByte frame buffer greatly reduces power consumption while dramatically improving graphics performance. The graphics engine and two graphics controllers share a high-bandwidth on-chip memory bus ensuring that graphics operations are not adversely affected by display refresh requirements. Placing the graphics frame buffer on-chip reduces power dissipation significantly while reducing chip count and improving the system form factor. Graphics controller 1 (GC1) produces control, timing and pixel data for a CRT display, and graphics controller 2 (GC2) produces control, timing and pixel data for a LCD display. The MQ-100/HD64464 provides a unique functionality called QView. TM which lets the OEM configure the primary LCD display and the optional CRT display at different resolutions, refresh rates and pixel depths. For example, utilizing the QView<sup>TM</sup> feature, a MQ-100/HD64464 based computing device can drive the LCD at a resolution of 640x480 8 bits per pixel (256 colors) at a refresh rate of 60 Hz while the CRT can be driven at a resolution of 800x600 8 bits per pixel (256 colors) at a refresh rate of 75 Hz. The QView<sup>TM</sup> feature also allows the application software to show independent or separate images to be displayed on the primary and secondary display devices: LCD and CRT. The MQ-100/HD64464 is a very low-power design, employing asynchronous design techniques and dynamic gated clocking (DynamiQ<sup>TM</sup>) to implement hardware dynamic power management, making the MQ-100/HD64464 ideal for portable and other low-power devices with demanding display requirements. Windows CE power management modes are directly supported, allowing the software to further reduce active system power consumption thus extending the battery life.

#### 1.1 MQ-100/HD64464 Features

#### **Superior Graphics Performance**

- Integrated high-performance 64-bit 2D graphics engine

- 16-deep command FIFO provides efficient interface between CPU and graphics engine

- Independent 16-deep source image FIFO

- Hardware support for font color expansion

- High-speed interface to the internal frame buffer memory

- Graphics acceleration functions include:

- Rectangular Source-copy block transfers (BitBLTs)

- Transparent source-copy BitBLTs

- Masked source-copy BitBLTs

- · Monochrome-to-color expansion on source and pattern data

- · Pattern and Rectangle Fills

- Hardware Clipping

- Panning and Scrolling

- 256 Raster Ops (ROPs)

- Horizontal Solid Line

- Vertical Solid Line

- Diagonal Solid Line (angle MUST be a multiple of 45 degrees)

#### **Two Independent Graphics Controllers**

- Full-featured CRT and LCD graphics controllers

- Support for 1, 2, 4, 8, 15, and 16-bits per pixel (bpp) modes

- Built-in triple 256x8 color lookup tables for 1-, 2-, 4- and 8-bpp modes

- Color lookup table can be used for gamma correction in 15 and 16-bpp modes

- Each graphics controller contains:

- FIFO for data from display memory

- Triple 256x8 color Look-Up Table (LUT)

- · Completely programmable display timing generator

- 64x64 hardware cursor with 24-bit foreground/background colors, transparency or inverse

- transparency

#### Dual-Display System Implementation with QView™ Technology

**QView**<sup>TM</sup> provides independent programmability of CRT and LCD parameters: resolution, color depth and refresh rate.

**QView**<sup>TM</sup> technology enhances the quality of the images in dual-display applications by providing separate refresh rates, resolutions and color depths for each display. Two graphics controllers are employed to provide optimal settings for each display device.

- The primary and secondary display devices can show the same image or separate images, constrained only by the amount of available video memory and the features supported by the O/S or device drivers

- Allows "panning" of an image on LCD and CRT display windows when same image is displayed; when different image is displayed, windows could be adjacent (left-right or top-bottom) or independent

- Automatic cursor switching between display windows provides smooth virtual desktop operation

#### Direct Interface to a Broad Range of Liquid Crystal Displays

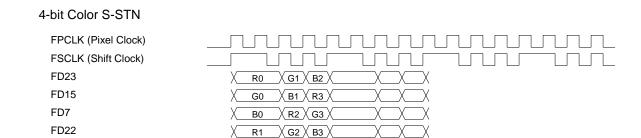

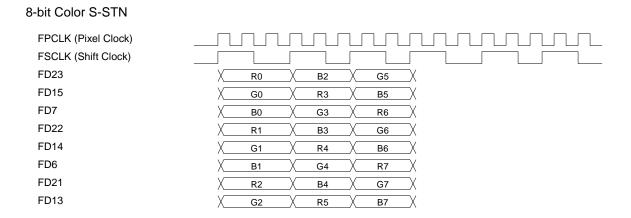

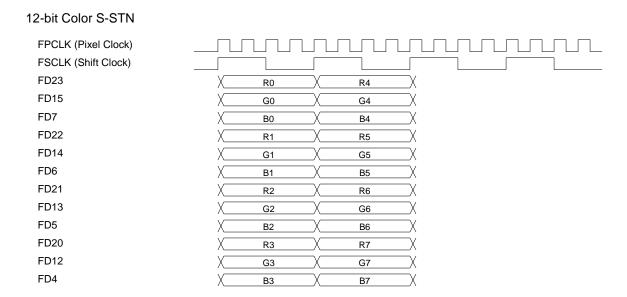

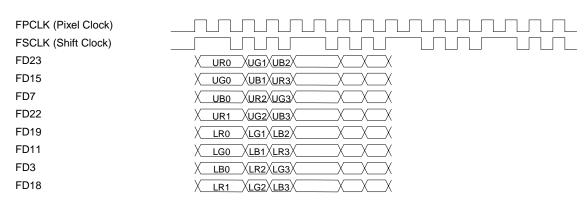

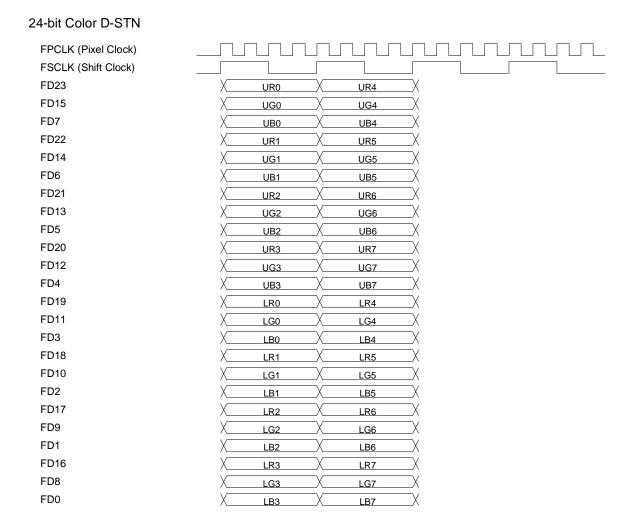

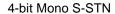

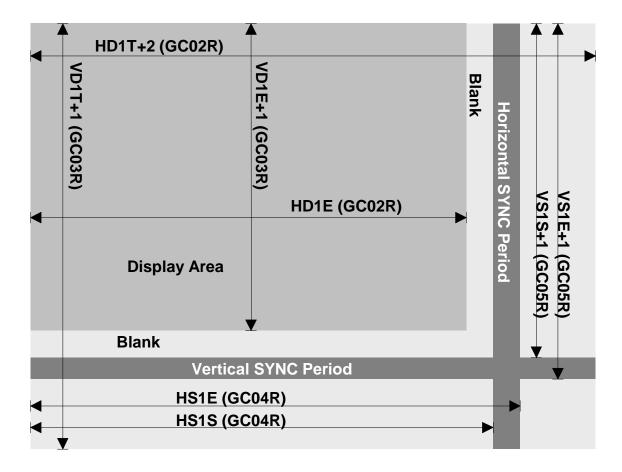

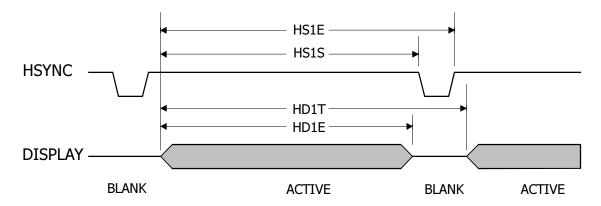

- Supports XGA, SVGA and VGA passive matrix color dual-scan STN (D-STN) and single-scan STN (S-STN) Liquid Crystal Displays (LCD) with 8-bit, 16-bit and 24-bit physical interfaces

- Supports XGA, SVGA and VGA active matrix color TFT LCDs with 9-bit, 12-bit, 18-bit and 24-bit (1 pixel/clock) interfaces

- Built-in color-to-monochrome conversion to support monochrome TFT, S-STN, and D-STN panels

- Advanced dithering and Frame Modulation (FRC) algorithms to generate up to 256 gray levels on monochrome and color STN panels

## Programmable Pulse Width Modulated (PWM) Outputs Control the Brightness and Contrast of the Liquid Crystal Display

- Wide range of PWM output clock frequencies: the source clock (which can be the oscillator clock, the bus clock or the power management clock) can be pre-divided by a factor ranging from 1 to 15

- Variable duty cycle: the output signal duty cycle is set by an 8-bit register, providing a range of duty cycles from 1/256 to 256/256

#### **Direct Interface to CRT Monitor Displays**

- Supports 640x480 (VGA) to 1024x768 (XGA) resolutions on CRT monitors with multiple refresh rates

- Built-in High Performance TrueColor DAC with monitor sense circuitry, blank pedestal and sync pedestal

- Cyclic Redundancy Check logic to insure datapath integrity for on-board diagnostics

## Integrated Programmable Frequency Synthesizers Provide Independent Frequencies for Display and Memory Operation

On-chip clocks are synthesized from a reference 12-25 MHz crystal Oscillator to provide three internal clocks.

#### **High Performance System Solution**

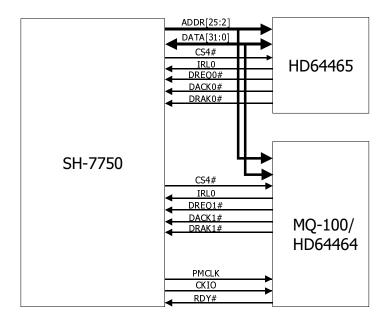

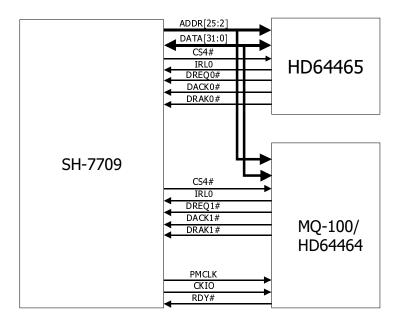

- Direct, "glueless" 32-bit interface to Hitachi SH-7750 and SH-7709 Microprocessors

- Burst-mode DMA is supported to optimize transfer of source image data to the Graphics Engine from main memory

- 64-bit Graphics Engine operates independently of the CPU, performing BitBLTs, rasterops (ROPs) and other graphics acceleration functions written to a command queue

- On-chip display memory greatly reduces memory contention and bottlenecks compared to systems that share system and display memory

- On-chip FIFOs are used extensively to ensure optimum bandwidth utilization of on-chip memory

#### **Embedded 1-MByte SDRAM for Display Memory**

- Lower power dissipation than conventional external frame buffers

- Low EMI emissions from reduced pin activity

- Single package display subsystem offers excellent system factor by eliminating external display memory

#### **Advanced Power Management Features**

- Compliant with the Microsoft OnNow Architecture Initiative: D0 (normal), D1, D2, and D3 (Sleep) power states are provided; transitions between states is accomplished via software

- D1 and D2 provide programmable "step down" states for selective functional shutdown

- Suspend mode: hardware suspend entered by asserting PDWN# input for maximum power savings

- Display memory contents can be preserved in all power saving modes provided the oscillator clock is maintained, supporting "instant on" capability

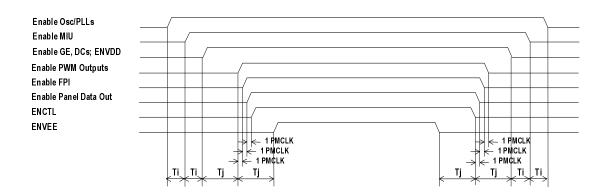

- Full-featured flat panel power sequencing with programmable intervals

- Flat panel sequencing compliant with Display Power Management Signaling (DPMS) Specification

- PWM activation can be tied to flat panel power sequencing to prevent out-of-sequence application of contrast or backlight control voltages

- Built-in DynamiQ<sup>™</sup> power management: by dynamically gating clocks, inactive portions of the MQ-100/HD64464 are automatically shut down without any software intervention, optimizing power consumption in all operating modes

**Built-in NAND Tree for Board-Level Test**

Fully Static Design fabricated in CMOS Process

Packaged in 176 pin LQFP package with 0.5 mm pitch

## 2 Pin Description

Figure 2: MQ-100/HD64464 Pinout Diagram

#### The following are valid pin types:

| Pin Type | Pin Type Description            |  |  |  |  |  |  |

|----------|---------------------------------|--|--|--|--|--|--|

| I        | Input pin.                      |  |  |  |  |  |  |

| 0        | Output pin.                     |  |  |  |  |  |  |

| I/O      | Bidirectional input/output pin. |  |  |  |  |  |  |

| Р        | Power (VDD) pin.                |  |  |  |  |  |  |

| G        | Ground (GND) pin.               |  |  |  |  |  |  |

| Α        | Analog input or output pin      |  |  |  |  |  |  |

| AP       | Analog power pin                |  |  |  |  |  |  |

| AG       | Analog ground pin               |  |  |  |  |  |  |

#### The following convention is also used in the signal names:

Note: A '#' indicates active low signal

#### 2.1 Flat Panel Interface

| Pin Name | Pin<br>Type | Pin #             | Drive<br>(mA) | Pin Description                                                                                                               |

|----------|-------------|-------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| ENVDD    | 0           | 10                | 8             | Enable VDD                                                                                                                    |

|          |             |                   |               | In panel power-up sequence, this signal is asserted first;                                                                    |

|          |             |                   |               | while in panel power-down sequence, this signal is driven                                                                     |

|          |             |                   |               | last (min. 32 ms after ENCTL). This signal is driven low dur-                                                                 |

|          |             |                   |               | ing reset.                                                                                                                    |

| ENCTL    | 0           | 11                | 8             | Enable data and control signals                                                                                               |

| (GP00)   |             |                   |               | In panel power-up sequence, this signal is asserted minimum                                                                   |

|          |             |                   |               | 32 ms after ENVDD and in panel power-down sequence, this                                                                      |

|          |             |                   |               | signal is driven minimum 32 ms after ENVEE. If not used as ENCTL, this signal can be configured as a General Purpose          |

|          |             |                   |               | Output Port Bit 0. This signal is driven low during reset.                                                                    |

| ENVEE    | 0           | 9                 | 8             | Enable VEE                                                                                                                    |

| (GPO1)   |             |                   |               | In panel power-up sequence, this signal is asserted last (min.                                                                |

|          |             |                   |               | 32 ms after ENCTL). While in panel power-down sequence,                                                                       |

|          |             |                   |               | this signal is driven first. If not used as Enable VEE, this sig-                                                             |

|          |             |                   |               | nal can be configured as a General Purpose Output Port Bit 1.                                                                 |

|          |             |                   |               | This signal is driven low during reset.                                                                                       |

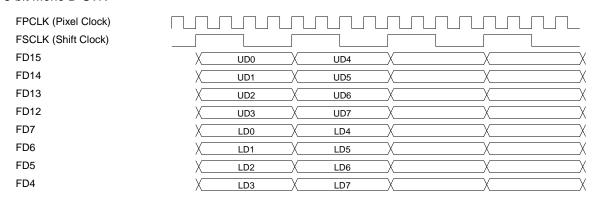

| FD[23:0] | 0           | 28-32,            | 8 / 16        | Flat Panel Data (optional data inversion)                                                                                     |

|          |             | 34-38,<br>40- 43, |               | These signals provide data to the flat panel. They are active approximately one 32 KHz clock after ENCTL is asserted and      |

|          |             | 40- 43,<br>45-47, |               | they will be driven approximately one 32 KHz clock before                                                                     |

|          |             | 49, 50,           |               | ENCTL is driven.                                                                                                              |

|          |             | 52-55,            |               |                                                                                                                               |

|          |             | 57                |               | For STN panels, FD0 pin can be programmed to output shift                                                                     |

|          |             |                   |               | clock, in which case, FSCLK pin will output pixel clock. These                                                                |

|          |             |                   |               | signals are driven low during reset, and when the flat panel is                                                               |

|          |             |                   | 0 / 10        | disabled, regardless of its polarity.                                                                                         |

| FDE      | 0           | 24                | 8 / 16        | Flat Panel Data Enable (programmable polarity)                                                                                |

|          |             |                   |               | This signal indicates the valid data area. Timing of this signal is the same as flat panel data. This signal is normally used |

|          |             |                   |               | for active matrix (TFT) LCD.                                                                                                  |

| FMOD     | O           |                   | 8 / 16        | Modulation clock for STN LCD panels                                                                                           |

|          |             |                   | - /           | This signal is driven low during reset and when flat panel is                                                                 |

|          |             |                   |               | disabled regardless of its polarity.                                                                                          |

| FDI      | 0           | 59                | 8 / 16        | Flat Panel Data Inversion                                                                                                     |

|          |             |                   |               | If flat panel data inversion is enabled, this signal will indicate                                                            |

|          |             |                   |               | whether the flat panel data is inverted or not. When FDI is                                                                   |

|          |             |                   |               | high, the flat panel data is inverted and when FDI is low the                                                                 |

|          |             |                   |               | flat panel data is not inverted. Timing of this signal is the same as flat panel data.                                        |

|          |             |                   |               | This signal is driven low during reset.                                                                                       |

| FVSYNC   | 0           | 25                | 8 / 16        | Flat Panel Vertical Sync for TFT LCD panels (program-                                                                         |

|          |             |                   | -, -5         | mable polarity)                                                                                                               |

| FLM      | 0           |                   | 8/16          | FLM for STN LCD panels (programmable polarity)                                                                                |

|          |             |                   |               | This signal is driven low during reset and when flat panel is                                                                 |

|          |             |                   |               | disabled regardless of its polarity.                                                                                          |

| FHSYNC         | 0   | 27                | 8 / 16 | Flat Panel Horizontal Sync for TFT LCD panels (programmable polarity)                                                                                                                                                                                                                                                                                      |

|----------------|-----|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP             | 0   |                   | 8 / 16 | LP for STN LCD panels (programmable polarity) This signal is driven low during reset and when flat panel is disabled regardless of its polarity.                                                                                                                                                                                                           |

| FSCLK          | 0   | 58                | 8 / 16 | Flat Panel Shift Clock Rising edge of this clock is used to output flat panel data and control signals therefore falling edge of this clock is normally used to externally latch flat panel data and control signals.                                                                                                                                      |

| PWM0<br>(GPO2) | 0   | 2                 | 4      | Pulse Width Modulation 0  This pulse width modulation clock is enabled just before flat panel control/data is enabled and deactivated just after flat panel control/data is enabled. This pulse can be used to control external contrast/brightness logic or backlight. If not used as PWM0, this signal can be used as General Purpose Output Port Bit 2. |

| PWM1<br>(GPO3) | 0   | 1                 | 4      | Pulse Width Modulation 1 This pulse width modulation clock is enabled just before flat panel control/data is enabled and deactivated just after flat panel control/data is enabled. This pulse can be used to control external contrast/brightness logic or backlight. If not used as PWM1, this signal can be used as General Purpose Output Port Bit 3.  |

| GPIO [2:0]     | I/O | 8, 5, 3           | 4      | <b>General Purpose I/Os.</b> These pins can be programmed to be either inputs or outputs. These pins are programmed as inputs during reset.                                                                                                                                                                                                                |

| FVDD[3:0]      | P   | 23, 33,<br>48, 56 | -      | Flat Panel Interface Power Supply pins                                                                                                                                                                                                                                                                                                                     |

| FGND[3:0]      | G   | 26, 39,<br>51, 61 | -      | Flat Panel Interface Ground Pins                                                                                                                                                                                                                                                                                                                           |

#### 2.2 CRT Interface

| Pin Name | Pin<br>Type | Pin # | Drive<br>(mA) | Pin Description                                                                               |

|----------|-------------|-------|---------------|-----------------------------------------------------------------------------------------------|

| AR       | A           | 80    | 16            | Analog Red Output to the CRT monitor                                                          |

| AG       | A           | 75    | 16            | Analog Green Output to the CRT monitor                                                        |

| AB       | A           | 87    | 16            | Analog Blue Output to the CRT monitor                                                         |

| VSYNC    | 0           | 63    | 8             | Output to the CRT monitor. In NAND Chain test mode, this pin is the output of the NAND chain. |

| HSYNC      | 0  | 62     | 8 | Horizontal Sync Output to the CRT monitor                                                                              |

|------------|----|--------|---|------------------------------------------------------------------------------------------------------------------------|

|            |    |        |   | output to the ext monitor                                                                                              |

| VREFIO     | A  | 85     | - | Voltage Reference Internal voltage reference output, leave unconnected                                                 |

| FSADJ      | Α  | 73     | - | Full-Scale Adjust                                                                                                      |

|            |    |        |   | This pin must be tied GND through a 186 ohm external resistor to set the full scale current value for the DAC outputs. |

| СОМР       | Α  | 78     | - | Compensation                                                                                                           |

|            |    |        |   | This pin is tied to one of the analog VDD pins through a 0.1 uF capacitor, such as AVDD1                               |

| AVDDC[4:1] | AP | 86,79, |   | Analog Power for CRT DAC                                                                                               |

| AVDDC[4.1] | AF | 77,76  |   | Alialog Fower for CRT DAC                                                                                              |

| AGNDC[4:1] | AG | 88,83, |   | Analog GND for CRT DAC                                                                                                 |

|            | -  | 81,74  |   |                                                                                                                        |

#### 2.3 CPU Interface

| Pin Name | Pin Type | Pin #                                                                      | Drive<br>(mA) | Pin Description                                                                                                                                                                     |

|----------|----------|----------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СКІО     | I        | 93                                                                         | -             | Bus Interface Clock This signal is the bus clock generated by the CPU and is used as the reference for bus interface signals. The frequency range of this clock is 8 MHz to 66 MHz. |

| BS#      | I        | 90                                                                         | -             | Bus Cycle Start CPU asserts this signal to request a bus cycle.                                                                                                                     |

| A[25:2]  | I        | 141-<br>148,<br>150-<br>154,<br>156,<br>157,<br>159-<br>164<br>166-<br>169 | -             | CPU Address Bus This address bus is driven by the CPU for all read/write accesses.                                                                                                  |

| D[31:0]     | I/O | 99,                                                                                         | 4 | CPU Data Bus                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-----|---------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |     | 101-<br>104,<br>106-<br>110,<br>112,<br>113,<br>115-<br>120,<br>122-<br>126,<br>128-<br>136 | • | This data bus is driven by the CPU during write accesses and driven by MQ-100/HD64464 during read accesses. These pins are tri-stated during reset and when the CPU is disabled (powered down).                                                                                                                                                                                                                 |

| CS#         | Ī   | 89                                                                                          | - | Chip Select Chip Select signal from the CPU to the MQ-100/ HD64464. MQ-100/HD64464 decodes the address presented on the CPU Address bus only when this signal is asserted.                                                                                                                                                                                                                                      |

| WE[3:0]#    | I   | 94, 96,<br>97, 98                                                                           | - | Write Enables[3:0] These are the byte enables [3:0] used for writes from the CPU to the MQ-100/HD64464. Read operations are always 32-bit wide reads.                                                                                                                                                                                                                                                           |

| RD/WR#      | Ī   | 91                                                                                          | - | Read/Write Signal This signal is valid through out the bus cycle. If it is at Logic High, a Read cycle takes place and if it is at Logic Low, a Write cycle takes place.                                                                                                                                                                                                                                        |

| IRL#        | 0   | 137                                                                                         | 4 | Interrupt Request Line Under the assumption that the CPU Interrupt Lines IRL3-IRL0 are programmed to be in non-encoded mode (Setting IRL interrupt lines to be used as four independent interrupt sources), this signal is a request from MQ-100/HD64464. Active Low. Connected to one of the IRL lines on the CPU.                                                                                             |

| STATUS[1:0] | I   | 172,<br>170                                                                                 | - | Status[1:0] This is status of the processor.                                                                                                                                                                                                                                                                                                                                                                    |

| WAIT#       | O   | 173                                                                                         | 4 | Wait (active low) In SH-7750 systems, this signal is asserted by MQ-100/HD64464 to request additional hardware wait states, asking the CPU to wait until the MQ-100/HD64464 is ready to complete the requested bus cycle Ready (active low) In SH-7709 systems, this signal is deasserted by MQ-100/HD64464 to request additional hardware wait states when it is not ready to complete the requested bus cycle |

| DREQ#       | 0   | 138                                                                                         | 4 | Data Transfer Request Data Transfer Request Input from MQ-100/HD64464 to Channel 0 of the DMA Controller in the CPU.                                                                                                                                                                                                                                                                                            |

| DRAK#       | I   | 139                                                                                         | - | DMA Transfer Request Acknowledge  DMA Transfer Request Acknowledge from the Channel 0 of the DMA Controller in the CPU to the MQ-100/ HD64464.                                                                                                                                                                                                                                                                  |

| DACK#       | I   | 140                                                                                         |   | Strobe from Channel 0 Strobe output to MQ-100/HD64464 from Channel 0 of the DMA Controller in the CPU.                                                                                                                                                                                                                                                                                                          |

| CVDD [5:1] | P | 155,<br>165,<br>121,<br>111, 92 | CPU Interface Power pins  |

|------------|---|---------------------------------|---------------------------|

| CGND [5:1] | G | 171,<br>158,<br>127,<br>114, 95 | CPU Interface Ground pins |

#### 2.4 Power Management and Miscellaneous Pins

| Pin Name   | Pin<br>Type | Pin #  | Drive<br>(mA) | Pin Description                                                                                              |

|------------|-------------|--------|---------------|--------------------------------------------------------------------------------------------------------------|

| DD14/01 // |             | 22     | (IIIA)        |                                                                                                              |

| PDWN#      | I           | 22     |               | Power Down                                                                                                   |

|            |             |        |               | This is an active low input to the MQ-100/HD64464. This places the MQ-100/HD64464 in the lowest power state. |

| PMCLK      | I           | 174    |               | Power Mode Clock                                                                                             |

|            |             |        |               | This is the 16.384KHz clock from the CPU, used to control the power state machine in the MQ-100/HD64464.     |

| VDD        | Р           | 12,    |               | Power Supply                                                                                                 |

|            |             | 100,   |               |                                                                                                              |

|            |             | 144    |               |                                                                                                              |

| GND        | G           | 17,    |               | Ground                                                                                                       |

|            |             | 105,   |               |                                                                                                              |

|            |             | 149    |               |                                                                                                              |

| VDDIO      | Р           | 4      |               | Additional Power input for pad I/O ring                                                                      |

| GNDIO      | G           | 7      |               | Additional Ground input for pad I/O ring                                                                     |

| NC         |             | 13,44, |               | No Connect                                                                                                   |

|            |             | 60,65, |               | <u>These pins should not be connected in the system</u> . They are                                           |

|            |             | 76,82, |               | reserved for future use. They must NOT be connected to                                                       |

|            |             | 84,    |               | VCC or GND or any other signal.                                                                              |

|            |             | 175,   |               |                                                                                                              |

|            |             | 176    |               |                                                                                                              |

#### 2.5 Clocks

| Pin Name      | Pin  | Pin #        | Drive | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------|--------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Type |              | (mA)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| osco          | A    | 19           |       | Reference Clock Oscillator Output This pin is connected to an external 12MHz to 25MHz crystal oscillator. The reference clock is used to generate a reference frequency for the three internal PLLs that generate Memory and Pixel clocks. The crystal value is dependent on the desired display resolution. The recommended value is 12.277MHz.                                                                                                                                                                                                                                                                                                   |

| OSCI<br>L1CLK | A    | 18           |       | Reference Clock Oscillator Input This pin is connected to an external 12MHz to 25MHz crystal. The reference clock oscillator is used to generate reference frequency for the three internal PLLs that generate Memory and Pixel clocks. The crystal value is dependent on the desired display resolution.  PLL 1 Bypass Clock When MQ-100/HD64464 is configured for test mode 10, PLL 1 (System Clock source) is bypassed and this input provides the clock that is normally provided by PLL 1. In normal mode, PLL 1 gets its input from the reference clock oscillator. When PMU control bit is set to a '1', L1CLK provides the input to PLL 1. |

| L2CLK         | I    | 68           |       | PLL 2 Bypass Clock When MQ-100/HD64464 is configured for test mode 10, PLL 2 (Primary Graphics Controller clock source) is bypassed and this input provides the clock that is normally provided by PLL 2. When not in test mode, PLL 2 gets its input from the OSCI pad. When PMU control bit is set to a '1', L2CLK provides the input to the PLL 2.                                                                                                                                                                                                                                                                                              |

| L3CLK         | I    | 71           |       | PLL 3 Bypass Clock When MQ-100/HD64464 is configured for test mode 10, PLL 3 is bypassed and this input provides the clock that is normally provided by PLL 3. When not in test mode, PLL 3 gets its input from the OSCI pad. When PMU control bit is set to a '1', L3CLK provides the input to the PLL 3.                                                                                                                                                                                                                                                                                                                                         |

| AVDD[3:1]     | Р    | 72,67,<br>66 |       | Analog Power Supply for the on-board PLLs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AGND[3:1]     | G    | 70,69,<br>64 |       | Analog GND for the on-board PLLs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### 2.6 Reset/Mode Control

| Pin Name | Pin  | Pin #  | Drive | Pin Description                                                                                                                                                                                                                                                   |

|----------|------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Type |        | (mA)  | -                                                                                                                                                                                                                                                                 |

| POR#     | I    | 21     |       | Power-On Reset This signal resets the whole system. It clears all the registers including RTC and its registers. It also puts the system in STANDBY mode.                                                                                                         |

| EN7      | I    | 20     |       | Enable SH-7709 This signal should be tied to VDD to enable SH-7709 processor interface and disable SH-7750 processor interface. If it is tied to GND then SH-7750 processor interface is enabled and SH-7709 interface is disabled.                               |

| EDTMEN   | I    | 6      |       | Embedded DRAM Test Mode Enable Setting the EDTST pin to a '1' will enable DRAM test mode. This pin should be connected to ground when not under test.                                                                                                             |

| TMEN     | I    | 14     |       | Test Mode Enable MQ-100/HD64464 has 5 different test modes. Setting the TESTMD pin to a '1', on reset, will put the chip in test mode. The appropriate test mode is selected based on the values on the TMD[1:0]pins                                              |

| TMD[1:0] | I    | 15, 16 |       | Test Mode Select These two pins select type of Test Mode for MQ-100/ HD64464. These two pins are used only when TESTMD pin is set to a '1' on reset.  TMD[1:0] Description 00 PLL/OSC Testing Mode 01 DAC Test mode 10 NAND Tree Mode 11 Logic Function Test Mode |

#### 2.7 Pin Assignment Summary

#### 2.7.1 Pin List Sorted By Pin Number

Table 2-1: Pin List Sorted by Pin Number

| lable                                        | 2-1: Pin Lis                                                          | t Sorted by                                                 |                                              |     |            |

|----------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|-----|------------|

| 1                                            | PWM1                                                                  | 71                                                          | L3CLK                                        | 141 | A25        |

| 2                                            | PWM0                                                                  | 72                                                          | AVDD3                                        | 142 | A24        |

| 3                                            | GPIO0                                                                 | 73                                                          | FSADJ                                        | 143 | A23        |

| 4                                            | VDDIO                                                                 | 74                                                          | AGNDC1                                       | 144 | VDD        |

|                                              |                                                                       |                                                             | _                                            |     |            |

| 5                                            | GPIO1                                                                 | 75                                                          | AG                                           | 145 | A22        |

| 6                                            | EDTMEN                                                                | 76                                                          | AVDDC1                                       | 146 | A21        |

| 7                                            | GNDIO                                                                 | 77                                                          | AVDDC4                                       | 147 | A20        |

| 8                                            | GPIO2                                                                 | 78                                                          | COMP                                         | 148 | A19        |

| 9                                            | ENVEE                                                                 | 79                                                          | AVDDC2                                       | 149 | GND        |

| 10                                           | ENVDD                                                                 | 80                                                          | AR                                           | 150 | A18        |

|                                              |                                                                       |                                                             |                                              |     |            |

| 11                                           | ENCTL                                                                 | 81                                                          | AGNDC2                                       | 151 | A17        |

| 12                                           | VDD                                                                   | 82                                                          | NC                                           | 152 | A16        |

| 13                                           | NC                                                                    | 83                                                          | AGNDC4                                       | 153 | A16        |

| 14                                           | TMEN                                                                  | 84                                                          | NC                                           | 154 | A14        |

| 15                                           | TMD1                                                                  | 85                                                          | VREFIO                                       | 155 | CVDD5      |

| 16                                           | TMD0                                                                  | 86                                                          | AVDDC3                                       | 156 | A13        |

| 17                                           | GND                                                                   | 87                                                          | AB                                           | 157 | A12        |

|                                              |                                                                       |                                                             |                                              |     |            |

| 18                                           | OSCI                                                                  | 88                                                          | AGNDC3                                       | 158 | CGND4      |

| 19                                           | OSCO                                                                  | 89                                                          | CS#                                          | 159 | A11        |

| 20                                           | EN7                                                                   | 90                                                          | BS#                                          | 160 | A10        |

| 21                                           | POR#                                                                  | 91                                                          | RDWR#                                        | 161 | A9         |

| 22                                           | PDWN#                                                                 | 92                                                          | CVDD1                                        | 162 | A8         |

| 23                                           | FVDD3                                                                 | 93                                                          | CKIO                                         | 163 | A7         |

|                                              |                                                                       |                                                             |                                              |     |            |

| 24                                           | FDE                                                                   | 94                                                          | WE3                                          | 164 | A6         |

| 25                                           | FVSYNC                                                                | 95                                                          | CGND1                                        | 165 | CVDD4      |

| 26                                           | FGND3                                                                 | 96                                                          | WE2                                          | 166 | A5         |

| 27                                           | FHSYNC                                                                | 97                                                          | WE1                                          | 167 | A4         |

| 28                                           | FD23                                                                  | 98                                                          | WE0                                          | 168 | A3         |

| 29                                           | FD22                                                                  | 99                                                          | D31                                          | 169 | A2         |

|                                              | FD21                                                                  |                                                             | VDD                                          | 170 |            |

| 30                                           |                                                                       | 100                                                         | _                                            |     | STATUS1    |

| 31                                           | FD20                                                                  | 101                                                         | D30                                          | 171 | CGND5      |

| 32                                           | FD19                                                                  | 102                                                         | D29                                          | 172 | STATUSS0   |

| 33                                           | FVDD2                                                                 | 103                                                         | D28                                          | 173 | WAIT#/RDY# |

| 34                                           | FD18                                                                  | 104                                                         | D27                                          | 174 | PMCLK      |

| 35                                           | FD17                                                                  | 105                                                         | GND                                          | 175 | NC         |

| 36                                           | FD16                                                                  | 106                                                         | D26                                          | 176 | NC         |

| 37                                           | FD15                                                                  | 107                                                         | D25                                          | 170 | 110        |

|                                              |                                                                       |                                                             |                                              |     |            |

| 38                                           | FD14                                                                  | 108                                                         | D24                                          |     |            |

| 39                                           | FGND2                                                                 | 109                                                         | D23                                          |     |            |

| 40                                           | FD13                                                                  | 110                                                         | D22                                          |     |            |

| 41                                           | FD12                                                                  | 111                                                         | CVDD2                                        |     |            |

| 42                                           | FD11                                                                  | 112                                                         | D21                                          |     |            |

| 43                                           | FD10                                                                  | 113                                                         | D20                                          |     |            |

| 44                                           | NC                                                                    | 114                                                         | CGND2                                        |     |            |

|                                              |                                                                       |                                                             |                                              |     |            |

| 45                                           | FD9                                                                   | 115                                                         | D19                                          |     |            |

| 46                                           | FD8                                                                   | 116                                                         | D18                                          |     |            |

| 47                                           | FD7                                                                   | 117                                                         | D17                                          |     |            |

| 48                                           | FVDD1                                                                 | 118                                                         | D16                                          |     |            |

| 49                                           | FD6                                                                   | 119                                                         | D15                                          |     |            |

| 50                                           | FD5                                                                   | 120                                                         | D14                                          |     |            |

| 51                                           | FGND1                                                                 | 121                                                         | CVDD3                                        |     |            |

| _                                            | FD4                                                                   | 122                                                         |                                              |     |            |

| 52                                           |                                                                       |                                                             | D13                                          |     |            |

| 53                                           | FD3                                                                   | 123                                                         | D12                                          |     | +          |

| 54                                           | FD2                                                                   | 124                                                         | D11                                          |     |            |

| 55                                           | FD1                                                                   | 125                                                         | D10                                          |     |            |

| 56                                           | FVDD0                                                                 | 126                                                         | D9                                           |     |            |

| 57                                           | FD0                                                                   | 127                                                         | CGND3                                        |     |            |

|                                              |                                                                       |                                                             | D8                                           |     |            |

| 58                                           | ESCL K                                                                | 128                                                         |                                              |     | 1          |

| <u>58</u>                                    | FSCLK                                                                 | 128                                                         |                                              |     |            |

| 59                                           | FDI                                                                   | 129                                                         | D7                                           |     |            |

| 59<br>60                                     | FDI<br>NC                                                             | 129<br>130                                                  | D7<br>D6                                     |     |            |

| 59<br>60<br>61                               | FDI<br>NC<br>FGND0                                                    | 129<br>130<br>131                                           | D7<br>D6<br>D5                               |     |            |

| 59<br>60                                     | FDI<br>NC                                                             | 129<br>130                                                  | D7<br>D6                                     |     |            |

| 59<br>60<br>61                               | FDI<br>NC<br>FGND0                                                    | 129<br>130<br>131                                           | D7<br>D6<br>D5                               |     |            |

| 59<br>60<br>61<br>62<br>63                   | FDI<br>NC<br>FGND0<br>HSYNC<br>VSYNC                                  | 129<br>130<br>131<br>132<br>133                             | D7<br>D6<br>D5<br>D4<br>D3                   |     |            |

| 59<br>60<br>61<br>62<br>63<br>64             | FDI<br>NC<br>FGND0<br>HSYNC<br>VSYNC<br>AGND1                         | 129<br>130<br>131<br>132<br>133<br>134                      | D7<br>D6<br>D5<br>D4<br>D3<br>D2             |     |            |

| 59<br>60<br>61<br>62<br>63<br>64<br>65       | FDI<br>NC<br>FGND0<br>HSYNC<br>VSYNC<br>AGND1<br>NC                   | 129<br>130<br>131<br>132<br>133<br>134<br>135               | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1       |     |            |

| 59<br>60<br>61<br>62<br>63<br>64<br>65<br>66 | FDI<br>NC<br>FGND0<br>HSYNC<br>VSYNC<br>AGND1<br>NC<br>AVDD1          | 129<br>130<br>131<br>132<br>133<br>134<br>135<br>136        | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0 |     |            |

| 59<br>60<br>61<br>62<br>63<br>64<br>65<br>66 | FDI<br>NC<br>FGND0<br>HSYNC<br>VSYNC<br>AGND1<br>NC<br>AVDD1<br>AVDD2 | 129<br>130<br>131<br>132<br>133<br>134<br>135<br>136<br>137 | D7 D6 D5 D4 D3 D2 D1 D0 IRL#                 |     |            |

| 59<br>60<br>61<br>62<br>63<br>64<br>65<br>66 | FDI<br>NC<br>FGND0<br>HSYNC<br>VSYNC<br>AGND1<br>NC<br>AVDD1          | 129<br>130<br>131<br>132<br>133<br>134<br>135<br>136        | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0 |     |            |

| 59<br>60<br>61<br>62<br>63<br>64<br>65<br>66 | FDI<br>NC<br>FGND0<br>HSYNC<br>VSYNC<br>AGND1<br>NC<br>AVDD1<br>AVDD2 | 129<br>130<br>131<br>132<br>133<br>134<br>135<br>136<br>137 | D7 D6 D5 D4 D3 D2 D1 D0 IRL#                 |     |            |

#### 2.7.2 Pin List Sorted By Signal Name

Table 2-2: Pin List Sorted by Signal Name

| Table 2-2               | : PIN LI                 | st Sorted               | i by Sigi    | nai Name                                         |                                                  |

|-------------------------|--------------------------|-------------------------|--------------|--------------------------------------------------|--------------------------------------------------|

| A10                     | 160                      | D25                     | 107          | L3CLK                                            | 71                                               |

| A11                     | 159                      | D26                     | 106          | NC                                               | 13                                               |

| A12                     | 157                      | D27                     | 104          | NC                                               | 44                                               |

| A13                     | 156                      | D28                     | 103          | NC                                               | 60                                               |

|                         |                          |                         |              | NC                                               |                                                  |

| A14                     | 154                      | D29                     | 102          |                                                  | 65                                               |

| A15                     | 153                      | D3                      | 133          | NC                                               | 84                                               |

| A16                     | 152                      | D30                     | 101          | NC                                               | 175                                              |

| A17                     | 151                      | D31                     | 99           | NC                                               | 176                                              |

| A18                     | 150                      | D4                      | 132          | OSCI                                             | 18                                               |

| A19                     | 148                      | D5                      | 131          | OSCO                                             | 19                                               |

| A2                      | 169                      | D6                      | 130          | PDWN#                                            | 22                                               |

| A20                     | 147                      | D7                      | 129          | PMCLK                                            | 174                                              |

|                         |                          |                         |              |                                                  |                                                  |

| A21                     | 146                      | D8                      | 128          | POR#                                             | 21                                               |

| A22                     | 145                      | D9                      | 126          | PWM0                                             | 2                                                |

| A23                     | 143                      | DACK#                   | 140          | PWM1                                             | 1                                                |

| A24                     | 142                      | DRAK#                   | 139          | RDWR#                                            | 91                                               |

| A25                     | 141                      | DREQ#                   | 138          | STATUS0                                          | 172                                              |

| A3                      | 168                      | EDTMEN                  | 6            | STATUS1                                          | 170                                              |

| A4                      | 167                      | EN7                     | 20           | TMD0                                             | 16                                               |

|                         |                          | ENCTL                   | 11           | TMD1                                             | 15                                               |

| A5                      | 166                      |                         |              |                                                  |                                                  |

| A6                      | 164                      | ENVDD                   | 10           | TMEN                                             | 14                                               |

| A7                      | 163                      | ENVEE                   | 9            | VDD                                              | 12                                               |

| A8                      | 162                      | FD0                     | 57           |                                                  | <u> </u>                                         |

| A9                      | 161                      | FD1                     | 55           | VDD                                              | 100                                              |

| AB                      | 87                       | FD10                    | 43           | VDD                                              | 144                                              |

| AG                      | 75                       | FD11                    | 42           | VDDIO                                            | 4                                                |

| AGND1                   | 64                       | FD12                    | 41           | VREFIO                                           | 85                                               |

|                         |                          |                         |              | VSYNC                                            |                                                  |

| AGND2                   | 69                       | FD13                    | 40           |                                                  | 63                                               |

| AGND3                   | 70                       | FD14                    | 38           | WAIT#/RDY#                                       | 173                                              |

| AGNDC1                  | 74                       | FD15                    | 37           | WE0                                              | 98                                               |

| AGNDC2                  | 81                       | FD16                    | 36           | WE1                                              | 97                                               |

| AGNDC3                  | 83                       | FD17                    | 35           | WE2                                              | 96                                               |

| AGNDC4                  | 88                       |                         |              |                                                  |                                                  |

| AR                      | 80                       | FD18                    | 34           | WE3                                              | 94                                               |

| AVDD1                   |                          |                         |              | VVLJ                                             | 34                                               |

|                         | 66                       | FD19                    | 32           |                                                  |                                                  |

| AVDD2                   | 67                       | FD2                     | 54           |                                                  |                                                  |

| AVDD3                   | 72                       | FD20                    | 31           |                                                  |                                                  |

| AVDDC1                  | 76                       | FD21                    | 30           |                                                  |                                                  |

| AVDDC2                  | 77                       | FD22                    | 29           |                                                  |                                                  |

| AVDDC3                  | 79                       | FD23                    | 28           |                                                  |                                                  |

| AVDDC4                  | 86                       |                         |              |                                                  |                                                  |

| BS#                     | 90                       | FD3                     | 53           |                                                  |                                                  |

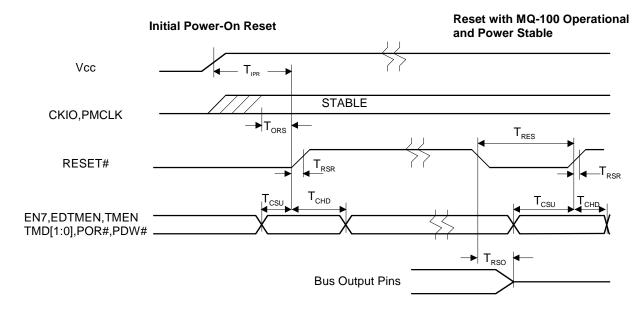

|                         |                          | FD4                     | 52           |                                                  |                                                  |