## LM4941 Boomer® Audio Power Amplifier Series

# 1.25 Watt Fully Differential Audio Power Amplifier With RF Suppression and Shutdown

## **General Description**

The LM4941 is a fully differential audio power amplifier primarily designed for demanding applications in mobile phones and other portable communication device applications. It is capable of delivering 1.25 watts of continuous average power to a  $8\Omega$  load with less than 1% distortion (THD+N) from a  $5V_{DC}$  power supply. The LM4941 does not require output coupling capacitors or bootstrap capacitors, and therefore is ideally suited for mobile phone and other small form factor applications where minimal PCB space is a primary requirement.

The LM4941 also features proprietary internal circuitry that suppresses the coupling of RF signals into the chip. This is important because certain types of RF signals (such as GSM) can couple into audio amplifiers in such a way that part of the signal is heard through the speaker. The RF suppression circuitry in the LM4941 makes it well-suited for portable applications in which strong RF signals generated by an antenna from or a cellular phone or other portable electronic device may couple audibly into the amplifier.

Other features include a low-power consumption shutdown mode, internal thermal shutdown protection, and advanced pop & click circuitry.

## **Key Specifications**

■ Improved PSRR at 217Hz 95dB (typ)

■ Power Output, V<sub>DD</sub> = 5.0V,

$R_{L} = 8\Omega$ , 1% THD+N 1.25W (typ)

■ Power Output,  $V_{DD} = 3.0V$ ,

$R_L = 8\Omega$ , 1% THD+N 430mW (typ)

■ Shutdown Current 0.1µA (typ)

## **Features**

- Improved RF suppression, by up to 20dB over previous designs in selected applications

- Fully differential amplification

- Available in space-saving micro SMD package

- Ultra low current shutdown mode

- Can drive capacitive loads up to 100pF

- Improved pop & click circuitry eliminates noises during turn-on and turn-off transitions

- 2.4 5.5V operation

- No output coupling capacitors, snubber networks or bootstrap capacitors required

## **Applications**

- Mobile phones

- PDAs

- Portable electronic devices

## **Typical Application**

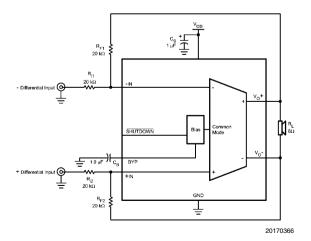

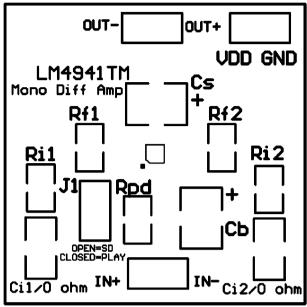

FIGURE 1. Typical Audio Amplifier Application Circuit

Boomer® is a registered trademark of National Semiconductor Corporation.

# **Connection Diagrams**

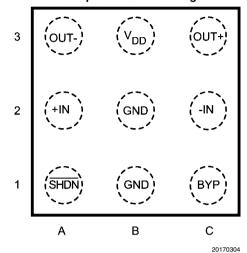

## 9 Bump micro SMD Package

Top View

Order Number LM4941TM

See NS Package Number TMD09AAA

# Pin 1 Top View X = Date Code V = Die Traceability G = Boomer Family H6 = LM4941TM

micro SMD Markings

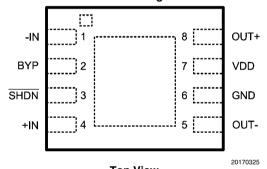

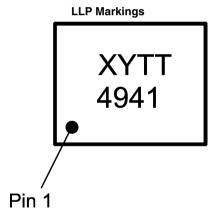

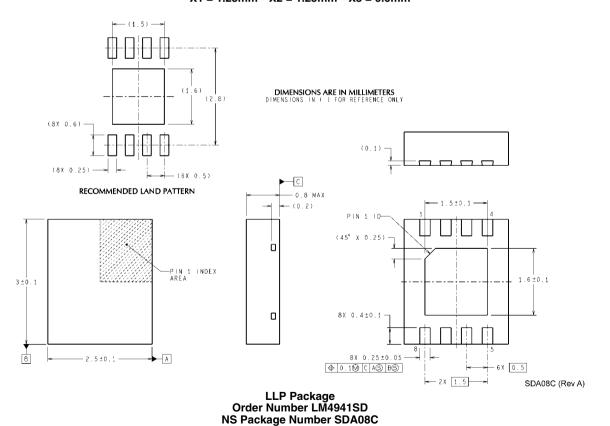

**LLP Package**

Top View Order Number LM4941SD See NS Package Number SDA08C

Top View

XY = Date Code

TT = Die Run Traceability

4941 = LM4941SD

www.national.com

# **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 6.0VStorage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C Input Voltage -0.3V to  $V_{DD}$  +0.3VPower Dissipation (Note 3) Internally Limited

ESD Susceptibility (Note 4) 2000V ESD Susceptibility (Note 5) 200V Junction Temperature 150°C Thermal Resistance

$\theta_{JA}$  (TM) 100°C/W  $\theta_{JA}$  (LLP) 71°C/W

Soldering Information See AN-1187

## **Operating Ratings**

Temperature Range

$T_{\text{MIN}} \le T_{\text{A}} \le T_{\text{MAX}} \qquad \qquad -40^{\circ}\text{C} \le T_{\text{A}} \le 85^{\circ}\text{C}$  Supply Voltage  $2.4\text{V} \le V_{\text{DD}} \le 5.5\text{V}$

# Electrical Characteristics $V_{DD} = 5V$ (Notes 1, 2)

|                   |                                   |                                                        | LM4941        |              | Units<br>(Limits) |

|-------------------|-----------------------------------|--------------------------------------------------------|---------------|--------------|-------------------|

| Symbol            | Parameter                         | Conditions                                             | Typical Limit |              |                   |

|                   |                                   |                                                        | (Note 6)      | (Notes 7, 8) | (Lillins)         |

| I <sub>DD</sub>   | Ouissant Dower Supply Current     | V <sub>IN</sub> = 0V, no load                          | 1.7           | 2.3          | mA (max)          |

|                   | Quiescent Power Supply Current    | $V_{IN} = 0V, R_L = 8\Omega$                           | 1.7           |              | mA                |

| I <sub>SD</sub>   | Shutdown Current                  | V <sub>SHDN</sub> = GND                                | 0.1           | 0.8          | μA (max)          |

|                   | Output Power                      | THD+N = 1% (max); f = 1 kHz                            |               |              |                   |

| Б                 |                                   | $R_L = 8\Omega$                                        | 1.25          | 1.15         | W (min)           |

| P <sub>O</sub>    |                                   | THD+N = 10% (max); f = 1 kHz                           |               |              |                   |

|                   |                                   | $R_L = 8\Omega$                                        | 1.54          |              | W                 |

| THD+N             | Total Harmonic Distortion + Noise | $P_{O} = 0.7 \text{ W; } f = 1 \text{kHz}$             | 0.04          |              | %                 |

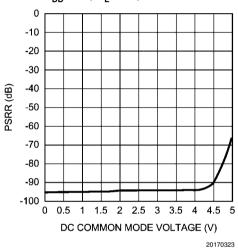

|                   | Power Supply Rejection Ratio      | V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> Sine        |               |              |                   |

| PSRR              |                                   | f = 217Hz (Note 9)                                     | 95            | 80           | dB (min)          |

|                   |                                   | f = 1kHz (Note 9)                                      | 90            |              | dB                |

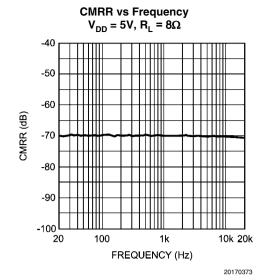

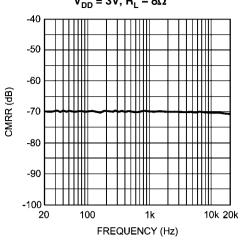

| CMRR              | Common-Mode Rejection Ratio       | f = 217Hz, V <sub>CM</sub> = 200mV <sub>P-P</sub> Sine | 70            |              | dB                |

|                   |                                   | f = 20Hz-20kHz , V <sub>CM</sub> = 200mV <sub>pp</sub> | 70            |              | dB                |

| V <sub>os</sub>   | Output Offset Voltage             | V <sub>IN</sub> = 0V                                   | 2             | 6            | mV (max)          |

| V <sub>SDIH</sub> | Shutdown Voltage Input High       |                                                        |               | 1.4          | V (min)           |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low        |                                                        |               | 0.4          | V (max)           |

| SNR               | Signal-to-Noise Ratio             | P <sub>O</sub> = 1W, f = 1kHz                          | 108           |              | dB                |

| T <sub>WU</sub>   | Wake-up Time from Shutdown        | C <sub>BYPASS</sub> = 1µF                              | 12            |              | ms                |

# **Electrical Characteristics V<sub>DD</sub> = 3V**

|                   |                                   |                                                       | LM4941   |              |                   |

|-------------------|-----------------------------------|-------------------------------------------------------|----------|--------------|-------------------|

| Symbol            | Parameter                         | Conditions                                            | Typical  | Limit        | Units<br>(Limits) |

|                   |                                   |                                                       | (Note 6) | (Notes 7, 8) | (Lillins)         |

| I <sub>DD</sub>   | Quiescent Power Supply Current    | V <sub>IN</sub> = 0V, no load                         | 1.6      | 2.2          | mA (max)          |

|                   |                                   | $V_{IN} = 0V, R_L = 8\Omega$                          | 1.6      |              | mA                |

| I <sub>SD</sub>   | Shutdown Current                  | V <sub>SHDN</sub> = GND                               | 0.1      | 0.8          | μΑ (max)          |

|                   | Output Power                      | THD+N = 1% (max); f = 1 kHz                           |          |              |                   |

| D                 |                                   | $R_L = 8\Omega$                                       | 0.43     |              | W                 |

| Po                |                                   | THD+N = 10% (max); f = 1 kHz                          |          |              |                   |

|                   |                                   | $R_L = 8\Omega$                                       | 0.54     |              | W                 |

| THD+N             | Total Harmonic Distortion + Noise | $P_{O} = 0.25W; f = 1kHz$                             | 0.05     |              | %                 |

|                   | Power Supply Rejection Ratio      | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub> Sine        |          |              |                   |

| PSRR              |                                   | f = 217Hz (Note 9)                                    | 95       |              | dB                |

|                   |                                   | f = 1kHz (Note 9)                                     | 90       |              | dB                |

| CMRR              | Common-Mode Rejection Ratio       | f = 217Hz, V <sub>CM</sub> = 200mV <sub>PP</sub> Sine | 70       |              | dB                |

| V <sub>os</sub>   | Output Offset Voltage             | $V_{IN} = 0V$                                         | 2        | 6            | mV (max)          |

| V <sub>SDIH</sub> | Shutdown Voltage Input High       |                                                       |          | 1.4          | V (min)           |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low        |                                                       |          | 0.4          | V (max)           |

| T <sub>WU</sub>   | Wake-up Time from Shutdown        | C <sub>BYPASS</sub> = 1μF                             | 8        |              | ms                |

Note 1: All voltages are measured with respect to the ground pin, unless otherwise specified.

**Note 2:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

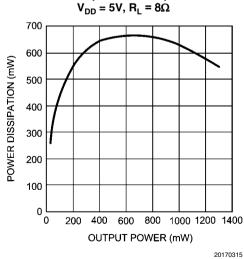

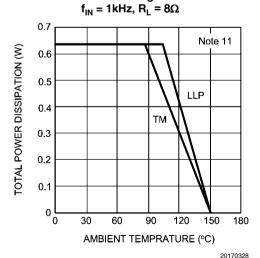

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4941, see power derating curve for additional information.

- Note 4: Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

- Note 5: Machine Model, 220pF 240pF discharged through all pins.

- Note 6: Typicals are measured at 25°C and represent the parametric norm.

- Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

- Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

- Note 9:  $10\Omega$  terminated input.

- Note 10: Data taken with Bandwidth = 80kHz,  $A_V = 1V/V$  and inputs are AC-coupled except where specified.

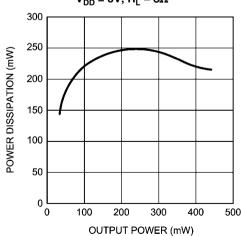

- Note 11: Maximum Power Dissipation (P<sub>DMAX</sub>) in the device occurs at an output power level significantly below full output power. P<sub>DMAX</sub> can be calculated using Equation 3 shown in the Application section. It may also be obtained from the Power Dissipation graphs.

## **External Components Description**

#### (Figure 1)

| Comp | onents                                                                                                                                                                                                                            | Functional Description                                                                                                                                                                                          |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.   | <ol> <li>C<sub>S</sub> Supply bypass capacitor which provides power supply filtering. Refer to the <b>Power Supply Bypassing</b> information concerning proper placement and selection of the supply bypass capacitor.</li> </ol> |                                                                                                                                                                                                                 |  |  |

| 2.   | СВ                                                                                                                                                                                                                                | Bypass pin capacitor which provides half-supply filtering. Refer to the section, <b>Proper Selection of External Components</b> , for information concerning proper placement and selection of C <sub>B</sub> . |  |  |

| 3.   | R <sub>i</sub>                                                                                                                                                                                                                    | Inverting input resistance which sets the closed-loop gain in conjunction with R <sub>F</sub> .                                                                                                                 |  |  |

| 4.   | R <sub>F</sub>                                                                                                                                                                                                                    | External feedback resistance which sets the closed-loop gain in conjunction with R <sub>i</sub> .                                                                                                               |  |  |

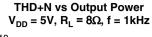

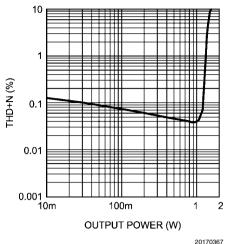

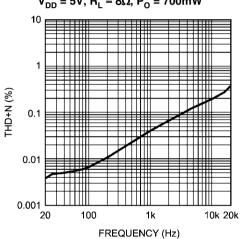

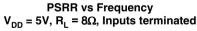

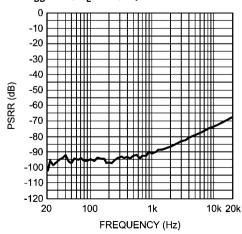

# **Typical Performance Characteristics** (Note 10)

THD+N vs Frequency  $V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$ ,  $P_O$  = 700mW

20170369

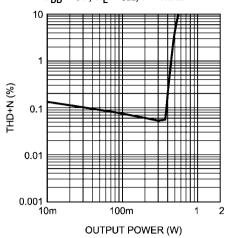

THD+N vs Output Power  $V_{DD} = 3V$ ,  $R_1 = 8\Omega$ , f = 1kHz

20170368

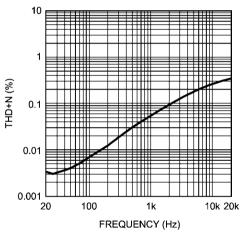

# THD+N vs Frequency $V_{DD}$ = 3V, $R_L$ = 8 $\Omega$ , $P_O$ = 250mW

20170370

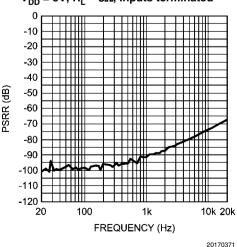

# PSRR vs Frequency $V_{DD}$ = 3V, $R_L$ = $8\Omega$ , Inputs terminated

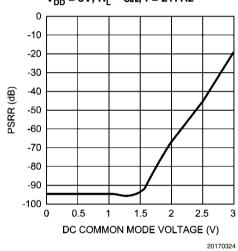

# PSRR vs Common Mode Voltage $V_{DD}$ = 5V, $R_L$ = 8 $\Omega$ , f = 217Hz

# Power Dissipation vs Output Power

# CMRR vs Frequency $V_{DD} = 3V$ , $R_L = 8\Omega$

20170374

# PSRR vs Common Mode Voltage $V_{DD}$ = 3V, $R_L$ = 8 $\Omega$ , f = 217Hz

Power Dissipation vs Output Power  $V_{DD}$  = 3V,  $R_L$  =  $8\Omega$

20170316

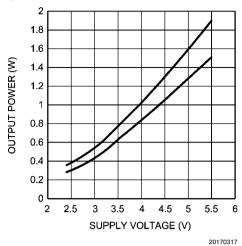

# Output Power vs Supply Voltage $R_L = 8\Omega$ , Top-THD+N = 10%; Bot-THD+N = 1%

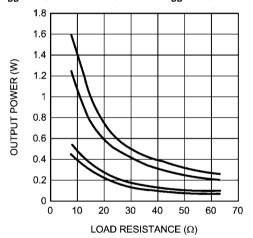

# Output Power vs Load Resistance Top-V<sub>DD</sub> = 5V, 10% THD+N, Topmid-V<sub>DD</sub> = 5V, 1% THD+N Bot-V<sub>DD</sub> = 3V, 10% THD+N, Botmid-V<sub>DD</sub> = 3V, 1% THD+N

## **Power Derating Curve**

20170319

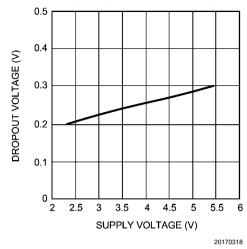

## Clipping Voltage vs Supply Voltage

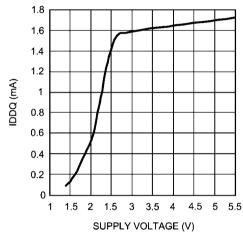

## IDDQ vs Supply Voltage

## **Application Information**

#### **OPTIMIZING RF IMMUNITY**

The internal circuitry of the LM4941 suppresses the amount of RF signal that is coupled into the chip. However, certain external factors, such as output trace length, output trace orientation, distance between the chip and the antenna, antenna strength, speaker type, and type of RF signal, may affect the RF immunity of the LM4941. In general, the RF immunity of the LM4941 is application specific. Nevertheless, optimal RF immunity can be achieved by using short output traces and increasing the distance between the LM4941 and the antenna.

#### **DIFFERENTIAL AMPLIFIER EXPLANATION**

The LM4941 is a fully differential audio amplifier that features differential input and output stages. Internally this is accomplished by two circuits: a differential amplifier and a common mode feedback amplifier that adjusts the output voltages so that the average value remains  $V_{\rm DD}$  / 2. When setting the differential gain, the amplifier can be considered to have "halves". Each half uses an input and feedback resistor ( $R_{\rm i}$  and  $R_{\rm F}$ ) to set its respective closed-loop gain (see Figure 1). With  $R_{\rm i1}=R_{\rm i2}$  and  $R_{\rm F1}=R_{\rm F2}$ , the gain is set at  $-R_{\rm F}$  /  $R_{\rm i}$  for each half. This results in a differential gain of

$$A_{VD} = -R_F/R_i \tag{1}$$

It is extremely important to match the input resistors to each other, as well as the feedback resistors to each other for best amplifier performance. See the **Proper Selection of External Components** section for more information. A differential amplifier works in a manner where the difference between the two input signals is amplified. In most applications, input signals will be 180° out of phase with each other. The LM4941 can be used, however, as a single-ended input amplifier while still retaining its fully differential benefits because it simply amplifies the difference between the inputs.

All of these applications provide what is known as a "bridged mode" output (bridge-tied-load, BTL). This results in output signals that are 180° out of phase with respect to each other. Bridged mode operation is different from the single-ended amplifier configuration that connects the load between the amplifier output and ground. A bridged amplifier design has distinct advantages over the single-ended configuration: it provides differential drive to the load, thus doubling maximum possible output swing for a specific supply voltage. Four times the output power is possible compared with a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited or clipped. In order to choose an amplifier's closed-loop gain without causing excess clipping, please refer to the **Audio Power Amplifier Design** section.

A bridged configuration, such as the one used in the LM4941, also creates a second advantage over single-ended amplifiers. Since the differential outputs are biased at half-supply, no net DC voltage exists across the load. This assumes that the input resistor pair and the feedback resistor pair are properly matched (see **Proper Selection of External Components**). BTL configuration eliminates the output coupling capacitor required in single-supply, single-ended amplifier configurations. If an output coupling capacitor is not used in

a single-ended output configuration, the half-supply bias across the load would result in both increased internal IC power dissipation as well as permanent loudspeaker damage. Further advantages of bridged mode operation specific to fully differential amplifiers like the LM4941 include increased power supply rejection ratio, common-mode noise reduction, and click and pop reduction.

#### **POWER DISSIPATION**

Power dissipation is a major concern when designing a successful amplifier, whether the amplifier is bridged or single-ended. Equation 2 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = (V_{DD})^2 / (2\pi^2 R_L)$$

Single-Ended (2)

However, a direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation versus a single-ended amplifier operating at the same conditions.

$$P_{DMAX} = 4 * (V_{DD})^2 / (2\pi^2 R_L)$$

Bridge Mode (3)

Since the LM4941 has bridged outputs, the maximum internal power dissipation is four times that of a single-ended amplifier. Even with this substantial increase in power dissipation, the LM4941 does not require additional heatsinking under most operating conditions and output loading. From Equation 3, assuming a 5V power supply and an  $8\Omega$  load, the maximum power dissipation point is 625mW. The maximum power dissipation point obtained from Equation 3 must not be greater than the power dissipation results from Equation 4:

$$P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$$

(4)

The LM4941's  $\theta_{JA}$  in an TMD09AAA package is 100°C/W. Depending on the ambient temperature,  $T_A$ , of the system surroundings, Equation 4 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 3 is greater than that of Equation 4, then either the supply voltage must be decreased, the load impedance increased, the ambient temperature reduced, or the θ ι reduced with heatsinking. In many cases, larger traces near the output, V<sub>DD</sub>, and GND pins can be used to lower the  $\theta_{1A}$ . The larger areas of copper provide a form of heatsinking allowing higher power dissipation. For the typical application of a 5V power supply, with an  $8\Omega$  load, the maximum ambient temperature possible without violating the maximum junction temperature is approximately 87.5°C provided that device operation is around the maximum power dissipation point. Recall that internal power dissipation is a function of output power. If typical operation is not around the maximum power dissipation point, the LM4941 can operate at higher ambient temperatures. Refer to the Typical Performance Characteristics curves for power dissipation information.

## **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection ratio (PSRR). The capacitor location on both the bypass and power supply pins should be as close to the device as possible. Typical applications employ a 5V regulator with 10µF and 0.1µF bypass capacitors that increase supply sta-

bility. This, however, does not eliminate the need for bypassing the supply nodes of the LM4941. The LM4941 will operate without the bypass capacitor  $C_{\rm B}$ , although the PSRR may decrease. A 1µF capacitor is recommended for  $C_{\rm B}$ . This value maximizes PSRR performance. Lesser values may be used, but PSRR decreases at frequencies below 1kHz. The issue of  $C_{\rm B}$  selection is thus dependant upon desired PSRR and click and pop performance as explained in the section **Proper Selection of External Components**.

#### SHUTDOWN FUNCTION

In order to reduce power consumption while not in use, the LM4941 contains shutdown circuitry that is used to turn off the amplifier's bias circuitry. The device may then be placed into shutdown mode by toggling the SHDN pin to logic low. It is best to switch between ground and supply for maximum performance. While the device may be disabled with shutdown voltages in between ground and supply, the idle current may be greater than the typical value of 0.1µA. In either case, the SHDN pin should be tied to a definite voltage to avoid unwanted state changes.

In many applications, a microcontroller or microprocessor output is used to control the shutdown circuitry, which provides a quick, smooth transition to shutdown. Another solution is to use a single-throw switch in conjunction with an external pull-up resistor. This scheme guarantees that the shutdown pin will not float, thus preventing unwanted state changes.

#### PROPER SELECTION OF EXTERNAL COMPONENTS

Proper selection of external components in applications using integrated power amplifiers is critical when optimizing device and system performance. Although the LM4941 is tolerant to a variety of external component combinations, consideration of component values must be made when maximizing overall system quality.

The LM4941 is unity-gain stable, giving the designer maximum system flexibility. The LM4941 should be used in low closed-loop gain configurations to minimize THD+N values and maximize signal to noise ratio. Low gain configurations require large input signals to obtain a given output power. Input signals equal to or greater than 1V<sub>RMS</sub> are available from

sources such as audio codecs. When used in its typical application as a fully differential power amplifier the LM4941 does not require input coupling capacitors for input sources with DC common-mode voltages of less than  $V_{\rm DD}.$  Exact allowable input common-mode voltage levels are actually a function of  $V_{\rm DD},\,R_{\rm i},$  and  $R_{\rm F}$  and may be determined by Equation 5:

$$V_{CMi} < (V_{DD}-1.2)(R_i+R_F)/R_F-V_{DD}/2(R_i/R_F)$$

(5)

$$-R_F/R_i = A_{VD}$$

(6)

When using DC coupled inputs, special care must be taken to match the values of the input resistors ( $\rm R_{i1}$  and  $\rm R_{i2}$ ) to each other. Because of the balanced nature of differential amplifiers, resistor matching differences can result in net DC currents across the load. This DC current can increase power consumption, internal IC power dissipation, reduce PSRR, and possibly damaging the loudspeaker. The chart below demonstrates this problem by showing the effects of differing values between the feedback resistors while assuming that the input resistors are perfectly matched. The results below apply to the application circuit shown in Figure 1, and assumes that  $\rm V_{DD}=5V,\ R_L=8\Omega,$  and the system has DC coupled inputs tied to ground.

| Tolerance | R <sub>i1</sub> | R <sub>i2</sub> | V <sub>01</sub> -V <sub>02</sub> | I <sub>LOAD</sub> |

|-----------|-----------------|-----------------|----------------------------------|-------------------|

| 20%       | 0.8R            | 1.2R            | -0.500V                          | 62.5mA            |

| 10%       | 0.9R            | 1.1R            | -0.250V                          | 31.25mA           |

| 5%        | 0.95R           | 1.05R           | -0.125V                          | 15.63mA           |

| 1%        | 0.99R           | 1.01R           | -0.025V                          | 3.125mA           |

| 0%        | R               | R               | 0                                | 0                 |

Since the same variations can have a significant effect on PSRR and CMRR performance, it is highly recommended that the input resistors be matched to 1% tolerance or better for best performance.

www.national.com

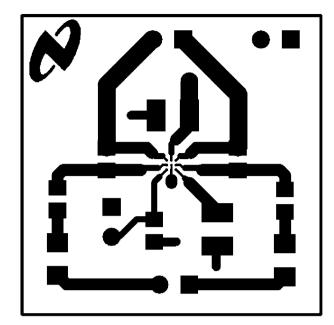

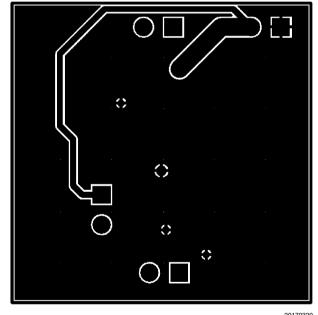

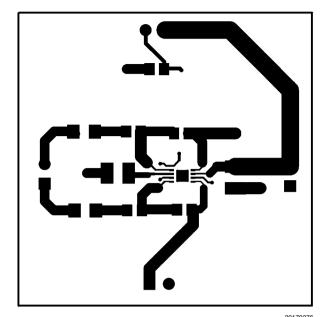

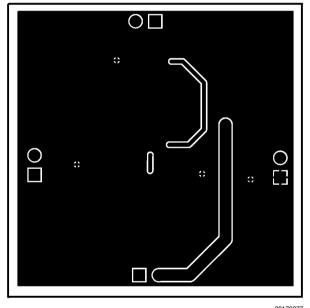

# **Recommended TM Board Layout**

Recommended TM Board Layout: Top Layer

Recommended TM Board Layout: Top Overlay

Recommended TM Board Layout: Bottom Layer

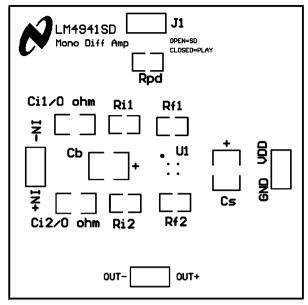

# **Recommended LLP Board Layout**

Recommended LLP Board Layout: Top Layer

Recommended LLP Board Layout: Top Overlay

Recommended LLP Board Layout: Bottom Layer

# LM4941 Reference Design Boards Bill Of Materials

| Designator       | Value | Tolerance | Part Description                  | Comments                                 |

|------------------|-------|-----------|-----------------------------------|------------------------------------------|

| Ri1, Ri2         | 20kΩ  | 0.10%     | 1/10W, 0.1% 0805 Resistor         |                                          |

| Rf1, Rf2         | 20kΩ  | 0.10%     | 1/10W, 0.1% 0805 Resistor         |                                          |

| Ci1, Ci2         | 0Ω    |           | 1/10W, 0.1% 0805 Resistor         |                                          |

| Cb, Cs           | 1µF   | 10%       | 16V Tantalum 1210 Capacitor       |                                          |

| In, Out, VDD, J1 |       |           | 0.100" 1x2 header, Vertical mount | Input, Output, VDD/GND, Shutdown Control |

# **Revision History**

| Rev | Date     | Description                                                                |  |  |

|-----|----------|----------------------------------------------------------------------------|--|--|

| 1.0 | 06/28/06 | Initial release.                                                           |  |  |

| 1.1 | 07/10/06 | Added the LLP pkg mktg outline (per Kashif J.)                             |  |  |

| 1.2 | 08/04/06 | Added the LLP package and marking diagrams.                                |  |  |

| 1.3 | 10/12/06 | Edited some of the Typical Performance curves' labels and some text edits. |  |  |

| 1.4 | 10/25/06 | Added the LLP boards.                                                      |  |  |

| 1.5 | 11/07/06 | Text edits.                                                                |  |  |

| 1.6 | 11/15/06 | Replaced curve 20170381 with 20170382 and input text edits.                |  |  |

| 1.7 | 03/09/07 | Changed the Limit value from 70 to 80 on the PSRR in the EC 5V EC table.   |  |  |

# Physical Dimensions inches (millimeters) unless otherwise noted

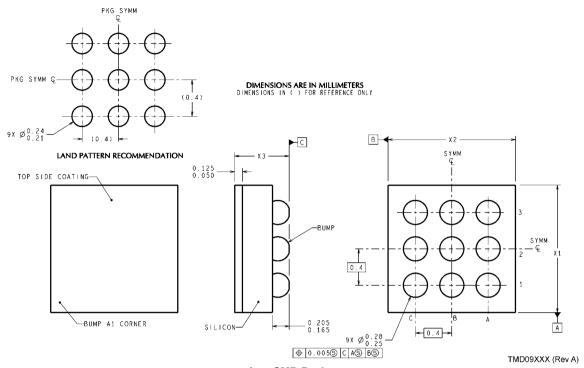

micro SMD Package Order Number LM4941TM NS Package Number TMD09AAA X1 = 1.25mm X2 = 1.25mm X3 = 0.6mm

## **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560