# **Motor Control using NXP's LPC2900**

## **Agenda**

- ▶ LPC2900 Overview and Development tools

- Control of BLDC Motors using the LPC2900

- CPU Load of BLDCM and PMSM

- Enhancing performance

- LPC2900 Demo BLDC motor

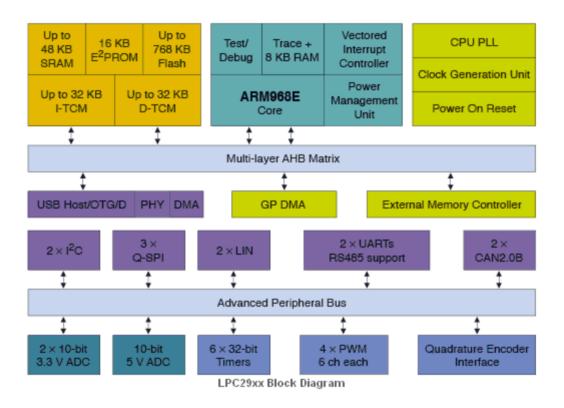

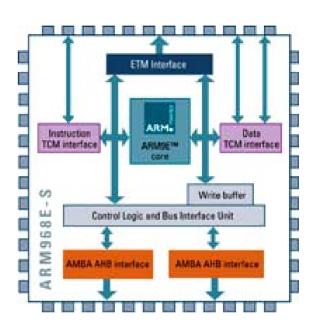

# LPC2900 Block diagram

## LPC2900 Summary

#### ARM968E core

- 125 MHz operation

- Vectored Interrupt Controller

- Power Management Unit

- Clock Generation Unit

- Embedded Trace with 8 KB buffer

#### Memories

- Up to 768 KB Flash

- Up to 48 KB SRAM (+ 8KB)

- Up to 32 KB I- & D- TCM

- 16 KB EEPROM (Byte)

- External Memory Controller

#### Analog Peripherals

- Two 3.3 V 10-bit/8-ch ADC's

- One 5V 10-bit/8-ch ADC's

#### Serial Peripherals

- USB 2.0 full-speed device/Host/OTG controller with on-chip PHY

- Two LIN 2.0 master controllers

- Up to four UARTs with baud rate generation, LIN and RS-485 support

- Two CAN 2.0B controllers

- Three Q-SPI controllers

- Two I<sup>2</sup>C-bus interfaces

#### Other Peripherals

- General Purpose DMA controller

- Motor control PWM and Quadrature Encoder Interface to support threephase motors

- Six 32-bit timers

- Up to 148 General Purpose I/O

# **LPC2900 Series Details**

| P/N        | Flash<br>(KB) | SRAM<br>(KB) | TCM(KB)<br>I- /D- | EEPROM<br>(KB) | CAN | LIN | UART | SPI | ADC | BMI | USB<br>Device | USB<br>OTG | USB<br>Host | Package |

|------------|---------------|--------------|-------------------|----------------|-----|-----|------|-----|-----|-----|---------------|------------|-------------|---------|

| LPC2939    | 768           | 48           | 32/32             | 16             | 2   | 2   | 4    | 3   | 3   | Υ   | Υ             | Υ          | Υ           | LQFP208 |

| LPC2930    | 0             | 48           | 32/32             | 16             | 2   | 2   | 4    | 3   | 3   | Υ   | Υ             | Υ          | Υ           | LQFP208 |

| LPC2929    | 768           | 48           | 32/32             | 16             | 2   | 2   | 4    | 3   | 3   | Υ   | Υ             | Υ          | -           | LQFP144 |

| LPC2927    | 512           | 48           | 32/32             | 16             | 2   | 2   | 4    | 3   | 3   | Υ   | Υ             | Υ          | -           | LQFP144 |

| LPC2925    | 512           | 32           | 16/16             | 16             | 2   | -   | 4    | 3   | 2   | -   | Υ             | -          | -           | LQFP100 |

| LPC2923    | 256           | 16           | 16/16             | 16             | 2   | -   | 4    | 3   | 2   | -   | Υ             | -          | -           | LQFP100 |

| LPC2921    | 128           | 16           | 16/16             | 16             | 2   | -   | 4    | 3   | 2   | -   | Υ             | -          | -           | LQFP100 |

| LPC2919/01 | 768           | 48           | 16/16             | 16             | 2   | 2   | 2    | 3   | 2   | Υ   | -             | -          | -           | LQFP144 |

| LPC2917/01 | 512           | 48           | 16/16             | 16             | 2   | 2   | 2    | 3   | 2   | Υ   | -             | -          | -           | LQFP144 |

## **LPC2900 Development Tools**

#### **Evaluation Boards**

- Hitex and Keil

- AC and DC Motor Control Add On

#### **Compilers/Debuggers**

- ▶ Keil, IAR, GreenHills

- Code bundles

#### **Hardware Debuggers**

All Standard ARM JTAG hardware debuggers work with the LPC2900 devices

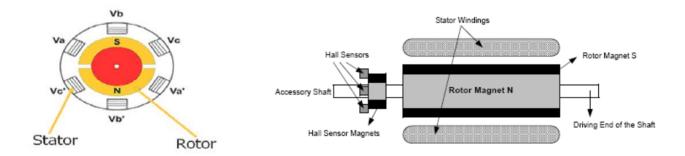

## **Overview Brushless DC EC Motors**

- There are two main EC-Motor types:

- Brushless Direct Current Motor (BLDCM)

- Permanent Magnet Synchronous Motor (PMSM)

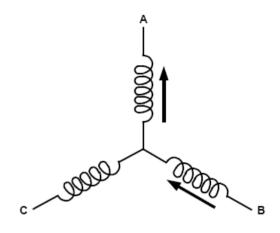

▶ EC-Motors consist of stator windings and a permanent-magnet rotor. The stator windings are controlled (commutated) by external electronics. The winding currents produce torque by interacting with the permanent magnet of the rotor and this keeps the Motor running.

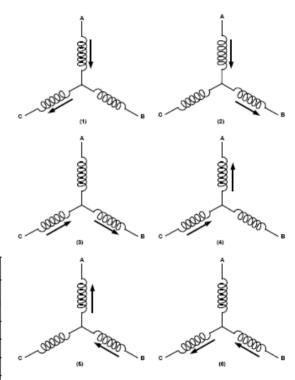

## **Brushless Motor Commutation**

- There are two main commutation methods:

- Sine-wave

- Six-step or block commutation

- Sine-wave commutation is used for PMSM

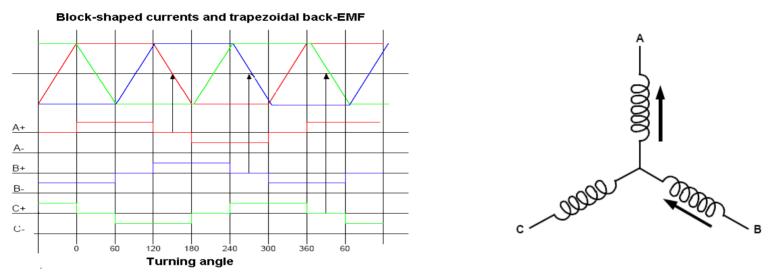

- Six Step Commutation is used BLDC Motors

- Drives channel current into only two windings at any one time

- Use PWM to control drive circuitry

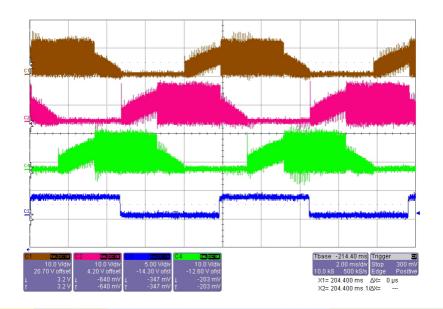

## **Back EMF**

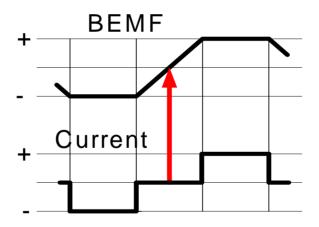

The main characteristics of BLDCMs are the square current waveforms and trapezoidal back-EMF.

- The amplitude of the current determines the torque of the motor.

- In practice switching the supply to the motor with a PWM pattern and adjusting its duty cycle control the effective amplitude

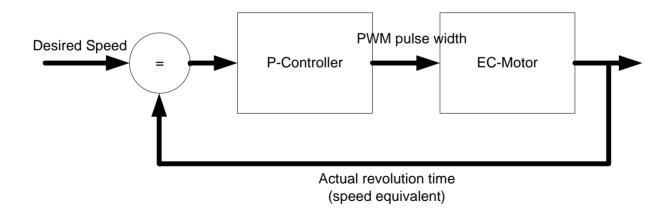

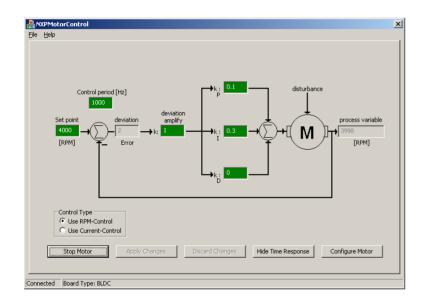

## **BLDCM** control

- BLDCM control mechanism via commutation point detection

- A timer measures the interval between commutation points

- Actual speed of motor is calculated

- P-controller adjusts PWM pulse width to control motor speed

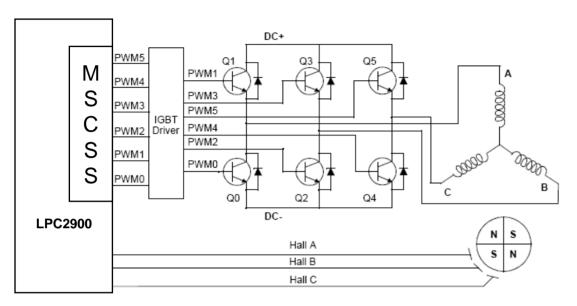

# Six Step Commutation – Closed Loop control

| Sequence | На | ill Sensor inp | out | Active DWMs       | Phase Current |     |     |

|----------|----|----------------|-----|-------------------|---------------|-----|-----|

| #        | Α  | В              | С   | - Active PWMs     | Α             | В   | С   |

| 1        | 0  | 0              | 1   | PWM1(Q1) PWM4(Q4) | DC+           | Off | DC- |

| 2        | 0  | 0              | 0   | PWM1(Q1) PWM2(Q2) | DC+           | DC- | Off |

| 3        | 1  | 0              | 0   | PWM5(Q5) PWM2(Q2) | Off           | DC- | DC+ |

| 4        | 1  | 1              | 0   | PWM5(Q5) PWM0(Q0) | DC-           | Off | DC+ |

| 5        | 1  | 1              | 1   | PWM3(Q3) PWM0(Q0) | DC-           | DC+ | Off |

| 6        | 0  | 1              | 1   | PWM3(Q3) PWM4(Q4) | Off           | DC+ | DC- |

## **Startup Open Loop - Hard Commutation**

- When the motor is halted the is no Hall sensor activity (interrupt)

- ▶ The control must use "hard" commutation for a predefined time.

- Use GPIO

- Switch the port function from PWM capture to GPIO

- By the appropriate applied commutation a Hall sensor interrupt is generated which makes "hard" commutation unnecessary.

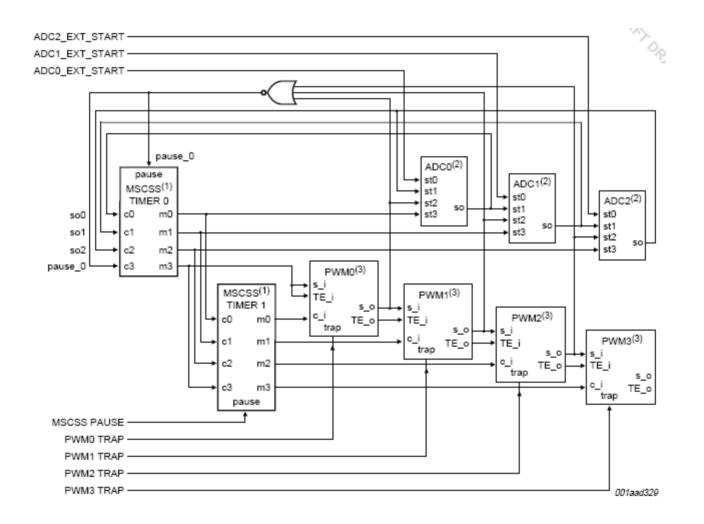

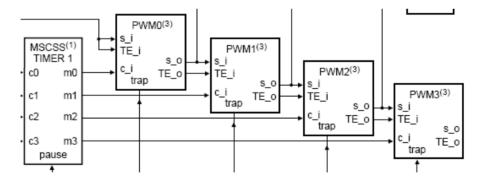

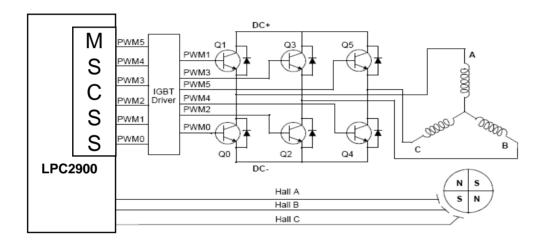

# **MSCSS Block diagram**

## **MSCSS** features for Motor Control

- The MSCSS provides useful features for motor control applications, making software implementation of motor control algorithms easier:

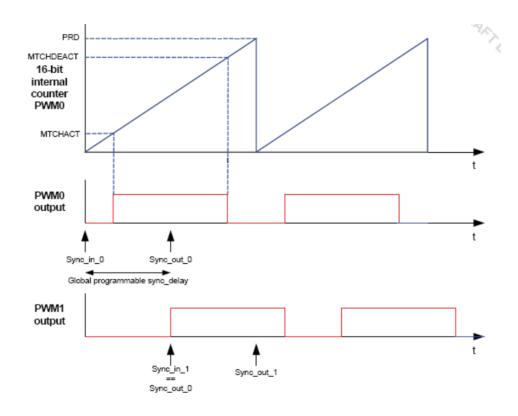

- Dual edge control

- PWM Synchronization delay

- ADC compare interrupt

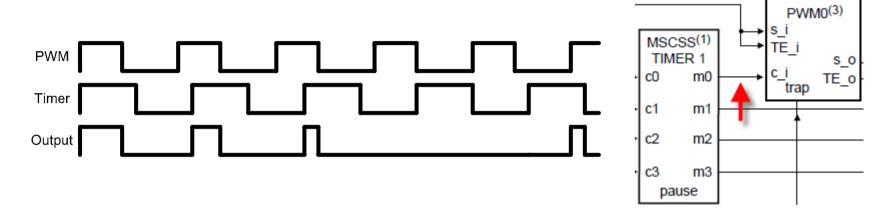

- Carrier input of PWM block

- Update PWM register through a timer match event

These features off-load the CPU

# PWM Dual edge and synchronization delay

## **ADC** compare interrupt

- 8 Channel 10bit ADC

- Configurable resolution: 2 to 10bit

- The ADC compare interrupt is a feature of the ADC.

- Interrupt when the conversion result is > or < a predefined threshold.</p>

- It reduces the interrupt load as no polling of the ADC result is required.

Table 347. COMPn register bit description

\* = reset value

| Bit       | Symbol     | Access | Value | Description                                                                       |

|-----------|------------|--------|-------|-----------------------------------------------------------------------------------|

| 31 to 18  | reserved   | R      | -     | Reserved; do not modify. Read as logic 0                                          |

| 17 and 16 | MATCH[1:0] | R/W    |       | Compare for values 'less than' or 'greater than<br>or equal to' the compare value |

|           |            |        | 00*   | No comparison is done                                                             |

|           |            |        | 01    | Unused                                                                            |

|           |            |        | 10    | Interrupt is generated when ADC data is less than compare data                    |

|           |            |        | 11    | Interrupt is generated when ADC data is<br>greater than or equal to compare data  |

| 15 to 10  | reserved   | R      | -     | Reserved; do not modify. Read as logic 0                                          |

| 9 to 0    | COMP_R     | R/W    |       | Compare data with respect to analog input<br>channel                              |

|           |            |        | 00h*  |                                                                                   |

## Carrier input of PWM block

This feature allows the PWM to be modulated by the MSCSS Timer

This mechanism is used to generate triangular signals, which represent approximated sine wave signals with little software overhead

## **Update PWM register via Timer match event**

- Update of PWM register value can be triggered by MSCSS timer 0

- Use this feature to update PWM settings

- After a preprogrammed time the PWM will be automatically updated

- This reduces CPU overhead

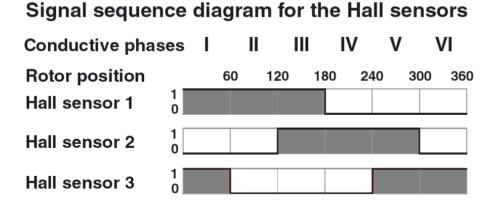

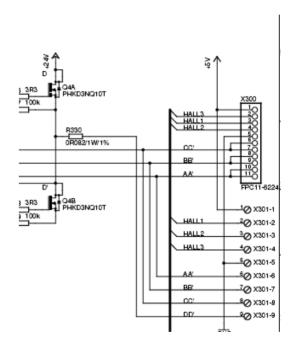

#### **Hall Sensor**

- Some motors have integrated Hall sensors for position measurement.

- Hall sensors directly indicate the commutation point. The control software has to switch to the next conduction phase on every edge of the sensor output.

- Connect to MSCSS PWM Capture inputs for control of motor

## **ADC** measurement of Hall sensor output

- ADC compare interrupt is used to detect the signal changes of the Hall sensor signals.

- Therefore the compare threshold has to be programmed with respect to the conduction state.

- With Hall sensors position information is always available even if the motor is standing still.

- Start → Use GPIO

- Run → Use as ADC

- The motor starts operation and an ADC compare interrupt is generated when a change on a Hall sensor signal is detected.

## PWM capturing of Hall sensor output

- This method uses an additional PWM block.

- ADC replaced by the PWM in capture mode.

- The start position is also derived from the GPIO pins.

- The capture ISR executes the control function and updates the PWM

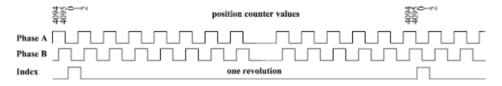

## **Quadrature Encoder**

- 3 signals, Indx, PhA and PhB, for position, direction & speed

- Programmable Digital filtering capability

- Direction and Position capture

- Velocity capture and compare feature

| Quadrature Encoder             | Hall Sensors                  |  |  |  |  |

|--------------------------------|-------------------------------|--|--|--|--|

| Three outputs                  | Three outputs                 |  |  |  |  |

| Doesn't give absolute position | Gives absolute position       |  |  |  |  |

| Gives 6 events per electrical  | Gives 6 events per electrical |  |  |  |  |

| revolution                     | revolution                    |  |  |  |  |

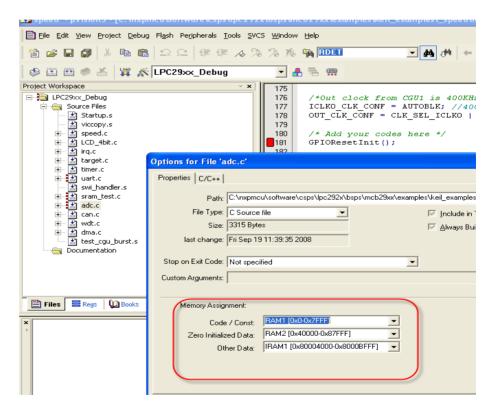

## **Enhancing performance using TCM**

- The LPC29xx devices come with up to 32KB of ITCM and DTCM

- Using tools like Keil uVision3 simplifies this

- ISR Routines in TCM

- Frequently called code

- Whole application!

## **CPU load of BLDCM (and PMSM)**

- The CPU load was measured for a motor running at 6000 rpm

- For all control algorithms the CPU load was reasonably low.

- BLDCM control the CPU load was only about 1%.

- PMSM motor control requires significantly more CPU time (16%).

## **CPU Load Measurements**

|                                             | Blo                          | Sine                                       |                                                 |                                        |         |

|---------------------------------------------|------------------------------|--------------------------------------------|-------------------------------------------------|----------------------------------------|---------|

| Position<br>Measurement<br>Method           | ADC<br>measure<br>of<br>BEMF | ADC<br>measure of<br>Hall sensor<br>output | PWM<br>capturing<br>of Hall<br>sensor<br>output | PWM capturing of Hall<br>sensor output |         |

| CPU Load                                    | 1.4                          | 1.4                                        | 1                                               | 12.2                                   | 8.7     |

| Time required for interrupt service +2 [us] | 23                           | 22                                         | 14.5                                            | 3.2+9.5                                | 2.3+6.8 |

| Location of application code                | Flash                        | Flash                                      | Flash                                           | Flash                                  | ITCM    |

## LPC29xx DC and AC Motor control Demo

- AC and DC motors Examples

- PID Controller implementation

- Application note detailing implementation

- Full board schematics

- Complete software (Keil, HiToP + more)

- Source code for PC GUI

# Demonstration of EC Motor Control using the LPC2900

# **Additional Product Details**

## **LPC2900**

#### 32-bit ARM968E-S processor

- State-of-the-Art ARM968E-S industry standard RISC core @ 125 MHz

- High performance (1.1MIPS/MHz) with low power consumption

- Peripherals connected via multilayer

Advanced High-performance Bus (AHB-lite)

- NXP Vectored Interrupt Controller (VIC) with 63 sources and 16 priority levels

- 16-bit THUMB instruction set for increased code density

#### **Memories / interfaces**

- Static RAM

- Up to 32KB Tightly Coupled Memory (TCM) for Data and Instruction

- 56 KB Total SRAM

- 32 KB general purpose SRAM

- Independent additional 16 KB SRAM

- 8KB of ETB SRAM can be used by CPU

- Memory shadowing from Flash to SRAM supported

- Enabling faster interrupt execution from SRAM

- External Bus Interface for 4 memory banks

- 24-bit Address and 32-bit data path

- Up to 4 banks with 16MB can be addressed

- Data bus configurable as 8-, 16- or 32-bit width

- Unused data bus pins become general purpose I/O

## **Tightly coupled memory**

- Fast memory, local to processor :

- High speed performance without system bus (AMBA) access

- Smaller die size penalty compared to equivalent amount of cache

- Fixed location in memory map

- Code and data TCM:

- to be initialised before execution

- require extra code execution for initialization

- Predictable real-time performance (a cache may miss.)

- Could be seen as an alternative approach to caches

- Can easily be controlled by a small footprint embedded OS

- Cache requires a MUCH larger OS to manage it efficiently

## Fast flash memory

- 768 KB embedded Flash Memory

- 8 small sectors with 8 KB and 11 sectors with 64 KB

- Flash security

- Robust 2-transistor Flash concept

- Self timed programming/erasing preventing over/under-burn/erase

- On-chip program/erase generation

- Writing in page-mode supported

- Flash 128-bit wide interface accelerator enables high speed operation

- Programming features

- Very fast programming at >2Mb/s, with source code protection features

- Initial JTAG Programming and In-Application Programming supported

#### **CAN** interfaces

#### 2 CAN Controllers

- Featuring receive FullCAN mode and Triple Transmit Buffers

- Data rates up to 1 Mb/s, CAN 2.0B & ISO 11898 compatible

- Error and System Diagnostics Support, Self Reception Mode & Listen Only Mode

- Advanced Hardware Acceptance Filter to reduce CPU load

- Certified CAN conformance

#### **UART** interfaces

- 2 industry standard 16C550 UARTs

- 16 bytes FIFO message buffer for transmit and receive

- Receiver FIFO trigger points at

1byte, 4bytes, 8bytes and 14bytes

- Register locations conform to 550 industry standard

- Built-in baud-rate generator

- ▶ RS-485 Support

- LIN Support

#### SPI & I<sup>2</sup>C interfaces

- 3 Full-duplex Queued-Quad SPI (Q-SPI)

- Master or slave operation

- Supports up to 4 slaves in <u>Sequential Multi Slave operation</u>

- Programmable clock bit rate and pre-scale, based on SPI source clock from the CGU

- Max. clock rate in master mode 40MHz, in slave mode 20MHz

- Separate transmit and receive FIFO buffers, 16-bit wide, 32 locations deep

- Programmable choice of interface operation: Motorola (SPI) or Texas Instruments (SSI)

- Programmable data frame size from 4 to 16 bits

- Internal loop back test mode

- 2 I<sup>2</sup>C buses

- 400 KHz transfer rates

- Supports monitor mode

- Supports multiple address recognition from one port.

#### **Fast A/D Converter**

- Two 3.3V A/D Converters

- 8 channels each

- Configurable resolution: 10-bit ..2-bit

- High accuracy: ±1LSB (±5mV, full scale ±20mV)

- 400k samples/s at 10bit resolution,

- 1.500k samples/s at 2bit resolution

- Conversion time ≤ 2.5 µs per channel

- Automatic scan mode

- Single or continuous, with interrupt at end of scan

- Internal & external trigger start options

- Zero-crossing detection

- Programmable reference level with an interrupt to CPU

- 5V A/D Converter

- 8 channels

## **PWM Module**

- 4 PWM modules

- Each module with 6 channels

- Configurable resolution: 16-bit ..2-bit (plus a 16-bit pre-scaler)

- Frequency range up to 58kHz (at 10bit)

- Double edge PWM generation

- 3 capture/compare inputs

- Support brushless DC motor

- Burst mode (e.g. 50kHz modulation) to reduce switching current

- Trap input signal

#### **Timers**

- Watchdog Timer, with timer change protection

- Internal chip reset when not triggered periodically

- Debug mode with interrupt instead of reset

- By default enabled with fixed time-out for watchdog configuring

- Watchdog time period change protected with access sequence

- ▶ 4 x 32-bit Counter/Timers with programmable 32-bit prescalers

- Up to four 32-bit Match Registers per counter/timer

- Up to four 32-bit Capture Channels per counter/timer

- External Capture and Match I/O supported

#### **Miscellaneous**

- Dual power supply

- CPU operating at 1.8V ± 5%

- I/O operating at 2.7V to 3.6V, 5V tolerant

- LQFP100/144/208 packages

- Multiplexed outputs, unused pins become general purpose I/O pins

- Boundary scan test supported via JTAG interface

- Operating temperature range -40 to +85 degree C

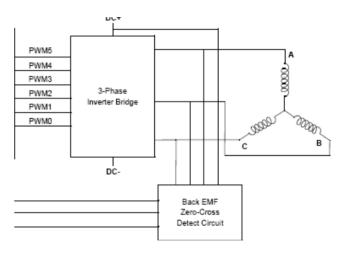

## **Basic EC-Motor Control System**

- LPC2900 MSCSS is used to control the motor power stage.

- Six Pulse Width Modulation (PWM) signals are fed to the power stage to control the six MOSFETs of the 3-phase inverter circuit.

3-phase Inverters consist of two half bridges for each motor phase. These half bridges consist of two power MOSFETs or IGBTs

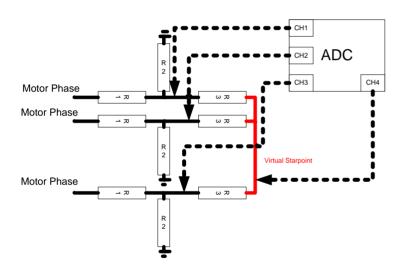

## **Sensorless Control**

## **Back EMF**

- The zero crossing point of the BEMF doesn't directly indicate the commutation point because it is in the middle of one conduction phase

- Therefore the half of the commutation time has to be advanced until the phase supply voltages can be changed.

#### **RPM Measurement**

- The RPM can be calculated by determining the period between two rising or falling edges of one Hall sensor through the captured value in the sensor related capture register.

- With the number of ticks between those events, the PWM base clock, and the PWM prescale value the speed can be calculated easily by using the following formula:

- RPM = ((PWM CLOCK/(PWM Prescaler+1))\*60.0)/(CaptureValue));

- For a higher precision the period between n rising edges is used to calculate the speed in this application, whereas n stands for the number of poles