Document Number: MC33810

Rev. 10.0, 4/2011

# **VRoHS**

# **Automotive Engine Control IC**

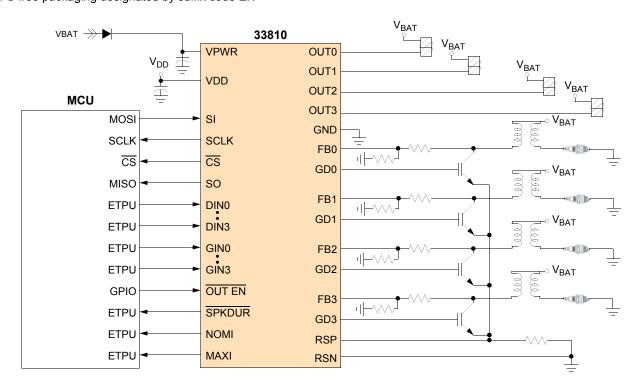

The 33810 is an eight channel output driver IC intended for automotive engine control applications. The IC consists of four integrated low side drivers and four low side gate pre-drivers. The low side drivers are suitable for driving fuel injectors, solenoids, lamps, and relays. The four gate pre-drivers can function either as ignition IGBT gate pre-drivers or as general purpose MOSFET gate pre-drivers.

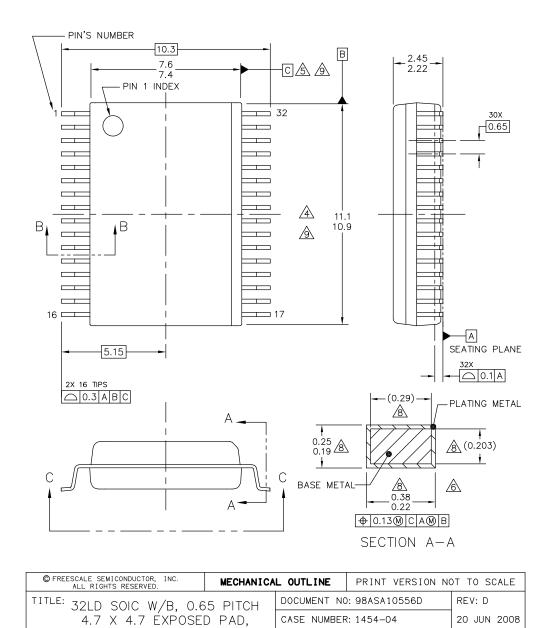

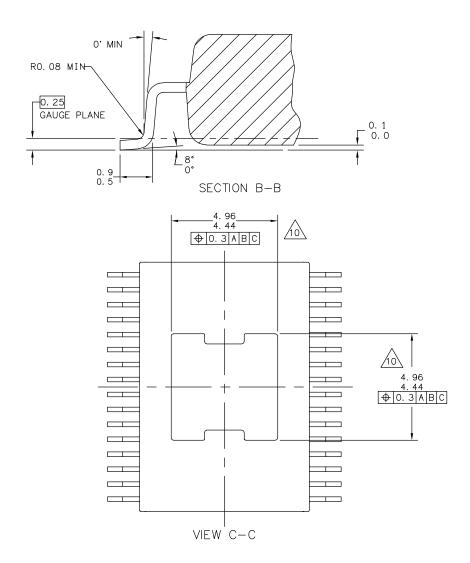

When configured as ignition IGBT gate pre-drivers, additional features are enabled such as spark duration, dwell time, and ignition coil current sense. When configured as a general purpose gate pre-driver, the 33810 provides external MOSFETs with short circuit protection, inductive flyback protection and diagnostics. The device is packaged in a 32 pin (0.65mm pitch) exposed pad SOIC.

#### **Features**

- Designed to operate over the range of 4.5V ≤ VPWR ≤ 36V

- Quad ignition IGBT or MOSFET gate pre-driver with Parallel/SPI and/or PWM control

- · Quad injector driver with Parallel/SPI control

- Interfaces directly to MCU using 3.3V/5.0V SPI protocol

- Injector driver current limit 4.5A max.

- · Independent fault protection and diagnostics

- VPWR standby current 10μA max.

- · Pb-free packaging designated by suffix code EK

# 33810

# **ENGINE CONTROL**

| ORDERING INFORMATION                       |                |             |  |  |  |

|--------------------------------------------|----------------|-------------|--|--|--|

| Device Temperature Range (T <sub>A</sub> ) |                | Package     |  |  |  |

| MCZ33810EK/R2                              | -40°C to 125°C | 32 SOICW-EP |  |  |  |

Figure 1. MC33810 Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2006 - 2011. All rights reserved.

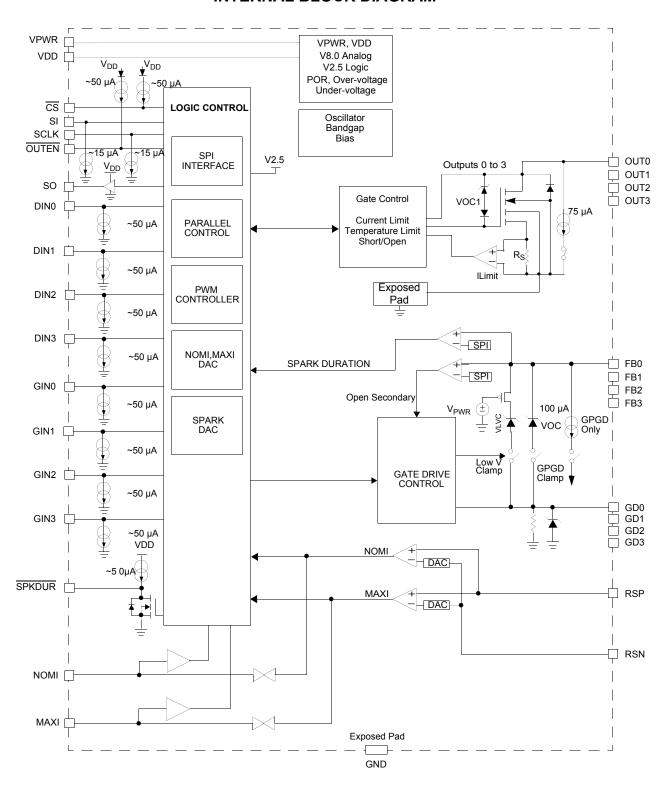

# INTERNAL BLOCK DIAGRAM

Figure 2. 33810 Simplified Internal Block Diagram

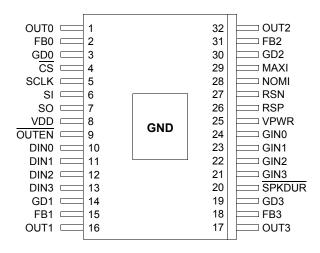

# **PIN CONNECTIONS**

Figure 3. 33810 Pin Connections

Table 1. 33810 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 15.

| Pin Number                            | Pin Name                | Pin Function | Formal Name                                                                              | Definition                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------|-------------------------|--------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                                     | VDD                     | Input        | Digital Logic Supply<br>Voltage                                                          | The VDD input supply voltage determines the interface voltage levels between the device and the MCU, and is used to supply power to the Serial Out buffer (SO), $\overline{\text{SPKDUR}}$ buffer, MAXI, NOMI, and pull-up current source for the Chip Select $(\overline{\text{CS}})$ .                                                                                              |

| 6                                     | SI                      | Input        | Serial Input Data                                                                        | The SI input pin is used to receive serial data from the MCU.                                                                                                                                                                                                                                                                                                                         |

| 5                                     | SCLK                    | Input        | Serial Clock Input                                                                       | The SCLK input pin is used to clock in and out the serial data on the SI and SO pins, while being addressed by the $\overline{\text{CS}}$ .                                                                                                                                                                                                                                           |

| 4                                     | CS                      | Input        | Chip Select                                                                              | The Chip Select input pin is an active low signal sent by the MCU to indicate that the device is being addressed. This input requires CMOS logic levels and has an internal active pull-up current source.                                                                                                                                                                            |

| 7                                     | SO                      | Output       | Serial Output Data                                                                       | The SO output pin is used to transmit serial data from the device to the MCU.                                                                                                                                                                                                                                                                                                         |

| 10, 11, 12, 13                        | DIN0,DIN1,<br>DIN2,DIN3 | Input        | Driver Input 0, Driver<br>Input 1, Driver Input 2,<br>Driver Input 3                     | Active HIGH input control for injector outputs OUT0 - 3. The parallel input data is logically OR'd with the corresponding SPI input data register contents.                                                                                                                                                                                                                           |

| 24, 23, 22, 21                        | GIN0,GIN1,<br>GIN2,GIN3 | Input        | Gate Driver Input 0<br>Gate Driver Input 1<br>Gate Driver Input 2<br>Gate Driver Input 3 | These pins are the active HIGH input control for IGBT/General Purpose Gate Driver outputs 0 - 3. The parallel input data is logically OR'd with the corresponding SPI input data register contents in General Purpose Mode Only.                                                                                                                                                      |

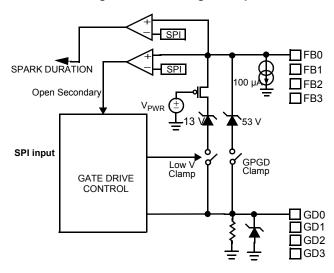

| 20                                    | SPKDUR                  | Output       | Spark Duration Output                                                                    | This pin is the Spark Duration Output. This open drain output is low while feedback inputs FB0 through FB3 are above the programmed spark detection threshold.                                                                                                                                                                                                                        |

| 25                                    | VPWR                    | Input        | Analog Supply Voltage                                                                    | VPWR is the main voltage input for all internal analog bias circuitry.                                                                                                                                                                                                                                                                                                                |

| Exposed Pad<br>(bottom of<br>package) | GND                     | Ground       | Ground                                                                                   | The exposed pad is the only ground reference for analog, digital and power ground connections. As such, it must be soldered directly to a low impedance ground plane for both electrical and thermal considerations. For more information about this package, please see application note AN2409 on the Freescale Web site, <a href="https://www.freescale.com">www.freescale.com</a> |

# Table 1. 33810 Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 15.

| Pin Number    | Pin Name   | Pin Function | Formal Name                        | Definition                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------|--------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9             | OUTEN      | Input        | Output Enable                      | The Output Enable pin (OUTEN) is an active low input. When the OUTEN pin is low, the device outputs are active. The outputs are disabled when OUTEN is high.                                                                                                                                                                                                                                              |

| 29            | MAXI       | Output       | Maximum Ignition Coil<br>Current   | This pin is the Maximum Ignition Coil Current output flag. This output is asserted when the IGBT Collector-Emitter current exceeds the selected level of the DAC. This signal also latches off the gate pre-drive outputs when configured as a General Purpose Gate pre-Driver. The MAXI current level is determined by the voltage drop across an external sense resistor connected to pins RSP and RSN. |

| 28            | NOMI       | Output       | Nominal Ignition Coil<br>Current   | This pin is the Nominal Ignition Coil Current output flag. This output is asserted when the IGBT Collector-Emitter current exceeds the level selected by the DAC.                                                                                                                                                                                                                                         |

| 2, 15, 31, 18 | FB0 - FB3  | Input        | Feedback Voltage<br>Sense          | In IGBT ignition gate pre-driver mode, these feedback inputs monitor the IGBT's collector voltage to provide the spark duration timer control signal.                                                                                                                                                                                                                                                     |

| 3, 14, 30,19  | GD0 -GD3   | Output       | Gate Drive Output                  | IGBT/General Purpose Gate pre-driver outputs are controlled by GIN0 - GIN3. Pull-up and pull-down current sources are used to provide a controlled slew rate to an external IGBT or MOSFET connected as a low side driver.                                                                                                                                                                                |

| 26            | RSP        | Input        | Resistor Sense<br>Positive         | This pin is the Positive input of a current sense amplifier.                                                                                                                                                                                                                                                                                                                                              |

| 27            | RSN        | Input        | Resistor Sense<br>Negative         | This pin is the Negative input of a current sense amplifier.                                                                                                                                                                                                                                                                                                                                              |

| 1, 16, 32, 17 | OUT0 -OUT3 | Output       | Low Side Injector<br>Driver Output | These pin are the Open drain low side injector driver outputs.                                                                                                                                                                                                                                                                                                                                            |

# **ELECTRICAL CHARACTERISTICS**

# **MAXIMUM RATINGS**

**Table 2. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted.

| Ratings                                                                                    | Symbol                                 | Value        | Unit            |

|--------------------------------------------------------------------------------------------|----------------------------------------|--------------|-----------------|

| LECTRICAL RATINGS                                                                          | I L                                    |              |                 |

| VPWR Supply Voltage <sup>(1)</sup>                                                         | V <sub>PWR</sub>                       | -1.5 to 45   | V <sub>DC</sub> |

| VDD Supply Voltage <sup>(1)</sup>                                                          | V <sub>DD</sub>                        | -0.3 to 7.0  | V <sub>DC</sub> |

| SPI Interface and Logic Input Voltage (CS, SI, SO, SCLK, OUTEN,                            | V <sub>IL</sub>                        | -0.3 to VDD  | V <sub>DC</sub> |

| DIN0 - DIN3, GIN0 - GIN3, SPKDUR, NOMI, MAXI, RSP,RSN)                                     | V <sub>IH</sub>                        |              |                 |

| IGBT/General Purpose Gate Pre-driver Drain Voltage (V <sub>FB0</sub> to V <sub>FB3</sub> ) | V <sub>FB</sub>                        | -1.5 to 60   | $V_{DC}$        |

| Injector Output Voltage (OUTx)                                                             | V <sub>OUTX</sub>                      | -1.5 to 60   | V <sub>DC</sub> |

| General Purpose Gate Pre-driver Output Voltage (GDx)                                       | V <sub>GDx</sub>                       | -0.3 to 10   | V <sub>DC</sub> |

| Output Clamp Energy (OUT0 to OUT3)(Single Pulse)                                           | E <sub>CLAMP</sub>                     | 100          | mJ              |

| T <sub>JUNCTION</sub> = 150°C, I <sub>OUT</sub> = 1.5 A                                    |                                        |              |                 |

| Output Clamp Energy (OUT0 to OUT3)(Continuous Pulse)                                       | E <sub>CLAMP</sub>                     | 100          | mJ              |

| T <sub>JUNCTION</sub> = 125°C, I <sub>OUT</sub> = 1.0 A (Max Injector frequency is 70 Hz)  | 02/11/11                               |              |                 |

| Output Continuous Current (OUT0 to OUT3)                                                   | lossss                                 | 2.0          | А               |

| T <sub>JUNCTION</sub> = 150°C                                                              | 00000                                  |              |                 |

| Maximum Voltage for RSN and RSP inputs                                                     | V <sub>RSX</sub>                       | -0.3 - VDD   | V <sub>DC</sub> |

| Frequency of SPI Operation (VDD = 5.0 V)                                                   | -                                      | 6.0          | MHz             |

| ESD Voltage <sup>(2), (3)</sup>                                                            |                                        |              | V               |

| Human Body Model (HBM)                                                                     | V <sub>ESD1</sub>                      | ±2000        |                 |

| Machine Model (MM)                                                                         | V <sub>ESD2</sub><br>V <sub>ESD3</sub> | ±200<br>±750 |                 |

| Charge Device Model (CDM)                                                                  | VESD3                                  | 1750         |                 |

| HERMAL RATINGS                                                                             | ·                                      |              |                 |

| Operating Temperature                                                                      |                                        |              | °C              |

| Ambient                                                                                    | T <sub>A</sub>                         | -40 to 125   |                 |

| Junction2                                                                                  | T <sub>J</sub>                         | -40 to 150   |                 |

| Case                                                                                       | T <sub>C</sub>                         | -40 to 125   |                 |

| Storage Temperature                                                                        | T <sub>STG</sub>                       | -55 to 150   | °C              |

| Power Dissipation (T <sub>A</sub> = 25°C)                                                  | P <sub>D</sub>                         | 1.7          | W               |

| Peak Package flow Temperature During Solder Mounting                                       | T <sub>SOLDER</sub>                    |              | °C              |

| DWB Suffix                                                                                 |                                        | 240          |                 |

| EW Suffix                                                                                  |                                        | 245          |                 |

| Thermal Resistance                                                                         |                                        |              | °C/W            |

| Junction-to-Ambient                                                                        | $R_{	hetaJA}$                          | 75           |                 |

| Junction- to-Lead<br>Junction-to-Flag                                                      | $R_{\theta JL}$                        | 8.0          |                 |

| Juliolion-to-riag                                                                          | $R_{	heta JC}$                         | 1.2          |                 |

# ELECTRICAL CHARACTERISTICS STATIC ELECTRICAL CHARACTERISTICS

#### Table 2. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted.

| Ratings | Symbol | Value | Unit | l |

|---------|--------|-------|------|---|

|---------|--------|-------|------|---|

#### Notes

- 1. Exceeding these limits may cause malfunction or permanent damage to the device.

- 2. ESD data available upon request.

- 3. ESD testing is performed in accordance with the Human Body Model (HBM) (AEC-Q100-002), the Machine Model (MM) (AEC-Q100-003), and the Charge Device Model (CDM), Robotic (AEC-Q100-011).

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where typical values reflect the parameter's approx. average value with VPWR = 13 V, TA = 25°C.

| Characteristic                                                                                                                                                                                                                                                | Symbol                   | Min         | Тур           | Max           | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|---------------|---------------|------|

| POWER INPUT (VDD, VPWR)                                                                                                                                                                                                                                       | - + +                    |             | 1             | !             |      |

| Supply Voltage <sup>(4)</sup>                                                                                                                                                                                                                                 |                          |             |               |               |      |

| Fully Operational Full Parameter Specification                                                                                                                                                                                                                | V <sub>PWR(FO)</sub>     | 4.5<br>6.0  | -             | 36<br>32      | V    |

| Supply Current All Outputs Disabled (Normal Mode)                                                                                                                                                                                                             | I <sub>VPWR(ON)</sub>    | _           | 10.0          | 14.0          | mA   |

| Sleep State Supply Current (Must have $V_{DD} \le 0.8 \text{ V}$ for sleep state), $V_{PWR} = 32 \text{ V}$                                                                                                                                                   | I <sub>VPWR(SS)</sub>    | _           | 15            | 30            | μА   |

| V <sub>PWR</sub> Over-voltage Shutdown Threshold Voltage <sup>(5)</sup>                                                                                                                                                                                       | V <sub>PWR(OV)</sub>     | 36.5        | 39            | 42            | V    |

| V <sub>PWR</sub> Over-voltage Shutdown Hysteresis Voltage                                                                                                                                                                                                     | V <sub>PWR(OV-HYS)</sub> | 0.5         | 1.5           | 3.0           | V    |

| V <sub>PWR</sub> Under-voltage Shutdown Threshold Voltage <sup>(6)</sup>                                                                                                                                                                                      | V <sub>PWR(UV)</sub>     | 3.0         | 4.0           | 4.4           | V    |

| V <sub>PWR</sub> Under-voltage Shutdown Hysteresis Voltage                                                                                                                                                                                                    | V <sub>PWR(UV-HYS)</sub> | 100         | 200           | 300           | mV   |

| V <sub>PWR</sub> Low Operating Voltage (Low-voltage reported via the SPI) <sup>(7)</sup>                                                                                                                                                                      | V <sub>PWR(LOV)</sub>    | 5.3         | _             | 8.99          | V    |

| VDD Supply Voltage                                                                                                                                                                                                                                            | V <sub>DD</sub>          | 3.0         | _             | 5.5           | V    |

| VDD Supply Current                                                                                                                                                                                                                                            | I <sub>VDD</sub>         |             |               |               | mA   |

| Static Condition and does not include VDD current out of device                                                                                                                                                                                               |                          | -           | _             | 1.0           |      |

| VDD Supply Under-voltage (Sleep State) Threshold Voltage <sup>(8)</sup>                                                                                                                                                                                       | V <sub>DD(UV)</sub>      | 8.0         | 2.5           | 2.8           | V    |

| INJECTOR DRIVER OUTPUTS (OUT 0:3)                                                                                                                                                                                                                             |                          |             |               |               |      |

| Drain-to-Source ON Resistance $I_{OUT} = 1.0 \text{ A, } T_J = 125^{\circ}\text{C, VPWR} = 13 \text{ V}$ $I_{OUT} = 1.0 \text{ A, } T_J = 25^{\circ}\text{C, VPWR} = 13 \text{ V}$ $I_{OUT} = 1.0 \text{ A, } T_J = -40^{\circ}\text{C, VPWR} = 13 \text{ V}$ | R <sub>DS (ON)</sub>     | -<br>-<br>- | -<br>0.2<br>- | 0.3<br>-<br>- | Ω    |

| Output Self Limiting Current                                                                                                                                                                                                                                  | I <sub>OUT(LIM)</sub>    | 3.0         | _             | 6.0           | Α    |

| Output Fault Detection Voltage Threshold <sup>(9)</sup> Outputs Programmed OFF (Open Load) Outputs Programmed ON (Short to Battery)                                                                                                                           | V <sub>OUT(FLT-TH)</sub> | 2.0         | 2.5           | 3.0           | V    |

| Output OFF Open Load Detection Current  V <sub>DRAIN</sub> = 18 V, Outputs Programmed OFF  V <sub>DRAIN</sub> = 32 V, Outputs Programmed OFF (-40°C)                                                                                                          | I <sub>(OFF)OCO</sub>    | 40          | 75            | 115<br>115    | μА   |

| Output ON Open Load Detection Current Current less then specification value considered open                                                                                                                                                                   | I <sub>(ON)OCO</sub>     | 20          | 100           | 200           | mA   |

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where typical values reflect the parameter's approx. average value with VPWR = 13 V, TA = 25°C.

| Characteristic | Symbol | Min | Тур | Max | Unit |  |

|----------------|--------|-----|-----|-----|------|--|

|----------------|--------|-----|-----|-----|------|--|

#### Notes

- 4. These parameters are guaranteed by design, but not production tested. Fully operational means driver outputs will toggle as expected with input toggling. SPI is guaranteed to be operational when VPWR > 4.5 V. SPI may not report correctly when VPWR < 4.5 V.

- 5. Over-voltage thresholds minimum and maximum include hysteresis.

- 6. Under-voltage thresholds minimum and maximum include hysteresis.

- 7. Device is functional provided T<sub>.I</sub> is less than 150°C. Some table parameters may be out of specification.

- 8. Device in Sleep State, returns from sleep state with power on reset.

- 9. Output fault detection thresholds with outputs programmed OFF. Output fault detect thresholds are the same for output open and shorts.

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where typical values reflect the parameter's approx. average value with VPWR = 13 V, TA = 25°C.

| Characteristic                                                                                                  | Symbol                    | Min        | Тур          | Max         | Unit |

|-----------------------------------------------------------------------------------------------------------------|---------------------------|------------|--------------|-------------|------|

| INJECTOR DRIVER OUTPUTS (OUT 0:3) (Continued)                                                                   |                           |            |              | <u> </u>    |      |

| Output Clamp Voltage 1                                                                                          | V <sub>OC1</sub>          |            |              |             | V    |

| I <sub>D</sub> = 20 mA                                                                                          |                           | 48         | 53           | 58          |      |

| Output Leakage Current                                                                                          | I <sub>OUT(LKG)</sub>     |            |              |             | μА   |

| VDD = 5.0 V, V <sub>DRAIN</sub> = 24 V, Open Load Detection Current Disabled                                    |                           | -          | _            | 20          |      |

| VDD = 5.0 V, V <sub>DRAIN</sub> = V <sub>OC</sub> - 1.0 V, Open Load Detection Current Disabled                 |                           | _          | _            | 3000        |      |

| VDD = 0 V, V <sub>DRAIN</sub> = 24 V, Sleep State                                                               |                           | _          | _            | 10          |      |

| Over-temperature Shutdown <sup>(10)</sup>                                                                       | T <sub>LIM</sub>          | 155        | _            | 185         | °C   |

| Over-temperature Shutdown Hysteresis <sup>(10)</sup>                                                            | T <sub>LIM(HYS)</sub>     | 5.0        | 10           | 15          | °C   |

| GNITION (IGBT) GATE DRIVER PARAMETERS (GD 0:3 FB0:3)                                                            |                           |            |              |             |      |

| Gate Driver Output Voltage                                                                                      |                           |            |              |             |      |

| $I_{GD} = 500 \mu A$                                                                                            | V <sub>GS(ON)</sub>       | 4.8        | 7.0          | 9.0         | V    |

| $I_{GD} = -500 \mu A$                                                                                           | V <sub>GS(OFF)</sub>      | 0          | 0.375        | 0.5         |      |

| Sleep Mode Gate to Source Resistor                                                                              | R <sub>GS(PULLDOWN</sub>  | 100        | 200          | 300         | ΚΩ   |

|                                                                                                                 | )                         |            |              |             |      |

| Sleep Mode FBx pin Leakage Current                                                                              | I <sub>FBX(LKG)</sub>     |            |              |             | μΑ   |

| $VDD = 0 V, V_{FBx} = 24 V,$                                                                                    |                           | -          | _            | 1.0         |      |

| Feedback Sense Current (FBx Input Current)                                                                      | I <sub>FBX(FLT-SNS)</sub> |            |              |             | μΑ   |

| FBx = 32 V, Outputs Programmed OFF                                                                              | , ,                       |            |              | 1.0         |      |

| Gate Drive Source Current (1 $\leq$ V <sub>GD</sub> $\leq$ 3)                                                   | I <sub>GATEDRIVE</sub>    | 650        | 780          | 950         | μΑ   |

| Gate Drive Turn Off Resistance                                                                                  | R <sub>DS(ON)</sub>       |            |              |             | Ω    |

|                                                                                                                 |                           | 500        | _            | 1000        |      |

| SOFT SHUTDOWN FUNCTION (VOLTAGES REFERENCED TO IGBT COLI                                                        | ECTOR)                    |            | •            | •           |      |

| Low Voltage Flyback Clamp                                                                                       |                           |            |              |             |      |

| Driver Command Off, Soft Shutdown Enabled, GDx = 2.0 V                                                          | $V_{LVC}$                 | VPWR       | VPWR         | VPWR + 13   | V    |

|                                                                                                                 |                           | +9.0       | +11          |             |      |

| Spark Duration Comparator Threshold (referenced to IC Ground Tab)                                               | V <sub>TH-RISE</sub>      |            |              |             | V    |

| Rising Edge Relative to VPWR                                                                                    |                           | 18         | 21           | 24          |      |

| Spark Duration Comparator Threshold (referenced to IC Ground Tab) <sup>(11)</sup>                               | V <sub>TH-FALL</sub>      | 1.2        | 2.75         | 3.6         | V    |

| Falling Edge Relative to VPWR, Default = 5.5 V Assuming ideal external                                          |                           | 4.9        | 5.5          | 6.1         |      |

| 10:1 voltage divider. Voltage measured at high end of divider, not at pin.<br>Tolerance of divider not included |                           | 7.4<br>9.9 | 8.2<br>11.00 | 9.1<br>12.1 |      |

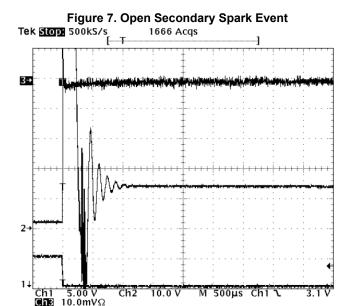

| Open Secondary Comparator Threshold (referenced from primary to                                                 | V                         |            |              |             | V    |

| Rising Edge Relative to GND. No hysteresis with 10:1 voltage divider.                                           | V <sub>TH-RISE</sub>      | 11.5       | _            | 15.5        | V    |

| CURRENT SENSE COMPARATOR (RSP, RSN)                                                                             |                           |            | 1            | . 3.0       |      |

| NOMI Trip Threshold Accuracy - Steady State Condition                                                           | NOMI                      |            |              |             | %    |

| 3.0 A across $0.02 \Omega$ (RSP - RSN = 60 mV)                                                                  | NOMI <sub>TRIPTA</sub>    | -10        | _            | 10          | 70   |

| 10.75 A across 0.04 Ω (RSP - RSN = 430 mV)                                                                      |                           | -10        | _            | 10          |      |

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where typical values reflect the parameter's approx. average value with VPWR = 13 V, TA = 25°C.

| Characteristic Symbol Min Typ Max Unit |

|----------------------------------------|

|----------------------------------------|

#### Notes

- 10. This parameter is guaranteed by design, however is not production tested.

- 11. Assuming Ideal external 10:1 Voltage Divider. Tolerance of 10:1 Voltage Divider is not included. Voltage is measured on the High End of Divider not at the pin. 10:1 N.3.A 10:1 Voltage Divider is produced using two resistors with a 9:1 resistance ratio by the basic formula:

$$\frac{\text{VOUT}}{\text{VIN}} = \frac{\text{R1}}{\text{R1} + \text{R2}}$$

Where R2 = 9XR1

## **CURRENT SENSE COMPARATOR (RSP, RSN) (CONTINUED)**

| MAXI Trip Threshold Accuracy                                                                      |                        |      |   | 7.5 | %       |

|---------------------------------------------------------------------------------------------------|------------------------|------|---|-----|---------|

| Steady State Condition                                                                            | MAXI <sub>TRIPTA</sub> |      | _ |     |         |

| 6.0 A across $0.02 \Omega$ (RSP - RSN = 120 mV)<br>21 A across $0.04 \Omega$ (RSP - RSN = 840 mV) |                        | -7.5 |   |     |         |

| MAXI Trip Point During Overlapping Dwell                                                          | MAXI <sub>TRIPOD</sub> | -35  | _ | +35 | %       |

| Input Bias Current                                                                                | I <sub>BIASRSX</sub>   |      | - | 50  | μA      |

| RSP and RSN                                                                                       |                        | -50  |   |     |         |

| Comparator Hysteresis Voltage                                                                     |                        |      |   |     |         |

| NOMI                                                                                              | NOMI <sub>HYS</sub>    | 40   | _ | 70  | % of VT |

| MAXI                                                                                              | MAXII <sub>HYS</sub>   | 40   | _ | 70  |         |

| Input Voltage Range (Maximum voltage between RSN and RSP) <sup>(12)</sup>                         | VCMVR <sub>CMVR</sub>  | 0.0  | _ | 2.0 | V       |

| Ground Offset Voltage Range <sup>(12)</sup>                                                       | VGND <sub>OVR</sub>    | -0.3 | - | 0.3 | V       |

| Maximum offset between RSN pin and IC Ground (Exposed Pad)                                        |                        |      |   |     |         |

# GENERAL PURPOSE GATE DRIVER PARAMETERS (GD 0:3)

| Gate Drive Sink and Source Current                                                                                        | I <sub>GD</sub>           | 1.0  | 2.0 | 5    | mA |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-----|------|----|

| Gate Drive Output Voltage                                                                                                 |                           |      |     |      |    |

| I <sub>GD</sub> = 1.0 mA                                                                                                  | V <sub>GS(ON)</sub>       | 4.8  | 7.0 | 9.0  | V  |

| I <sub>GD</sub> = -1.0 mA                                                                                                 | V <sub>GS(OFF)</sub>      | 0.0  | 0.2 | 0.5  | V  |

| Short to Battery Fault Detection Voltage Threshold                                                                        | V <sub>DS(FLT-TH)</sub>   |      |     |      | V  |

| V <sub>DD</sub> = 5.0 V, Outputs Programmed ON<br>Programmable from 0.5 to 3.0 V in 0.5 V increments. ( <u>Table 14</u> ) |                           | -35% |     | +35% |    |

| Open Fault Detection Voltage Threshold (referenced to IC ground tab)                                                      | V <sub>DS(FLT-TH)</sub>   |      |     |      | V  |

| V <sub>DD</sub> = 5.0 V, Outputs Programmed OFF                                                                           | , , ,                     | 2.0  | 2.5 | 3.0  |    |

| Output OFF Open Load Detection Current                                                                                    | I <sub>FBX(FLT-SNS)</sub> |      |     |      | μА |

| FBx = 18 V, Outputs Programmed OFF                                                                                        | ,                         | 50   | 75  | 120  |    |

| Output Clamp Voltage                                                                                                      | V <sub>oc</sub>           |      |     |      | V  |

| Driver Command Off, Clamp Enabled, V <sub>GATE</sub> = 2.0 V                                                              |                           | 48   | 53  | 58   |    |

#### **DIGITAL INTERFACE**

| Input Logic High-voltage Thresholds | V <sub>IH</sub>       | 0.7 x V <sub>DD</sub> | _ | V <sub>DD</sub> + 0.3 | V  |

|-------------------------------------|-----------------------|-----------------------|---|-----------------------|----|

| Input Logic Low-voltage Thresholds  | V <sub>IL</sub>       | GND - 0.3             | _ | 0.2 x V <sub>DD</sub> | V  |

| Input Logic-voltage Hysteresis      | V <sub>HYS</sub>      | 100                   | _ | 400                   | mV |

| Input Logic Capacitance             | C <sub>IN</sub>       | -                     | _ | 20                    | pF |

| Sleep Mode Input Logic Current      | I <sub>LOGIC_SS</sub> |                       |   |                       | μΑ |

| V <sub>DD</sub> = 0 V               |                       | -10                   | - | 10                    |    |

# ELECTRICAL CHARACTERISTICS STATIC ELECTRICAL CHARACTERISTICS

# **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where typical values reflect the parameter's approx. average value with VPWR = 13 V, TA = 25°C.

| Characteristic                                    | Symbol                | Min | Тур | Max | Unit |

|---------------------------------------------------|-----------------------|-----|-----|-----|------|

| Input Logic Pull-down Current                     |                       |     |     |     | μА   |

| 0.8 to 5.0 V (DIN $_{\rm X}$ and GIN $_{\rm X}$ ) | I <sub>LOGIC_PD</sub> | 30  | 50  | 100 |      |

#### Notes

<sup>12.</sup> This parameter is guaranteed by design, however it is not production tested.

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where typical values reflect the parameter's approx. average value with VPWR = 13 V, TA = 25°C.

| Characteristic                                                                                           | Symbol                    | Min                   | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|-----|------|------|

| DIGITAL INTERFACE (CONTINUED)                                                                            | •                         | •                     |     | •    | •    |

| Input Logic Pull-down Current 0.8 to 5.0 V (SI)                                                          | I <sub>SI_PD</sub>        | 5.0                   | 15  | 25   | μА   |

| Input Logic Pull-up Current on OUT_EN OUT_EN = 0.0 V, V <sub>DD</sub> = 5.0 V                            | I <mark>OUT_EN</mark> _PU | -30                   | -50 | -100 | μА   |

| OUT_EN Leakage Current to V <sub>DD</sub> OUT_EN = 5.0 V, V <sub>DD</sub> = 0 V                          | I <sub>OUT_EN</sub> (LKG) | _                     | ı   | 50   | μА   |

| SCLK Pull-down Current  V <sub>SCLK</sub> = V <sub>DD</sub>                                              | I <sub>SCLK</sub>         | 5                     | 15  | 25   | μА   |

| Tri-state SO Output<br>0 to 5.0 V                                                                        | I <sub>TRISO</sub>        | -10                   | ı   | 10   | μА   |

| CS Input Current CS = V <sub>DD</sub>                                                                    | I <del>cs</del>           | -50                   | _   | 50   | μА   |

| CS Pull-up Current CS = 0 V                                                                              | I <u>CS</u> _PU           | -30                   | -50 | -100 | μА   |

| CS Leakage Current to V <sub>DD</sub> CS = 5.0 V, V <sub>DD</sub> = 0 V                                  | I <u>CS</u> (LKG)         | _                     | -   | 50   | μА   |

| SO Input Capacitance in Tri-state Mode                                                                   | C <sub>SO</sub>           | _                     | 20  | _    | pF   |

| SO High State Output Voltage  I <sub>SO-HIGH</sub> = -1.0 mA                                             | V <sub>SO_HIGH</sub>      | V <sub>DD</sub> - 0.4 | -   | _    | V    |

| SO Low State Output Voltage  I <sub>SO-LOW</sub> = 1.0 mA                                                | V <sub>SO_LOW</sub>       | -                     | 1   | 0.4  | V    |

| NOMI, MAXI in V10 Mode Pull-down Current<br>NOMI, MAXI = 0.8 V, V <sub>DD</sub> = 5.0 V                  | I <sub>PD</sub>           | 30                    | 70  | 100  | μА   |

| SPKDUR Output Voltage   SPKDUR = 1.0 mA                                                                  | V <sub>SPKDUR_LO</sub>    | -                     | -   | 0.4  | V    |

| Output Pull-up Current for SPKDUR                                                                        | I <u>spkdur</u> pv        | 30                    | 50  | 100  | μА   |

| NOMI, MAXI High State Output Voltage  I <sub>NOMI-HIGH</sub> = -1.0 mA  I <sub>MAXI-HIGH</sub> = -1.0 mA | V <sub>I_HIGH</sub>       | V <sub>DD</sub> - 0.4 | -   | -    | V    |

| NOMI, MAXI Low State Output Voltage  I <sub>NOMI-LOW</sub> = 250 μA  I <sub>MAXI-LOW</sub> = 250 μA      | V <sub>I_LOW</sub>        | -                     | -   | 0.4  | V    |

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

# **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with VPWR = 13 V, TA = 25°C.

| Characteristic                                                          | Symbol                | Min | Тур | Max | Unit     |

|-------------------------------------------------------------------------|-----------------------|-----|-----|-----|----------|

| POWER INPUT                                                             |                       |     |     |     | <u> </u> |

| Required Low State Duration on VPWR for Under-voltage Detect            | t <sub>UV</sub>       |     |     |     | μS       |

| V <sub>PWR</sub> ≤ 0.2 V                                                | -                     | 1.0 | _   | _   |          |

| Required Low State Duration on VDD for Power On Reset                   | t <sub>RESET</sub>    |     |     |     | μS       |

| $V_{DD} \le 0.2 \text{ V}$                                              |                       | 1.0 | _   | -   |          |

| INJECTOR DRIVERS                                                        |                       |     | •   |     |          |

| Output ON Current Limit Fault Filter Timer (Short to Battery Fault)     | t <sub>SC</sub>       | 30  | 60  | 90  | μs       |

| Output ON Open Circuit Fault Filter Timer                               | t <sub>(ON)OC</sub>   | 3.0 | 7.5 | 12  | ms       |

| Output Retry Timer                                                      | t <sub>REF</sub>      | _   | 10  | 15  | ms       |

| Output OFF Open Circuit Fault Filter Timer                              | t <sub>(OFF)OC</sub>  | 100 |     | 400 | μs       |

| Output Slew Rate (No faster than 1.5 µs from off to on and on to off)   | t <sub>SR(RISE)</sub> |     |     |     | V/µs     |

| $R_{LOAD}$ = 14 $\Omega$ , $V_{LOAD}$ = 14 $V$                          | ,                     | 1.0 | 5.0 | 10  |          |

| Output Slew Rate                                                        | t <sub>SR(FALL)</sub> |     |     |     | V/μs     |

| $R_{LOAD}$ = 14 $\Omega$ , $V_{LOAD}$ = 14 $V$                          | ,                     | 1.0 | 5.0 | 10  |          |

| Propagation Delay (Input Rising Edge OR CS to Output Falling Edge)      | t <sub>PHL</sub>      |     | 1.0 | 5.0 | μs       |

| Input @ 50%V <sub>DD</sub> to Output voltage 90% of V <sub>LOAD</sub>   |                       |     |     |     |          |

| Propagation Delay (Input Falling Edge OR CS to Output Rising Edge)      | t <sub>PLH</sub>      |     | 1.0 | 5.0 | μs       |

| Input @ 50%V <sub>DD</sub> to Output voltage 10% of V <sub>LOAD</sub>   |                       |     |     |     |          |

| IGNITION & GENERAL PURPOSE GATE DRIVER PARAMETERS                       |                       |     |     |     |          |

| Propagation Delay (GINx Input Rising Edge OR CS to Output Rising Edge)  | t <sub>PLH</sub>      |     | 0.2 | 1.0 | μs       |

| Input @ 50%V <sub>DD</sub> to Output voltage 10% of V <sub>GS(ON)</sub> |                       |     |     |     |          |

| Propagation Delay (Input Falling Edge OR CS to Output Falling Edge)     | t <sub>PHL</sub>      |     | 0.2 | 1.0 | μs       |

| Input @ 50%V <sub>DD</sub> to Output voltage 90% of V <sub>GS(ON)</sub> |                       |     |     |     |          |

| IGNITION PARAMETERS                                                     |                       |     | •   |     |          |

| Open Secondary Fault Timer accuracy (uncalibrated)                      |                       | -35 | _   | 35  | %        |

| Maximum Dwell Timer Accuracy (uncalibrated)                             |                       | -35 | _   | 35  | %        |

| End of Spark Filter Accuracy (uncalibrated) <sup>(13)</sup>             |                       | -35 | _   | 35  | %        |

#### Notes

13. This parameter is guaranteed by design, however it is not production tested.

# **Table 4. Dynamic Electrical Characteristics (continued)**

Characteristics noted under conditions of 3.0 V  $\leq$  VDD  $\leq$  5.5 V, 6.0 V  $\leq$  VPWR  $\leq$  32 V, -40°C  $\leq$  TC  $\leq$  125°C, and calibrated timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with VPWR = 13 V, TA = 25°C.

| Characteristic                                                                                                                                                                                             | Symbol                  | Min  | Тур | Max | Unit |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----|-----|------|--|--|

| GENERAL PURPOSE GATE DRIVER PARAMETERS                                                                                                                                                                     |                         |      |     |     |      |  |  |

| Short to Battery Fault Detection Filter Timer Accuracy  VDD = High, Outputs Programmed ON  Programmable from 30 µs to 960 µs in replicating increments  Tolerance of timer after using calibration command | V <sub>DS(flt-th)</sub> | -10  |     | +10 | %    |  |  |

| Tolerance of timer before using calibration command                                                                                                                                                        |                         | -35  |     | +35 |      |  |  |

| Output OFF Open Circuit Fault Filter Timer  VDD = 5.0 V, Outputs Off                                                                                                                                       | t <sub>(OFF)</sub> OC   |      |     |     | μs   |  |  |

| Tolerance of timer before using calibration command                                                                                                                                                        |                         | 100  |     | 400 |      |  |  |

| PWM Frequency 10 Hz to 1.28 kHz Tolerance after using calibration command                                                                                                                                  | PWM <sub>FREQ</sub>     | -10% |     | 10% |      |  |  |

| PWM Frequency 10 Hz to 1.28 kHz Tolerance before using calibration command                                                                                                                                 | PWM <sub>FREQ</sub>     | -35% |     | 35% |      |  |  |

| Gate Driver Short Fault Duty Cycle                                                                                                                                                                         | GD <sub>SHRT_DC</sub>   |      | 1.0 | 3.0 | %    |  |  |

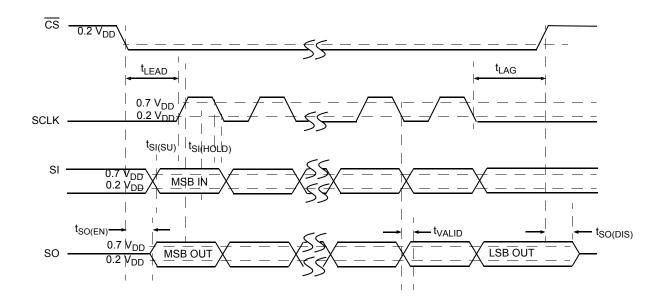

| SPI DIGITAL INTERFACE TIMING <sup>(14)</sup>                                                                                                                                                               |                         |      |     |     |      |  |  |

| Falling Edge of CS to Rising Edge of SCLK  Required Setup Time                                                                                                                                             | t <sub>LEAD</sub>       | 100  | _   | _   | ns   |  |  |

| Falling Edge of SCLK to Rising Edge of CS  Required Setup Time                                                                                                                                             | t <sub>LAG</sub>        | 50   | _   | -   | ns   |  |  |

| SI to Rising Edge of SCLK<br>Required Setup Time                                                                                                                                                           | t <sub>SI(SU)</sub>     | 16   | _   | _   | ns   |  |  |

| Rising Edge of SCLK to SI<br>Required Hold Time                                                                                                                                                            | t <sub>SI(HOLD)</sub>   | 20   | _   | -   | ns   |  |  |

| SI, CS, SCLK Signal Rise Time <sup>(15)</sup>                                                                                                                                                              | t <sub>R(SI)</sub>      | _    | 5.0 | _   | ns   |  |  |

| SI, CS, SCLK Signal Fall Time <sup>(16)</sup>                                                                                                                                                              | t <sub>F(SI)</sub>      | -    | 5.0 | _   | ns   |  |  |

| Time from Falling Edge of CS Low-impedance <sup>(17)</sup>                                                                                                                                                 | t <sub>SO(EN)</sub>     | -    | _   | 55  | ns   |  |  |

| Time from Rising Edge off CS to SO High-impedance <sup>(18)</sup>                                                                                                                                          | t <sub>SO(DIS)</sub>    | _    | _   | 55  | ns   |  |  |

| Time from Falling Edge of SCLK to SO Data Valid <sup>(19)</sup>                                                                                                                                            | t <sub>VALID</sub>      | -    | 25  | 55  | ns   |  |  |

| Sequential Transfer Rate Time required between data transfers                                                                                                                                              | t <sub>STR</sub>        | 1.0  | -   | -   | μs   |  |  |

| DIGITAL INTERFACE                                                                                                                                                                                          | •                       |      | •   | •   |      |  |  |

| Calibrated Timer Accuracy                                                                                                                                                                                  | t <sub>TIMER</sub>      | -    | _   | 10  | %    |  |  |

| Un-calibrated Timer Accuracy                                                                                                                                                                               | t <sub>TIMER</sub>      | -    | -   | 35  | %    |  |  |

|                                                                                                                                                                                                            |                         |      |     |     |      |  |  |

#### Notes

- 14. These parameters are guaranteed by design. Production test equipment uses 1.0 MHz, 5.0 V SPI interface.

- 15. This parameter is guaranteed by design, however it is not production tested.

- 16. Rise and Fall time of incoming SI, CS and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

- 17. Time required for valid output status data to be available on SO pin.

- 18. Time required for output states data to be terminated at SO pin.

- 19. Time required to obtain valid data out from SO following the fall of SCLK with 200 pF load.

# **TIMING DIAGRAMS**

# **FUNCTIONAL DESCRIPTION**

#### **FUNCTIONAL PIN DESCRIPTION**

#### **ANALOG SUPPLY VOLTAGE (VPWR)**

The VPWR pin is the battery input to the 33810 IC. The VPWR pin requires external reverse battery and transient protection. All IC analog current and internal logic current is provided from the VPWR pin. With VDD applied to the IC, the application of VPWR will perform a POR.

## **DIGITAL LOGIC SUPPLY VOLTAGE (VDD)**

The VDD input pin is used to determine communication logic levels between the microprocessor and the 33810 IC. Current from VDD is used to drive SO output and the pull-up current for  $\overline{\text{CS}}$ .  $\text{V}_{\text{DD}}$  must be applied for normal mode operation. Removing  $\text{V}_{\text{DD}}$  from the IC will place the device in sleep mode. With VPWR applied to the IC, the application of  $\text{V}_{\text{DD}}$  will perform a POR.

#### **GROUND (GND)**

The bottom pad or FLAG provides the only ground connection for the IC. The VPWR and VDD supplies are both referenced to the GND pad. The GND pad is used for both de-coupling the power supplies as well as power ground for the output drivers. Although the silicon die is epoxy attached to the top side of the pad, the pad must be grounded for proper electrical operation.

# **SERIAL CLOCK INPUT (SCLK)**

The system clock (SCLK) pin clocks the internal shift register of the 33810. The SI data is latched into the input shift register on the rising edge of SCLK signal. The SO pin shifts status bits out on the falling edge of SCLK. The SO data is available for the MCU to read on the rising edge of SCLK. With  $\overline{\text{CS}}$  in a logic high state, signals on the SCLK and SI pins will be ignored and the SO pin is tri-state

# CHIP SELECT (CS)

The system MCU selects the 33810 to receive communication using the chip select  $(\overline{CS})$  pin. With the  $\overline{CS}$  in a logic low state, command words may be sent to the 33810 via the serial input (SI) pin, and status information is received by the MCU via the serial output (SO) pin. The falling edge of  $\overline{CS}$  enables the SO output and transfers status information into the SO buffer.

Rising edge of the  $\overline{CS}$  initiates the following operation:

Disables the SO driver (high-impedance)

Activates the received command word, allowing the 33810 to activate/deactivate output drivers.

To avoid any spurious data, it is essential that the high-to-low and low-to-high transitions of the  $\overline{\text{CS}}$  signal occur only when SCLK is in a logic low state. Internal to the 33810 device is an active pull-up to VDD on  $\overline{\text{CS}}$ .

#### **SERIAL INPUT DATA (SI)**

The SI pin is used for serial instruction data input. SI information is latched into the input register on the rising edge of SCLK. A logic high state present on SI will program a *one* in the command word on the rising edge of the CS signal. To program a complete word, 16 bits of information or multiples of 8 there of must be entered into the device.

#### **SERIAL OUTPUT DATA (SO)**

The SO pin is the output  $\underline{\text{from}}$  the shift register. The SO pin remains tri-stated until the  $\overline{\text{CS}}$  pin transitions to a logic low state. All *normal operating drivers* are reported as  $\underline{\text{zero}}$ , all  $\underline{\text{faulted drivers}}$  are reported as  $\underline{\text{one}}$ . The negative transition of  $\underline{\overline{\text{CS}}}$  enables the SO driver.

The SI/SO shifting of the data follows a first-in-first-out protocol, with both input and output words transferring the most significant bit (MSB) first.

# **OUTPUT ENABLE (OUTEN)**

The OUTEN pin is an active low input. When the OUTEN pin is low, all the device outputs are active. The outputs are all disabled when OUTEN pin is high. SPI and parallel communications are still active in either state of OUTEN.

#### FEEDBACK VOLTAGE SENSOR (FB0-FB3)

The FBx pin has multiple functions for control and diagnostics of the external MOSFET/IGBT Ignition gate driver.

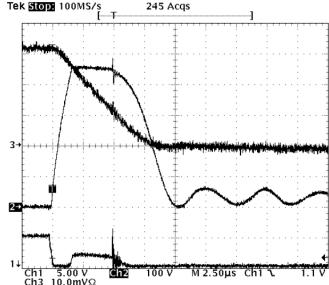

In Ignition (IGBT) Gate Driver Mode, the feedback inputs monitor the IGBT's collector voltage to provide the spark duration timer control signal. The spark duration timer monitors this input to determine if the secondary clamp function should be activated. In secondary clamp mode, the IGBT's collector voltage is internally clamped to V<sub>PWR</sub>+11V.

In the General Purpose Gate Driver mode, this input monitors the drain of an external MOSFET to provide short-circuit and open circuit detection by monitoring the MOSFET's drain to source voltage. The filter timer and threshold voltage are easily programmed through SPI (See tables 18 and 19 for SPI messages).

In General Purpose Gate Driver mode the FBx pin also provides a drain to gate clamp for fast turn off of inductive loads and external MOSFET protection.

#### **GATE DRIVER OUTPUT (GD0-GD3)**

The  ${\rm GD_X}$  pins are the gate drive outputs for an external MOSFET or IGBT. Internal to the device is a Gate to Source resistor designed to hold the external device in the OFF state while the device is in the POR or SLEEP state.

# LOW SIDE INJECTOR DRIVER OUTPUT (OUT0 - OUT3)

OUT0 - OUT3 are the Open drain low side (Injector) driver outputs. The drain voltage is actively clamped during turn off of inductive loads. These outputs can be connected in parallel for higher current loads provided the turn off energy rating is not exceeded.

# **RESISTOR SENSE POSITIVE (RSP)**

Resistor Sense Positive - Positive input of a current sense amplifier. The ignition coil current is monitored by sensing the voltage across an external resistor connected between RSP and RSN. The output of the current sense amplifier feeds the inputs of the NOMI and MAXI comparators.

Note: RSN and RSP must be grounded in V10 mode.

#### **RESISTOR SENSE NEGATIVE (RSN)**

Resistor Sense Negative - Negative input of a current sense amplifier. The ignition coil current is monitored by sensing the voltage across an external resistor connected to RSP and RSN. The output of the current sense amplifier feeds the inputs of the NOMI and MAXI comparators.

Note: RSN and RSP must be grounded in V10 mode.

#### NOMINAL IGNITION COIL CURRENT (NOMI)

Nominal ignition coil current output flag. This output is asserted when the output current exceeds the level selected by the DAC.

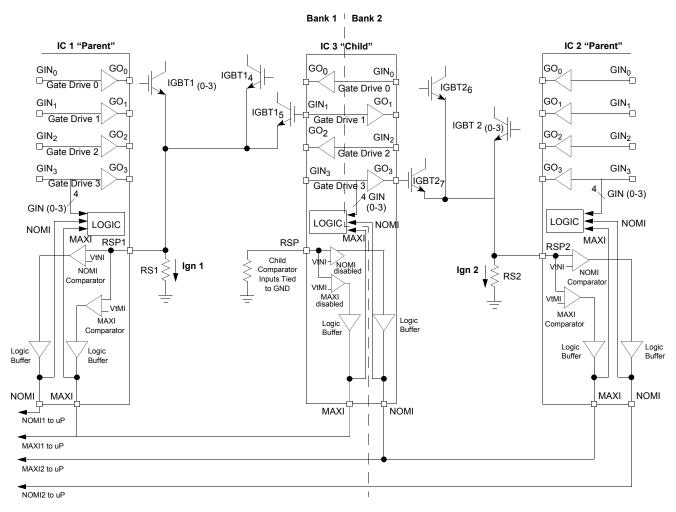

NOMI can be configured as an input pin for V10 mode applications where the gate drive needs to be latched off by another device's MAXI current sense amplifier output. The NOMI input will latch off gate drivers 5 and 6 when configured as a V10 mode ignition gate driver See Figure 10.

#### **SPARK DURATION OUTPUT (SPKDUR)**

SPKDUR is the Spark Duration output. This open drain output is low while feedback inputs FB0 through FB3 are above the programmed spark detection threshold. This output indicates an ignition flyback event. Each feedback input (FB0 - FB3) is logically OR'd to drive the SPKDUR output. There is a  $50\mu A$  pull up current source connected internally to the SPKDUR pin.

#### **MAXIMUM IGNITION COIL CURRENT (MAXI)**

Maximum ignition coil current output flag. This output is asserted when the output ignition coil current exceeds the selected level of the DAC. This signal also latches off the gate drive outputs when configured as an ignition gate driver. The MAXI current level is determined by the voltage drop across an external sense resistor connected to pins RSP and RSN.

MAXI can be configured as an input pin for V10 applications where the gate drive needs to be latched off by another devices MAXI current sense amplifier output. The MAXI input will latch off gate drivers 7 and 8 when configured as ignition gate drive outputs See Figure 10.

# DRIVER INPUT (DIN0-DIN3), GATE DRIVER INPUT (GIN0-GIN3)

Parallel input pins for OUT0-OUT3 low side drivers and GD0-GD3 gate drivers. Each parallel input control pin is active high and has an internal pull-down current sink. The parallel input data is logically OR'd with the corresponding SPI input data register contents, except for the ignition mode IGBT drivers. They are only controlled by the parallel inputs GIN0-GIN3. In GPGD mode, GIN0-GIN3 are logically OR'd with SPI input data. All outputs are disabled when the OUTEN pin is HIGH, regardless of the state of the command inputs.

# Power Supply POR Injector Drivers SPI Interface OUT0 - OUT3 Parallel Control Inputs PWM Controller Ignition Gate Pre-Drivers NOMI / MAXI DAC SPARKDUR DAC Power Supply MCU Interface and Output Driver Control Drivers

#### FUNCTIONAL INTERNAL BLOCK DESCRIPTION

Figure 4. Functional Internal Block Diagram

#### **POWER SUPPLY/POR**

The 33810 is designed to operate from 4.5 to 36 V on the VPWR pin. The VPWR pin supplies power to all internal regulators, analog, and logic circuit blocks. The VDD supply is used for setting communication threshold levels and supplying power to the SO driver. This IC architecture provides a low quiescent current sleep mode. Applying VPWR and VDD to the device will generate a Power On Reset (POR) and place the device in the Normal State. The Power On Reset circuit incorporates a timer to prevent high frequency transients from causing a POR.

# MCU INTERFACE AND OUTPUT CONTROL

This component provides parallel input pins for OUT0-OUT3 low side drivers and GD0-GD3 gate drivers. Each parallel input control pin is active high and has an internal pulldown current sink. The parallel input data is logically OR'd

with the corresponding SPI input data register contents. All outputs are disabled when the OUTEN pin is HIGH, regardless of the state of the command inputs.

#### **INJECTOR DRIVERS: OUT0 - OUT3**

These pins are the Open drain low side (Injector) driver outputs. The drain voltage is actively clamped during turn off of inductive loads. These outputs can be connected in parallel for higher current loads, provided the turn off energy rating is not exceeded.

# **IGNITION GATE PRE-DRIVERS: GD0 - GD3**

These pins are the gate drive outputs for an external MOSFET or IGBT. Internal to the device is a Gate to Source resistor designed to hold the external device in the OFF state while the device is in the POR or Sleep State.

#### **FUNCTIONAL DEVICE OPERATION**

#### **OPERATIONAL MODES**

#### **POWER SUPPLY**

The 33810 is designed to operate from 4.5 to 36 V on the VPWR pin. The VPWR pin supplies power to all internal regulators, analog and logic circuit blocks. The VDD supply is used for setting communication threshold levels and supplying power to the SO driver. This IC architecture provides flexible microprocessor interfacing and low quiescent current sleep mode.

#### **POWER-ON RESET (POR)**

Applying  $V_{PWR}$  and  $V_{DD}$  to the device will generate a Power On Reset (POR) and place the device in the Normal State. The Power On Reset circuit incorporates a filter to prevent high frequency transients from causing a POR.

All outputs are disabled when the OUTEN input pin is HIGH regardless of the SPI control registers or the logic level on the parallel input pins. With the OUTEN pin high, SPI messages may be sent and received by the device. Upon enabling the device (OUTEN low), outputs will be activated based on the state of the command register or parallel input.

Table 5. Operational States

| VPWR | VDD | OUTEN | OUTPUTS | STATE        |

|------|-----|-------|---------|--------------|

| L    | L   | X     | OFF     | Power<br>Off |

| L    | Н   | Х     | OFF     | POR          |

| Н    | L   | Х     | OFF     | SLEEP        |

| Н    |     | Х     | OFF     | POR          |

|      | Н   | Х     | OFF     | POR          |

|      | L   | Х     | OFF     | SLEEP        |

| Н    | Н   | L     | ACTIVE  | NORMAL       |

| Н    | Н   | Н     | OFF     | NORMAL       |

#### **SLEEP STATE**

Sleep State is entered when the  $V_{DD}$  supply voltage is removed from the VDD pin. In Sleep State all outputs are off. Applying  $V_{DD}$  will force the device to exit the Sleep State and generates a POR.

#### **NORMAL STATE**

The default Normal State is entered when power is applied to the VPWR and VDD pins.

Control register settings from a Power-ON Reset (POR) are as follows:

- · All outputs off

- IGNITION gate driver mode enabled (IGBT Ignition Mode).

- · PWM frequency and duty cycle control disabled.

- Off State open load detection enabled (LSD)

- MAXI dac set to 14 A, NOMI DAC set to 5.5A

- Spark detect level VIL DAC set to V<sub>PWR</sub> +5.5V

- Open secondary timer set to 100 μs

- · Dwell timer set 32ms

- · Soft shutdown disabled

- · Low-voltage flyback clamp disabled

- · Dwell overlap MAXI offset disabled

#### MODES OF OPERATION

In Normal State, the 33810 gate driver has three modes of operation, ignition Mode, GPGD (General Purpose Gate Driver) Mode and V10 mode. The operating mode of each gate driver may be set individually and is programmed using the Mode Select Command.

#### MODE SELECT COMMAND

The MODE Select Command is used to set the operating mode for the GDx gate driver outputs, over/under-voltage operation and to enable V10 Mode and the PWM generators. The Mode Select Command programmable features are listed below.

- · Ignition/GPGD Mode select (gate drivers)

- V10 Mode enable

- · Over/Under-voltage operation for all drivers

- GPGD PWM controller enable

#### **IGNITION/GPGD MODE SELECT**

The Ignition/General Purpose Gate Driver Mode select bits determine independently, the operating mode of each of the GDx gate driver outputs. Bits 8,9,10,11 correspond to GD0, GD1, GD2, GD3 respectively. Setting the bit to a logic 0 sets the GDx driver to the Ignition Mode. Setting the bit to a logic 1 commands the GDX driver to the General Purpose Mode and disables the ignition features for that particular gate driver (except the MAXI current shutdown feature). Further information on GDx gate driver in Ignition Mode and General Purpose Mode is provided later in this section of the data sheet.

#### V10 MODE ENABLE BIT

The V10 Enable bit allows the user to configure the device for 10 cylinder applications. When the V10 Mode is enabled, the device configures the NOMI pin and MAXI pin as digital inputs rather than outputs. The new MAXI input pin receives

the MAXI shutdown signal for GD0 and GD2 and the new NOMI input pin receives the MAXI shutdown signal for GD1 and GD3. Further information on V10 Mode is provided in the V10 Application section.

Note: RSN and RSP must be grounded in V10 Mode.

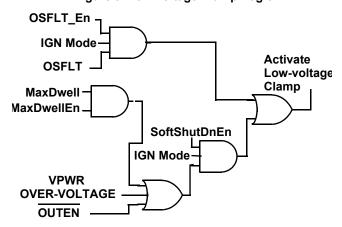

#### OVER/UNDER-VOLTAGE SHUTDOWN/RETRY BIT

The Over/Under-voltage Shutdown/Retry bit allows the user to select the global over and under-voltage fault strategy for all the outputs. In an over-voltage or under-voltage condition on the VPWR pin, all outputs are commanded off. The Over/Under-voltage control bit sets the operation of the outputs when returning from over/under- voltage. Setting the Over/Under-voltage bit to logic [1] will force all outputs to remain OFF when V<sub>PWR</sub> returns to normal level. To turn the output on again, the corresponding input pin or SPI bit must be reactivated. Setting the Over/Under-voltage bit to logic [0] will command all outputs to resume their previous state when VPWR returns to normal level. Table 6 below provides the output state when returning from over or under-voltage.

Table 6. Over-voltage/Under-voltage Truth Table

| GINx DINx<br>Input Pin | SPI<br>Bit | Over/<br>Under-<br>voltage<br>Control<br>Bit | OUTEN<br>Input pin | State When<br>Returning From<br>Over/Under-voltage |

|------------------------|------------|----------------------------------------------|--------------------|----------------------------------------------------|

| Х                      | X          | Х                                            | 1                  | OFF                                                |

| Х                      | Х          | 1                                            | 0                  | OFF                                                |

| 0                      | 0          | 0*                                           | 0                  | OFF                                                |

| Х                      | 1          | 0*                                           | 0                  | ON                                                 |

| 1                      | Х          | 0*                                           | 0                  | ON                                                 |

<sup>\*</sup> Default Setting

Note: The SPI bit does not control the Gate Driver outputs in the Ignition Mode, only in the GPGD Mode.

An under-voltage condition on VDD results in the global shutdown of all outputs and reset of all internal control registers. The  $V_{DD}$  under-voltage threshold is between 0.8V and 2.8V

#### PWM<sub>X</sub> ENABLE BIT