# MC145574 ISDN S/T-Interface Transceiver

Coming through loud and clear.

This page intentionally left blank.

# MC145574 **ISDN S/T-Interface Transceiver**

Freescale Semiconductor, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 1999

#### **MC145574 TABLE OF CONTENTS**

#### MC145574 ISDN S/T-INTERFACE TRANSCEIVER

# **SECTION 1**INTRODUCTION

| 1.1            | INTRODUCTION                                    | 1–1        |

|----------------|-------------------------------------------------|------------|

| 1.2            | ORGANIZATION OF DATA SHEET                      | 1–1        |

| 1.3            | FEATURES                                        | 1–2        |

| 1.4            | BLOCK DIAGRAM                                   | 1–3        |

| 1.5            | PACKAGING                                       | 1–3        |

|                |                                                 |            |

|                | SECTION 2                                       |            |

|                | WIRING CONFIGURATIONS                           |            |

| 2.1            | INTRODUCTION                                    | 2–1        |

| 2.2            | POINT-TO-POINT OPERATION                        | 2–1        |

| 2.3            | SHORT PASSIVE BUS OPERATION                     | 2–2        |

| 2.4            | EXTENDED PASSIVE BUS OPERATION                  | 2–2        |

| 2.5            | BRANCHED PASSIVE BUS OPERATION                  | 2–3        |

| 2.6            | NT1 STAR MODE OF OPERATION                      | 2–3        |

|                | SECTION 3                                       |            |

|                | ACTIVATION/DEACTIVATION OF S/T TRANSCEIVER      |            |

| 3.1            | INTRODUCTION                                    | 3–1        |

| 3.2            | TRANSMISSION STATES FOR NT MODE S/T TRANSCEIVER | 3–1        |

| 3.3            | TRANSMISSION STATES FOR TE MODE S/T TRANSCEIVER | 3–1        |

| 3.4            | ACTIVATION OF S/T LOOP BY NT                    | 3–1        |

| 3.5            | ACTIVATION OF S/T LOOP BY TE                    | 3–2        |

| 3.6            | ACTIVATION PROCEDURES IGNORED                   | 3–2        |

| 3.7            | FRAME SYNC                                      | 3–2        |

| 3.7.1          | NT Mode                                         | 3–2        |

| 3.7.2          | TE Mode                                         | 3–2        |

| 3.8            | ACTIVATION INDICATION                           | 3–2        |

| 3.9            | NR1(2) — ERROR INDICATION (EI)                  | 3–2        |

| 3.10           | DEACTIVATION PROCEDURES                         | 3–3        |

| 3.11           | INITIAL STATE OF B1 AND B2 CHANNELS             | 3–3        |

| 3.11.1         | NT                                              | 3–3        |

| 3.11.2         | TE                                              | 3–3        |

| 3.12<br>3.12.1 | ADDITIONAL NOTES                                | 3–3<br>3–3 |

| 3.12.1         | Echo Channel                                    | 3–3        |

| 3.12.3         | A Bit                                           | 3–4        |

| 3.12.4         | SCP Nomenclature                                | 3–4        |

| 3.12.5         | SCP Indication of Transmit and Receive States   | 3–4        |

|                |                                                 |            |

# **MC145574 TABLE OF CONTENTS**

# SECTION 4 THE INTERCHIP DIGITAL LINK

| 4.1          | INTRODUCTION                                                                           | 4–1 |

|--------------|----------------------------------------------------------------------------------------|-----|

| 4.2          | SIGNAL DESCRIPTION                                                                     | 4–1 |

| 4.3          | IDL2 STANDARD MODE                                                                     | 4–2 |

| 4.3.1        | NT IDL2 Slave                                                                          | 4–2 |

| 4.3.2        | NT IDL2 Master                                                                         | 4–3 |

| 4.3.3        | TE IDL2 Master                                                                         | 4–3 |

| 4.3.4        | TE IDL2 Master Free Run                                                                | 4–3 |

| 4.3.5        | TE IDL2 Slave                                                                          | 4–3 |

| 4.3.6        | Additional Notes                                                                       | 4–4 |

| 4.3.6.1      | Phase Relationship of the NT Transmit Signal with Respect to FSC/FSR                   | 4–4 |

| 4.3.6.2      | Phase Relationship of the TE Transmit Signal with Respect to FSC/FSR, When in the IDL2 |     |

|              | Master Mode                                                                            | 4–4 |

| 4.3.6.3      | Operation of Multiple MC145574s in TE Slave Mode                                       | 4–4 |

| 4.3.6.4      | Independent Tx/Rx Frame Syncs                                                          | 4–4 |

| 4.3.6.5      | Timeslot Assignment                                                                    | 4–4 |

| 4.3.6.6      | Short and Long Framing                                                                 | 4–8 |

| 4.3.6.7      | TSEN Signal                                                                            | 4–9 |

| 4.3.6.8      | Miscellaneous                                                                          | 4–9 |

| 4.3.6.9      | IDL2 Waveform Diagrams                                                                 | 4–9 |

|              |                                                                                        |     |

|              | SECTION 5                                                                              |     |

|              | SERIAL CONTROL PORT                                                                    |     |

| 5.1          | INTRODUCTION                                                                           | 5–1 |

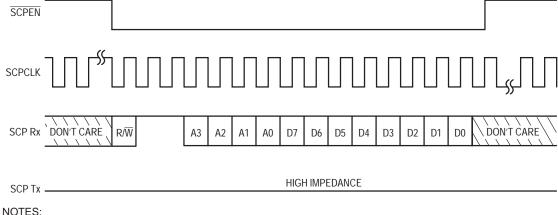

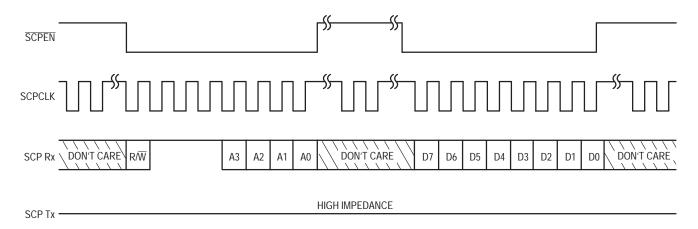

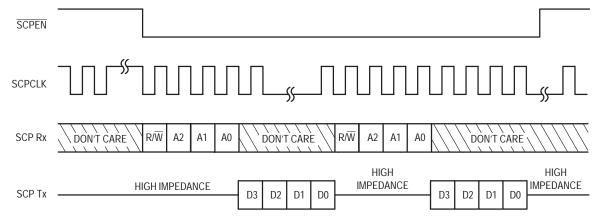

| 5.2          | SCP TRANSACTIONS                                                                       | 5–1 |

| 5.2.1        | SCP Nibble Register Read                                                               | 5–1 |

| 5.2.2        | SCP Nibble Register Write                                                              | 5–2 |

| 5.2.3        | SCP Byte Register Read                                                                 | 5–3 |

| 5.2.4        | SCP Byte Register Write                                                                | 5–4 |

| 5.2.5        | SCP Merged Read/Write                                                                  | 5–5 |

| 5.3          | SIGNAL DESCRIPTION                                                                     | 5–6 |

| 5.3.1        | SCP Tx                                                                                 | 5–6 |

| 5.3.2        | SCP Rx                                                                                 | 5–6 |

| 5.3.3        | SCPCLK                                                                                 | 5–6 |

| 5.3.4        | SCPEN                                                                                  | 5–7 |

| 5.3.5        | ĪRQ                                                                                    | 5–7 |

| 5.4          | SCP HIGH-IMPEDANCE DIGITAL OUTPUT MODE (SCP HIDOM)                                     | 5–7 |

| 5.5          | ADDITIONAL NOTES                                                                       | 5–7 |

| 5.5.1        | SCP Independent of Crystal                                                             | 5–7 |

| 5.5.2        | SCP Slave                                                                              | 5–7 |

|              |                                                                                        |     |

|              | SECTION 6                                                                              |     |

|              | SECTION 6 GENERAL CIRCUIT INTERFACE                                                    |     |

|              | GENERAL CIRCUIT INTERFACE                                                              |     |

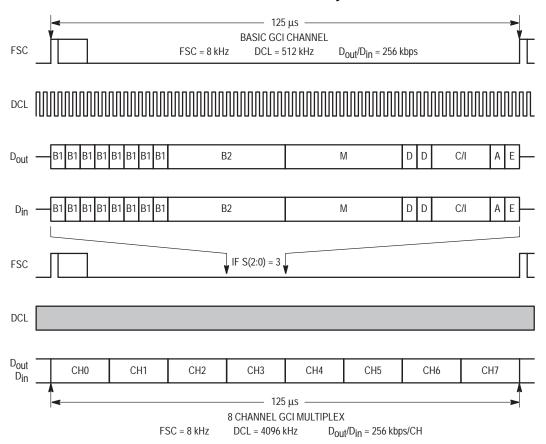

| 6.1          | OVERVIEW                                                                               | 6–1 |

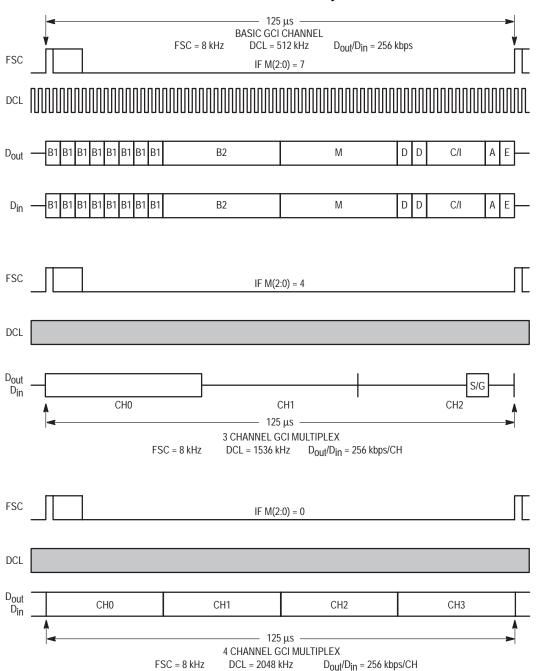

| 6.2          | GCI FRAME STRUCTURE                                                                    | 6–1 |

| 6.3          | ENABLING THE GCI MODES                                                                 | 6–1 |

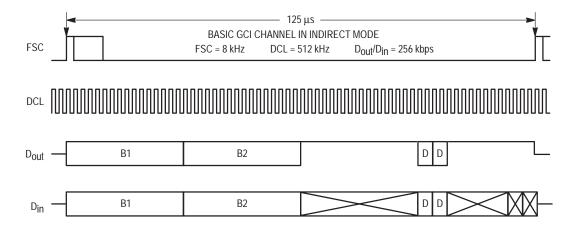

| 6.4          | GCI INDIRECT MODE                                                                      | 6–4 |

|              |                                                                                        | _   |

| 6.5<br>6.5.1 | GCI DIRECT MODE                                                                        | 6–6 |

| 0.0.1        | Slave Mode                                                                             | 6–6 |

|              |                                                                                        |     |

# **MC145574 TABLE OF CONTENTS**

#### **SECTION 6 (continued)**

| 6.5.2            | Master Mode                                                         | 6–6        |  |  |  |  |

|------------------|---------------------------------------------------------------------|------------|--|--|--|--|

| 6.6              | 2B+D CHANNELS                                                       | 6–7        |  |  |  |  |

| 6.7              | M AND A/E CHANNELS                                                  | 6–7        |  |  |  |  |

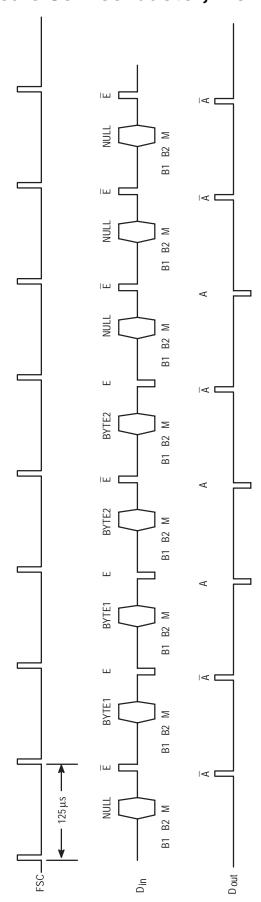

| 6.7.1            | Monitor Channel Operation                                           | 6–8        |  |  |  |  |

| 6.8              | •                                                                   |            |  |  |  |  |

| 6.8.1            | MONITOR CHANNEL MESSAGES    6-      Monitor Channel Commands    6-1 |            |  |  |  |  |

| 6.8.2            | Monitor Channel Response Messages                                   | 6–10       |  |  |  |  |

| 6.8.3            | Monitor Channel Status Indication Messages                          | 6–10       |  |  |  |  |

| 6.8.4            | Accessible Monitor Channel Registers                                | 6–11       |  |  |  |  |

| 6.8.5            | SCP/GCI Register Differences                                        | 6–12       |  |  |  |  |

| 6.9              | COMMAND INDICATE CHANNEL OPERATION                                  | 6–12       |  |  |  |  |

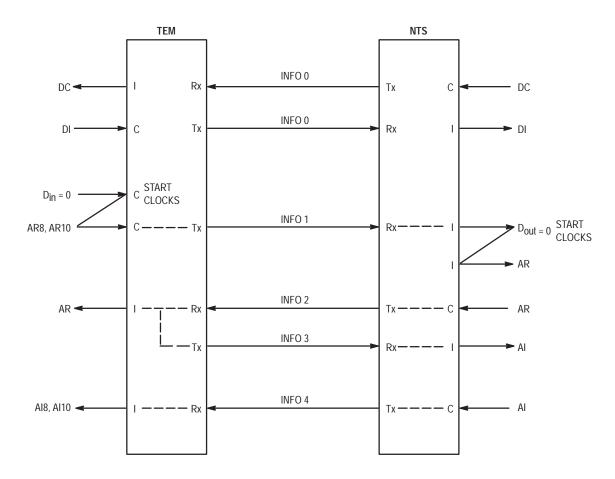

| 6.10             | GCI ACTIVATION AND DEACTIVATION TIMING DIAGRAMS                     |            |  |  |  |  |

| 6.10             | GCI ACTIVATION AND DEACTIVATION TIMING DIAGRAMS                     | 6-14       |  |  |  |  |

|                  | SECTION 7                                                           |            |  |  |  |  |

|                  | SECTION 7 PIN DESCRIPTIONS                                          |            |  |  |  |  |

| 7.1              | INTRODUCTION                                                        | 7–1        |  |  |  |  |

| 7.2              | PIN DESCRIPTIONS                                                    | 7–1        |  |  |  |  |

| 7.2.1            | ISET                                                                | 7–1        |  |  |  |  |

| 7.2.2            | RxN, RxP                                                            | 7–1        |  |  |  |  |

| 7.2.3            | TE/NT                                                               | 7–2        |  |  |  |  |

| 7.2.4            | M/S                                                                 | 7–2        |  |  |  |  |

| 7.2.5            | T_IN/TFSC/TCLK/FIX                                                  | 7–2        |  |  |  |  |

| 7.2.6            | V <sub>SS</sub>                                                     | 7–2        |  |  |  |  |

| 7.2.7            | SG/DGRANT/ANDOUT                                                    | 7–2        |  |  |  |  |

| 7.2.8            | DREQUEST/ANDIN                                                      | 7–2        |  |  |  |  |

| 7.2.9            | CLASS/ECHO_IN                                                       | 7–3        |  |  |  |  |

| 7.2.10           | FSC/FSR                                                             | 7–3        |  |  |  |  |

| 7.2.11           | DCL                                                                 | 7–3        |  |  |  |  |

| 7.2.12           | D <sub>in</sub>                                                     | 7–3        |  |  |  |  |

| 7.2.13           | D <sub>out</sub>                                                    | 7–3        |  |  |  |  |

| 7.2.14           | SCP Tx/S0/M0                                                        | 7–3        |  |  |  |  |

| 7.2.15           | SCP Rx/S1/M1                                                        | 7–3        |  |  |  |  |

| 7.2.16           | SCPCLK/S2/M2                                                        | 7–3        |  |  |  |  |

| 7.2.17           | SCPEN/GCIEN                                                         | 7–3        |  |  |  |  |

| 7.2.18           | TSEN/FST/BCL/LBA                                                    | 7–3        |  |  |  |  |

| 7.2.19           |                                                                     | 7–4        |  |  |  |  |

| 7.2.20           | V <sub>DD</sub> 3                                                   | 7–4        |  |  |  |  |

| 7.2.21<br>7.2.22 | V <sub>DD</sub> I/O                                                 | 7–4<br>7–4 |  |  |  |  |

| 7.2.22           | V <sub>DD</sub> 5                                                   | 7-4<br>7-4 |  |  |  |  |

| 7.2.23<br>7.2.24 | EXTALXTAL                                                           | 7-4<br>7-4 |  |  |  |  |

| 7.2.24           | TxN, TxP                                                            | 7-4<br>7-4 |  |  |  |  |

| 7.2.25<br>7.2.26 | RESET                                                               | 7-4<br>7-4 |  |  |  |  |

| 7.2.20           |                                                                     | 7–4<br>7–5 |  |  |  |  |

| 7.3<br>7.3.1     | ADDITIONAL NOTES                                                    | 7–5<br>7–5 |  |  |  |  |

| 7.3.1<br>7.3.2   | Input Levels                                                        | 7–5<br>7–5 |  |  |  |  |

| 7.3.2            | SCP HIDOM                                                           | 7–5<br>7–5 |  |  |  |  |

|                  |                                                                     | , 0        |  |  |  |  |

# **MC145574 TABLE OF CONTENTS**

# SECTION 8 NIBBLE REGISTER MAP DEFINITION

| 8.1   | INTRODUCTION                               | 8–1  |

|-------|--------------------------------------------|------|

| 8.2   | NR0                                        | 8–2  |

| 8.3   | NR1                                        | 8–3  |

| 8.4   | NR2                                        | 8–3  |

| 8.5   | NR3                                        | 8–4  |

| 8.6   | NR4                                        | 8–5  |

| 8.7   | NR5                                        | 8–6  |

| 8.8   | NR6                                        | 8–7  |

| 8.9   | NR7                                        | 8–8  |

|       |                                            |      |

|       | SECTION 9 BYTE REGISTER MAP DEFINITION     |      |

| 9.1   | INTRODUCTION                               | 9–1  |

| 9.2   | BR0                                        | 9–3  |

| 9.3   | BR1                                        | 9–3  |

| 9.4   | BR2                                        | 9–3  |

| 9.5   | BR3                                        | 9–3  |

| 9.6   | BR4                                        | 9–4  |

| 9.7   | BR5                                        | 9–5  |

| 9.8   | BR6                                        | 9–5  |

| 9.9   | BR7                                        | 9–6  |

| 9.10  | BR8                                        | 9–8  |

| 9.11  | BR9                                        | 9–8  |

| 9.12  | BR10                                       | 9–9  |

| 9.13  | BR11                                       | 9–10 |

| 9.14  | BR12                                       | 9–12 |

| 9.15  | BR13                                       | 9–12 |

| 9.16  | BR14                                       | 9–13 |

| 9.17  | BR15                                       | 9–13 |

|       |                                            |      |

|       | SECTION 10 OVERLAY REGISTER MAP DEFINITION |      |

| 10.1  | INTRODUCTION                               | 10–1 |

| 10.1  | OR0                                        | 10-1 |

| 10.2  | OR1                                        | 10-2 |

| 10.3  | OR2                                        | 10-2 |

| 10.5  | OR3                                        | 10-3 |

| 10.6  | OR4                                        | 10-3 |

| 10.7  | OR5                                        | 10-3 |

| 10.7  | OR6                                        | 10-4 |

| 10.9  | OR7                                        | 10-5 |

| 10.10 | OR8                                        | 10–6 |

| 10.10 | OR9                                        | 10-7 |

| 10.12 | OR15                                       | 10–7 |

|       |                                            |      |

# **MC145574 TABLE OF CONTENTS**

#### SECTION 11 D CHANNEL OPERATION

| 11.1<br>11.2<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4                    | INTRODUCTION  IDL2 D CHANNEL OPERATION  Gaining Access to the D Channel in the TE Mode  Setting the Class for TE Mode of Operation  Generation of an Interrupt in the TE Mode  Gaining Access to the D Channel in the NT Mode | 11–1<br>11–2<br>11–2<br>11–2<br>11–3<br>11–3                 |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 11.2.5                                                                  | GCI D Channel Operation                                                                                                                                                                                                       | 11–3                                                         |

|                                                                         | SECTION 12 MULTIFRAMING                                                                                                                                                                                                       |                                                              |

| 12.1<br>12.2                                                            | INTRODUCTIONACTIVATION/DETECTION OF MULTIFRAMING IN THE MC145574                                                                                                                                                              | 12–1<br>12–1                                                 |

| 12.3                                                                    | WRITING S CHANNEL DATA TO AN NT-CONFIGURED MC145574                                                                                                                                                                           | 12–1                                                         |

| 12.4                                                                    | MULTIFRAME INTERRUPTS IN AN NT-CONFIGURED MC145574                                                                                                                                                                            | 12–2                                                         |

| 12.5<br>12.6                                                            | READING Q CHANNEL DATA FROM AN NT-CONFIGURED MC145574                                                                                                                                                                         | 12–3<br>12–3                                                 |

| 12.6                                                                    | MULTIFRAME INTERRUPTS IN A TE-CONFIGURED MC145574                                                                                                                                                                             | 12-3                                                         |

| 12.8                                                                    | READING S SUBCHANNEL DATA FROM A TE-CONFIGURED MC145574                                                                                                                                                                       | 12–3                                                         |

| 12.9                                                                    | MULTIFRAMING IN GCI MODE                                                                                                                                                                                                      | 12-3                                                         |

|                                                                         | SECTION 13                                                                                                                                                                                                                    |                                                              |

|                                                                         | DEVICE CONFIGURATIONS                                                                                                                                                                                                         |                                                              |

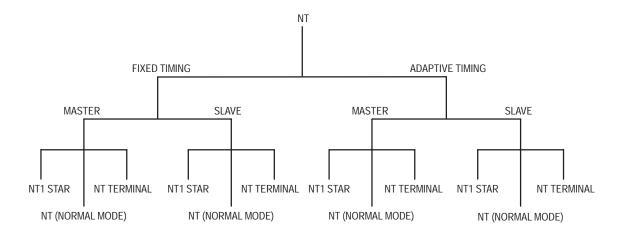

| 13.1<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.3.1<br>13.1.3.2<br>13.2<br>1 | NT CONFIGURATIONS NT Fixed or Adaptive Timing NT Master or Slave NT1 Star and NT Terminal Modes NT1 Star Mode NT Terminal Mode TE CONFIGURATIONS TE Master Mode (TEM) TE Slave Mode (TES)                                     | 13-1<br>13-1<br>13-2<br>13-2<br>13-4<br>13-4<br>13-5<br>13-5 |

|                                                                         | SECTION 14 CLOCK INTERFACE                                                                                                                                                                                                    |                                                              |

|                                                                         |                                                                                                                                                                                                                               |                                                              |

|                                                                         | SECTION 15 INTERRUPTS                                                                                                                                                                                                         |                                                              |

| 15.1                                                                    | INTRODUCTION                                                                                                                                                                                                                  | 15–1                                                         |

| 15.2                                                                    | IRQ7 NR3(0) — NT : D CHANNEL COLLISION  TE : NOT APPLICABLE  NR4(0) — ENABLE                                                                                                                                                  | 15–1                                                         |

| 15.3                                                                    | IRQ1 NR3(1) — TE: D CHANNEL COLLISION NT: NOT APPLICABLE                                                                                                                                                                      |                                                              |

| 15 1                                                                    | NR4(1) — ENABLE                                                                                                                                                                                                               | 15–1                                                         |

| 15.4                                                                    | IRQ2 NR3(2) — MULTIFRAME RECEPTION NR4(2) — ENABLE                                                                                                                                                                            | 15–1                                                         |

# **MC145574 TABLE OF CONTENTS**

#### **SECTION 15 (continued)**

| 15.5             | IRQ3 NR3(3) — CHANGE IN Rx INFO STATE NR4(3) — ENABLE                        | 15–2         |

|------------------|------------------------------------------------------------------------------|--------------|

| 15.6             | IRQ6 NR3(1) — NT: FAR-END CODE VIOLATION (FECV) DETECTION TE: NOT APPLICABLE |              |

| 15 7             | NR4(1) — ENABLE                                                              | 15–2<br>15–2 |

| 15.7             | GCI MODE                                                                     | 15-2         |

|                  | SECTION 16 TRANSMISSION LINE INTERFACE CIRCUITRY                             |              |

| 16.1             | INTRODUCTION                                                                 | 16–1         |

| 16.2             | TRANSMIT LINE INTERFACE CIRCUITRY                                            | 16–1         |

| 16.3<br>16.4     | RECEIVE LINE INTERFACE CIRCUITRY  ADDITIONAL NOTES                           | 16–1<br>16–3 |

| 16.4.1           | Sources of Line Interface Transformers                                       | 16–3         |

| 16.4.2           | Termination Resistors                                                        | 16–3         |

| 16.4.3           | Protection Diodes                                                            | 16–3         |

|                  | SECTION 17 POWER MODE OPERATION                                              |              |

| 17.1             | POWER SUPPLY STRATEGY                                                        | 17–1         |

| 17.2             | POWER MODES                                                                  | 17–1         |

| 17.2.1           | Normal Operation                                                             | 17–1         |

| 17.2.2<br>17.2.3 | Transmit Power–Down Absolute Minimum Power                                   | 17–1<br>17–2 |

| 17.2.4           | Sleep                                                                        | 17–2         |

|                  | CECTION 40                                                                   |              |

|                  | SECTION 18 ELECTRICAL SPECIFICATIONS                                         |              |

| 18.1             | MAXIMUM RATINGS                                                              | 18–1         |

| 18.2             | DIGITAL DC ELECTRICAL CHARACTERISTICS                                        | 18–1         |

| 18.3             | ANALOG CHARACTERISTICS                                                       | 18–2         |

| 18.4             |                                                                              | 18–2         |

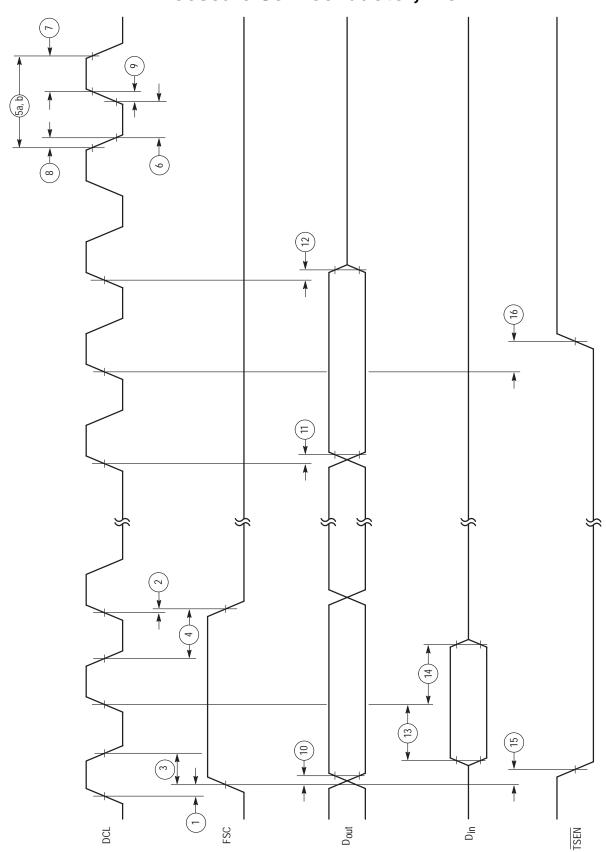

| 18.5<br>18.5.1   | IDL2 TIMING CHARACTERISTICS                                                  | 18–3<br>18–3 |

| 18.5.2           | IDL2 Slave Timing, 8– and 10–bit Formats                                     |              |

| 18.6             | GCI TIMING FOR MASTER AND SLAVE MODE                                         | 18–6         |

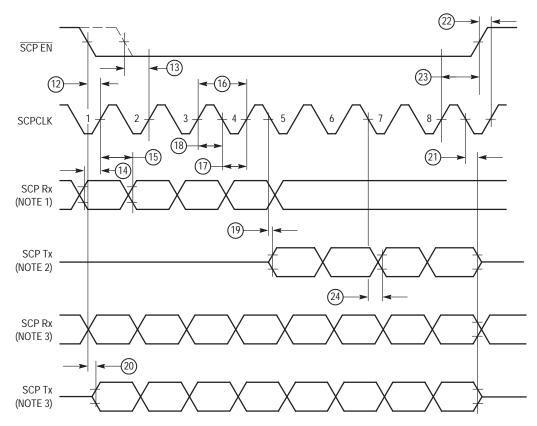

| 18.7             | SCP TIMING CHARACTERISTICS                                                   | 18–8         |

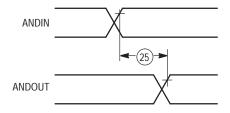

| 18.8             | NT1 STAR MODE TIMING CHARACTERISTICS                                         | 18–9         |

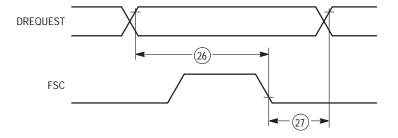

| 18.9             | D CHANNEL TIMING CHARACTERISTICS (IDL2 MODE)                                 | 18–9         |

#### **MC145574 TABLE OF CONTENTS**

#### SECTION 19 MECHANICAL DATA

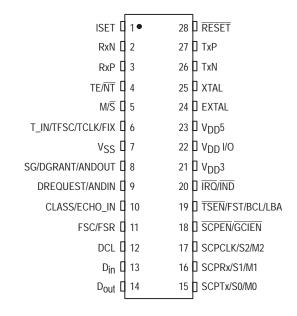

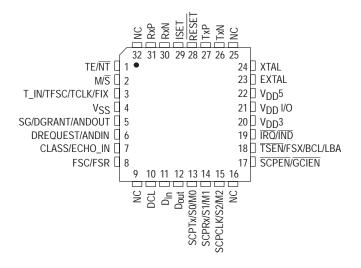

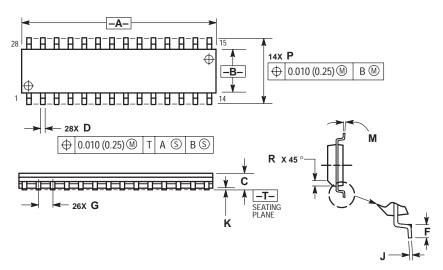

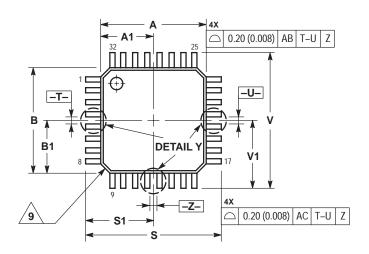

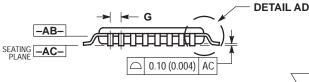

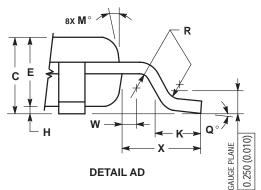

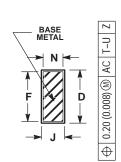

| 19.1                                  | PIN ASSIGNMENTS                                                                                              | 19–1                            |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------|

| 19.2                                  | PACKAGE DIMENSIONS                                                                                           | 19–2                            |

|                                       | SECTION 20<br>F57J4 MASK SET DIFFERENCES                                                                     |                                 |

| 20.1<br>20.1.1<br>20.1.2<br>20.1.3    | FUNCTIONAL DIFFERENCES  Differences in Section 6  Differences in Section 10  Differences in Section 13.1.3.2 | 20-1<br>20-1<br>20-1<br>20-1    |

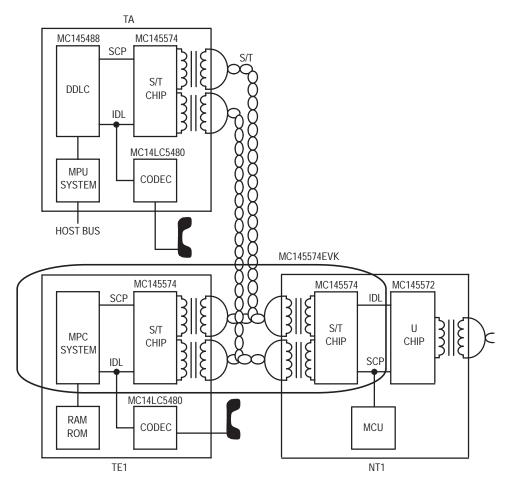

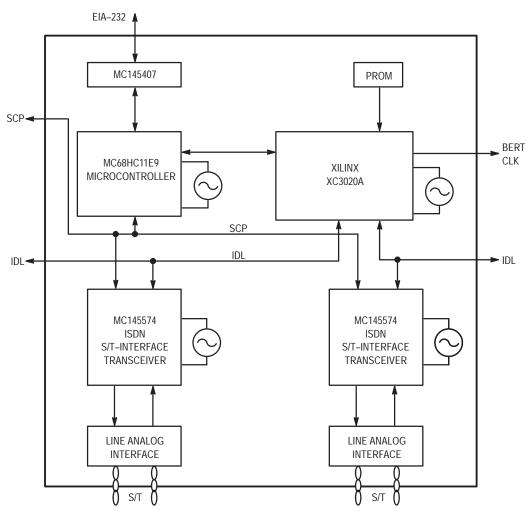

|                                       | APPENDIX A  MC145574EVK ISDN S/T-INTERFACE TRANSCEIVER EVALUATION KIT                                        |                                 |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3 | INTRODUCTION FEATURES General Hardware Software                                                              | A-1<br>A-2<br>A-2<br>A-2<br>A-2 |

| A.3                                   | BLOCK DIAGRAM                                                                                                | A-3                             |

APPENDIX B

GLOSSARY OF TERMS AND ABBREVIATIONS

# MC145574 LIST OF FIGURES

| Figure 1–1.    | Block Diagram                                                             | 1–3  |

|----------------|---------------------------------------------------------------------------|------|

| Figure 2–1.    | Point-to-Point                                                            | 2-1  |

| Figure 2–2.    | Short Passive Bus                                                         | 2–2  |

| Figure 2–3.    | Extended Passive Bus                                                      | 2–2  |

| Figure 2–4.    | Branched Passive Bus                                                      | 2-3  |

| Figure 4–1.    | Phase Relationship of NT Transmit Signal                                  | 4–5  |

| Figure 4–2.    | Two-Baud Turnaround in TE                                                 | 4–6  |

| Figure 4–3.    | Phase Relationship of TE Transmit Signal                                  | 4–7  |

| Figure 4–4.    | Example Architecture of an NT2                                            | 4–8  |

| Figure 4–5.    | Standard IDL2 10–Bit Mode                                                 | 4-10 |

| Figure 4–6.    | Standard IDL2 8–Bit Mode with Long Frame Sync                             | 4-10 |

| Figure 4–7.    | Standard IDL2 8–Bit Slave Mode with Independent Frame Syncs               | 4-10 |

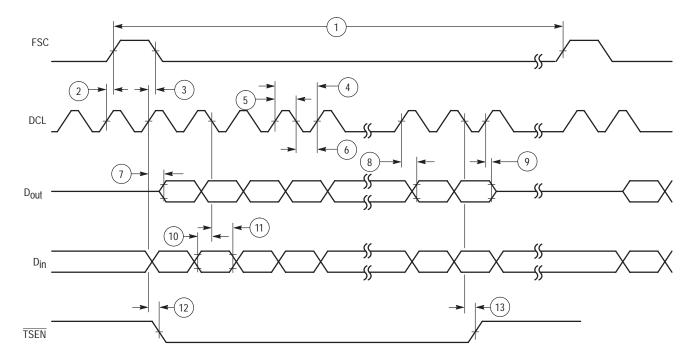

| Figure 4–8.    | Timeslot Operation with Independent Slave Frame Syncs, TSEN               | 4–11 |

| Figure 5–1.    | Serial Control Port Nibble Register Read Operation                        | 5–2  |

| Figure 5–2.    | Serial Control Port Nibble Register Write Operation                       | 5–2  |

| Figure 5–3.    | Serial Control Port Byte Register Read Operation                          | 5–3  |

| Figure 5–4.    | Serial Control Port Byte Register Read Operation Double 8–Bit Transaction | 5–4  |

| Figure 5–5.    | Serial Control Port Byte Register Write Operation                         | 5–4  |

| Figure 5–6.    | Serial Control Byte Register Write Operation Double 8–Bit Transaction     | 5–5  |

| Figure 5–7.    | Merged Serial Control Port Nibble Register Read Operation                 | 5–5  |

| Figure 6–1. a. | Relative Channel Positions (GCI Slave Mode)                               | 6–2  |

| Figure 6–1. b. | Relative Channel Positions (GCI Master Mode)                              | 6–3  |

| Figure 6–2.    | GCI Indirect Mode                                                         | 6–4  |

| Figure 6–3.    | Monitor Channel Access Protocol                                           | 6–9  |

| Figure 6–4.    | Activation from TE End                                                    | 6–14 |

| Figure 6–5.    | Deactivation from NT End                                                  | 6–15 |

| Figure 6–6.    | Activation from NT End                                                    | 6–15 |

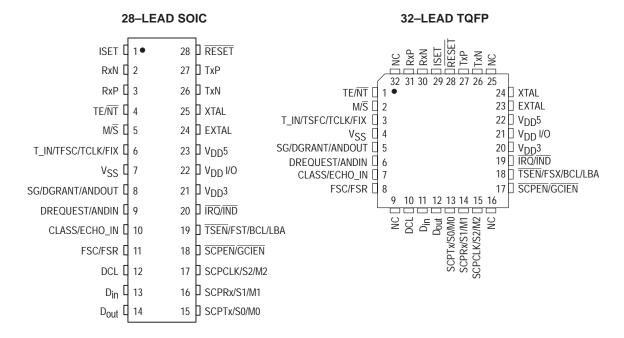

| Figure 7–1.    | Pin Assignments                                                           | 7–1  |

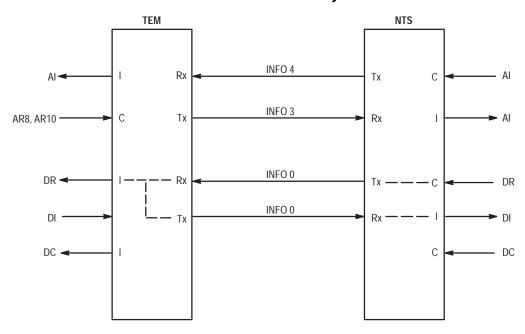

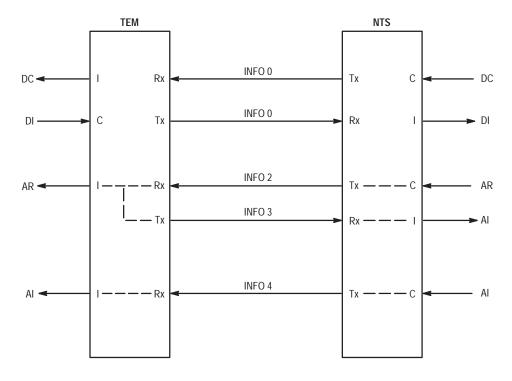

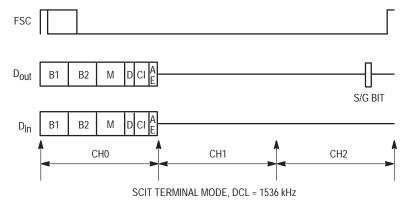

| Figure 11–1.   | SCIT Terminal Mode                                                        | 11–4 |

| Figure 13–1.   | NT Family Tree                                                            | 13–1 |

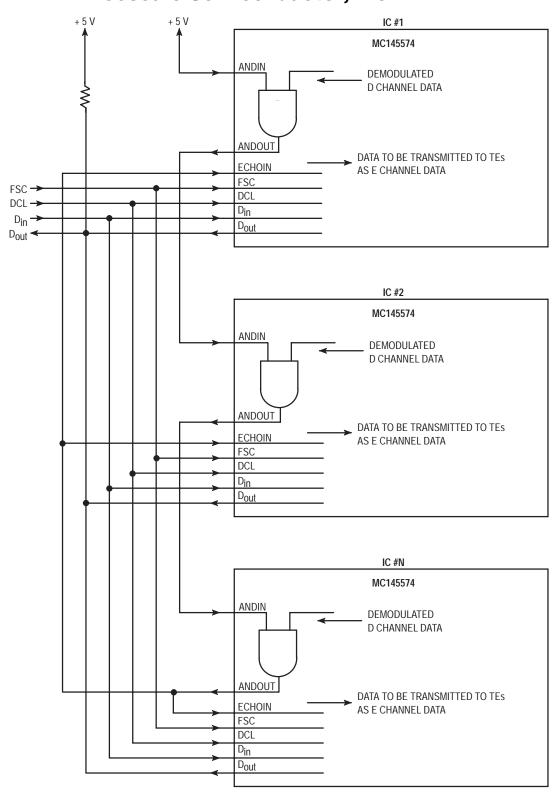

| Figure 13–2.   | NT1 Star Mode of Operation                                                | 13–3 |

| Figure 13–3.   | NT2 Architecture                                                          | 13–6 |

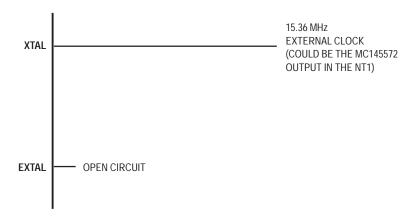

| Figure 14–1.   | Typical Crystal Oscillator Connection                                     | 14–1 |

| Figure 14–2.   | Connection with External Clock                                            | 14–1 |

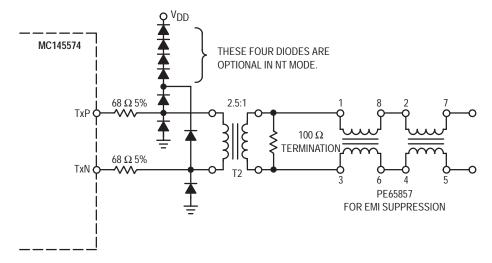

| Figure 16–1.   | Transmit Line Interface Circuit                                           | 16–2 |

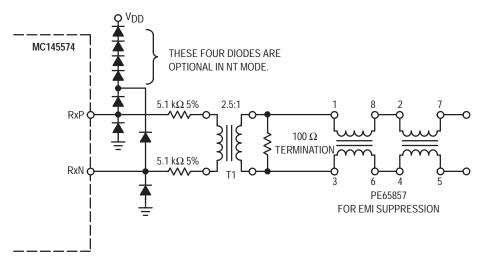

| Figure 16–2.   | Receive Line Interface Circuit                                            | 16–2 |

| Figure 18–1.   | IDL2 Master Timing, 8– and 10–Bit Formats                                 | 18–3 |

| Figure 18–2.   | IDL2 Slave Timing, 8– and 10–Bit Formats                                  | 18–5 |

| Figure 18–3.   | GCI Timing For Master and Slave Mode                                      | 18–7 |

| Figure 18–4.   | SCP Timing Characteristics                                                | 18–8 |

| Figure 18–5.   | NT1 Star Mode                                                             | 18–9 |

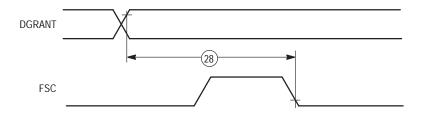

| Figure 18–6.   | D Channel Request Timing                                                  | 18–9 |

| Figure 18–7.   | D Channel Grant Timing                                                    | 18–9 |

| Figure 19–1.   | MC145574DW Pin Assignment (SOIC 28–Pin Package, Case 751F)                | 19–1 |

| Figure 19–2.   | MC145574PB Pin Assignment (TQFP 32–Pin Package, Case 873A)                | 19–1 |

| Figure A–1.    | Motorola Silicon Applications and the MC145574EVK                         | A-1  |

| Figure A–2.    | Block Diagram                                                             | A-3  |

|                |                                                                           |      |

# MC145574 LIST OF TABLES

| Table 3–1.  | NT Mode Transmission States                     | 3–1  |

|-------------|-------------------------------------------------|------|

| Table 3–2.  | TE Mode Transmission States                     | 3–1  |

| Table 4–1.  | IDL2 Clock Speeds                               | 4–2  |

| Table 6–1.  | CLK1, CLK0 GCI Clock Selection                  | 6–4  |

| Table 6–2.  | GCI Timeslot Assignment                         | 6–5  |

| Table 6–3.  | M2, M1, and M0 Pins in GCI NT Master Mode       | 6–6  |

| Table 6–4.  | M2, M1, and M0 Pins in GCI TE Master Mode       | 6–7  |

| Table 6–5.  | Monitor Channel Commands                        | 6–10 |

| Table 6–6.  | Monitor Channel Response Messages               | 6–10 |

| Table 6–7.  | Monitor Channel Status Indication Messages      | 6–10 |

| Table 6–8.  | C/I Channel Commands and Indications            | 6–13 |

| Table 6–9.  | GCI C/I Codes                                   | 6–13 |

| Table 8–1.  | SCP Nibble Register Map for NT Operation        | 8–1  |

| Table 8–2.  | SCP Nibble Register Map for TE Operation        | 8–1  |

| Table 8–3.  | Nibble Register Initialization After Any Reset  | 8–2  |

| Table 9–1.  | Byte Register Map for NT Mode of Operation      | 9–1  |

| Table 9–2.  | Byte Register Map for TE Mode of Operation      | 9–2  |

| Table 9–3.  | Byte Register Initialization After Any Reset    | 9–2  |

| Table 9–4.  | IDL2 Clock Speed Codes                          | 9–8  |

| Table 9–5.  | BR11(5), BR11(4) Rx INFO State Codes            | 9–11 |

| Table 9–6.  | BR11(3), BR11(2) Tx INFO State Codes            | 9–11 |

| Table 10–1. | Overlay Register Map                            | 10–1 |

| Table 10–2. | Overlay Register Initialization After Any Reset | 10–2 |

| Table 10–3. | S(2:0) GCI Timeslot Assignment                  | 10–3 |

| Table 10-4. | S(2:0) GCI Timeslot Assignment                  | 10–4 |

| Table 11–1. | Channel SCP Bit Description                     | 11–1 |

| Table 11–2. | D Channel Operation Pin Description             | 11–1 |

| Table 11–3. | MC145574 Class Operations                       | 11–2 |

| Table 12-1. | S Channel Data Transmission                     | 12–2 |

| Table 12–2. | Multiframe Interrupts                           | 12–2 |

| Table 12–3. | TE Multiframe Interrupts                        | 12–3 |

| Table 13–1. | Pin Operations                                  | 13–2 |

| Table 13-2. | Pin Operations for Master and Slave Modes       | 13–4 |

# 1 INTRODUCTION

#### 1.1 INTRODUCTION

The MC145574 is Motorola's second generation S/T transceiver and is a follow-up to the MC145474/75 transceiver.

The MC145574 provides the improved interfacing capabilities and reduced power consumption required by today's ISDN applications, while maintaining the functionality and extended range performance of the MC145474/75.

The MC145574 provides an economical VLSI layer 1 interface for the transportation of two 64 kbps B channels and one 16 kbps D channel between the network termination (NT) and terminal equipment applications (TEs). The MC145574 conforms to CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specifications.

The MC145574 provides the modulation/line drive and demodulation/line receive functions required of the interface. In addition, the MC145574 provides the activation/deactivation, error monitoring, framing, bit, and octet timing. The MC145574 provides the control signals for the interface to the layer 2 devices. Complete multiframe capability is provided.

The MC145574 features the interchip digital link (IDL2) for the exchange of the 2B+D channel information between ISDN components and systems. The MC145574 provides an industry standard serial control port (SCP) to program the operation of the transceiver. As an alternative to the IDL2+SCP combination, a general circuit interface (GCI) is provided.

The MC145574 is not pin compatible with the MC145474/75, but it does have a compatible register set. However, to make full use of the additional MC145574 features, software enhancements are required.

#### 1.2 ORGANIZATION OF DATA SHEET

This data sheet is comprised of 20 sections. Section 1 is an introduction, serving to outline the features, package types, and pin assignments of the MC145574. Section 2 describes the various wiring configurations which are applicable to the MC145574, and the operational distances as recommended by CCITT I.430, ETSI ETS 300012, and ANSI T1.605. Section 3 addresses the activation and deactivation procedures of the MC145574.

The MC145574 incorporates the IDL2. This is a four—wire interface used for full—duplex communication between ICs on the board level. Two 64 kbps B channels and one 16 kbps D channel are transmitted and received over this interface. Section 4 is a detailed description of the IDL2.

The MC145574 incorporates an SCP interface. The SCP is a four–wire interface conforming to an industry standard multi–drop serial link. The SCP is compatible with Motorola's serial peripheral interface (SPI). The SCP makes use of seven nibble registers, 16 byte registers and 10 overlay registers. Section 5 is a description of the SCP. A per bit description of the nibble, byte, and overlay registers is provided in Sections 8, 9, and 10, respectively. When the MC145574 is configured as a TE, it is equipped with five interrupt modes. When configured as an NT, it is equipped with four interrupt modes. Section 15 describes these interrupts.

The MC145574 also features a GCI interface. This is a standard four–wire interface which allows full–duplex transmission of two 64 kbps B channels and one 16 kbps D channel, multiplexed with control and maintenance information channels. Section 6 is a description of the GCI.

Section 7 contains pin descriptions of the MC145574. The pin descriptions differentiate between the device configured for NT mode or TE mode of operation, and GCI and IDL2+SCP.

As mentioned previously, the MC145574 is used for the transmission of two 64 kbps B channels and one 16 kbps D channel. Access to the B channels is determined by the network. The TEs gain access to the D channel in accordance with CCITT I.430, ETSI ETS 300012, and ANSI T1.605 recommendations. A description of the D channel operation is contained in Section 11.

In addition to the 2B+D channels, the S/T transceiver has a multiframing capability. Multiframing is a layer 1 signalling channel for use between the NT and the TE(s). The multiframing operation is described in Section 12.

The MC145574 can be configured in several different operating modes depending on the application. Section 13 describes all the possible configurations, whether in the NT or TE mode.

Section 16 describes how to interface the MC145574 to the S/T bus. Section 17 describes the various power modes of operation. Section 18 contains electrical specifications, and Section 19 contains mechanical data relevant to the MC145574. Section 20 describes the differences between this data book and the F57J4 mask version of the MC145574.

#### 1.3 FEATURES

The features of the MC145574 are described below.

- Conforms to CCITT I.430, ETSI ETS 300012, and ANSI T1.605 Specifications

- Register Compatible With the First Generation MC145474/75

- Exceeds Q.502 Jitter Requirements for TE Slave Applications

- Pin Selectable NT or TE Modes of Operation

- Incorporates the IDL2, With Timeslot Assigner

- Industry Standard Microprocessor SCP

- GCI Interface

- Uses 2.5:1 Transformers for Transmit and Receive

- Exceeds the Recommended Range of Operation in All Configurations

- Complete Multiframing Capability Supported (SC1 SC5 and Q Channel)

- · Optional B Channel Idle, Invert, or Exchange

- Supports Full Range of S/T and IDL2 Loopbacks

- Supports Transmit Power-Down, Listening, and Absolute Minimum Power Modes

- Supports Crystal or External Clock Input Mode

- NT Star and NT Terminal Modes Supported

- Low Power Consumption

- Compatible with 3 V Devices

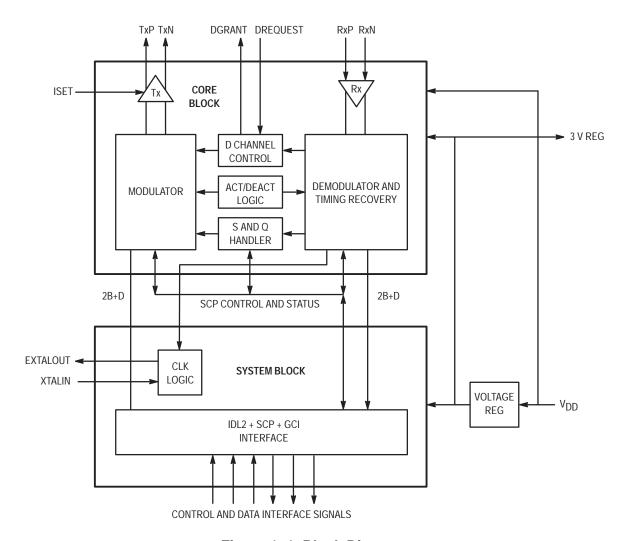

#### 1.4 BLOCK DIAGRAM

Figure 1–1. Block Diagram

#### 1.5 PACKAGING

The MC145574 comes in the following packages:

28-Pin, 600 mil Wide, Plastic SOIC 32-Pin, 700 mil Square, TQFP

The pin assignments for the MC145574 are described in Section 7. Package dimensions are in Section 19.

#### WIRING CONFIGURATIONS

#### 2.1 INTRODUCTION

The MC145574 ISDN S/T transceiver conforms to CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specifications. It is a layer 1 transceiver designed for use at the ISDN S and T reference points. It is designed for both point—to—point and multipoint operation. The S/T transceiver is designed for use in either the network terminating (NT) mode or in the terminal endpoint (TE) applications. Two 64 kpbs B channels and one 16 kbps D channel are transmitted in a full—duplex fashion across the interface.

Sections 2.2 through 2.6 contain suggested wiring configurations for use. These configurations are deemed to be the most common but by no means the only wiring configurations. Section 16 specifies the recommended circuitry for interfacing the MC145574 to the S/T bus. Note that when operating in the TE mode, only one TE has the 100  $\Omega$  termination resistors in the transmit and receive paths. Figures 2–1 through 2–4 illustrate where to connect the termination resistors for the described loop configurations.

A description of the most commonly used loop configurations is as described below.

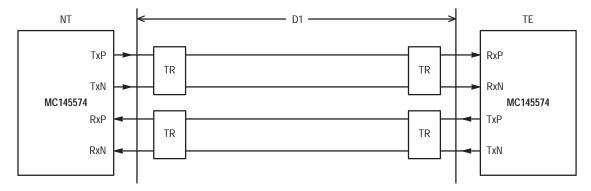

#### 2.2 POINT-TO-POINT OPERATION

In the point—to—point mode of operation, one NT communicates with one TE. As such,  $100~\Omega$  termination resistors must be connected across the transmit and receive paths of both the NT and TE transceivers. Figure 2–1 illustrates this wiring configuration.

When using the MC145574 in this configuration, the NT must be in adaptive timing. This is accomplished by holding the FIX pin low; i.e., connecting it to VSS. Refer to Section 6 for a more detailed description of this pin function. CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specify that the S/T transceiver must be able to operate up to a distance of 1 km in the point—to—point mode. This is the distance D1 as shown in Figure 2–1.

Figure 2–1. Point–to–Point

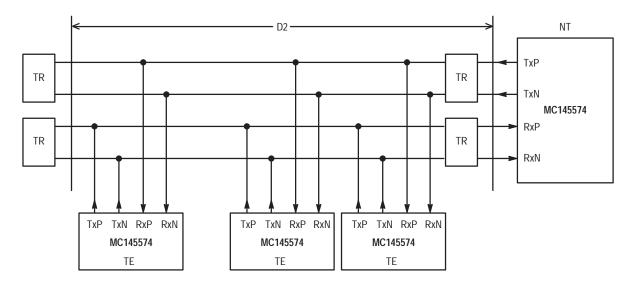

#### 2.3 SHORT PASSIVE BUS OPERATION

The short passive bus is intended for use when up to eight TEs are required to communicate with one NT. The TEs can be distributed at any point along the passive bus, the only requirement being that the termination resistors be located at the end of the passive bus. Figure 2–2 illustrates this wiring configuration. CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specify a maximum operational distance from the NT of 200 meters. This corresponds to the distance D2 as shown in Figure 2–2.

Figure 2-2. Short Passive Bus

#### 2.4 EXTENDED PASSIVE BUS OPERATION

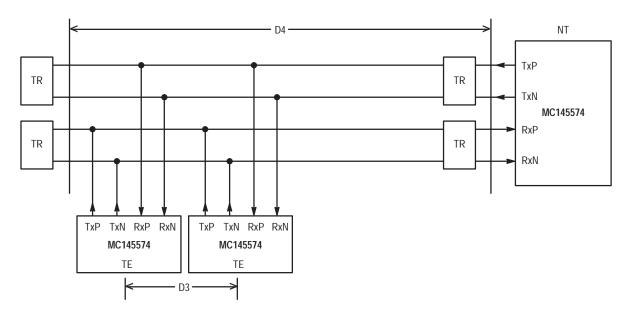

A wiring configuration whereby the TEs are restricted to a grouping at the far end of the cable, distant from the NT, is shown as the "Extended Passive Bus." This configuration is shown in Figure 2–3. The termination resistors are to be positioned as shown in Figure 2–3.

Figure 2–3. Extended Passive Bus

The essence of this configuration is that a restriction is placed on the distance between the TEs. The distance, D3 (as shown in Figure 2–3), corresponds to the maximum distance between the grouping of TEs. CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specify a distance of 25 – 50 meters for the separation between the TEs, and a distance of 500 meters for the total length. These distances correspond to the distances D3 and D4 as shown in Figure 2–3.

Note that the "NT configured" MC145574 should be placed in the adaptive timing mode for this configuration. This is achieved by holding the FIX pin low.

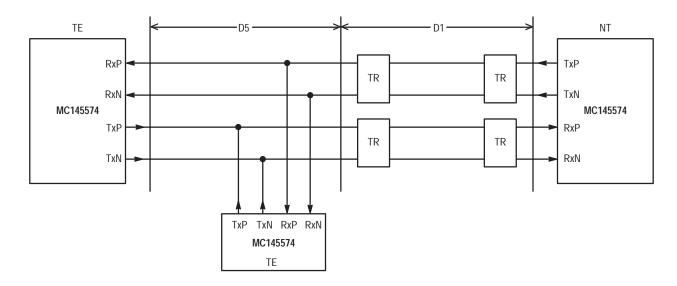

#### 2.5 BRANCHED PASSIVE BUS OPERATION

A wiring configuration which has somewhat similar characteristics to those of the "extended passive bus" is known as the "branched passive bus" and is shown in Figure 2–4. In this configuration the branching occurs at the end of the bus. The branching occurs after a distance D1 from the NT. The distance D5 corresponds to the maximum separation between the TEs.

Figure 2–4. Branched Passive Bus

#### 2.6 NT1 STAR MODE OF OPERATION

A wiring configuration which may be used to support multiple T interfaces is known as the "NT1 Star mode of operation." This mode of operation is supported by the MC145574. This mode is described in Section 11. Note that the NT1 Star mode contains multiple NTs. Each of these NTs can be connected to either a passive bus (short, extended, or branched) or to a single TE.

For More In**fo@mation** On This Product, Go to: www.freescale.com

# **ACTIVATION/DEACTIVATION OF S/T TRANSCEIVER**

#### 3.1 INTRODUCTION

CCITT I.430, ETSI ETS 300012, and ANSI T1.605 define five information states for the S/T transceiver. When the NT is in the fully operational state, it transmits INFO 4. When the TE is in the fully operational state, it transmits INFO 3. INFO 1 is transmitted by the TE when it wants to wake up the NT. INFO 2 is transmitted by the NT when it wants to wake up the TE, or in response to the TE's transmitted INFO 1. These states cause unique patterns of symbols to be transmitted over the S/T—interface. Only when the S/T loop is in the fully activated state are the 2B+D channels of data transmitted over the interface.

#### 3.2 TRANSMISSION STATES FOR NT MODE S/T TRANSCEIVER

When configured as an NT, an S/T transceiver can be in any of the following transmission states shown in Table 3–1.

Table 3-1. NT Mode Transmission States

| Information State | Description                                                                                                       |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------|--|

| INFO 0            | he NT transmits 1s in every bit position. This corresponds to no signal being transmitted.                        |  |

| INFO 2            | The NT sets its B1, B2, D, and E channels to 0. The A bit is set to 0. (See Sections 3.12.1 and 3.12.2.)          |  |

| INFO 4            | INFO 4 corresponds to frames containing operational data on the B1, B2, D, and E channels. The A bit is set to 1. |  |

#### 3.3 TRANSMISSION STATES FOR TE MODE S/T TRANSCEIVER

When configured as a TE, an S/T transceiver can be in any of the following transmission states shown in Table 3–2.

Table 3–2. TE Mode Transmission States

| Information State | Description                                                                                                                                                       |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| INFO 0            | The TE transmits 1s in every bit position. This corresponds to no signal being transmitted.                                                                       |  |

| INFO 1            | The TE transmits a continuous signal with the following pattern: positive 0, negative 0, six 1s. This signal is asynchronous to the NT.                           |  |

|                   | INFO 3 corresponds to frames containing operational data on the B1, B2, and D channels. If INFO 4 or INFO 2 is being received, INFO 3 will be synchronized to it. |  |

#### 3.4 ACTIVATION OF S/T LOOP BY NT

The NT activates the loop by transmitting INFO 2 to the TE(s). This is accomplished in the MC145574 by setting NR2(3) to a 1 (see Section 3.12.3). Note that this bit is internally reset to 0 after the internal activation state machine has recognized its active transition.

The TE on receiving INFO 2 synchronizes to it and transmits back INFO 3 to the NT. The NT, on receiving INFO 3 from the TE, responds with INFO 4, thus activating the loop.

#### 3.5 ACTIVATION OF S/T LOOP BY TE

The TE activates an inactive loop by transmitting INFO 1 to the NT. This is accomplished in the MC145574 by setting NR2(3) to a 1. Note that this bit is internally reset to 0 after the internal activation state machine has recognized its active transition.

The NT, upon detecting INFO 1 from the TE, responds with INFO 2. The TE, upon receiving a signal from the NT, ceases transmission of INFO 1, reverting to transmitting INFO 0. After synchronizing to the received signal and having fully verified that it is INFO 2, the TE responds with INFO 3, thus activating the loop.

#### 3.6 ACTIVATION PROCEDURES IGNORED

The MC145574 has the capability of being forced into the highest transmission state. This is accomplished by setting BR7(7) to a 1. Thus when this bit is set in the NT, it forces the NT to transmit INFO 4. Correspondingly, in the TE, setting this bit to 1 forces the TE to transmit INFO 3.

Note that CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specifications allow a TE to be activated by reception of INFO 4, without having to go through the intermediate handshaking. This is to allow for the situation where a TE is connected to an already active loop.

However, an NT can not be activated by a TE sending it INFO 3, without going through the intermediate INFO 1, INFO 2, INFO 3, and INFO 4 states.

This "Activation Procedures Ignored" feature is provided for test purposes, allowing the NT to forcibly activate the TE(s). In the TE, the forced transmission of INFO 3 enables verification of the TEs operation.

#### 3.7 FRAME SYNC

#### 3.7.1 NT Mode

When the S/T transceiver in the NT mode is receiving INFO 3 from the TE(s) and has achieved frame synchronization, it sets the FSYNC status bit NR1(0) high.

#### 3.7.2 **TE Mode**

When the TE is receiving either INFO 2 or INFO 4 from the NT, and has achieved frame synchronization, the MC145574 internally sets the SCP nibble bit, NR1(0). NR1(0) performs this function in both the NT and TE modes, for the MC145574.

#### 3.8 ACTIVATION INDICATION

NR1(3), the activation indication bit, is used to signify that the loop is fully active. When the MC145574 is configured as an NT, this corresponds to the NT transmitting INFO 4 and receiving INFO 3. When the MC145574 is configured as a TE, this corresponds to it transmitting INFO 3 and receiving INFO 4. When the loop is in the fully active state, NR1(3) is internally set high.

#### 3.9 NR1(2) — ERROR INDICATION (EI)

NR1(2) is set by the MC145574 S/T transceiver to indicate an error condition has been detected by the activation state machine of the transceiver, as outlined in CCITT I.430, ETSI ETS 300012, and ANSI T1.605. The low-to-high level transition of the EI bit corresponds to the EI1 error indication reporting, while the high-to-low level transition of the EI bit corresponds to the EI2 error indication reporting recovery. Note that NR1(2) is a read only bit.

#### 3.10 DEACTIVATION PROCEDURES

CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specifications dictate that only an NT can deactivate the S/T loop. Intuitively, this has to be the case because in a passive bus if one TE sends INFO 0, seeking to deactivate the loop, the other TE's INFO 3 simply overrides it.

An NT transmits INFO 0 to the TE(s) when it wishes to deactivate the S/T loop. This is done by setting NR2(2) (Deactivation Request) to a 1. Note that this bit is internally reset to 0 after the internal activation state machine has recognized its active transition.

#### 3.11 INITIAL STATE OF B1 AND B2 CHANNELS

#### 3.11.1 NT

When the MC145574 is configured as an NT, NR5(3:2) corresponds to "IDLE B1 channel on S/T loop", and "IDLE B2 channel on S/T loop", respectively. The device comes out of a hardware or software reset with these two bits reset to 0. Thus, the NT comes out of reset with the B1 and B2 channels enabled. When the NT is transmitting INFO 4, data on the B1 and B2 IDL2 timeslots will be modulated onto the S/T loop. Setting either of these nibble bits in the NT mode will idle the corresponding B channel on the S/T loop. Note that putting a B channel in the idle mode affects only the transmitted B channel. The demodulated B data is still transmitted out on IDL2 Tx, in accordance with the IDL2 specification.

#### 3.11.2 TE

When the MC145574 is configured as a TE, NR5(3:2) corresponds to "ENABLE B1 channel on S/T loop," and "ENABLE B2 channel on S/T loop," respectively. The device comes out of a hardware or software reset with these two bits reset to 0. Thus, the TE comes out of reset with the B1 and B2 channels disabled. When the TE is transmitting INFO 3, data on the B1 and B2 IDL2 timeslots is not modulated onto the S/T loop. Setting either of these bits enables the modulation of the corresponding B channel onto the S/T loop.

Note that although the TE comes out of reset with both B channels in the idle mode, this only affects the modulation path. Demodulated data is still transmitted on  $D_{OUT}$ .

#### 3.12 ADDITIONAL NOTES

#### 3.12.1 M and N Parameters

For conformance qualification procedures, it is often necessary to state the values of M and N, where:

M is the number of successive good S0 frames for frame synchronization, and N is the number of successive bad S0 frames for frame loss.

For the MC145574, M = 5 and N = 3.

#### 3.12.2 Echo Channel

The NT demodulates the 2B+D data received from the TE(s). In addition to passing this data onto the network, the NT echoes the D channel data back to the TE(s) using the echo channel. This echo channel is monitored by the TEs and used in the D channel contention algorithm. For a detailed description, refer to Section 11.

#### 3.12.3 A Bit

An S/T frame consists of 48 bauds. In the NT to TE direction, one of these bauds is for the A bit. The A bit is set to 1 when the S/T loop is in the fully activated state and is set to 0 at all other times. Thus, when the NT is transmitting INFO 2, the A bit is set to 0. When the NT is transmitting INFO 4, the A bit is set to 1.

#### 3.12.4 SCP Nomenclature

There are seven nibble registers, 16 byte registers, and 10 overlay registers in the MC145574. These registers are accessed by means of the SCP. NR1(2) refers to nibble register 1, bit 2. Likewise, BR3(4) refers to byte register 3, bit 4, and OR5(6) refers to overlay register 5, bit 6.

The overlay registers are a second bank of registers available when the overlay register control bit BR15(7) is set to logic 1.

#### 3.12.5 SCP Indication of Transmit and Receive States

Note that there are two SCP bits, BR11(5:4), used to signify what INFO state the MC145574 is receiving. In addition to this, BR11(3:2) are used to signify what INFO state the MC145574 is transmitting. Refer to Tables 9–2 and 9–3 for a detailed description of these bits.

#### THE INTERCHIP DIGITAL LINK

#### 4.1 INTRODUCTION

The Interchip Digital Link (IDL2) of the MC145574 is backwards compatible with the IDL of the MC145474/75 S/T transceiver of first generation. In addition to the standard operating mode, this enhanced interface features new modes that are programmable through the SCP.

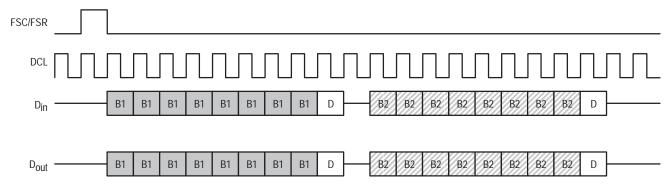

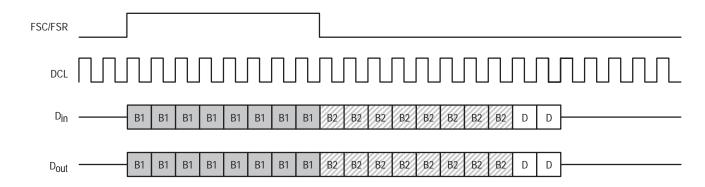

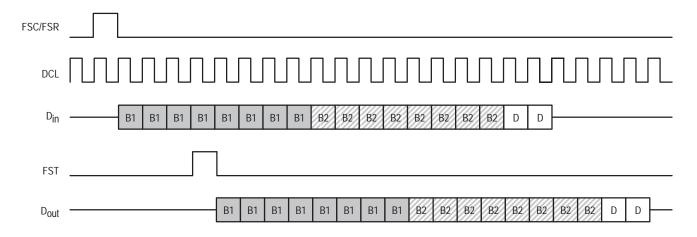

The IDL2 is a four–wire interface used for full–duplex communication between ICs on the board level. The interface consists of a transmit path, a receive path, an associated clock, and a sync signal. These signals are known as D<sub>out</sub>, D<sub>in</sub>, DCL, and FSC, respectively. The clock determines the rate of exchange of data in both the transmit and receive directions, and the sync signal controls when this exchange is to take place. Three channels of data are exchanged every 8 kHz. These channels consist of two 64 kbps B channels and one 16 kbps D channel used for full–duplex communication between the NT and TE.

There are two modes of operation for an IDL2 device: IDL2 master and IDL2 slave. If an IDL2 device is configured as an IDL2 master, then FSC and DCL are outputs from the device. Conversely, if an IDL2 device is configured as an IDL2 slave, then FSC and DCL are inputs to the device. Ordinarily the MC145574 should be configured as an IDL2 slave when acting as an NT, and as an IDL2 master when acting as a TE. The exception to this rule is the option to configure the NT as an IDL2 master. The TE configured MC145574 also features the new option of operating in the IDL2 slave mode. These operation modes are described in Section 4.3.

#### 4.2 SIGNAL DESCRIPTION

There are six pins associated with the IDL2 interface.

#### FSC/FSR

This pin is normally FSC and is an input/output pin to which all serial interface events are synchronized. This pin is periodic at 8 kHz. In the master mode, the pin is an output and is either derived from the S/T frame or from the XTAL. In the slave mode, this pin is an input.

FSC can be reconfigured through the SCP to be FSR. In this mode, the IDL2 operates with two independent frame syncs, one for the Tx direction (FST) and one for the Rx direction (FSR). FSR is bidirectional, the direction depending on whether the IDL2 is a master or a slave. See Register OR7 description.

#### **DCL**

This is an input/output pin that provides the clock to the serial interface. In the master mode, this pin is an output. In the slave mode, this pin is an input. The clock is continuous and the edges are synchronous with the frame sync.

When DCL is an output, the clock rate can be programmed through the SCP to be 2.56 MHz, 2.048 MHz, 1.536 MHz, or 512 kHz. When DCL is an input, the clock rate can be between 512 kHz and 4096 kHz (DCL should be a multiple of FSC.) Selection of the clock frequency is accomplished in the same manner as used in MC145474, through the bits BR7(2) and BR13(5). See Table 4–1 for IDL2 clock speeds.

Table 4-1. IDL2 Clock Speeds

| BR13(5) | BR7(2) | DCL       |

|---------|--------|-----------|

| 0       | 0      | 2.56 MHz  |

| 0       | 1      | 2.048 MHz |

| 1       | 0      | 1.536 MHz |

| 1       | 1      | 512 kHz   |

#### Din

This pin is always an input. Data to be output on the S/T-interface is input on this pin.

#### Dout

This pin is a three–state output. Data received on the S/T–interface is output on this pin during programmed timeslots and is high impedance at all other times.

#### TSEN/FST

This pin is normally three–state, but it can be reconfigured through the SCP to be used as TSEN or FST. See Register OR7 description.

TSEN is an open drain output. TSEN can be used to enable an external bus driver and pulses low when data is being output on the D<sub>Out</sub> pin. This signal can be used to control a high drive bus/backplane driver in applications where the D<sub>Out</sub> data is going off–board. Since TSEN is open drain, it can be wire–OR'd with other devices and share the same driver.

This pin can also be reconfigured through the SCP to be used as FST. In this mode, the IDL2 interface operates with two independent frame syncs, one for the Tx direction (FST) and one for the Rx direction (FSR). FST is bidirectional, the direction depending on whether the IDL2 is a master or a slave.

#### TFSC/TCLK/T IN/FIX

This pin is the FIX input in NT modes, but in the TE slave mode it is reconfigured to be used as TFSC and outputs an 8 kHz signal that is synchronized to the incoming S/T-interface frames. The TFSC can be used in NT2 applications where the TE slave mode is utilized. The TFSC can be used to synchronize the TE slaves to the network. Alternatively, this pin can output TCLK, selected via the SCP. TCLK is a clock whose frequency can be chosen via the SCP, which is also synchronized to the received S/T-interface. TCLK can be used as an alternative to TFSC in the NT2 slave—slave mode. Refer to the slave—slave mode section for further details on TFSC and TCLK. See Register OR7 description.

In the NT Terminal mode (NTTERM), this pin is T\_IN. See the section on NT Terminal mode. See description for Register OR8.

#### 4.3 IDL2 STANDARD MODE

#### 4.3.1 NT IDL2 Slave

This is the normal mode of operation for the MC145574, when active as an NT. In this mode FSC and DCL are inputs to the device, and the outgoing S/T frame is synchronized to the IDL2 frame sync. Typically the MC145574, when configured as an NT, is situated on a line card or an NT1 box. As an IDL2 slave, this allows the S/T chip to derive its timing from the backplane or from the MC14LC5472/MC145572 U–chips. As mentioned previously, FSC must be 8 kHz, while DCL can be input to the device with any frequency from 512 kHz to 4.096 MHz.

When the MC145574 is configured as an NT, then BR7(3) determines whether the NT is acting as an IDL2 master or as an IDL2 slave. When BR7(3) is a 0, the MC145574, when acting as an NT, is behaving as an IDL2 slave. Conversely, when BR7(3) or OR8(3) is set to a 1, or when pulling high the  $M/\overline{S}$  pin, the chip acting as an NT behaves as an IDL2 timing master.

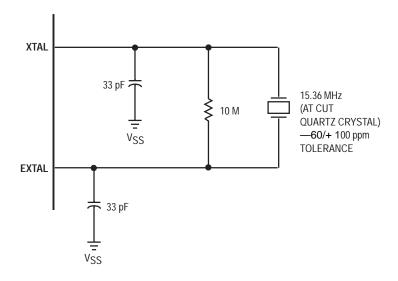

#### 4.3.2 NT IDL2 Master

As mentioned previously, the normal configuration for the MC145574, when configured as an NT, is as an IDL2 slave. However, in order to facilitate testing of the environment in which the MC145574 resides, the capability exists to configure the chip as an NT IDL2 master. In this mode of operation, the chip outputs FSC and DCL. These signals are divided down from the 15.36 MHz crystal input XTALIN and hence are synchronous with it. The NT IDL2 master mode also finds use in testing PC-based local area networks or in passive bus configurations. In these environments, it may be required to configure one of the TEs to act as an NT. The NT IDL2 master enables the user to do this. Writing a 1 to BR7(3) or OR8(3), or pulling high the M/S pin, puts the NT into the IDL2 master mode. Note that a software or a hardware reset reconfigures the NT as an IDL2 slave.

When the MC145574 is acting as an NT IDL2 master, the DCL can be programmed to output one of four frequencies. The DCL rate is determined by BR7(2) and BR13(5). In the NT IDL2 master mode, the DCL is obtained by dividing down from the 15.36 MHz crystal. Application of a software or a hardware reset will reset BR7(2) and BR13(5) to 0. Note that these bits have no application when the MC145574 is an NT IDL2 slave.

#### 4.3.3 TE IDL2 Master

This is the normal mode of operation for the MC145574 when active as an NT. In this mode, the MC145574 derives its timing from the inbound data from the NT. When the TE is receiving either INFO 2 or INFO 4 from the NT, it adaptively phase–locks onto it. The TE sets the FSYNC bit (NR1(0)) high when this frame synchronization has been achieved. When this occurs, the TE outputs FSC, DCL, and D<sub>out</sub> synchronous with the inbound INFO 2 or INFO 4. If the TE is receiving INFO 2, it outputs "idle 1s" on D<sub>out</sub> in the B1, B2, and D channel timeslots. If the TE is receiving INFO 4, it outputs valid data in these timeslots.

Note that when the TE has reached its fully active state, it internally sets the activate indication bit (NR1(3)). (The active state for a TE is when it is receiving INFO 4 from the NT, has phase–locked onto it, and is transmitting back INFO 3 to the NT.) In the TE IDL2 master mode, BR7(2) and BR7(3) determine the output DCL rate. See description of BR7 bits 1 and 2 in Section 9.9.

#### 4.3.4 TE IDL2 Master Free Run

The capability exists in the MC145574 to configure the chip as a TE operating in the IDL2 master free run mode. This is done by setting BR7(3) to a 1. In this mode, the TE sends out a DCL and FSC regardless of the state of the frame synchronization bit (NR1(0)). If NR1(0) is low, then FSC and DCL are derived from the crystal in the same way as in the NT IDL2 master mode. Upon achieving frame synchronization (i.e., the TE is receiving either INFO 2 or INFO 4 from the NT, has phase–locked onto it, and has set NR1(0)), FSC and DCL will become synchronous to the inbound INFO 2 or INFO 4 from the NT. The TE IDL2 master mode has the capability of providing four clock rates: 2.56 MHz, 2.048 MHz, 1.536 MHz, and 512 kHz.

#### 4.3.5 TE IDL2 Slave

The TE slave—slave mode should be selected when the device is to be used on the T-interface of an NT2. In this mode, the IDL2 is in the slave mode, and D channel data is continuously transmitted/received to/from the T-interface. The D channel access algorithm is disabled in this mode.

In this mode, the frame sync and serial clock are inputs. The IDL2 circuitry incorporates buffering to accommodate any phase relationship between the frame sync and the received S/T frame. The buffering is able to absorb low–frequency wander between the IDL2 frame sync and the S/T frame. The wander absorption capability exceeds the requirement of Q.502, which defines wander as 18  $\mu$ s peak–to–peak at frequencies below 10 Hz over a 24–hour period.

#### 4.3.6 Additional Notes

#### 4.3.6.1 Phase Relationship of the NT Transmit Signal with Respect to FSC/FSR

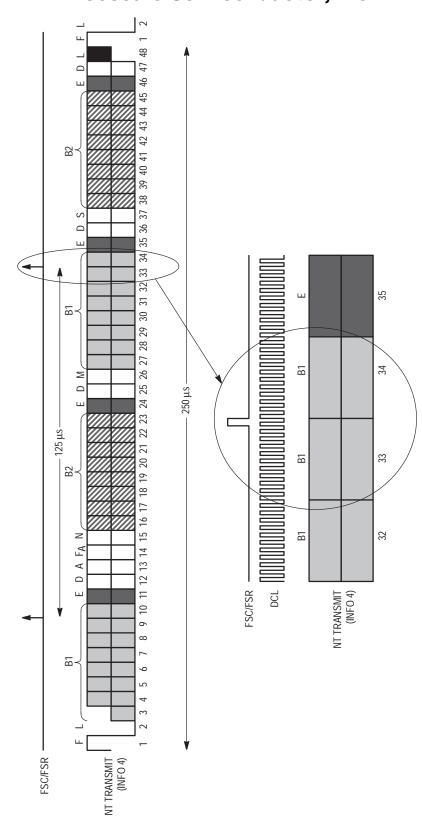

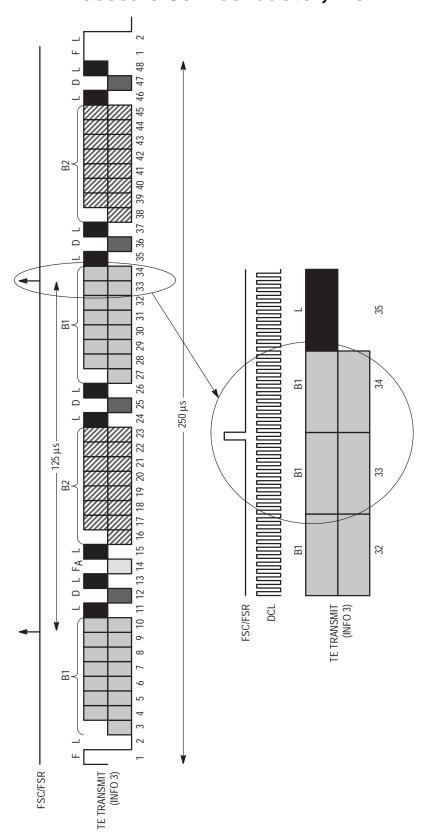

The MC145574 operating as an NT behaves as an IDL2 slave, FSC/FSR and DCL being inputs to the device. FSC/FSR is a single positive polarity pulse, one DCL cycle in duration, and is periodic at an 8 kHz rate. The MC145574 operating as an NT uses FSC/FSR to correctly position its outbound waveform. Thus, the FSC/FSR input to the NT and the NT's outbound INFO 2 or INFO 4 are synchronous. The phase relationship of these signals is shown in Figure 4–1 with a "close–up shot" included.

# 4.3.6.2 Phase Relationship of the TE Transmit Signal with Respect to FSC/FSR, When in the IDL2 Master Mode

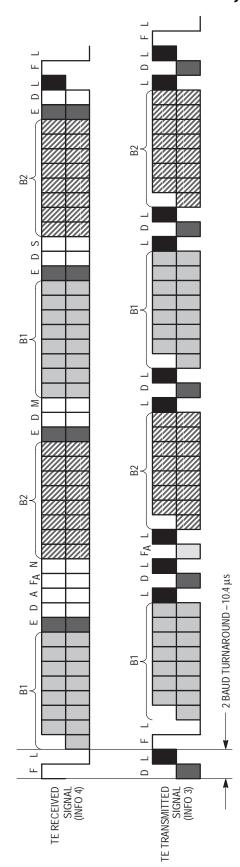

The MC145574 operating as a TE behaves as an IDL2 master; FSC/FSR and DCL are outputs from the device. The TE derives its timing from the inbound INFO 2 or INFO 4 from the NT. There is a two–baud turnaround in the TE in accordance with CCITT I.430, ETSI ETS 300012, and ANSI T1.605 specifications; i.e., the time between the TE's received "F bit" and its transmitted "F bit" is equivalent to two bauds. This is indicated in Figure 4–2. The TE outputs FSC/FSR, DCL, and Dout when it has achieved frame synchronization. The phase relationship of the TE's transmitted INFO 3 and FSC/FSR is as shown in Figure 4–3 with a "close–up shot" included.

#### 4.3.6.3 Operation of Multiple MC145574s in TE Slave Mode

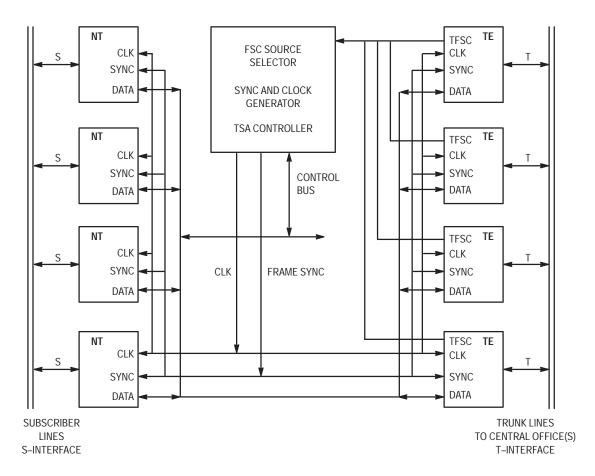

When the MC145574 is configured for TE slave mode in NT2 applications, the T\_IN/TFSC/TCLK/FIX pin defaults to the TFSC function. As TFSC, this pin outputs an 8 kHz frame sync that is synchronized to recovered timing from the network.

In TE slave mode, the T\_IN/TFSC/TCLK/FIX pin function can be changed to TCLK, which outputs a network synchronized high frequency clock. This is done by setting OR7(5) to a 1. The clock frequency of TCLK is selected in the same manner as programming the DCL clock in IDL2 master mode.

Elastic buffers are included in TE slave mode to allow the MC145574 to operate with any phase relationship between the IDL2 frame sync and the network. This buffer also allows the frame sync to wander with respect to the network, up to  $60 \,\mu s$  peak—to—peak. This exceeds the requirements of Q.502, which states that wander up to  $18 \,\mu s$  peak—to—peak may arise over a 24—hour period.

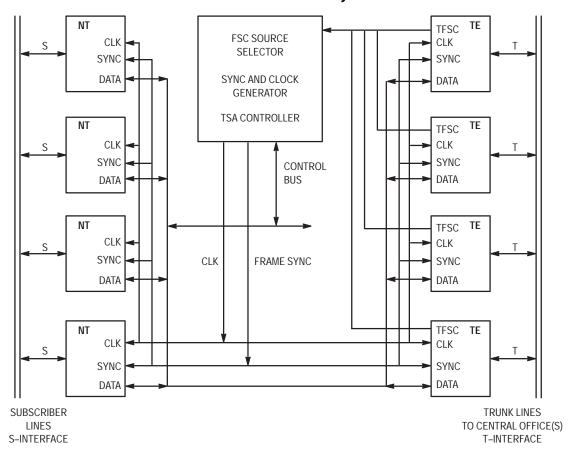

An example architecture of an NT2 is shown in Figure 4–4. The TFSC or TCLK signal supplied by the TE is used to synchronize the entire NT2 to the network. The TFSC/TCLK pins can be wire OR'd together and connected to VDD via a pull–up resistor. Each TE looks at the TFSC/TCLK pin during its programmed B1 channel timeslot. If there is no signal present and the TE is activated, it outputs a synchronized signal on TFSC/TCLK. It is important for all TEs to have their B and D channels configured using the timeslot assigner, and no two devices can share a timeslot.

#### 4.3.6.4 Independent Tx/Rx Frame Syncs

Via the SCP, two pins (FST and FSR) are available to handle the transmit and receive frames independently on the IDL2 interface. These pins must operate synchronously with the DCL clock. Operation of FST and FSR is dependent on the master or slave mode. Separate frame syncs are enabled by setting OR7(4) to a 1.

In the slave mode, FST and FSR may assume any relationship with respect to each other.

In the master mode, both FST and FSR are operational and locked together in time. Long frame format can not be used with independent Tx/Rx frame syncs.

#### 4.3.6.5 Timeslot Assignment

The MC145574 contains a timeslot assigner. The timeslot immediately following the FSC/FSR/FST signal is timeslot zero. Timeslots are available up to the maximum DCL rate of 4096 kHz. The timeslots are programmed through a group of control registers in the overlay register map. Up to 256 start times may be defined, corresponding to each 2–bit boundary defined by DCL.

Figure 4–1. Phase Relationship of NT Transmit Signal

Figure 4-2. Two-Baud Turnaround in TE

Figure 4-3. Phase Relationship of TE Transmit Signal

Figure 4–4. Example Architecture of an NT2

Independent timeslot assignment is available for the B1, B2, and D channels in both the transmit and receive directions. B1, B2, and D timeslots may be enabled separately. When a timeslot is enabled, the IDL2 automatically enters timeslot mode. If any one channel's timeslot is not enabled, data transmitted by the framer for that channel will be filled with all ones, and the channel will not be present on D<sub>Out</sub>.

With a DCL rate of 4096 kHz, it is possible to allocate 1 of 256 possible timeslots to each data channel. It is important that the software selects a timeslot consistent with the DCL rate. When a clock rate of 2048 kHz is being used, only 128 timeslots are available. If a timeslot out with the available range is chosen, then no data transfer occurs for that timeslot.

The default values assigned to the B1, B2, and D channels are 00H, 04H, and 08H. These values provide an IDL2 8-bit output format as default.

The IDL2 10-bit mode is not available when the timeslot assigner has been enabled.

#### **CAUTION**

Do not program overlapping timeslots even if a timeslot has not been enabled. The transmit and receive timeslot for a given B1, B2, or D channel can be the same.

#### 4.3.6.6 Short and Long Framing

In master timing mode, the default state is to supply a one–clock–wide FSC/FSR/FST frame sync. However, an option is provided to change this to long frame. The length of the long frame pulse is always 8–bit clocks, regardless of whether an 8– or 10–bit format is selected. In the slave mode, the MC145574 will automatically adjust to whichever framing method is supplied. If the frame sync is two or more clocks wide, the MC145574 assumes a long frame format.

A long frame format cannot be used in timeslot assignment mode.

#### 4.3.6.7 TSEN Signal

The TSEN signal is enabled via the SCP. See description for OR7 bits 1 and 0. This pin then becomes an open drain output that pulls low when data is being output from D<sub>OUt</sub>. This signal can then be used to enable an external driver in applications where the IDL2 data goes off–board, such as PBXs, channel banks, etc.

#### 4.3.6.8 Miscellaneous

#### **Clock Options**

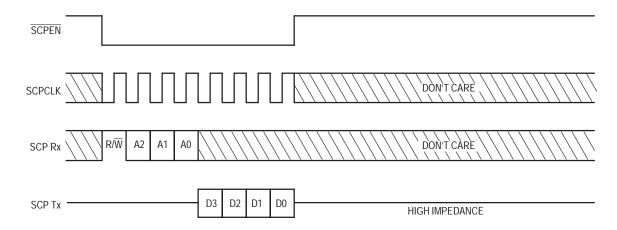

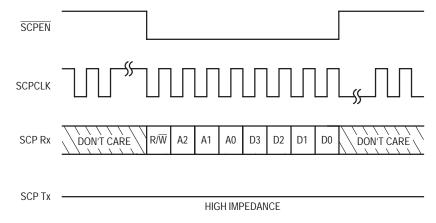

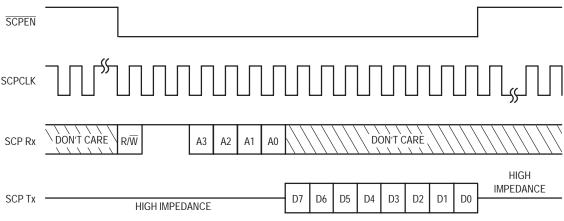

In the slave mode, the IDL2 interface accepts any clock from 512 kHz to 4096 kHz in 8 kHz increments.