# KSZ8842-PMQL/PMBL

#### 2-Port Ethernet Switch with PCI Interface

Rev.1.5

# **General Description**

The KSZ8842-series of 2-port switches includes PCI and non-PCI CPU interfaces. This datasheet describes the KSZ8842-PMQL/PMBL PCI CPU interface chips. KSZ8842-PMQL is PQFP package chip, KSZ8842-PMBL is LFBGA package chip. For information on the KSZ8842-MQL/MBL CPU non-PCI interface switches, refer to the KSZ8842-MQL/MBL datasheet.

The KSZ8842-PMQL/PMBL is the industry's first fully managed 2-port switch with a 32 bit/33MHz PCI processor interface. It is a proven, 4th generation, integrated Layer 2 switch that is compliant with the IEEE 802.3u standard. An industrial temperature grade version of the KSZ8842-PMQL/PMBL, also can be ordered the KSZ8842-PMQLI/PMBL AM.

The KSZ8842-PMQL/PMBL can be configured as a switch or as a low-latency (<310 nanoseconds) repeater in latency-critical, embedded or industrial Ethernet applications. For industrial automation applications, the

KSZ8842-PMQL/PMBL can run in half-duplex mode regardless of the application. The KSZ8842-PMQL/PMBL offers an extensive feature set that includes tag/port-based VLAN, quality of service (QoS) priority management, management information base (MIB) counters, and CPU control/data interfaces to effectively address Fast Ethernet applications.

The KSZ8842-PMQL/PMBL contains two 10/100 transceivers with patented, mixed-signal, low-power technology three media access control (MAC) units, a direct memory access (DMA) channel, a high-speed, non-blocking, switch fabric, a dedicated 1K entry forwarding table, and an on-chip frame buffer memory.

Datasheets and support documentation can be found on Micrel's web site at: <a href="https://www.micrel.com">www.micrel.com</a>.

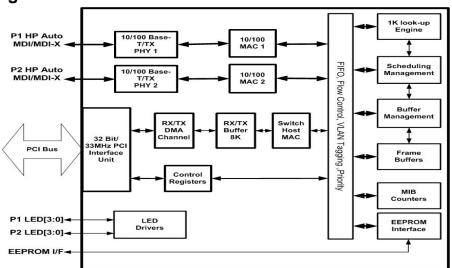

# **Functional Diagram**

Figure 1. KSZ8842-PMQL/PMBL Functional Diagram

LinkMD is a registered trademark of Micrel, Inc Magic Packet is a trademark of Advanced Micro Devices, Inc.

Product/Application names used in this datasheet are for identification purposes only and may be trademarks of their respective companies.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

October 2007 M9999-100207-1.5

### **Features**

# **Switch Management**

- Non-blocking switch fabric assures fast packet delivery by utilizing a 1K entry MAC Address look-up engine and a store-and-forward architecture

- Fully compliant with IEEE802.3u standards

- Full-duplex IEEE 802.3x flow control (Pause) with force mode option

- Half-duplex back pressure flow control

# **Advanced Switch Management**

- IEEE 802.1Q VLAN support for up to 16 groups (fullrange of VLAN IDs)

- VLAN ID tag/untag options, per port basis

- IEEE 802.1p/Q tag insertion or removal on a per-port basis (egress)

- Programmable rate limiting at the ingress and egress port

- Broadcast storm protection

- IEEE 802.1d spanning tree protocol support

- MAC filtering function to filter unicast packets

- Unknown MAC address forwarding function

- Direct forwarding mode enabling the processor to identify the ingress port and to specify the egress port

- IGMP v1/v2 snooping support for multicast packet filtering

- IPV6 Multicast Listener Discovery (MLD) snooping support

## Monitoring

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic to any port

- Management information base (MIB) counters for fully compliant statistics gathering: 32 MIB counters per port

- Loop back modes for remote failure diagnostics

# **Comprehensive Register Access**

- There are three kinds of register groups:

- The PCI configuration registers are used to initialize and configure the PCI interface

- The PCI control/status registers are used to communicate between the host and KSZ8842-PMQL/PMBL

- Switch registers are used to support transceiver control and status. They are configurable on-the-fly (portpriority, 802.1p/d/Q, etc.)

### **QoS/CoS Packets Prioritization Support**

- Per port, 802.1p and DiffServ based

- Re-mapping of 802.1p priority field on a per port basis

# Power Modes, Packaging, and Power Supplies

- Full-chip hardware power-down (register configuration not saved) provides for low power dissipation

- Per port-based software power-save on PHY (idle link detection, register configuration preserved)

- Single power supply: 3.3V

- Commercial Temperature Range: 0°C to +70°C

- Industrial Temperature Range: -40°C to +85°C

- Available in 128-pin PQFP and 100-ball LFBGA

# **Additional Features**

In addition to offering all of the features of an integrated Layer-2 managed switch, the KSZ8842-PMQL/PMBL offers:

- Repeater mode capabilities to allow for cut through in latency critical Industrial Ethernet or Embedded Ethernet applications

- Dynamic buffer memory scheme essential for applications such as Video over IP where image jitter is unacceptable

- 2-Port switch with a 32-bit/33MHz PCI processor interface.

- Micrel LinkMD<sup>®</sup> cable diagnostics to determine cable length, diagnose faulty cables, and determine distanceto-fault

- Hewlett Packard (HP) Auto MDI-X crossover with disable and enable options

- Four priority queues to handle voice, video, data, and control packets

- Ability to transmit and receive jumbo frame sizes up to 1916 bytes

# **Applications**

- Video Distribution Systems

- High-end Cable, Satellite, and IP set-top boxes

- Video over IP

- Voice over IP (VoIP) and Analog Telephone Adapters (ATA)

- Industrial Control in Latency Critical Applications

- Motion Control

- Industrial Control Sensor Devices (Temperature, Pressure, Levels, and Valves)

- Security and Surveillance Cameras

# **Markets**

- Fast Ethernet

- Embedded Ethernet

- Industrial Ethernet

# **Ordering Information**

| Part Number                   | Operation<br>Temp. Range | Package        |

|-------------------------------|--------------------------|----------------|

| KSZ8842-PMQL                  | 0°C to 70°C              | 128-Pin PQFP   |

| KSZ8842-PMQLI                 | -40°C to +85°C           | 128-Pin PQFP   |

| (Industrial grade)            |                          |                |

| KSZ8842-PMBL                  | 0°C to 70°C              | 100-Ball LFBGA |

| KSZ8842-PMBL AM               | -40°C to +85°C           | 100-Ball LFBGA |

| (Industrial/Automotive grade) |                          |                |

# **Revision History**

| Revision | Date     | Summary of Changes                                                                        |  |

|----------|----------|-------------------------------------------------------------------------------------------|--|

| 1.0      | 09/29/05 | Data sheet created.                                                                       |  |

| 1.1      | 01/13/06 | Package information updated.                                                              |  |

| 1.2      | 01/16/07 | Update support transformer, table and other.                                              |  |

| 1.3      | 04/17/07 | Add the base address and range for host MIB, change description for soft reset and other. |  |

| 1.4      | 06/01/07 | Add the package thermal information in the operating ratings.                             |  |

| 1.5      | 10/02/07 | Add the KSZ8842-PMBL BGA device information.                                              |  |

# **Contents**

| Pin Configuration                                     | 9  |

|-------------------------------------------------------|----|

| Pins Description of KSZ8842-PMQL                      | 11 |

| Functional Description                                | 20 |

| Functional Overview: PCI Bus Interface Unit           |    |

| PCI Bus Interface                                     | 20 |

| TXDMA Logic and TX Buffer Manager                     | 20 |

| RXDMA Logic and RX Buffer Manager                     |    |

| Functional Overview: Physical Layer Transceiver (PHY) | 20 |

| 100BASE-TX Transmit                                   |    |

| 100BASE-TX Receive                                    |    |

| PLL Clock Synthesizer (Recovery)                      |    |

| Scrambler/De-scrambler (100BASE-TX Only)              |    |

| 10BASE-T Transmit                                     |    |

| 10BASE-T Receive                                      |    |

| Power Management                                      |    |

| MDI/MDI-X Auto Crossover                              |    |

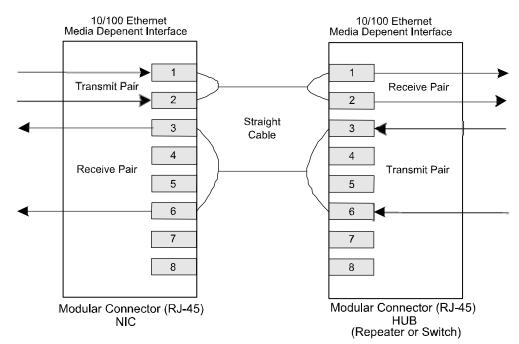

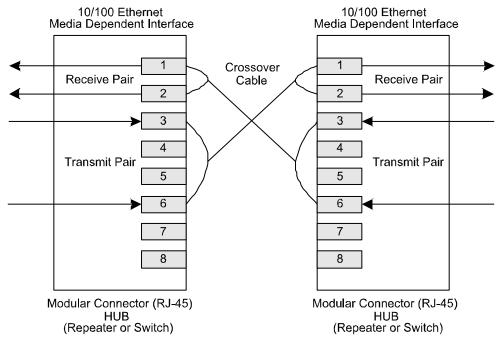

| Straight Cable                                        |    |

| Crossover Cable                                       |    |

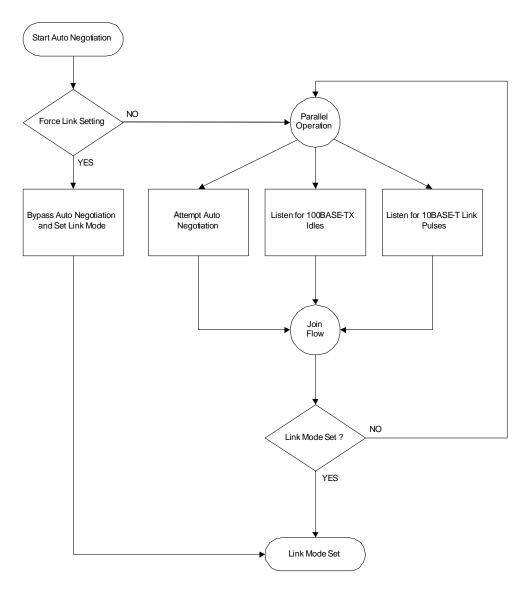

| Auto Negotiation                                      |    |

| LinkMD Cable Diagnostics                              |    |

| Access                                                |    |

| Usage                                                 |    |

| Functional Overview: MAC and Switch                   |    |

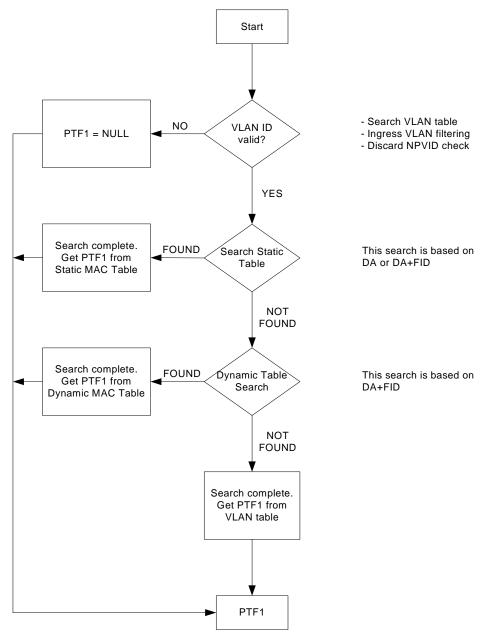

| Address Lookup                                        |    |

| Learning                                              |    |

| Migration                                             |    |

| Aging                                                 |    |

| Forwarding                                            |    |

| Switching Engine                                      |    |

| MAC Operation                                         |    |

| Inter Packet Gap (IPG)                                |    |

| Back-Off Algorithm                                    |    |

| Late Collision                                        |    |

| Illegal Packet Size                                   |    |

| Flow Control                                          |    |

| Half-Duplex Backpressure                              |    |

| Broadcast Storm Protection                            |    |

| Repeater Mode                                         |    |

| Clock Generator                                       | 29 |

| Advanced Switch Functions                             | 29 |

| Spanning Tree Support                                 | 29 |

| IGMP Support                                          | 30 |

| "IGMP" Snooping                                       | 30 |

| "Multicast Address Insertion" in the Static MAC Table | 30 |

| IPv6 MLD Snooping                                     | 30 |

| Port Mirroring Support                                |    |

| IEEE 802.1Q VLAN Support                              |    |

| QoS Priority Support                                  |    |

| Port-Based Priority                                   |    |

| 802.1p-Based Priority                                 |    |

| DiffServ based Priority                               |    |

| Rate Limiting Support                                 | 32 |

| MAC Filtering Function                                | 33 |

| -                                                     |    |

| Configuration Interface                                             |    |

|---------------------------------------------------------------------|----|

| EEPROM Interface                                                    | 33 |

| Loop back Support                                                   | 33 |

| Host Communication                                                  | 35 |

| Host Communication Descriptor Lists and Data Buffers                | 35 |

| Receive Descriptors (RDES0-RDES3)                                   | 35 |

| Transmit Descriptors (TDES0-TDES3)                                  |    |

| PCI Configuration Registers                                         | 39 |

| Configuration ID Register (CFID Offset 00H)                         | 39 |

| Command and Status Configuration Register (CFCS Offset 04H)         | 39 |

| Configuration Revision Register (CFRV Offset 08H)                   |    |

| Configuration Latency Timer Register (CFLT Offset 0CH)              |    |

| Configuration Base Memory Address Register (CBMA Offset 10H)        |    |

| Subsystem ID Register (CSID Offset 2CH)                             | 42 |

| Configuration Interrupt Register (CFIT Offset 3CH)                  |    |

| PCI Control & Status Registers                                      |    |

| MAC DMA Transmit Control Register (MDTXC Offset 0x0000)             | 43 |

| MAC DMA Receive Control Register (MDRXC Offset 0x0004)              |    |

| MAC DMA Transmit Start Command Register (MDTSC Offset 0x0008)       |    |

| MAC DMA Receive Start Command Register (MDRSC Offset 0x000C)        |    |

| Transmit Descriptor List Base Address Register (TDLB Offset 0x0010) | 46 |

| Receive Descriptor List Base Address Register (RDLB Offset 0x0014)  | 46 |

| Reserved (Offset 0x0018)                                            |    |

| Reserved (Offset 0x001C)                                            |    |

| MAC Multicast Table 0 Register (MTR0 Offset 0x0020)                 |    |

| MAC Multicast Table 1 Register (MTR1 Offset 0x0024)                 |    |

| Interrupt Enable Register (INTEN Offset 0x0024)                     |    |

| Interrupt Status Register (INTST Offset 0x002C)                     | 48 |

| MAC Additional Station Address Low Register (MAAL0-15)              |    |

| MAC Additional Station Address High Register (MAAH0-15)             |    |

| MAC/PHY and Control Registers                                       |    |

| MAC Address Register Low (0x0200): MARL                             |    |

| MAC Address Register Middle (0x0202): MARM                          |    |

| MAC Address Register High (0x0204): MARH                            | 50 |

| Reserved (Offset 0x0206 - 0x020A                                    |    |

| On-Chip Bus Control Register (Offset 0x0210): OBCR                  | 51 |

| EEPROM Control Register (Offset 0x0212): EEPCR                      | 51 |

| Memory BIST Info Register (Offset 0x0214): MBIR                     |    |

| Global Reset Register (Offset 0x0216): GRR                          |    |

| Switch Registers                                                    |    |

| Switch ID and Enable Register (Offset 0x0400): SIDER                |    |

| Switch Global Control Register 1 (Offset 0x0402): SGCR1             |    |

| Switch Global Control Register 2 (Offset 0x0404): SGCR2             |    |

| Switch Global Control Register 3 (Offset 0x0406): SGCR3             |    |

| Switch Global Control Register 4 (Offset 0x0408): SGCR4             |    |

| Switch Global Control Register 5 (Offset 0x040A): SGCR5             |    |

| Switch Global Control Register 6 (Offset 0x0410): SGCR6             |    |

| Switch Global Control Register 7 (0x0412): SGCR7                    |    |

| Reserved (Offset 0x0414 - 0x046F)                                   |    |

| MAC Address Register 1 (Offset 0x0470): MACAR1                      |    |

| MAC Address Register 2 (Offset 0x0472): MACAR2                      |    |

| MAC Address Register 3 (Offset 0x0474): MACAR3                      |    |

| Reserved (Offset 0x0476 - 0x047F)                                   |    |

| Priority Control Register 1 (Offset 0x0480): TOSR1                  | 59 |

| TOS Priority Control Register 2 (Offset 0x482): TOSR2               |    |

| TOS Priority Control Register 3 (Offset 0x484): TOSR3               |    |

| · · · · · · · · · · · · · · · · · · ·                               |    |

| 105 Priority Control Register 4 (Offset 0x486): 105R4                         |    |

|-------------------------------------------------------------------------------|----|

| TOS Priority Control Register 5 (Offset 0x488): TOSR5                         | 61 |

| TOS Priority Control Register 6 (Offset 0x48A): TOSR6                         | 62 |

| TOS Priority Control Register 7 (Offset 0x490): TOSR7                         | 62 |

| TOS Priority Control Register 8 (Offset 0x492): TOSR8                         | 63 |

| Reserved (Offset 0x0494 - 0x049A)                                             | 63 |

| Indirect Access Control Register (Offset 0x04A0): IACR                        | 64 |

| Indirect Access Data Register 1 (Offset 0x04A2): IADR1                        | 64 |

| Indirect Access Data Register 2 (Offset 0x04A4): IADR2                        |    |

| Indirect Access Data Register 3 (Offset 0x04A6): IADR3                        |    |

| Indirect Access Data Register 4 (Offset 0x04A8): IADR4                        |    |

| Indirect Access Data Register 5 (Offset 0x04AA): IADR5                        |    |

| Reserved (Offset 0x04B0 - 0x04BA)                                             | 65 |

| Reserved (Offset 0x04C0 –0x04CF)                                              | 65 |

| PHY 1 MII Basic Control Register (Offset 0x04D0): P1MBCR                      | 65 |

| PHY 1 MII Basic Status Register (Offset 0x04D2): P1MBSR                       | 66 |

| PHY 1 PHYID Low Register (Offset 0x04D4): PHY1ILR                             | 67 |

| PHY 1 PHYID High Register (Offset 0x04D6): PHY1IHR                            | 67 |

| PHY 1 Auto-Negotiation Advertisement Register (Offset 0x04D8): P1ANAR         |    |

| PHY 1 Auto-Negotiation Link Partner Ability Register (Offset 0x04DA): P1ANLPR |    |

| PHY 2 MII Basic Control Register (Offset 0x04E0): P2MBCR                      |    |

| PHY 2 MII Basic Status Register (Offset 0x04E2): P2MBSR                       | 69 |

| PHY 2 PHYID Low Register (Offset 0x04E4): PHY2ILR                             | 70 |

| PHY 2 PHYID High Register (Offset 0x04E6): PHY2IHR                            |    |

| PHY 2 Auto-Negotiation Advertisement Register (Offset 0x04E8): P2ANAR         |    |

| PHY 2 Auto-Negotiation Link Partner Ability Register (Offset 0x04EA): P2ANLPR |    |

| PHY1 LinkMD Control/Status (Offset 0x04F0): P1VCT                             | 72 |

| PHY1 Special Control/Status Register (Offset 0x04F2): P1PHYCTRL               | 72 |

| PHY2 LinkMD Control/Status (Offset 0x04F4): P2VCT                             | 73 |

| PHY2 Special Control/Status Register (Offset 0x04F6): P2PHYCTRL               | 73 |

| Reserved (Offset 0x04F8 - 0x04FA)                                             | 73 |

| Port 1 Control Register 1 (Offset 0x0500): P1CR1                              |    |

| Port 1 Control Register 2 (Offset 0x0502): P1CR2                              | 75 |

| Port 1 VID Control Register (Offset 0x0504): P1VIDCR                          | 76 |

| Port 1 Control Register 3 (Offset 0x0506): P1CR3                              |    |

| Port 1 Ingress Rate Control Register (Offset 0x0508): P1IRCR                  | 77 |

| Port 1 Egress Rate Control Register (Offset 0x050A): P1ERCR                   | 79 |

| Port 1 PHY Special Control/Status, LinkMD (Offset 0x0510): P1SCSLMD           | 81 |

| Port 1 Control Register 4 (Offset 0x0512): P1CR4                              |    |

| Port 1 Status Register (Offset 0x0514): P1SR                                  |    |

| Port 1 Reserved (Offset 0x0516 – 0x051A)                                      |    |

| Port 2 Control Register 1 (Offset 0x0520): P2CR1                              |    |

| Port 2 Control Register 2 (Offset 0x0522): P2CR2                              |    |

| Port 2 VID Control Register (Offset 0x0524): P2VIDCR                          |    |

| Port 2 Control Register 3 (Offset 0x0526): P2CR3                              |    |

| Port 2 Ingress Rate Control Register (Offset 0x0528): P2IRCR                  | 87 |

| Port 2 Egress Rate Control Register (Offset 0x052A): P2ERCR                   |    |

| Port 2 PHY Special Control/Status, LinkMD (Offset 0x0530): P2SCSLMD           |    |

| Port 2 Control Register 4 (Offset 0x0532): P2CR4                              |    |

| Port 2 Status Register (Offset 0x0534): P2SR                                  |    |

| Port 2 Reserved (Offset 0x0536 – 0x053A)                                      |    |

| Host Control Register 1 (Offset 0x0540): P3CR1                                |    |

| Host Control Register 2 (Offset 0x0542): P3CR2                                |    |

| Host VID Control Register (Offset 0x0544): P3VIDCR                            |    |

| Host Control Register 3 (Offset 0x0546): P3CR3                                | 97 |

| Host Ingress Rate Control Register (Offset 0x0548): P3IRCR                    | 98 |

| Host Egress Rate Control Register (Offset 0x054A): P3ERCR | 100 |

|-----------------------------------------------------------|-----|

| Reserved (Offset 0x0550)                                  | 102 |

| Reserved (Offset 0x0554)                                  | 102 |

| Reserved (Offset 0x0556)                                  |     |

| Reserved (Offset 0x0560)                                  | 102 |

| MIB (Management Information Base) Counters                | 103 |

| Additional MIB Information                                |     |

| Static MAC Address Table                                  |     |

| Dynamic MAC Address Table                                 | 107 |

| VLAN Table                                                | 108 |

| Absolute Maximum Ratings <sup>(1)</sup>                   | 109 |

| Operating Ratings <sup>(2)</sup>                          | 109 |

| Electrical Characteristics <sup>(4)</sup>                 | 109 |

| Timing Diagrams                                           |     |

| EEPROM Timing                                             | 111 |

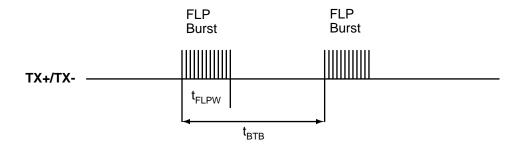

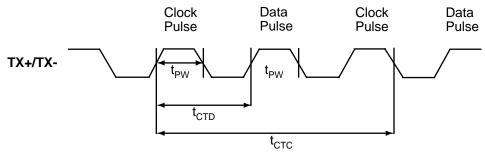

| Auto Negotiation Timing                                   | 112 |

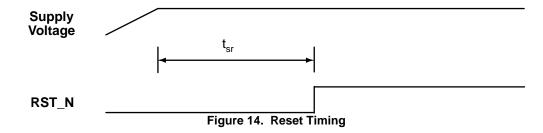

| Reset Timing                                              | 113 |

| Selection of Isolation Transformers                       | 114 |

| Selection of Reference Crystal                            | 114 |

| Package Information                                       | 115 |

| Acronyms and Glossary                                     | 117 |

|                                                           |     |

# **List of Figures**

| Figure 1. KSZ8842-PMQL/PMBL Functional Diagram                           |            |

|--------------------------------------------------------------------------|------------|

| Figure 2. KSZ8842-PMQL 128-Pin PQFP (Top View)                           |            |

| Figure 3. KSZ8842-PMBL 100-Ball LFBGA (Top View)                         |            |

| Figure 4. Typical Straight Cable Connection                              |            |

| Figure 5. Typical Crossover Cable Connection                             |            |

| Figure 6. Auto Negotiation and Parallel Operation                        |            |

| Figure 7. Destination Address Lookup Flow Chart, Stage 1                 |            |

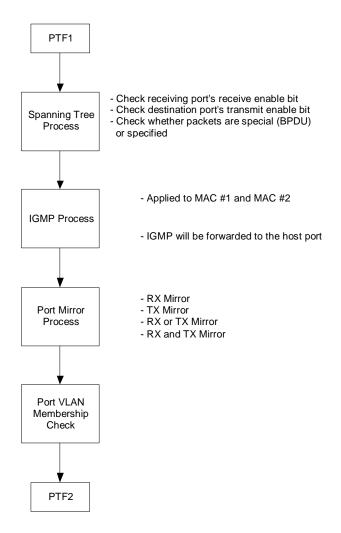

| Figure 8. Destination Address Resolution Flow Chart, Stage 2             | 27         |

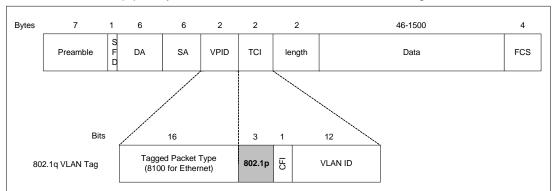

| Figure 9. 802.1p Priority Field Format                                   |            |

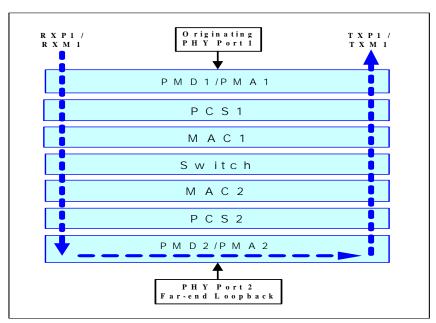

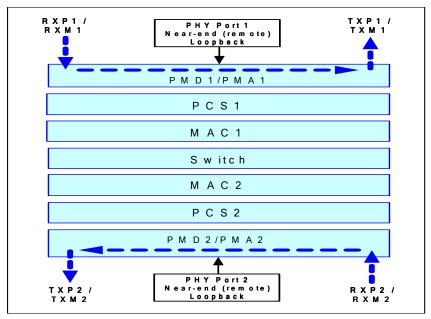

| Figure 10. Port 2 Far-End Loop back Path                                 | 34         |

| Figure 11. Port 1 and Port 2 Near-End (Remote) Loop back Path            | 34         |

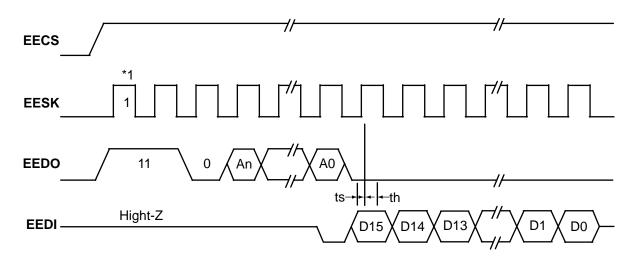

| Figure 12. EEPROM Read Cycle Timing Diagram                              | 111        |

| Figure 13. Auto-Negotiation Timing                                       |            |

| Figure 14. Reset Timing                                                  | 113        |

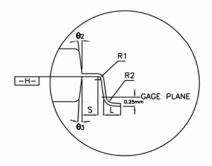

| Figure 15. Standard Package: 128-Pin PQFP                                |            |

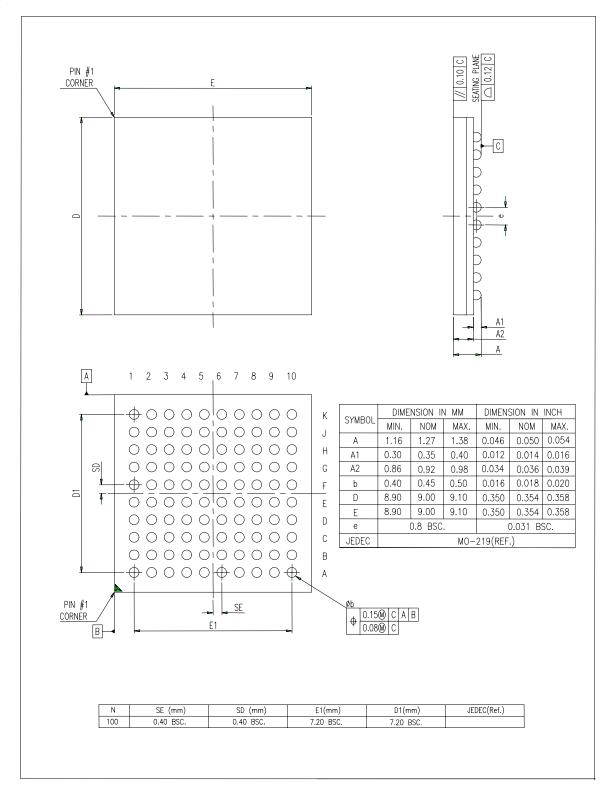

| Figure 16. Standard Package: 100-Ball LFBGA                              | 116        |

| Table 1. KSZ8842-PMQL Pin Description                                    | 19         |

| Table 3. MDI/MDI-X Pin Definitions                                       |            |

| Table 4. KSZ8841-PMQL/PMBL EEPROM Format                                 |            |

| Table 5. FID+DA Lookup in VLAN Mode                                      |            |

| Table 6. FID+SA Lookup in VLAN Mode                                      |            |

| Table 7. EEPROM Format                                                   |            |

| Table 8. Format of Per Port MIB Counters                                 |            |

| Table 10. "All Port Dropped Packet" MIB Counters Format                  |            |

| Table 11. "All Port Dropped Packet" MIB Counters Indirect Memory Offsets |            |

| Table 12. Static MAC Table Format (8 Entries)                            |            |

| Table 13. Dynamic MAC Address Table Format (1024 Entries)                |            |

| Table 14. VLAN Table Format (16 Entries)                                 |            |

| Table 15. EEPROM Timing Parameters                                       |            |

| Table 16. Auto Negotiation Parameters                                    | 112        |

| Table 17. Reset Timing Parameters                                        | 440        |

| Table 18. Transformer Selection Criteria                                 |            |

|                                                                          | 114        |

| Table 19. Qualified Single Port Magnetics                                | 114<br>114 |

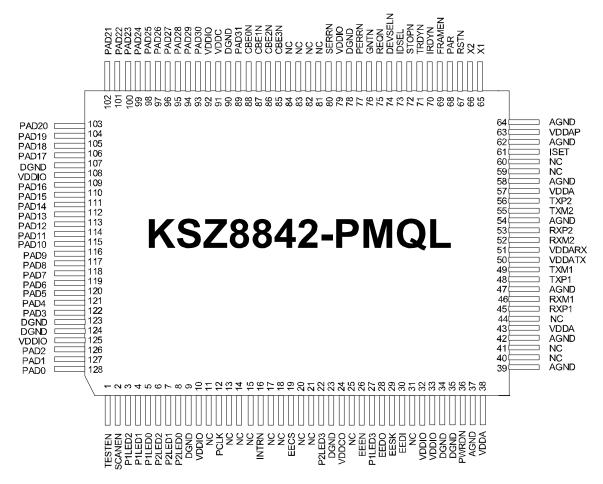

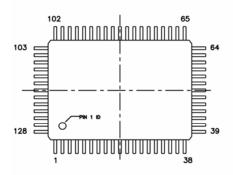

# **Pin Configuration**

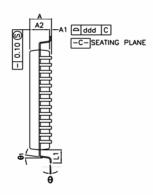

Figure 2. KSZ8842-PMQL 128-Pin PQFP (Top View)

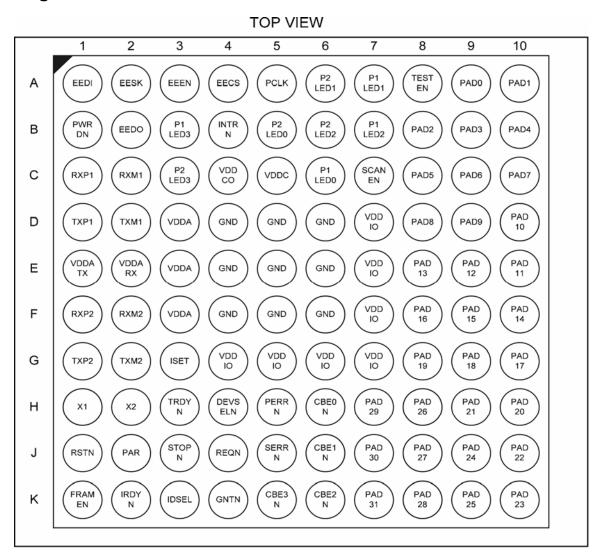

# **Balls Configuration**

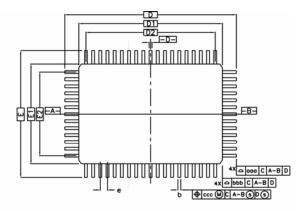

Figure 3. KSZ8842-PMBL 100-Ball LFBGA (Top View)

# Pins Description of KSZ8842-PMQL

| Pin<br>Number | Pin<br>Name      | Туре       | Pin Function                     |                                       |                                                        |

|---------------|------------------|------------|----------------------------------|---------------------------------------|--------------------------------------------------------|

| 1             | TEST_EN          | I          | Test Enable                      |                                       |                                                        |

|               |                  |            | For normal operation, pull-o     | lown this pin to grou                 | nd.                                                    |

| 2             | SCAN_EN          | I          | Scan Test Scan Mux Enal          | ble                                   |                                                        |

|               |                  |            | For normal operation, pull-o     | lown this pin to grou                 | nd.                                                    |

| 3             | P1LED2           | Opu        | Port 1 and Port 2 LED indic      | ators <sup>1</sup> defined as foll    | lows:                                                  |

| 4             | P1LED1           | Opu        | LEDs turn on when low.           |                                       |                                                        |

| 5             | P1LED0<br>P2LED2 | Opu<br>Opu |                                  | Chip Global Contr<br>SGCR5 bit [15,9] | rol Register 5:                                        |

| 7             | P2LED1           | Opu        |                                  | [0,0] Default                         | [0,1]                                                  |

| 8             | P2LED0           | Opu        | P1LED3 <sup>2</sup> /P2LED3      | _                                     | <u> -</u>                                              |

|               |                  | •          | P1LED2/P2LED2                    | Link/Act                              | 100Link/Act                                            |

|               |                  |            | P1LED1/P2LED1                    | Full duplex/Col                       | 10Link/Act                                             |

|               |                  |            | P1LED0/P2LED0                    | Speed                                 | Full duplex                                            |

|               |                  |            |                                  |                                       |                                                        |

|               |                  |            |                                  | Reg. SGCR5 bit [                      | 15,9]                                                  |

|               |                  |            |                                  | [1,0]                                 | [1,1]                                                  |

|               |                  |            | P1LED3 <sup>2</sup> /P2LED3      | Act                                   | _                                                      |

|               |                  |            | P1LED2/P2LED2                    | Link                                  | _                                                      |

|               |                  |            | P1LED1/P2LED1                    | Full duplex/Col                       | _                                                      |

|               |                  |            | P1LED0/P2LED0                    | Speed                                 | _                                                      |

|               |                  |            | Notes:                           |                                       |                                                        |

|               |                  |            | 1. Link = On; Activity = Blinl   | k; Link/Act = On/Blin                 | k; Full Dup/Col = On/Blink;                            |

|               |                  |            | Full Duplex = On (Full duple     | , , ,                                 |                                                        |

|               |                  |            | Speed = On (100BASE-T);          |                                       |                                                        |

|               |                  |            | 2. P1LED3 is pin 27. P2LEI       | D3 is pin 22                          |                                                        |

|               |                  |            | Port 1 and Port 2 LED indic      |                                       |                                                        |

|               |                  |            |                                  | Switch Global Cor<br>SGCR5 bit [15,9] | ntrol Register 5:                                      |

|               |                  |            |                                  | [0,0] Default                         | [0,1] [1,0],[1,1]                                      |

|               |                  |            | P1LED3/P2LED3                    | RPT_COL,<br>RPT_ACT                   |                                                        |

|               |                  |            | P1LED2/P2LED2                    | RPT_Link3/RX,<br>RPT_ERR3             | _                                                      |

|               |                  |            | P1LED1/P2LED1                    | RPT_Link2/RX,<br>RPT_ERR2             | _                                                      |

|               |                  |            | P1LED0/P2LED0                    | RPT_Link1/RX,<br>RPT_ERR1             | _                                                      |

|               |                  |            | Note: 1. RPT_COL = Blink; RPT_   | Link3/RX (Host port)                  | ) = On/Blink:                                          |

|               |                  |            | $RPT_Link2/RX (Port 2) = O$      | ` ' '                                 | •                                                      |

|               |                  |            | ` '                              |                                       | st port) = On if any CRC error;                        |

|               |                  |            | =                                | •                                     | $\Gamma_{\text{ERR1}}$ (port 1) = On if any CRC error; |

| 9             | DGND             | Gnd        | Digital ground                   | <u> </u>                              | ,                                                      |

| 10            | VDDIO            | Р          | 3.3V digital I/O V <sub>DD</sub> |                                       |                                                        |

| Pin<br>Number | Pin<br>Name | Туре | Pin Function                                                                                                                                                                                                  |

|---------------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11            | NC          | _    | No connect                                                                                                                                                                                                    |

| 12            | PCLK        | lpd  | PCI Bus Clock                                                                                                                                                                                                 |

|               |             |      | This Clock provides the timing for all PCI bus phases. The rising edge defines the start of each phase. The clock maximum frequency is 33MHz.                                                                 |

| 13            | NC          | _    | No connect                                                                                                                                                                                                    |

| 14            | NC          | _    | No connect                                                                                                                                                                                                    |

| 15            | NC          | _    | No connect                                                                                                                                                                                                    |

| 16            | INTRN       | Opd  | Interrupt Request                                                                                                                                                                                             |

|               |             |      | Active Low signal to host CPU to request an interrupt when any one of the interrupt conditions occurs in the registers. This pin should be pull-up externally.                                                |

| 17            | NC          | _    | No connect                                                                                                                                                                                                    |

| 18            | NC          | _    | No connect                                                                                                                                                                                                    |

| 19            | EECS        | Opu  | EEPROM Chip Select                                                                                                                                                                                            |

|               |             |      | This signal is used to select an external EEPROM device                                                                                                                                                       |

| 20            | NC          | _    | No connect                                                                                                                                                                                                    |

| 21            | NC          | _    | No connect                                                                                                                                                                                                    |

| 22            | P2LED3      | Opd  | Port 2 LED Indicator                                                                                                                                                                                          |

|               |             |      | See the description in pins 6, 7, and 8.                                                                                                                                                                      |

| 23            | DGND        | Gnd  | Digital IO Ground                                                                                                                                                                                             |

| 24            | VDDCO       | Р    | 1.2V Core Voltage Output. (Internal 1.2V LDO power supply output)                                                                                                                                             |

|               |             |      | This pin is used to provide 1.2V power supply to all 1.2V power VDDC, VDDA and VDDAP. It is recommended the pin should be connected to 3.3V power rail by a 100ohm resistor for the internal LDO application. |

| 25            | NC          | _    | No connect                                                                                                                                                                                                    |

| 26            | EEEN        | lpd  | EEPROM Enable                                                                                                                                                                                                 |

|               |             |      | EEPROM is enabled and connected when this pin is pull-up.                                                                                                                                                     |

|               |             |      | EEPROM is disabled when this pin is pull-down or no connect.                                                                                                                                                  |

| 27            | P1LED3      | Opd  | Port 1 LED Indicator                                                                                                                                                                                          |

|               |             |      | See the description in pins 3, 4, and 5.                                                                                                                                                                      |

| 28            | EEDO        | Opd  | EEPROM Data Out                                                                                                                                                                                               |

|               |             |      | This pin is connected to DI input of the serial EEPROM.                                                                                                                                                       |

| 29            | EESK        | Opd  | EEPROM Serial Clock                                                                                                                                                                                           |

|               |             |      | 4μs serial clock to load configuration data from the serial EEPROM.                                                                                                                                           |

| 30            | EEDI        | lpd  | EEPROM Data In                                                                                                                                                                                                |

|               |             |      | This pin is connected to DO output of the serial EEPROM.                                                                                                                                                      |

| 31            | NC          | _    | No connect                                                                                                                                                                                                    |

| 32            | VDDIO       | Р    | 3.3V digital I/O V <sub>DD</sub> .                                                                                                                                                                            |

| 33            | VDDIO       | Р    | 3.3V digital I/O V <sub>DD</sub> .                                                                                                                                                                            |

| 34            | DGND        | Gnd  | Digital ground                                                                                                                                                                                                |

| 35            | DGND        | Gnd  | Digital ground                                                                                                                                                                                                |

| 36            | PWRDN       | lpu  | Full-chip power-down input. Active Low.                                                                                                                                                                       |

| 37            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                 |

| 38            | VDDA        | Р    | 1.2V analog V <sub>DD</sub>                                                                                                                                                                                   |

| 39            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                 |

| 40            | NC          |      | No connect                                                                                                                                                                                                    |

October 2007 12 M9999-100207-1.5

| Pin<br>Number | Pin<br>Name | Туре | Pin Function                                                                                                                                                                                                                                                                                                                            |

|---------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41            | NC          | _    | No connect                                                                                                                                                                                                                                                                                                                              |

| 42            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                                                                                                                                           |

| 43            | VDDA        | Р    | 1.2V analog V <sub>DD</sub>                                                                                                                                                                                                                                                                                                             |

| 44            | NC          | _    | No connect                                                                                                                                                                                                                                                                                                                              |

| 45            | RXP1        | I/O  | Physical receive (MDI) or transmit (MDIX)signal (+ differential)                                                                                                                                                                                                                                                                        |

| 46            | RXM1        | I/O  | Physical receive (MDI) or transmit (MDIX) signal (– differential)                                                                                                                                                                                                                                                                       |

| 47            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                                                                                                                                           |

| 48            | TXP1        | I/O  | Physical transmit (MDI) or receive (MDIX) signal (+ differential)                                                                                                                                                                                                                                                                       |

| 49            | TXM1        | I/O  | Physical transmit (MDI) or receive (MDIX) signal (- differential)                                                                                                                                                                                                                                                                       |

| 50            | VDDATX      | Р    | 3.3V analog V <sub>DD</sub>                                                                                                                                                                                                                                                                                                             |

| 51            | VDDARX      | Р    | 3.3V analog V <sub>DD</sub>                                                                                                                                                                                                                                                                                                             |

| 52            | RXM2        | I/O  | Port 2 physical receive (MDI) or transmit (MDIX)signal (- differential)                                                                                                                                                                                                                                                                 |

| 53            | RXP2        | I/O  | Port 2 physical receive(MDI) or transmit (MDIX) signal (+ differential)                                                                                                                                                                                                                                                                 |

| 54            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                                                                                                                                           |

| 55            | TXM2        | I/O  | Port 2 physical transmit (MDI) or receive (MDIX) signal (- differential)                                                                                                                                                                                                                                                                |

| 56            | TXP2        | I/O  | Port 2 physical transmit (MDI) or receive (MDIX) signal (+ differential)                                                                                                                                                                                                                                                                |

| 57            | VDDA        | Р    | 1.2 analog V <sub>DD</sub>                                                                                                                                                                                                                                                                                                              |

| 58            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                                                                                                                                           |

| 59            | NC          | _    | No connect                                                                                                                                                                                                                                                                                                                              |

| 60            | NC          | _    | No connect                                                                                                                                                                                                                                                                                                                              |

| 61            | ISET        | 0    | Set physical transmit output current                                                                                                                                                                                                                                                                                                    |

|               |             |      | Pull-down this pin with a 3.01K 1% resistor to ground.                                                                                                                                                                                                                                                                                  |

| 62            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                                                                                                                                           |

| 63            | VDDAP       | Р    | 1.2V analog V <sub>DD</sub> for PLL                                                                                                                                                                                                                                                                                                     |

| 64            | AGND        | Gnd  | Analog ground                                                                                                                                                                                                                                                                                                                           |

| 65            | X1          | - 1  | 25MHz crystal/oscillator clock connections                                                                                                                                                                                                                                                                                              |

| 66            | X2          | 0    | Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V tolerant oscillator and X2 is not connected.                                                                                                                                                                                                        |

|               |             |      | Note: Clock is ±50ppm for both crystal and oscillator.                                                                                                                                                                                                                                                                                  |

| 67            | RSTN        | lpu  | Hardware Reset, Active Low                                                                                                                                                                                                                                                                                                              |

|               |             |      | RSTN will cause the KSZ8842-PMQL to reset all of its functional blocks. RSTN must be asserted for a minimum duration of 10 ms.                                                                                                                                                                                                          |

| 68            | PAR         | I/O  | PCI Parity                                                                                                                                                                                                                                                                                                                              |

|               |             |      | Even parity computed for PAD [31:0] and CBE [3:0]N, master drives PAR for address and write data phase, target drives PAR for read data phase.                                                                                                                                                                                          |

| 69            | FRAMEN      | I/O  | PCI Cycle Frame                                                                                                                                                                                                                                                                                                                         |

|               |             |      | This signal is asserted low to indicate the beginning of the address phase of the bus transaction and de-asserted before the final transfer of the data phase of the transaction in a bus master mode. As a target, the device monitors this signal before decoding the address to check if the current transaction is addressed to it. |

| 70            | IRDYN       | I/O  | PCI Initiator Ready                                                                                                                                                                                                                                                                                                                     |

|               |             |      | As a bus master, this signal is asserted low to indicate valid data phases on PAD [31:0] during write data phases, indicates it is ready to accept data during read data phases. As a target, it'll monitor this IRDYN signal that indicates the master has put the data on the bus.                                                    |

| Pin<br>Number | Pin<br>Name | Туре | Pin Function                                                                                                                                                                                                                                                                                              |

|---------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71            | TRDYN       | I/O  | PCI Target Ready                                                                                                                                                                                                                                                                                          |

|               |             |      | As a bus target, this signal is asserted low to indicate valid data phases on PAD [31:0] during read data phases, indicating it is ready to accept data during write data phases. As a master, it will monitor this TRDYN signal that indicates the target is ready for data during read/write operation. |

| 72            | STOPN       | I/O  | PCI Stop                                                                                                                                                                                                                                                                                                  |

|               |             |      | This signal is asserted low by the target device to stop the current transaction.                                                                                                                                                                                                                         |

| 73            | IDSEL       | I/O  | PCI Initialization Device Select                                                                                                                                                                                                                                                                          |

|               |             |      | This signal is used to select the KSZ8842-PMQL during configuration read and write transactions.                                                                                                                                                                                                          |

| 74            | DEVSELN     | I/O  | PCI Device Select                                                                                                                                                                                                                                                                                         |

|               |             |      | This signal is asserted low when it is selected as a target during a bus transaction. As a bus master, the KSZ8842-PMQL samples this signal to insure that the destination address for the data transfer is recognized by a PCI target.                                                                   |

| 75            | REQN        | 0    | PCI Bus Request                                                                                                                                                                                                                                                                                           |

|               |             |      | The KSZ8842-PMQL will assert this signal low to request PCI bus master operation.                                                                                                                                                                                                                         |

| 76            | GNTN        | I    | PCI Bus Grant                                                                                                                                                                                                                                                                                             |

|               |             |      | This signal is asserted low to indicate to the KSZ8842-PMQL that it has been granted the PCI bus master operation.                                                                                                                                                                                        |

| 77            | PERRN       | I/O  | PCI Parity Error                                                                                                                                                                                                                                                                                          |

|               |             |      | The KSZ8842-PMQL as a master or target will assert this signal low to indicate a parity error on any incoming data. As a bus master, it will monitor this signal on all write operations.                                                                                                                 |

| 78            | DGND        | Gnd  | Digital I/O ground                                                                                                                                                                                                                                                                                        |

| 79            | VDDIO       | Р    | 3.3V digital I/O V <sub>DD</sub>                                                                                                                                                                                                                                                                          |

| 80            | SERRN       | 0    | PCI System Error                                                                                                                                                                                                                                                                                          |

|               |             |      | This system error signal is asserted low by the KSZ8842-PMQL. This signal is used to report address parity errors.                                                                                                                                                                                        |

| 81            | NC          |      | No connect                                                                                                                                                                                                                                                                                                |

| 82            | NC          |      | No connect                                                                                                                                                                                                                                                                                                |

| 83            | NC          |      | No connect                                                                                                                                                                                                                                                                                                |

| 84            | NC          |      | No connect                                                                                                                                                                                                                                                                                                |

| 85            | CBE3N       | 1    | Command and Byte Enable                                                                                                                                                                                                                                                                                   |

| 86            | CBE2N       | 1    | These signals are multiplexed on the same PCI pins. During the address phase, these                                                                                                                                                                                                                       |

| 87            | CBE1N       | I    | lines define the bus command. During the data phase, these lines are used as Byte Enables. The Byte enables are valid for the entire data phase and determine which byte                                                                                                                                  |

| 88            | CBE0N       | I    | lanes carry meaningful data.                                                                                                                                                                                                                                                                              |

| 89            | PAD31       | I/O  | PCI Address / Data 31                                                                                                                                                                                                                                                                                     |

|               |             |      | Address and data are multiplexed on the all of the PAD pins. The PAD pins carry the physical address during the first clock cycle of a transaction, and carry data during the subsequent clock cycles.                                                                                                    |

| 90            | DGND        | Gnd  | Digital core ground                                                                                                                                                                                                                                                                                       |

| 91            | VDDC        | Р    | 1.2V digital core V <sub>DD</sub>                                                                                                                                                                                                                                                                         |

| 92            | VDDIO       | Р    | 3.3V digital I/O V <sub>DD</sub>                                                                                                                                                                                                                                                                          |

| 93            | PAD30       | I/O  | PCI Address / Data 30                                                                                                                                                                                                                                                                                     |

| 94            | PAD29       | I/O  | PCI Address / Data 29                                                                                                                                                                                                                                                                                     |

| 95            | PAD28       | I/O  | PCI Address / Data 28                                                                                                                                                                                                                                                                                     |

| Pin<br>Number | Pin<br>Name | Туре | Pin Function                     |

|---------------|-------------|------|----------------------------------|

| 96            | PAD27       | I/O  | PCI Address / Data 27            |

| 97            | PAD26       | I/O  | PCI Address / Data 26            |

| 98            | PAD25       | I/O  | PCI Address / Data 25            |

| 99            | PAD24       | I/O  | PCI Address / Data 24            |

| 100           | PAD23       | I/O  | PCI Address / Data 23            |

| 101           | PAD22       | I/O  | PCI Address / Data 22            |

| 102           | PAD21       | I/O  | PCI Address / Data 21            |

| 103           | PAD20       | I/O  | PCI Address / Data 20            |

| 104           | PAD19       | I/O  | PCI Address / Data 19            |

| 105           | PAD18       | I/O  | PCI Address / Data 18            |

| 106           | PAD17       | I/O  | PCI Address / Data 17            |

| 107           | DGND        | Gnd  | Digital I/O ground               |

| 108           | VDDIO       | Р    | 3.3V digital I/O V <sub>DD</sub> |

| 109           | PAD16       | I/O  | PCI Address / Data 16            |

| 110           | PAD15       | I/O  | PCI Address / Data 15            |

| 111           | PAD14       | I/O  | PCI Address / Data 14            |

| 112           | PAD13       | I/O  | PCI Address / Data 13            |

| 113           | PAD12       | I/O  | PCI Address / Data 12            |

| 114           | PAD11       | I/O  | PCI Address / Data 11            |

| 115           | PAD10       | I/O  | PCI Address / Data 10            |

| 116           | PAD9        | I/O  | PCI Address / Data 9             |

| 117           | PAD8        | I/O  | PCI Address / Data 8             |

| 118           | PAD7        | I/O  | PCI Address / Data 7             |

| 119           | PAD6        | I/O  | PCI Address / Data 6             |

| 120           | PAD5        | I/O  | PCI Address / Data 5             |

| 121           | PAD4        | I/O  | PCI Address / Data 4             |

| 122           | PAD3        | I/O  | PCI Address / Data 3             |

| 123           | DGND        | Gnd  | Digital I/O ground               |

| 124           | DGND        | Gnd  | Digital core ground              |

| 125           | VDDIO       | Р    | 3.3V digital I/O V <sub>DD</sub> |

| 126           | PAD2        | I/O  | PCI Address / Data 2             |

| 127           | PAD1        | I/O  | PCI Address / Data 1             |

| 128           | PAD0        | I/O  | PCI Address / Data 0             |

Table 1. KSZ8842-PMQL Pin Description

# Notes:

P = Power supply.

$\mathsf{Gnd} = \mathsf{Ground}.$

I = Input.

O = Output.

I/O = Bi-directional.

Ipd = Input with internal pull-down.

lpu = Input with internal pull-up.

Opd = Output with internal pull-down.

Opu = Output with internal pull-up.

# **Balls Description of KSZ8842-PMBL**

| Ball<br>Number | Ball<br>Name | Туре | Ball Function                                                                                                           |                                          |                |                              |

|----------------|--------------|------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|------------------------------|

| A8             | TEST_EN      | 1    | Test Enable.                                                                                                            |                                          |                |                              |

|                |              |      | For normal operation, pull-d                                                                                            | own this pin to grou                     | nd.            |                              |

| C7             | SCAN_EN      | 1    | Scan Test Scan Mux Enable                                                                                               | э.                                       |                |                              |

|                |              |      | For normal operation, pull-d                                                                                            | own this pin to grou                     | nd.            |                              |

| B7             | P1LED2       | Opu  | Port 1 and Port 2 LED indic                                                                                             | ators <sup>1</sup> defined as fol        | lows:          |                              |

| A7             | P1LED1       | Opu  |                                                                                                                         | Switch Global Co                         | ntrol Registe  | er 5:                        |

| C6             | P1LED0       | Opu  |                                                                                                                         | SGCR5 bit [15,9]                         | 1              |                              |

| B6             | P2LED2       | Opu  |                                                                                                                         | [0,0] Default                            | [0,1]          |                              |

| A6             | P2LED1       | Opu  | P1LED3 <sup>2</sup> /P2LED3                                                                                             | _                                        |                |                              |

| B5             | P2LED0       | Opu  | P1LED2/P2LED2                                                                                                           | Link/Act                                 | 100Link/A      | Act                          |

|                |              |      | P1LED1/P2LED1                                                                                                           | Full duplex/Col                          | 10Link/Ac      | et                           |

|                |              |      | P1LED0/P2LED0                                                                                                           | Speed                                    | Full duple     | ×                            |

|                |              |      |                                                                                                                         |                                          |                |                              |

|                |              |      |                                                                                                                         | Reg. SGCR5 bit [                         | 15,9]          |                              |

|                |              |      |                                                                                                                         | [1,0]                                    | [1,1]          |                              |

|                |              |      | P1LED3 <sup>2</sup> P2LED3                                                                                              | Act                                      | _              |                              |