260-Pin BGA Com & Ind Temp POD I/O

# 144Mb SigmaDDR-IVe™ Burst of 2 Single-Bank ECCRAM™

Up to 933 MHz  $1.2V \sim 1.3V V_{DD}$   $1.2V \sim 1.3V V_{DDO}$

#### **Features**

- 4Mb x 36 and 8Mb x 18 organizations available

- Organized as a single logical memory bank

- 933 MHz maximum operating frequency

- 933 MT/s peak transaction rate (in millions per second)

- 67 Gb/s peak data bandwidth (in x36 devices)

- Common I/O DDR Data Bus

- Non-multiplexed SDR Address Bus

- One operation Read or Write per clock cycle

- No address/bank restrictions on Read and Write ops

- Burst of 2 Read and Write operations

- 5 cycle Read Latency

- On-chip ECC with virtually zero SER

- Loopback signal timing training capability

- 1.2V ~ 1.3V nominal core voltage

- 1.2V ~ 1.3V POD I/O interface

- Configuration registers

- Configurable ODT (on-die termination)

- ZQ pin for programmable driver impedance

- ZT pin for programmable ODT impedance

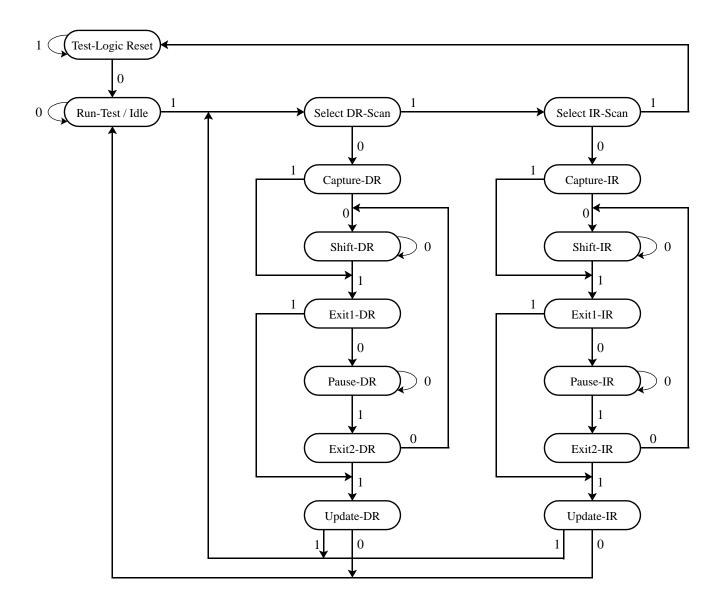

- IEEE 1149.1 JTAG-compliant Boundary Scan

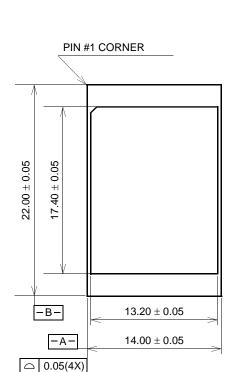

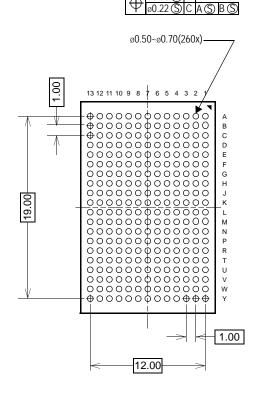

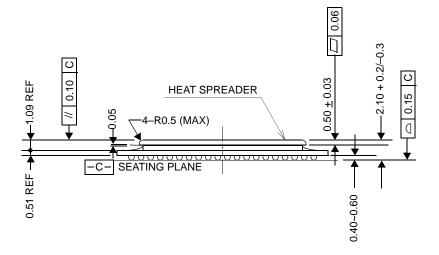

- 260-pin, 14 mm x 22 mm, 1 mm ball pitch, 6/6 RoHScompliant BGA package

## SigmaDDR-IVe™ Family Overview

SigmaDDR-IVe ECCRAMs are the Common I/O half of the SigmaQuad-IVe/SigmaDDR-IVe family of high performance ECCRAMs. Although similar to GSI's third generation of networking SRAMs (the SigmaQuad-IIIe/SigmaDDR-IIIe family), these fourth generation devices offer several new features that help enable significantly higher performance.

### Clocking and Addressing Schemes

The GS81314PT19/37GK SigmaDDR-IVe ECCRAMs are synchronous devices. They employ three pairs of positive and negative input clocks; one pair of master clocks, CK and  $\overline{CK}$ , and two pairs of write data clocks, KD[1:0] and  $\overline{KD}$ [1:0]. All six input clocks are single-ended; that is, each is received by a dedicated input buffer.

CK and  $\overline{\text{CK}}$  are used to latch address and control inputs, and to control all output timing. KD[1:0] and  $\overline{\text{KD}}$ [1:0] are used solely to latch data inputs.

Each internal read and write operation in a SigmaDDR-IVe B2 ECCRAM is two times wider than the device I/O bus. An input data bus de-multiplexer is used to accumulate incoming data before it is simultaneously written to the memory array. An output data multiplexer is used to capture the data produced from a single memory array read and then route it to the appropriate output drivers as needed. Therefore, the address field of a SigmaDDR-IVe B2 ECCRAM is always one address pin less than the advertised index depth (e.g. the 8M x 18 has 4M addressable index).

### On-Chip Error Correction Code

GSI's ECCRAMs implement an ECC algorithm that detects and corrects all single-bit memory errors, including those induced by SER events such as cosmic rays, alpha particles, etc. The resulting Soft Error Rate of these devices is anticipated to be <0.002 FITs/Mb — a 5-order-of-magnitude improvement over comparable SRAMs with no on-chip ECC, which typically have an SER of 200 FITs/Mb or more.

All quoted SER values are at sea level in New York City.

## **Parameter Synopsis**

| Speed Grade | Max Operating Frequency | ing Frequency Read Latency |                |  |

|-------------|-------------------------|----------------------------|----------------|--|

| -933        | 933 MHz                 | 5 cycles                   | 1.25V to 1.35V |  |

| -800        | 800 MHz                 | 5 cycles                   | 1.15V to 1.35V |  |

| 8M x | 18 | Pinout | (Top | View) |

|------|----|--------|------|-------|

|------|----|--------|------|-------|

| - | 1                | 2                | 3                | 4         | 5               | 6                  | 7                  | 8                  | 9               | 10        | 11               | 12               | 13               |

|---|------------------|------------------|------------------|-----------|-----------------|--------------------|--------------------|--------------------|-----------------|-----------|------------------|------------------|------------------|

| Α | $V_{DD}$         | $NU_{IO}$        | $V_{DD}$         | $NU_{I}$  | NC<br>(RSVD)    | MCH<br>(CFG)       | MRW                | ZQ                 | PZT1            | $NU_{I}$  | $V_{DD}$         | DQINV0           | $V_{DD}$         |

| В | $V_{SS}$         | NU <sub>IO</sub> | $V_{SS}$         | $NU_{I}$  | MCL             | MCL                | NC<br>(RSVD)       | MCL<br>(SIOM)      | PZT0            | $NU_{I}$  | $V_{SS}$         | DQ0              | $V_{SS}$         |

| С | DQ17             | V <sub>DDQ</sub> | NUI              | $V_{DDQ}$ | V <sub>SS</sub> | SA13               | $V_{DD}$           | SA14               | $V_{SS}$        | $V_{DDQ}$ | NUI              | $V_{DDQ}$        | NU <sub>IO</sub> |

| D | V <sub>SS</sub>  | NU <sub>IO</sub> | $V_{SS}$         | NUI       | SA19            | $V_{\mathrm{DDQ}}$ | NC<br>(288 Mb)     | $V_{\mathrm{DDQ}}$ | SA20            | NUI       | $V_{SS}$         | DQ1              | $V_{SS}$         |

| Ε | DQ16             | V <sub>DDQ</sub> | NUI              | $V_{DD}$  | V <sub>SS</sub> | SA11               | $V_{SS}$           | SA12               | $V_{SS}$        | $V_{DD}$  | NUI              | $V_{DDQ}$        | NU <sub>IO</sub> |

| F | V <sub>SS</sub>  | NU <sub>IO</sub> | $V_{SS}$         | NUI       | SA17            | $V_{DD}$           | $V_{\mathrm{DDQ}}$ | $V_{DD}$           | SA18            | NUI       | $V_{SS}$         | DQ2              | $V_{SS}$         |

| G | DQ15             | NU <sub>IO</sub> | NUI              | NUI       | $V_{SS}$        | SA9                | NUI                | SA10               | V <sub>SS</sub> | NUI       | NUI              | DQ3              | NU <sub>IO</sub> |

| Н | DQ14             | $V_{DDQ}$        | NUI              | $V_{DDQ}$ | SA15            | $V_{DDQ}$          | R/W                | $V_{DDQ}$          | SA16            | $V_{DDQ}$ | NUI              | $V_{DDQ}$        | NU <sub>IO</sub> |

| J | V <sub>SS</sub>  | NU <sub>IO</sub> | $V_{SS}$         | NUI       | $V_{SS}$        | SA7                | $V_{SS}$           | SA8                | V <sub>SS</sub> | NUI       | V <sub>SS</sub>  | DQ4              | $V_{SS}$         |

| K | CQ1              | V <sub>DDQ</sub> | V <sub>REF</sub> | $V_{DD}$  | KD1             | $V_{DD}$           | CK                 | $V_{DD}$           | KD0             | $V_{DD}$  | V <sub>REF</sub> | $V_{DDQ}$        | CQ0              |

| L | CQ1              | V <sub>SS</sub>  | QVLD1            | $V_{SS}$  | KD1             | $V_{\mathrm{DDQ}}$ | CK                 | $V_{DDQ}$          | KD0             | $V_{SS}$  | QVLD0            | $V_{SS}$         | CQ0              |

| М | $V_{SS}$         | DQ13             | $V_{SS}$         | NUI       | $V_{SS}$        | SA5                | $V_{SS}$           | SA6                | $V_{SS}$        | NUI       | $V_{SS}$         | NU <sub>IO</sub> | $V_{SS}$         |

| N | NU <sub>IO</sub> | $V_{DDQ}$        | NUI              | $V_{DDQ}$ | PLL             | $V_{DDQ}$          | LD                 | $V_{DDQ}$          | MCL             | $V_{DDQ}$ | NUI              | $V_{DDQ}$        | DQ5              |

| Р | NU <sub>IO</sub> | DQ12             | NUI              | NUI       | $V_{SS}$        | SA3                | MZT                | SA4                | V <sub>SS</sub> | NUI       | NUI              | NU <sub>IO</sub> | DQ6              |

| R | $V_{SS}$         | DQ11             | $V_{SS}$         | NUI       | MCH             | $V_{DD}$           | $V_{DDQ}$          | $V_{DD}$           | RST             | $NU_{I}$  | $V_{SS}$         | NU <sub>IO</sub> | $V_{SS}$         |

| T | NU <sub>IO</sub> | $V_{DDQ}$        | NUI              | $V_{DD}$  | $V_{SS}$        | SA1                | $V_{SS}$           | SA2                | $V_{SS}$        | $V_{DD}$  | NU <sub>I</sub>  | $V_{DDQ}$        | DQ7              |

| U | $V_{SS}$         | DQ10             | $V_{SS}$         | NUI       | NC<br>(576 Mb)  | $V_{\mathrm{DDQ}}$ | NC<br>(RSVD)       | $V_{DDQ}$          | NC<br>(1152 Mb) | $NU_{I}$  | $V_{SS}$         | NU <sub>IO</sub> | $V_{SS}$         |

| ٧ | NU <sub>IO</sub> | V <sub>DDQ</sub> | NUI              | $V_{DDQ}$ | $V_{SS}$        | SA21<br>(x18)      | $V_{DD}$           | SA0<br>(B2)        | V <sub>SS</sub> | $V_{DDQ}$ | NUI              | $V_{DDQ}$        | DQ8              |

| W | V <sub>SS</sub>  | DQ9              | $V_{SS}$         | NUI       | TCK             | MCL                | RCS                | MCL                | TMS             | NUI       | $V_{SS}$         | NU <sub>IO</sub> | $V_{SS}$         |

| Υ | V <sub>DD</sub>  | DQINV1           | $V_{DD}$         | NUI       | TDO             | NU                 | NC<br>(RSVD)       | MCL                | TDI             | NUI       | $V_{DD}$         | NU <sub>IO</sub> | $V_{DD}$         |

- 1. Pins 5B, 6B, 6W, 8W, 8Y, and 9N must be tied Low in this device.

- 2. Pin 5R must be tied High in this device.

- 3. Pin 6A is defined as mode pin CFG in the pinout standard. It must be tied High in this device to select x18 configuration.

- 4. Pin 8B is defined as mode pin SIOM in the pinout standard. It must be tied Low in this device to select Common I/O configuration.

- 5. Pin 6V is defined as address pin SA for x18 devices. It is used in this device.

- 6. Pin 8V is defined as address pin SA for B2 devices. It is used in this device.

- 7. Pin 7D is reserved as address pin SA for 288Mb devices. It is a true no-connect in this device.

- 8. Pin 5U is reserved as address pin SA for 576 Mb devices. It is a true no connect in this device.

- 9. Pin 9U is reserved as address pin SA for 1152 Mb devices. It is a true no connect in this device.

| 4M x 36 Pinout ( | (Top View) |

|------------------|------------|

|------------------|------------|

| _ | 1               | 2                | 3                | 4                  | 5               | 6                        | 7                  | 8                  | 9               | 10        | 11               | 12               | 13       |

|---|-----------------|------------------|------------------|--------------------|-----------------|--------------------------|--------------------|--------------------|-----------------|-----------|------------------|------------------|----------|

| Α | $V_{DD}$        | DQINV3           | $V_{DD}$         | $NU_{I}$           | NC<br>(RSVD)    | MCL<br>(CFG)             | MRW                | ZQ                 | PZT1            | $NU_{I}$  | $V_{DD}$         | DQINV0           | $V_{DD}$ |

| В | $V_{SS}$        | DQ35             | $V_{SS}$         | NUI                | MCL             | MCL                      | NC<br>(RSVD)       | MCL<br>(SIOM)      | PZT0            | NUI       | $V_{SS}$         | DQ0              | $V_{SS}$ |

| С | DQ26            | $V_{DDQ}$        | NUI              | $V_{DDQ}$          | V <sub>SS</sub> | SA13                     | $V_{DD}$           | SA14               | $V_{SS}$        | $V_{DDQ}$ | NUI              | V <sub>DDQ</sub> | DQ9      |

| D | V <sub>SS</sub> | DQ34             | $V_{SS}$         | NUI                | SA19            | $V_{\mathrm{DDQ}}$       | NC<br>(288 Mb)     | $V_{\mathrm{DDQ}}$ | SA20            | NUI       | $V_{SS}$         | DQ1              | $V_{SS}$ |

| Ε | DQ25            | $V_{DDQ}$        | NUI              | $V_{DD}$           | V <sub>SS</sub> | SA11                     | $V_{SS}$           | SA12               | $V_{SS}$        | $V_{DD}$  | NUI              | V <sub>DDQ</sub> | DQ10     |

| F | V <sub>SS</sub> | DQ33             | $V_{SS}$         | NUI                | SA17            | $V_{DD}$                 | $V_{\mathrm{DDQ}}$ | $V_{DD}$           | SA18            | NUI       | $V_{SS}$         | DQ2              | $V_{SS}$ |

| G | DQ24            | DQ32             | NU <sub>I</sub>  | NUI                | $V_{SS}$        | SA9                      | NUI                | SA10               | $V_{SS}$        | NUI       | NUI              | DQ3              | DQ11     |

| Н | DQ23            | $V_{DDQ}$        | NUI              | $V_{DDQ}$          | SA15            | $V_{DDQ}$                | R/W                | $V_{DDQ}$          | SA16            | $V_{DDQ}$ | NUI              | V <sub>DDQ</sub> | DQ12     |

| J | V <sub>SS</sub> | DQ31             | $V_{SS}$         | NUI                | $V_{SS}$        | SA7                      | $V_{SS}$           | SA8                | $V_{SS}$        | NUI       | V <sub>SS</sub>  | DQ4              | $V_{SS}$ |

| K | CQ1             | $V_{DDQ}$        | V <sub>REF</sub> | $V_{DD}$           | KD1             | $V_{DD}$                 | CK                 | $V_{DD}$           | KD0             | $V_{DD}$  | V <sub>REF</sub> | V <sub>DDQ</sub> | CQ0      |

| L | CQ1             | $V_{SS}$         | QVLD1            | $V_{SS}$           | KD1             | $V_{\mathrm{DDQ}}$       | CK                 | $V_{\mathrm{DDQ}}$ | KD0             | $V_{SS}$  | QVLD0            | V <sub>SS</sub>  | CQ0      |

| М | V <sub>SS</sub> | DQ22             | $V_{SS}$         | NUI                | $V_{SS}$        | SA5                      | $V_{SS}$           | SA6                | $V_{SS}$        | NUI       | V <sub>SS</sub>  | DQ13             | $V_{SS}$ |

| N | DQ30            | $V_{DDQ}$        | NUI              | $V_{DDQ}$          | PLL             | $V_{DDQ}$                | LD                 | $V_{DDQ}$          | MCL             | $V_{DDQ}$ | NUI              | V <sub>DDQ</sub> | DQ5      |

| Р | DQ29            | DQ21             | NU <sub>I</sub>  | NUI                | $V_{SS}$        | SA3                      | MZT                | SA4                | $V_{SS}$        | NUI       | NUI              | DQ14             | DQ6      |

| R | $V_{SS}$        | DQ20             | $V_{SS}$         | $NU_{I}$           | MCH             | $V_{DD}$                 | $V_{DDQ}$          | $V_{DD}$           | RST             | $NU_{I}$  | $V_{SS}$         | DQ15             | $V_{SS}$ |

| T | DQ28            | V <sub>DDQ</sub> | NU <sub>I</sub>  | $V_{DD}$           | $V_{SS}$        | SA1                      | $V_{SS}$           | SA2                | $V_{SS}$        | $V_{DD}$  | NUI              | V <sub>DDQ</sub> | DQ7      |

| U | V <sub>SS</sub> | DQ19             | $V_{SS}$         | NUI                | NC<br>(576 Mb)  | $V_{\mathrm{DDQ}}$       | NC<br>(RSVD)       | $V_{DDQ}$          | NC<br>(1152 Mb) | NUI       | V <sub>SS</sub>  | DQ16             | $V_{SS}$ |

| ٧ | DQ27            | V <sub>DDQ</sub> | NU <sub>I</sub>  | $V_{\mathrm{DDQ}}$ | $V_{SS}$        | NU <sub>I</sub><br>(x18) | $V_{DD}$           | SA0<br>(B2)        | V <sub>SS</sub> | $V_{DDQ}$ | NUI              | V <sub>DDQ</sub> | DQ8      |

| W | V <sub>SS</sub> | DQ18             | $V_{SS}$         | NUI                | TCK             | MCL                      | RCS                | MCL                | TMS             | NUI       | V <sub>SS</sub>  | DQ17             | $V_{SS}$ |

| Υ | V <sub>DD</sub> | DQINV2           | $V_{DD}$         | NU <sub>I</sub>    | TDO             | NU                       | NC<br>(RSVD)       | MCL                | TDI             | NUI       | $V_{DD}$         | DQINV1           | $V_{DD}$ |

- 1. Pins 5B, 6B, 6W, 8W, 8Y, and 9N must be tied Low in this device.

- 2. Pin 5R must be tied High in this device.

- 3. Pin 6A is defined as mode pin CFG in the pinout standard. It must be tied Low in this device to select x36 configuration.

- 4. Pin 8B is defined as mode pin SIOM in the pinout standard. It must be tied Low in this device to select Common I/O configuration.

- 5. Pin 6V is defined as address pin SA for x18 devices. It is unused in this device, and must be left unconnected or driven High.

- 6. Pin 8V is defined as address pin SA for B2 devices. It is used in this device.

- 7. Pin 7D is reserved as address pin SA for 288Mb devices. It is a true no-connect in this device.

- 8. Pin 5U is reserved as address pin SA for 576 Mb devices. It is a true no connect in this device.

- 9. Pin 9U is reserved as address pin SA for 1152 Mb devices. It is a true no connect in this device.

## **Pin Description**

| Symbol                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Туре   |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| SA[21:0]                            | Address — Read or write address is registered on ↑CK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input  |

| DQ[35:0]                            | Write/Read Data — Registered on ↑KD and ↑KD during Write operations; aligned with ↑CQ and ↑CQ during Read operations.  DQ[17:0] - x18 and x36.  DQ[35:18] - x36 only.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O    |

| DQINV[3:0]                          | Write/Read Data Inversion — Registered on ↑KD and ↑KD (along with write data) during Write operations; indicate if the associated write data byte is inverted (DQINVx = 1) or not (DQINVx = 0). Aligned with ↑CQ and ↑CQ (along with read data) during Read operations; indicate if the associated read data byte is inverted (DQINVx = 1) or not (DQINVx = 0).  DQINV0 - associated with DQ[8:0] in x18 and x36.  DQINV1 - associated with DQ[17:9] in x18 and x36.  DQINV2 - associated with DQ[26:18] in x36 only.  DQINV3 - associated with DQ[35:27] in x36 only.  Note: Treated as NU I/Os when Data Inversion is disabled. | I/O    |

| QVLD[1:0]                           | Read Data Valid — Driven high one half cycle before valid read data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Output |

| CK, CK                              | Primary Input Clocks — Dual single-ended. Used for latching address and control inputs, for internal timing control, and for output timing control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input  |

| <u>KD</u> [1:0],<br>KD[1:0]         | Write Data Input Clocks — Dual single-ended. Used for latching write data inputs.  KD0, KD0: latch DQ[17:0], DQINV[1:0] in x36, and DQ[8:0], DQINV0 in x18.  KD1, KD1: latch DQ[35:18], DQINV[3:2] in x36, and DQ[17:9], DQINV1 in x18.                                                                                                                                                                                                                                                                                                                                                                                           | Input  |

| <u>CQ</u> [1:0],<br><u>CQ</u> [1:0] | Read Data Output Clocks — Free-running output (echo) clocks, tightly aligned with read data outputs.  Facilitate source-synchronous operation.  CQ0, CQ0: align with DQ[17:0], DQINV[1:0] in x36, and DQ[8:0], DQINV0 in x18.  CQ1, CQ1: align with DQ[35:18], DQINV[3:2] in x36, and DQ[17:9], DQINV1 in x18.                                                                                                                                                                                                                                                                                                                    | Output |

| LD                                  | Load Enable — Registered on↑CK. See the Clock Truth Table for functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Input  |

| R/W                                 | Read / Write Enable — Registered on ↑CK. See the Clock Truth Table for functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input  |

| MRW                                 | Mode Register Write — Registered on↑CK. Can be used synchronously or asynchronously to enable Register Write Mode. See the State and Clock Truth Tables for functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input  |

| PLL                                 | PLL Enable — Weakly pulled High internally. PLL = 0: disables internal PLL. PLL = 1: enables internal PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input  |

| RST                                 | Reset — Holds the device inactive and resets the device to its initial power-on state when asserted High. Weakly pulled Low internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input  |

| ZQ                                  | <b>Driver / ODT Impedance Control Resistor Input</b> — Must be connected to V <sub>SS</sub> through an external resistor RQ to program driver and ODT impedances.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input  |

| RCS                                 | Current Source Resistor Input — Must be connected to $V_{SS}$ through an external $2K\Omega$ resistor to provide an accurate current source for the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input  |

| Symbol           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Туре   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| MZT              | ODT Mode Select — Sets the default ODT state globally for all input groups during power-up and reset.  Must be tied High or Low.  MZT = 0: disables ODT on all input groups, regardless of PZT[1:0].  MZT = 1: enables ODT on select input groups, as specified by PZT[1:0].  Note: The ODT state for each input group can be changed at any time via the Configuration Registers.                                                                                                                                                 | Input  |

| PZT[1:0]         | ODT Configuration Select — Set the default ODT state for various combinations of input groups during power-up and reset, when MZT = 1. Must be tied High or Low.  PZT[1:0] = 00: enables ODT on write data only.  PZT[1:0] = 01: enables ODT on write data and input clocks.  PZT[1:0] = 10: enables ODT on write data, address, and control.  PZT[1:0] = 11: enables ODT on write data, input clocks, address, and control.  Note: The ODT state for each input group can be changed at any time via the Configuration Registers. | Input  |

| V <sub>DD</sub>  | Core Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _      |

| V <sub>DDQ</sub> | I/O Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _      |

| V <sub>REF</sub> | Input Reference Voltage — Input buffer reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _      |

| V <sub>SS</sub>  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _      |

| TCK              | JTAG Clock — Weakly pulled Low internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Input  |

| TMS              | JTAG Mode Select — Weakly pulled High internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input  |

| TDI              | JTAG Data Input — Weakly pulled High internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input  |

| TDO              | JTAG Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Output |

| MCH              | <b>Must Connect High</b> — May be tied to $V_{DDQ}$ directly or via a $1k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                         | Input  |

| MCL              | <b>Must Connect Low</b> — May be tied to $V_{SS}$ directly or via a $1k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input  |

| NC               | No Connect — There is no internal chip connection to these pins. They may be left unconnected, or tied/ driven High or Low.                                                                                                                                                                                                                                                                                                                                                                                                        | _      |

| NUI              | Not Used Input — There is an internal chip connection to these input pins, but they are unused by the device. They are pulled High internally. They may be left unconnected or tied/driven High. They should not be tied/driven Low.                                                                                                                                                                                                                                                                                               | Input  |

| NU <sub>IO</sub> | Not Used Input/Output — There is an internal chip connection to these I/O pins, but they are unused by the device. The drivers are tri-stated internally. They are pulled High internally. They may be left unconnected or tied/driven High. They should not be tied/driven Low.                                                                                                                                                                                                                                                   | I/O    |

### **Initialization Summary**

Prior to functional use, these devices must first be initialized and configured. The steps described below will ensure that the internal logic has been properly reset, and that functional timing parameters have been configured.

# Flow Chart Power-Up Reset SRAM Wait for Calibrations Enable PLL Wait for Lock Training No Required? Yes Address / Control Input Training Read Data Output Training Write Data Input Training Additional Configuration Normal Operation No

- MZT and PZT[1:0] mode pins are used to set the default ODT state of all input groups at power-up, and whenever RST is asserted High. The ODT state for each input group can be changed any time thereafter using Register Write Mode to program certain bits in the Configuration Registers.

- Calibrations are performed for driver impedance, ODT impedance, and the PLL current source immediately after RST is de-asserted Low. The calibrations can take up to 384K cycles total. See the Power-Up and Reset Requirements section for more information.

- 3. The PLL can be enabled by the PLL pin, or by the PLL Enable (PLE) bit in the Configuration Registers. See the PLL Operation section for more information.

- 4. If the PLE register bit is used to enable the PLL, then Register Write Mode will likely have to be utilized in the "Asynchronous, Pre-Input Training" method in order to change the state of the bit, since Address / Control Input Training has not yet been performed. See the Configuration Registers section for more information.

- 5. It can take up to 64K cycles for the PLL to lock after it has been enabled.

- Special Loopback Modes are available in these devices to perform Address / Control Input Training; they are selected and enabled via the Loopback Mode Select (LBK[1:0]) and Loopback Mode Enable (LBKE) bits in the Configuration Registers.

- If Loopback Modes are used to perform Address / Control Input Training, then Register Write Mode will likely have to be utilized in the "Asynchronous, Pre-Input Training" method in order to change the states of the LBK[1:0] and LBKE register bits.

- Loopback Modes can also be used for Read Data Output Training, if desired.

See the Signal Timing Training and Loopback Mode sections for more information.

- 9. "Additional Configuration" includes programming the Read Latency to 5 cycles (which is required by these devices), and any other configuration changes required by the system. Since this step is performed after Address / Control Input Training, Register Write Mode can be utilized in the "Asynchronous, Post-Input Training" method (or perhaps the "Synchronous" method, if the synchronous timing requirements can be met at the particular operating frequency).

- 10. It is up to the system to determine if/when re-training is necessary.

### Power-Up and Reset Requirements

For reliability purposes, power supplies must power up simultaneously, or in the following sequence:

$V_{SS}$ ,  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{REF}$  and inputs.

Power supplies must power down simultaneously, or in the reverse sequence.

After power supplies power up, the following start-up sequence must be followed.

Step 1: Assert RST High for at least 1ms.

While RST is asserted high:

- The PLL is disabled.

- The states of  $\overline{LD}$ , R/W, and MRW control inputs are ignored.

**Note**: If possible, RST should be asserted High before input clocks begin toggling, and remain asserted High until input clocks are stable and toggling within specification, in order to prevent unstable, out-of-spec input clocks from causing trouble in the SRAM.

**Step 2:** Begin toggling input clocks.

After input clocks begin toggling, but not necessarily within specification:

- DQ are placed in the non-Read state, and remain so until the first Read operation.

- QVLD are driven Low, and remain so until the first Read operation.

- CQ,  $\overline{CQ}$  begin toggling, but not necessarily within specification.

**Step 3**: Wait until input clocks are stable and toggling within specification.

Step 4: De-assert RST Low.

Step 5: Wait at least 384K (393,216) cycles.

During this time:

- Driver and ODT impedances are calibrated. Can take up to 320K cycles.

- The current source for the PLL is calibrated (based on RCS pin). Can take up to 64K cycles.

Step 6: Enable the PLL.

Step 7: Wait at least 64K (65,536) cycles for the PLL to lock.

After the PLL has locked:

• CQ,  $\overline{CQ}$  begin toggling within specification.

Step 8: Continue initialization (see the Initialization Flow Chart).

#### Reset Usage

Although not generally recommended, RST may be asserted High at any time after completion of the initial power-up sequence described above, to reset the SRAM control logic to its initial power-on state. However, whenever RST is subsequently de-asserted Low, as in step 4 above, steps 5~7 above must be followed before normal operation is resumed. It is up the system to determine whether further re-initialization beyond step 7 (as outlined in the Initialization Flow Chart) is required before normal operation is resumed.

Note: Memory array content may be perturbed/corrupted when RST is asserted High.

### **PLL Operation**

A PLL is implemented in these devices to control all output timing. It uses the CK input clock as a source, and is enabled when all of the following conditions are met:

- 1. RST is de-asserted Low, and

- 2. Either the PLL Enable pin (PLL) or the PLL Enable register bit (PLE) is asserted High, and

- 3. CK cycle time  $\leq$  t<sub>KHKH</sub> (max), as specified in the AC Timing Specifications section.

Once enabled, the PLL requires 64K stable clock cycles in order to lock/synchronize properly.

When the PLL is enabled, it aligns output clocks and read data to input clocks (with some fixed delay), and it generates all mid-cycle output timing. See the Output Timing section for more information.

The PLL can tolerate changes in input clock frequency due to clock jitter (i.e. such jitter will not cause the PLL to lose lock/ synchronization), provided the cycle-to-cycle jitter does not exceed 200ps (see "t<sub>KJITcc</sub>" in the AC Timing Specifications section for more information). However, the PLL must be resynchronized (i.e. disabled and then re-enabled) whenever the nominal input clock frequency is changed.

The PLL is disabled when any of the following conditions are met:

- 1. RST is asserted High, or

- 2. Both the PLL Enable pin (PLL) and the PLL Enable register bit (PLE) are deasserted Low, or

- 3. CK is stopped for at least 30ns, or CK cycle time  $\geq$  30ns.

### **On-Chip Error Correction**

These devices implement a single-error correct, single-error detect (SEC-SED) ECC algorithm (specifically, a Hamming Code) on each 18-bit data word transmitted in DDR fashion on each 9-bit data bus (i.e., transmitted on D/Q[8:0], D/Q[17:9], D/Q[26:18], and D/Q[35:27]). To accomplish this, 5 ECC parity bits (invisible to the user) are utilized per every 18 data bits (visible to the user). As such, these devices actually comprise 184Mb of memory, of which 144Mb are visible to the user.

The ECC algorithm cannot detect multi-bit errors. However, these devices are architected in such a way that a single SER event very rarely causes a multi-bit error across any given "transmitted data unit", where a "transmitted data unit" represents the data transmitted as the result of a single read or write operation to a particular address. The extreme rarity of multi-bit errors results in the SER mentioned previously (i.e., <0.002 FITs/Mb, measured at sea level).

Not only does the on-chip ECC significantly improve SER performance, but it can also free up the entire memory array for data storage. Very often SRAM applications allocate 1/9th of the memory array (i.e., one "error bit" per eight "data bits", in any 9-bit "data byte") for error detection (either simple parity error detection, or system-level ECC error detection and correction). Depending on the application, such error-bit allocation may be unnecessary in these devices, in which case the entire memory array can be utilized for data storage, effectively providing 12.5% greater storage capacity compared to SRAMs of the same density not equipped with on-chip ECC.

### **Configuration Registers**

These devices utilize a set of registers for device configuration. The configuration registers are written via **Register Write Mode**, which is initiated by asserting MRW High and  $\overline{LD}$  Low. When Register Write Mode is utilized, up to sixteen distinct 6-bit registers can be programmed using SDR timing on the SA[10:1] address input pins. The DQ data input pins are not used.

**Note**: Register Write Mode only provides the ability to write the configuration registers. The ability to read the configuration registers is provided via a private JTAG instruction and register. Please contact GSI for more information.

Register Write Mode can be utilized in two ways:

- 1. **Asynchronous Method**: MRW is driven asynchronously, such that is does not meet setup and hold time specs to ↑CK.

- 2. **Synchronous Method**: MRW is driven synchronously, such that is meets setup and hold time specs to ↑CK.

Regardless how Register Write Mode is utilized, at least 16 NOPs must be initiated before beginning a Register Write sequence, to ensure any previous Read and Write operations are completed before the sequence begins. And, at least 16 NOPs must be initiated after completing a Register Write sequence and before initiating Read and Write operations, and before utilizing Loopback Mode, to allow sufficient time for the newly programmed register settings to take effect.

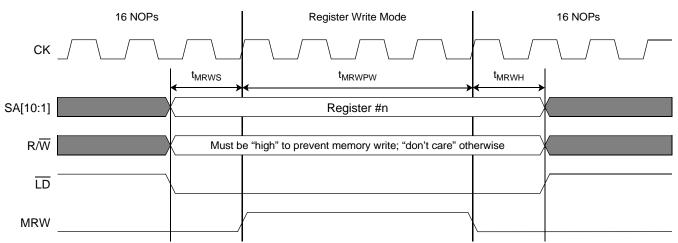

## Register Write Mode Utilization - Asynchronous Method

Register Write Mode can be utilized asynchronously up to the full operating speed of the device. When Register Write Mode is utilized asynchronously, there are two cases to consider:

- 1. **Pre Input Training:** SA[10:1],  $\overline{LD}$ ,  $R/\overline{W}$  are driven such that they do not meet setup and hold time specs to  $\uparrow CK$ .

- 2. **Post Input Training**: SA[10:1],  $\overline{LD}$ , R/ $\overline{W}$  are driven such that they meet setup and hold time specs to  $\uparrow$ CK.

Each case is examined separately below.

#### **Pre Input Training Requirements**

In this case, MRW,  $\overline{LD}$ , R/ $\overline{W}$ , and SA[10:1] are all driven asynchronously. When Register Write Mode is utilized in this manner, only one register can be programmed during any particular instance that MRW is asserted High.

The requirements for this usage case are as follows:

- At least 16 NOPs must be initiated before and after the Register Write sequence.

- MRW High must meet minimum pulse width requirements (tMRWPW).

- LD Low and SA[10:1] Valid must meet minimum setup time requirements (tMRWS) to MRW High.

- LD Low and SA[10:1] Valid must meet minimum hold time requirements (tMRWH) from MRW Low.

- R/W High must also meet minimum setup time requirements (tMRWS) to MRW High, if inadvertent memory writes are to be prevented during the Register Write process. Otherwise, R/W state is "don't care".

- R/W High must also meet minimum hold time requirements (tMRWH) from MRW Low, if inadvertent memory writes are to be prevented during the Register Write process. Otherwise, R/W state is "don't care".

**Note**: tMRWPW = tMRWS = tMRWH = 4 cycles (minimum).

**Note**: Inadvertent memory reads will occur while MRW and  $\overline{LD}$  are Low and R/ $\overline{W}$  is High during the Register Write process. The memory reads are harmless, and can be ignored.

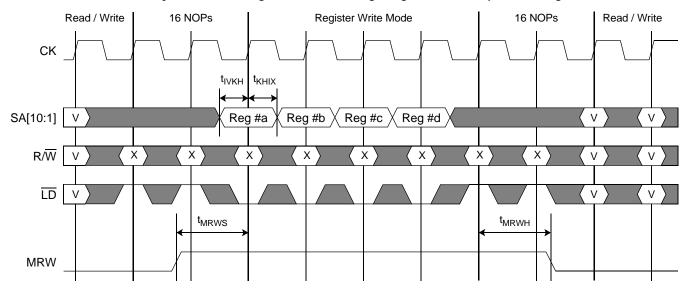

#### Post Input Training Requirements

In this case, MRW is driven asynchronously, whereas  $\overline{\text{LD}}$ , R/W, and SA[10:1] are all driven synchronously (i.e. they all meet setup and hold time specs to  $\uparrow$ CK). When Register Write Mode is utilized in this manner, multiple registers can be programmed during any particular instance that MRW is asserted High. The timing diagrams below arbitrarily show four registers programmed while MRW is asserted High, but in practice it can be any number greater than or equal to one.

The requirements for this usage case are as follows:

- At least 16 NOPs must be initiated before and after the Register Write(s).

- MRW High must meet minimum setup time requirements (tMRWS) to the \tag{CK} that generates the first Register Write.

- MRW High must meet minimum hold time requirements (tMRWH) from the \tag{CK} that generates the first NOP after the last Register Write.

- LD must be driven Low (synchronously) and SA[10:1] must be driven Valid (synchronously) for each Register Write.

- $R/\overline{W}$  state is a "don't care" (synchronously) for each Register Write.

**Note**: tMRWS = tMRWH = 4 cycles (minimum).

## Asynchronous Register Write Timing Diagram - Pre Input Training

## Asynchronous Register Write Timing Diagram - Post Input Training

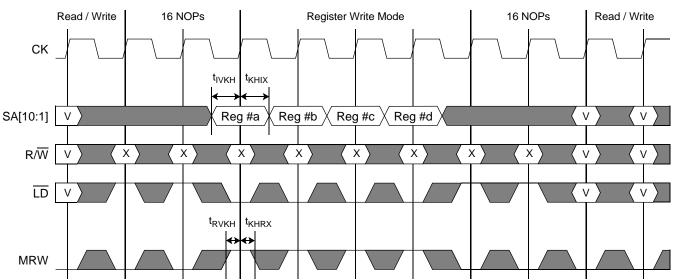

### Register Write Mode Utilization - Synchronous Method

Register Write Mode can also be utilized synchronously up to the full operating speed of the device. However, MRW cannot be trained using Loopback Mode, so the ability to use it synchronously may be limited to slower operating frequencies where the lack of training capability is less problematic for the user.

In this case, MRW,  $\overline{LD}$ , R/ $\overline{W}$ , and SA[10:1] are all driven synchronously (i.e. they all meet setup and hold time specs to  $\uparrow$ CK). When Register Write Mode is utilized in this manner, multiple registers can be programmed in successive cycles. The timing diagrams below arbitrarily show four registers programmed in successive cycles, but in practice it can be any number greater than or equal to one.

The requirements for this usage case are as follows:

- At least 16 NOPs must be initiated before and after the Register Write(s).

- MRW must be driven High (synchronously),  $\overline{\text{LD}}$  must be driven Low (synchronously), and SA[10:1] must be driven Valid (synchronously) for each Register Write.

- $R/\overline{W}$  state is a "don't care" (synchronously) for each Register Write.

## Synchronous Register Write Timing Diagram

## **Register Description**

As described previously, Register Write Mode provides the ability to program up to sixteen distinct 6-bit configuration registers using SDR timing on the SA[10:1] address input pins. Specifically, SA[4:1] are used to select one of the sixteen distinct registers, and SA[10:5] are used to program the six data bits of the selected register.

The registers are defined as follows:

| Address   | SA10                               | SA9 | SA8     | SA7       | SA6   | SA5  | SA4        | SA3        | SA2 | SA1    |         |

|-----------|------------------------------------|-----|---------|-----------|-------|------|------------|------------|-----|--------|---------|

| Pin       | 8G                                 | 6G  | 8J      | 6J        | 8M    | 6M   | 8P         | 6P         | 8T  | 6T     | Reg#    |

| Bit Usage |                                    | R   | egister | Data Bit  | S     |      | Re         |            |     |        |         |

| Active    |                                    | DI  |         |           |       | RLM  | 0          | 0          | 0   | 0      | 0       |

| Active    |                                    |     |         | RSVD[2:0] |       | PLE  | 0          | 0          | 0   | 1      | 1       |

| Active    |                                    |     |         | LBK       | [1:0] | LBKE | 0          | 0          | 1   | 0      | 2       |

| Active    |                                    | DZT |         | KDZT      |       | CKZT | 0          | 0          | 1   | 1      | 3       |

| Active    |                                    |     |         | CZT       |       | AZT  | 0          | 1          | 0   | 0      | 4       |

| Unused    |                                    |     |         |           |       | Al   | l Others e | xcept "111 | Χ"  | 5 ~ 13 |         |

| Active    | Reserved for GSI Internal Use Only |     |         |           |       |      | 1          | 1          | 1   | Χ      | 14 ~ 15 |

#### Notes:

- 1. Unused/unlabeled register bits should be written to "0".

- 2. The RSVD[2:0] bits in Register #1 should be written to "100".

- 3. Registers #14 and #15 are reserved for GSI internal use only. Users should not access these registers.

### **Register Bit Definitions**

| Read Latency Select |                         |  |  |  |

|---------------------|-------------------------|--|--|--|

| RLM                 |                         |  |  |  |

| 0                   | Read Latency = 5 cycles |  |  |  |

| 1                   | reserved                |  |  |  |

| 1                   | POR/RST Default         |  |  |  |

| PLL Enable |                             |  |  |  |  |

|------------|-----------------------------|--|--|--|--|

| PLE        |                             |  |  |  |  |

| 0          | Disable PLL, if PLL pin = 0 |  |  |  |  |

| 1          | Enable PLL                  |  |  |  |  |

| 0          | POR/RST Default             |  |  |  |  |

| Data Inversion Enable |                        |  |  |  |

|-----------------------|------------------------|--|--|--|

| DI                    |                        |  |  |  |

| 0                     | Disable Data Inversion |  |  |  |

| 1                     | Enable Data Inversion  |  |  |  |

| 0                     | POR/RST Default        |  |  |  |

**Note**: The power-on / reset default value of the RLM register bit is "1". Consequently, Register Write Mode must be used to set the RLM bit to "0", to program RL=5 in these devices, prior to issuing Read operations.

| Loopback Mode Enable |                       |  |  |  |  |

|----------------------|-----------------------|--|--|--|--|

| LBKE                 |                       |  |  |  |  |

| 0                    | Disable Loopback Mode |  |  |  |  |

| 1                    | Enable Loopback Mode  |  |  |  |  |

| 0                    | POR/RST Default       |  |  |  |  |

|     | Loopback Mode Select |                                   |  |  |  |  |  |  |  |  |

|-----|----------------------|-----------------------------------|--|--|--|--|--|--|--|--|

| LBK | [1:0]                |                                   |  |  |  |  |  |  |  |  |

| 0   | 0                    | XOR Loopback Mode, input group #1 |  |  |  |  |  |  |  |  |

| 0   | 1                    | XOR Loopback Mode, input group #2 |  |  |  |  |  |  |  |  |

| 1   | 0                    | INV Loopback Mode, input group #1 |  |  |  |  |  |  |  |  |

| 1   | 1                    | INV Loopback Mode, input group #2 |  |  |  |  |  |  |  |  |

| 0   | 0                    | POR/RST Default                   |  |  |  |  |  |  |  |  |

**Note**: In the ODT Control register bit definitions below, MZT and PZT[1:0] pins set the default state of the register bits at power-up and whenever RST is asserted High. The register bits can then be overwritten (via Register Write Mode), while RST is de-asserted Low, to change the state of the feature controlled by the register bits.

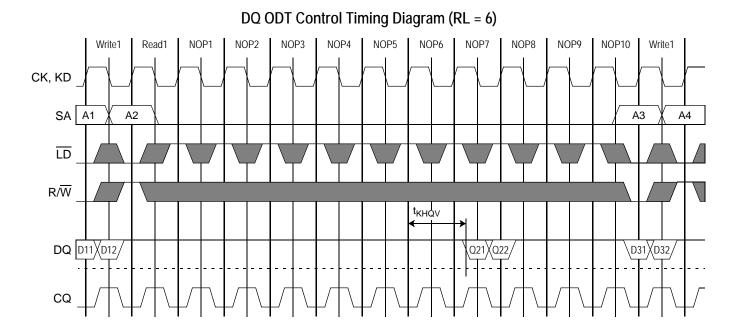

| Input Clock ODT Control                                 |                      |  |  |  |  |  |  |

|---------------------------------------------------------|----------------------|--|--|--|--|--|--|

| CKZT                                                    |                      |  |  |  |  |  |  |

| KDZT                                                    |                      |  |  |  |  |  |  |

| 0                                                       | disabled             |  |  |  |  |  |  |

| 1                                                       | enabled: PU = 0.3*RQ |  |  |  |  |  |  |

| 0, if MZT = 0 or PZT0 = 0<br>1, if MZT = 1 and PZT0 = 1 | POR/RST Default      |  |  |  |  |  |  |

| Address & Control ODT Control                           |                      |  |  |  |  |  |  |

|---------------------------------------------------------|----------------------|--|--|--|--|--|--|

| AZT                                                     |                      |  |  |  |  |  |  |

| CZT                                                     |                      |  |  |  |  |  |  |

| 0                                                       | disabled             |  |  |  |  |  |  |

| 1                                                       | enabled: PU = 0.3*RQ |  |  |  |  |  |  |

| 0, if MZT = 0 or PZT1 = 0<br>1, if MZT = 1 and PZT1 = 1 | POR/RST Default      |  |  |  |  |  |  |

| Write Data ODT Control         |                      |  |  |  |  |  |  |

|--------------------------------|----------------------|--|--|--|--|--|--|

| DZT                            |                      |  |  |  |  |  |  |

| 0                              | disabled             |  |  |  |  |  |  |

| 1                              | enabled: PU = 0.3*RQ |  |  |  |  |  |  |

| 0, if MZT = 0<br>1, if MZT = 1 | POR/RST Default      |  |  |  |  |  |  |

### Signal Timing Training

Signal timing training (aka "deskew") is often required for reliable signal transmission between components at the I/O speeds supported by these devices. Typically, the timing training is performed in the following sequence:

- Step 1: Address / Control input training.

These devices support a special Loopback Mode of operation to facilitate address / control input training.

- Step 2: Read Data output training.

These devices support a special Loopback Mode of operation to facilitate read data output training.

Alternatively, slow-frequency Memory Write operations can be used to store DDR data patterns in the memory array reliably (full-frequency Memory Write operations cannot be used because write data signals have not been trained yet), and full-frequency Memory Read operations can then be used to train the read data output signals.

- Step 3: Write Data input training.

Since address, control, and read data signals have already been trained at this point, full-frequency Memory Write and Read operations can then be used to train the write data inputs.

#### Loopback Mode

These devices support two distinct **Loopback Modes** of operation, which can be used to:

- 1. Perform per-pin training on the address (SA), control  $(\overline{LD}, R/\overline{W})$ , and write data clock (KD,  $\overline{KD})$  inputs.

- 2. Perform per-pin training on the data (DQ, DQINV) outputs.

In both cases, SA,  $\overline{LD}$ , R/ $\overline{W}$ , KD,  $\overline{KD}$  input pin values are sampled, logically manipulated, and looped back to DQ, DQINV output pins.

Register bit LBKE is used to enable/disable Loopback Mode. When LBKE = 1 and MRW = 0, Loopback Mode is enabled, and Memory Read and Write operations are blocked regardless of the states of  $\overline{\text{LD}}$  and R/ $\overline{\text{W}}$ . When LBKE = 0 or MRW = 1, Loopback Mode is disabled. See the State Truth Table for more information.

Register bits LBK[1:0] are used to select between the two distinct Loopback Modes supported by the design (controlled by LBK1), and between the two groups of inputs used during the selected Loopback Mode (controlled by LBK0), as follows:

- LBK[1:0] = 00: selects XOR LBK Mode using Input Group 1. Loopback Mode "00".

- LBK[1:0] = 01: selects XOR LBK Mode using Input Group 2. Loopback Mode "01".

- LBK[1:0] = 10: selects INV LBK Mode using Input Group 1. Loopback Mode "10".

- LBK[1:0] = 11: selects INV LBK Mode using Input Group 2. Loopback Mode "11".

**Note**: For convenience, KD clocks have been included in the group of inputs that can be trained via Loopback Mode. However, the timing requirement for KD clocks is that their edges be tightly aligned to CK clock edges, unlike the timing requirement for address/control signals, whose edges must be centered (approximately) between CK edges in order to optimize setup and hold times to those CK edges. Consequently, it is questionable whether Loopback Mode can be used to train KD clocks effectively.

**Note**: When Loopback Mode is enabled, Data Inversion is disabled regardless of the state of register bit DI.

#### Loopback Latency

Loopback Latency ("LBKL") - i.e. the number of cycles from when the inputs are sampled to when the proper result appears on the output pins, is equal to 7 cycles.

#### **Enabling Loopback Mode**

Loopback Mode is enabled as follows:

- Step 1: Initiate a Register Write operation with SA[10:1] = "000ab1.0010" to select Register #2, set LBKE = 1 to enable Loopback Mode, and set LBK[1:0] to "ab" to select Loopback Mode "ab".

- Step 2: Wait 16 cycles for new register settings to take effect.

Loopback Mode "ab" is enabled after step 2 because MRW = 0, LBKE = 1, and LBK[1:0] = "ab".

#### Changing Loopback Modes

Once enabled, Loopback Mode can be changed as follows

- Step 1: Initiate a Register Write operation with SA[10:1] = "000cd1.0010" to select Register #2, keep LBKE = 1 to keep Loopback Mode enabled, and set LBK[1:0] to "cd" to select Loopback Mode "cd".

- Step 2: Wait 16 cycles for new register settings to take effect.

Loopback Mode "cd" is enabled after step 2 because MRW = 0, LBKE = 1, and LBK[1:0] = "cd".

#### Disabling Loopback Mode

Loopback Mode is disabled as follows:

- Step 1: Initiate a Register Write operation with SA[10:1] = "000xx0.0010" to select Register #2 and set LBKE = 0 to disable Loopback Mode.

- Step 2: Wait 16 cycles for new register settings to take effect.

Loopback Mode is disabled after step 2 because LBKE = 0.

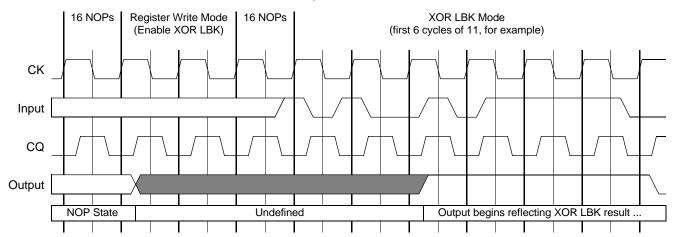

#### XOR LBK Mode

XOR LBK Mode is for address/control input training. It is defined as follows:

- Each input pin of the selected input group is sampled on  $\uparrow$ CK and  $\uparrow$ CK.

- For each input sampled, the value sampled on  $\uparrow$ CK is XORed with the value sampled on  $\uparrow$ CK.

- For each input sampled, the XOR result is subsequently driven out on its associated output pin (concurrently with \(^{\chi}CQ\)) for one full clock cycle, beginning "LBKL" cycles after the input is sampled.

Consequently, the output data pattern is always SDR regardless of the input data pattern, and regardless whether the SRAM samples the inputs correctly or not. The SDR output data pattern enables address/control inputs to be trained before data outputs.

XOR LBK Mode enables the controller to input various SDR and DDR data patterns on a particular input, and then determine whether the SRAM sampled them correctly or not by observing SDR data patterns on the associated output. Via multiple iterations of this process, the controller can adjust its output timing (in order to adjust the SRAM input timing) until optimum setup and hold margin at both SRAM input sample points is achieved, thereby individually "training" each address/control input pin.

### **INV LBK Mode**

INV LBK Mode is primarily for read data output training. It is defined as follows:

- Each input pin of the selected input group is sampled on  $\uparrow$ CK and  $\uparrow$ CK.

- For each input sampled, the value sampled on \(^\text{CK}\) is subsequently driven out on its associated output pin (concurrently with \(^\text{CQ}\)) for half a clock cycle, beginning "LBKL" cycles after the input is sampled.

- For each input sampled, the value sampled on  $\uparrow \overline{CK}$  is *inverted* and then subsequently driven out on its associated output pin (concurrently with  $\uparrow \overline{CQ}$ ) for half a clock cycle, beginning "LBKL + 0.5" cycles after the input is sampled.

Consequently, the output data pattern is DDR if the input data pattern is SDR (and vice versa), provided the SRAM samples the inputs correctly. Therefore, to ensure deterministic output behavior, address/control inputs should be trained before data outputs.

INV LBK Mode enables the controller to input various SDR (or DDR) data patterns on a particular input, to generate deterministic DDR (or SDR) data patterns on a particular output. The controller latches the output as it would during a normal Read operation, and verifies whether it received the expected values or not. Via multiple iterations of this process, the controller can adjust its input timing until optimum setup and hold margin at both controller input sample points is achieved, thereby individually "training" each read data output pin.

**Note**: INV LBK Mode can be used for address/control input training, if desired. However, such usage can be problematic because the output data pattern may be erroneous (i.e. it could be SDR or DDR regardless of the input pattern) if the SRAM samples the input incorrectly. In which case the controller may have difficulty detecting the erroneous behavior, and/or interpreting it.

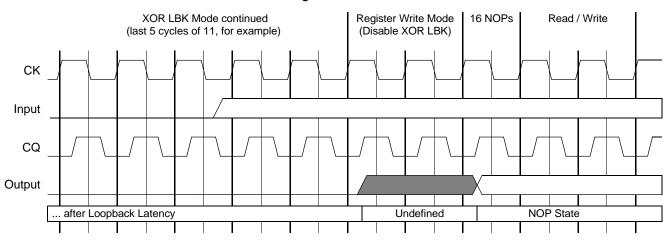

## **Entering XOR LBK Mode**

## **Exiting XOR LBK Mode**

Note: "Input" represents any loop-backed input pin. "Output" represents the output pin on which "Input" is looped back.

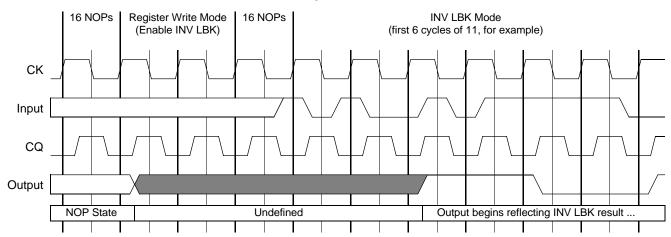

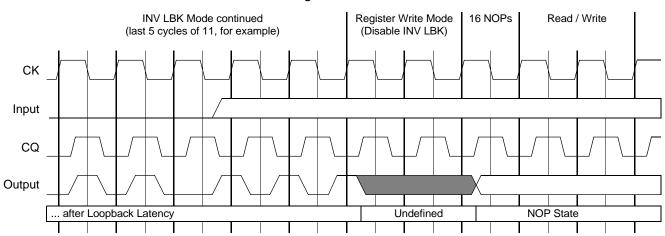

## **Entering INV LBK Mode**

## **Exiting INV LBK Mode**

Note: "Input" represents any loop-backed input pin. "Output" represents the output pin on which "Input" is looped back.

### Loopback Mode Input Group Definition and Input-to-Output Pin Mapping

Inputs are divided into 2 groups because there are up to 28 inputs to train (22 address, 2 control, and 4 KD clocks), but as few as 18 outputs available to loop them back to (in x18 devices).

There are 20 inputs per group - one per DQ, DQINV output in x18 devices, and one per two DQ, DQINV outputs in x36 devices.

| Bit # | Input | Pins | Input Signals |      | Outp | out Pins | Outpu  | ıt Signals |                                |

|-------|-------|------|---------------|------|------|----------|--------|------------|--------------------------------|

| DIL#  | GP1   | GP2  | GP1           | GP2  | x18  | x36      | x18    | x36        |                                |

| 1     | 8T    |      | SA2           | RSVD | n/a  | 12Y      | n/a    | DQINV1     |                                |

| 2     | 8P    | 8V   | SA4           | SA0  | 13V  | 13V, 12W | DQ8    | DQ8, DQ17  |                                |

| 3     | 8M    | 8T   | SA6           | SA2  | 13T  | 13T, 12U | DQ7    | DQ7, DQ16  | e(s)                           |

| 4     | 8J    |      | SA8           | RSVD | 13P  | 13P, 12R | DQ6    | DQ6, DQ15  | Byt                            |

| 5     | 9H    | 9L   | SA16          | KD0  | 13N  | 13N, 12P | DQ5    | DQ5, DQ14  | Right Side Output Data Byte(s) |

| 6     | 8G    | 9K   | SA10          | KD0  | 12J  | 12J, 12M | DQ4    | DQ4, DQ13  | ut D                           |

| 7     | 9F    | 7H   | SA18          | R/W  | 12G  | 12G, 13H | DQ3    | DQ3, DQ12  | Jutp                           |

| 8     | 8E    |      | SA12          | RSVD | 12F  | 12F, 13G | DQ2    | DQ2, DQ11  | de (                           |

| 9     | 9D    |      | SA20          | RSVD | 12D  | 12D, 13E | DQ1    | DQ1, DQ10  | ıt Si                          |

| 10    | 8C    |      | SA14          | RSVD | 12B  | 12B, 13C | DQ0    | DQ0, DQ9   | Righ                           |

| 20    | 6C    |      | SA13          | RSVD | 12A  | 12A      | DQINV0 | DQINV0     |                                |

| 1     | 8T    |      | SA2           | RSVD | 2Y   | 2Y       | DQINV1 | DQINV2     |                                |

| 11    | 6T    |      | SA1           | RSVD | 2W   | 2W, 1V   | DQ9    | DQ18, DQ27 |                                |

| 12    | 6P    | 6V   | SA3           | SA21 | 2U   | 2U, 1T   | DQ10   | DQ19, DQ28 | rte(s                          |

| 13    | 6M    |      | SA5           | RSVD | 2R   | 2R, 1P   | DQ11   | DQ20, DQ29 | a By                           |

| 14    | 6J    | 7N   | SA7           | LD   | 2P   | 2P, 1N   | DQ12   | DQ21, DQ30 | Dat                            |

| 15    | 5H    | 5L   | SA15          | KD1  | 2M   | 2M, 2J   | DQ13   | DQ22, DQ31 | put                            |

| 16    | 6G    | 5K   | SA9           | KD1  | 1H   | 1H, 2G   | DQ14   | DQ23, DQ32 | Left Side Output Data Byte(s)  |

| 17    | 5F    |      | SA17          | RSVD | 1G   | 1G, 2F   | DQ15   | DQ24, DQ33 | ide                            |

| 18    | 6E    |      | SA11          | RSVD | 1E   | 1E, 2D   | DQ16   | DQ25, DQ34 | eft S                          |

| 19    | 5D    | 6C   | SA19          | SA13 | 1C   | 1C, 2B   | DQ17   | DQ26, DQ35 | _                              |

| 20    | 6C    |      | SA13          | RSVD | n/a  | 2A       | n/a    | DQINV3     |                                |

- 1. Blue shading indicates input pins that are unused (NU) in certain device configurations. During Loopback Mode, the associated output pins loop back the states of those input pins regardless whether they are used or unused.

- 2. Gray shading indicates Group 2 inputs that are reserved (RSVD) for future use. During Loopback Mode, the associated output pins act as if they were looping back input pins tied Low.

- 3. Green shading indicates DQINV output pins that are unused (NU) when Data Inversion is disabled. During Loopback Mode, they loop back the states of the associated input pins regardless whether Data Inversion is enabled or disabled.

- 4. The 18 unused DQ and the 2 unused DQINV in x18 devices remain in their "NU" states during Loopback Mode.

- 5. Bit #1 and bit #20 are repeated in the table to show that they are used in both the right and left side data bytes in x36 devices.

## **Address Bus Utilization**

The address bus is a non-multiplexed SDR bus. One memory address may be loaded per cycle - a read address at  $\uparrow$ CK or a write address at  $\uparrow$ CK; consequently only one memory operation - a Read or a Write - may be initiated per clock cycle. The address bus is also sampled at  $\uparrow$ CK during a Register Write operation.

## Address Bit Encoding

| Command  | Addr | Device |    | SA Address Bits |    |    |    |    |    |    |    |    |    |       |    |        |       |    |   |   |       |        |   |   |

|----------|------|--------|----|-----------------|----|----|----|----|----|----|----|----|----|-------|----|--------|-------|----|---|---|-------|--------|---|---|

| Communa  | Load | Dovido | 21 | 20              | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10    | 9  | 8      | 7     | 6  | 5 | 4 | 3     | 2      | 1 | 0 |

| Read     | ↑CK  | x36    | NU | Address Address |    |    |    |    |    |    |    |    |    |       |    |        |       |    |   |   |       |        |   |   |

| Reau     | TOR  | x18    |    | Address         |    |    |    |    |    |    |    |    |    |       |    |        |       |    |   |   |       |        |   |   |

| Write    | ↑CK  | x36    | NU |                 |    |    |    |    |    |    |    |    | А  | ddres | SS |        |       |    |   |   |       |        |   |   |

| wille    | TCK  | x18    |    | Address         |    |    |    |    |    |    |    |    |    |       |    |        |       |    |   |   |       |        |   |   |

| Register | ↑CK  | x36    | NU | Χ               | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  | Х  | Χ  |       | Re | egiste | er Da | ta |   |   | Regis | ster # | ŧ | Х |

| Write    | IUN  | x18    | Χ  | Χ               | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |       | Re | egiste | er Da | ta |   |   | Regis | ster # | ŧ | Х |

#### **Data Bus Inversion**

Because the POD I/O standard employs high-side (pull-up) termination only, signals driven High consume less power than those driven Low. Consequently, these devices provide the ability to invert all data pins on a per byte basis, such that any transmitted data byte always contains more 1s than 0s, thereby reducing average I/O power as well as SSO noise. To accomplish this, one data inversion (DQINV) bit is utilized per 9-bit data (DQ) byte.

During Write operations, the controller inverts a particular 9-bit write data byte before transmitting it to the SRAM if it contains less than 5 High bits; otherwise, it transmits the data byte uninverted. If it inverts the data byte, the controller drives the corresponding write data inversion bit High; otherwise, it drives it Low. Upon receiving the write data byte, the SRAM uses the state of the corresponding write data inversion bit to determine whether or not to invert the data byte before storing it in the memory array.

During Read operations, the SRAM inverts a particular 9-bit read data byte before transmitting it to the controller if it contains less than 5 High bits; otherwise, it transmits the data byte uninverted. If it inverts the data byte, the SRAM drives the corresponding read data inversion bit High; otherwise, it drives it Low. Upon receiving the read data byte, the controller uses the state of the corresponding read data inversion bit to determine whether or not to invert the data byte before utilizing it.

With this implementation, each 10-bit data group (nine data bits plus one data inversion bit) is guaranteed to have no more than five pins driven low at any given time. Consequently, no more than five pins in each group can switch in the same direction during each bit time, reducing SSO noise effects.

Note: Data Inversion can be enabled and disabled via register bit DI.

### Read Latency

Read Latency (i.e. the number of cycles from read command input to first read data output) is specified as follows:

| Read Latency | Comment                                                  |

|--------------|----------------------------------------------------------|

| 5 cycles     | First read data output 5 cycles after read command input |

**Note**: The RLM register bit must be written to "0" in these devices prior to initiating Read operations, to set Read Latency = 5 cycles.

### Write Latency

Write Latency (i.e. the number of cycles from write command input to first write data input) is specified as follows:

| Write Latency | Comment                                                    |

|---------------|------------------------------------------------------------|

| 0 cycles      | First write data input concurrent with write command input |

#### Read / Write Coherency

These devices are fully coherent. That is, Read operations always return the most recently written data to a particular address, even when a Read operation to a particular address occurs one cycle after a Write operation to the same address.

#### State Truth Table

| RST | MRW | LBKE | LD | R/W   | SA         | DQ (D)  | SRAM State          | DQ (Q)          |

|-----|-----|------|----|-------|------------|---------|---------------------|-----------------|

| 1   | Х   | Х    | Χ  | Х     | Χ          | Х       | Reset               | NOP State       |

| 0   | 1   | Х    | 0  | Х     | V          | Х       | Register Write Mode | Undefined       |

| 0   | 0   | 1    | Х  | Х     | Х          | Х       | Loopback Mode       | Loopback        |

| 0   | 1   | Χ    | 1  | S00 C | lock Truth | Table   | Memory Mode         | See Clock Truth |

| 0   | 0   | 0    | Х  | 366.0 | IUCK IIUU  | I IANIE | (Read, Write, NOP)  | Table           |

Note: 1 = High; 0 = Low; V = Valid; X = don't care.

### **Clock Truth Table**

| SA                       | MRW                      | LD                       | R/W                      | Current Operation | DQ, DC                   | INV (D)                                | DQ, DQ                     | (D) VNI                                 |

|--------------------------|--------------------------|--------------------------|--------------------------|-------------------|--------------------------|----------------------------------------|----------------------------|-----------------------------------------|

| ↑CK<br>(t <sub>n</sub> ) | ↑CK<br>(t <sub>n</sub> ) | ↑CK<br>(t <sub>n</sub> ) | ↑CK<br>(t <sub>n</sub> ) | (t <sub>n</sub> ) | ↑KD<br>(t <sub>n</sub> ) | ↑ <del>KD</del><br>(t <sub>n+½</sub> ) | ↑CQ<br>(t <sub>n+5</sub> ) | ↑ <del>CQ</del><br>(t <sub>n+5½</sub> ) |

| V                        | Х                        | 1                        | Χ                        | NOP               | Χ                        | Х                                      | Hi-Z /                     | other                                   |

| V                        | 0                        | 0                        | 0                        | Write             | D1                       | D2                                     | Hi-Z /                     | other                                   |

| V                        | 0                        | 0                        | 1                        | Read              | Х                        | Х                                      | Q1                         | Q2                                      |

| V                        | 1                        | 0                        | Х                        | Register Write    | Х                        | Х                                      | Unde                       | efined                                  |

- 1. 1 = High; 0 = Low; V = Valid; X = don't care.

- 2. D1 and D2 indicate the first and second pieces of write data transferred during Write operations.

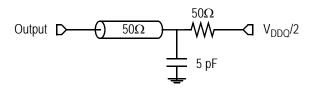

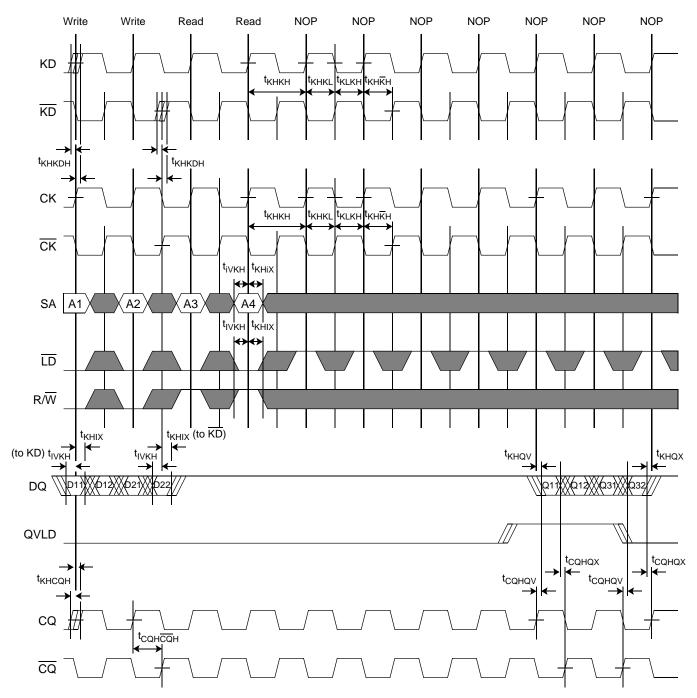

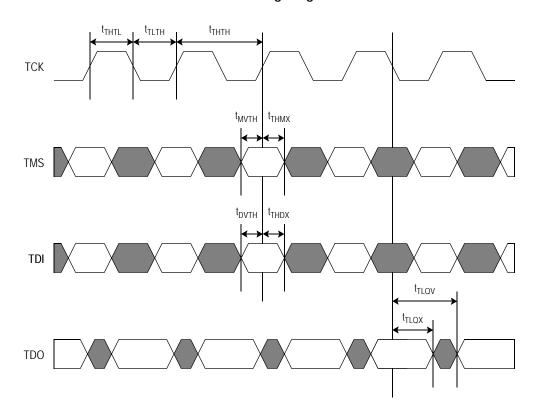

- 3. Q1 and Q2 indicate the first and second pieces of read data transferred during Read operations.