# Am2148/Am2149 Am21L48/Am21L49

1024x4 Static RAM

## DISTINCTIVE CHARACTERISTICS

- High speed access times as fast as 35 ns

- Fully static storage and interface circuitry

- Automatic power-down when deselected (Am2148)

- TTL-compatible interface levels

- Low power dissipation

- Am2148: 990 mW active, 165 mW power down

- Am21L48: 688 mW active, 110 mW power down

- High output drive

- Up to seven standard TTL loads

### **GENERAL DESCRIPTION**

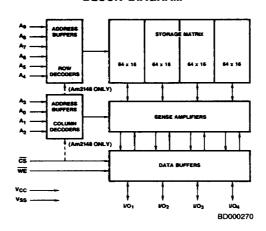

The Am2148 and Am2149 are high-performance, static, N-Channel, read/write, random-access memories, organized as 1024 x 4. Operation is from a single 5-V supply, and all input/output levels are identical to standard TTL specifications. The Am2148 and Am2149 are the same except that the Am2149 offers an automatic S power-down feature.

The Am2148 remains in a low-power standby mode as long as  $\overline{\text{CS}}$  remains HIGH, thus reducing its power requirements.

The Am2148 power decreases from 990 mW to 165 mW in the standby mode. The  $\overline{\text{CS}}$  input does not affect the power dissipation of the Am2149.

Data readout is not destructive and has the same polarity as data input.  $\overline{CS}$  provides for easy selection of an individual package when the outputs are OR-tied.

#### **BLOCK DIAGRAM**

### PRODUCT SELECTOR GUIDE

| Part Number  Maximum Access Time (ns) |         | Am2148/9<br>-35 | Am2148/9<br>-45 | Am21L48/9<br>-45 | Am2148/9<br>-55 | Am21L48/9<br>-55 | Am2148/9<br>-70 | Am21L48/9<br>-70 |  |

|---------------------------------------|---------|-----------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|--|

|                                       |         | 35 45           | 45              | 45               | 55              | 55               | 70              | 70               |  |

| I <sub>CC</sub> Max. (mA)             | 0 to    | 180             | 180             | 125              | 180             | 125              | 180             | 125              |  |

| I <sub>SB</sub> * Max. (mA)           | + 70°C  | 30              | 30              | 20               | 30              | 20               | 30              | 20               |  |

| Icc Max. (mA)                         | -55 to  | N/A             | 180             | N/A              | 180             | N/A              | 180             | N/A              |  |

| I <sub>SB</sub> * Max. (mA)           | + 125°C | N/A             | 30              | N/A              | 30              | N/A              | 30              | N/A              |  |

<sup>\*</sup>Am2148 and Am21L48 only.

Publication # Rev. Amendment 03210 F /0 Issue Date: January 1989

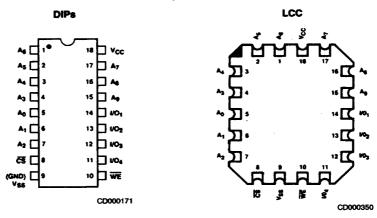

# CONNECTION DIAGRAMS Top View

Note: Pin 1 is marked for orientation.

# **METALLIZATION AND PAD LAYOUT**

| Address Designators |                |  |  |  |  |  |  |

|---------------------|----------------|--|--|--|--|--|--|

| External            | Internal       |  |  |  |  |  |  |

| Ao                  | A <sub>7</sub> |  |  |  |  |  |  |

| A <sub>1</sub>      | A <sub>8</sub> |  |  |  |  |  |  |

| A <sub>2</sub>      | A <sub>9</sub> |  |  |  |  |  |  |

| A3                  |                |  |  |  |  |  |  |

| A4                  | A <sub>5</sub> |  |  |  |  |  |  |

| A <sub>5</sub>      | A4             |  |  |  |  |  |  |

| A <sub>6</sub>      | A3             |  |  |  |  |  |  |

| A <sub>7</sub>      | A <sub>2</sub> |  |  |  |  |  |  |

| A <sub>8</sub>      | A <sub>1</sub> |  |  |  |  |  |  |

| Ag                  | A <sub>0</sub> |  |  |  |  |  |  |

Die Size: 0.107" x 0.145"

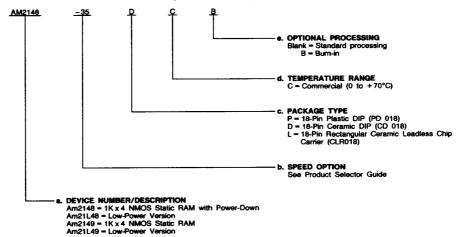

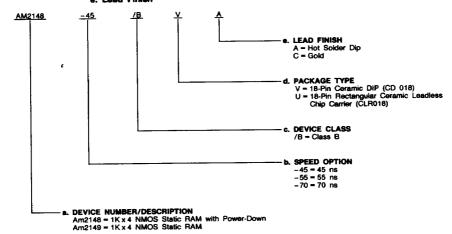

#### ORDERING INFORMATION

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid      | Valid Combinations  AM2148-35  AM2149-35  AM21L48-45  AM21L48-45  AM21L48-55  AM21L49-55  AM21L49-70  AM2148-45  AM2149-45  AM2149-45  AM2149-55  AM2149-55  AM2149-55  AM2149-55  AM2149-55  AM2149-55  CC  CB |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AM2148-35  |                                                                                                                                                                                                                 |  |  |

| AM2149-35  |                                                                                                                                                                                                                 |  |  |

| AM21L48-45 |                                                                                                                                                                                                                 |  |  |

| AM21L49-45 |                                                                                                                                                                                                                 |  |  |

| AM21L48-55 |                                                                                                                                                                                                                 |  |  |

| AM21L49-55 |                                                                                                                                                                                                                 |  |  |

| AM21L48-70 |                                                                                                                                                                                                                 |  |  |

| AM21L49-70 |                                                                                                                                                                                                                 |  |  |

| AM2148-45  |                                                                                                                                                                                                                 |  |  |

| AM2149-45  |                                                                                                                                                                                                                 |  |  |

| AM2148-55  |                                                                                                                                                                                                                 |  |  |

| AM2149-55  | LC, LCB                                                                                                                                                                                                         |  |  |

| AM2148-70  | 7                                                                                                                                                                                                               |  |  |

| AM2149-70  |                                                                                                                                                                                                                 |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

# MILITARY ORDERING INFORMATION APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid C                                                                                                                        | Valid Combinations |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|--|--|

| AM2148-45                                                                                                                      |                    |  |  |  |  |  |  |

| AM2149-45                                                                                                                      |                    |  |  |  |  |  |  |

| AM2148-55                                                                                                                      | /BVA               |  |  |  |  |  |  |

| AM2149-55                                                                                                                      | 784                |  |  |  |  |  |  |

| AM2148-70                                                                                                                      |                    |  |  |  |  |  |  |

| AM2149-70                                                                                                                      |                    |  |  |  |  |  |  |

| AM2148-45                                                                                                                      |                    |  |  |  |  |  |  |

| AM2149-45                                                                                                                      |                    |  |  |  |  |  |  |

| AM2148-45<br>AM2148-55<br>AM2149-55<br>AM2148-70<br>AM2149-70<br>AM2148-45<br>AM2149-45<br>AM2148-55<br>AM2148-55<br>AM2148-70 | /BUC               |  |  |  |  |  |  |

|                                                                                                                                | 7800               |  |  |  |  |  |  |

| AM2148-70                                                                                                                      |                    |  |  |  |  |  |  |

| AM2149-70                                                                                                                      |                    |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A Tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

# PIN DESCRIPTION

A<sub>0</sub>-A<sub>9</sub> Address Inputs

The address input lines select the RAM location to be read or written.

CS Chip Select (Input, Active LOW)

The Chip Select selects the memory device.

The Chip Select selects the memory device

WE Write Enable (input, Active LOW)

When WE is LOW and CS is also LOW, data is written into

the location specified on the address pins.

i/O<sub>1</sub>-I/O<sub>4</sub> Data in/Out Bus (Bidirectional, Active HIGH)

These I/O lines provide the path for data to be read from or written to the selected memory location.

V<sub>CC</sub> Power Supply

V<sub>SS</sub> Ground

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature      | 65 to +150°C    |

|--------------------------|-----------------|

| Ambient Temperature with |                 |

| Power Applied            | 55 to +125°C    |

| Supply Voltage           | 0.5 V to +7.0 V |

| Signal Voltages with     |                 |

| Respect to Ground        | 3.5 V to +7.0 V |

| Power Dissipation        | 1.2 W           |

| DC Output Current        | 20 mA           |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

Absolute Maximum Ratings are for system-design reference; parameters given are not 100% tested.

#### **OPERATING RANGES**

| Commercial (C) Devices Ambient Temperature (T <sub>A</sub> ) | 0 to +70°C   |

|--------------------------------------------------------------|--------------|

| Supply Voltage (VCC)                                         |              |

| Military (M) Devices                                         |              |

| Ambient Temperature (TA*)                                    | 55 to +125°C |

| Supply Voltage (VCC)                                         |              |

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*TA is defined as the "instant on" case temperature.

DC CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Davameter           |                             |                                                                                       |                                                |      | dard      | Low Power |      | Í    |

|---------------------|-----------------------------|---------------------------------------------------------------------------------------|------------------------------------------------|------|-----------|-----------|------|------|

| Parameter<br>Symbol | Parameter<br>Description    | Test                                                                                  | Min.                                           | Max. | Min.      | Max.      | Unit |      |

| Юн                  | Output HIGH Current         | V <sub>OH</sub> = 2.4 V                                                               | V <sub>CC</sub> = 4.5 V                        | -4   |           | -4        |      | mA   |

| loL                 | Output LOW Current          | 1, 4, 4                                                                               | T <sub>A</sub> = 70°C                          | - 8  |           | 8         |      | mA   |

|                     |                             | V <sub>OL</sub> = 0.4 V                                                               | T <sub>A</sub> = 125°C                         | 8    | Ι         | N/A       |      | IIIA |

| VIH                 | Input HIGH Voltage          |                                                                                       |                                                | 2.0  | 6.0       | 2.0       | 6.0  | ٧    |

| VIL                 | Input LOW Voltage           |                                                                                       |                                                | -0.5 | 0.8       | -0.5      | 0.8  | ٧    |

| ŧιχ                 | Input Load Current          | V <sub>SS</sub> ≤ V <sub>1</sub> ≤ V <sub>CC</sub>                                    |                                                | -10  | 10        |           | 10   | μА   |

| loz                 | Output Leakage<br>Current   | GND < V <sub>O</sub> < V <sub>CC</sub> Output Disabled  T <sub>A</sub> = -55 to+125°C |                                                | -50  | 50        | -50       | 50   | μΑ   |

| CI                  | Input Capacitance           | Test Frequency = 1.0                                                                  |                                                | 5    |           | 5         | ρF   |      |

| C <sub>I/O</sub>    | Input/Output<br>Capacitance | T <sub>A</sub> = 25°C, All Pins a<br>(Note 12)                                        | $T_A = 25$ °C, All Pins at 0 V, $V_{CC} = 5$ V |      |           |           | 7    |      |

| loc                 | V <sub>CC</sub> Operating   | Max. V <sub>CC</sub> , CS < V <sub>IL</sub>                                           | TA = 0 to+ 70°C                                |      | 180       |           | 125  | mΑ   |

| -α.                 | Supply Current              | Output Open                                                                           | T <sub>A</sub> = -55 to+125°C                  |      | 180       |           | N/A  |      |

|                     | Automatic CS Power          | Max. V <sub>CC</sub>                                                                  | T <sub>A</sub> = 0 to+70°C                     |      | 30        |           | 20   | mA   |

| ISB                 | Down Current                | (CS > VIH)                                                                            | T <sub>A</sub> = -55 to+125°C                  |      | 30        |           | N/A  | HIP  |

|                     | Peak Power-On               | Max. Voc.                                                                             | T <sub>A</sub> = 0 to+70°C                     |      | 50        |           | 30   |      |

| l <sub>PO</sub>     | Current                     | (CS > V <sub>IH</sub> )<br>(Notes 3 & 12)                                             | T <sub>A</sub> = -55 to+125°C                  | 50   |           | N/A       | mA   |      |

| los                 | Output Short-Circuit        | GND < VO < VCC                                                                        | TA = 0 to+70°C                                 |      | ±275      |           | ±275 | mA   |

| ·US                 | Current                     | (Notes 11, 12)                                                                        | T <sub>A</sub> = -55 to+125°C                  |      | ±350 ±350 |           | ±350 | ]    |

- Notes: 1. Test conditions assume signal transition times of 10 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V and output loading of the specified to //oH and 30 pF load capacitance. Output timing reference is 1.5 V.

- 2. The internal write time of the memory is defined by the overlap of CS LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write

- 3. A pullup resistor to VCC on the CS input is required to keep the device deselected during VCC power up. Otherwise Ipo will exceed values given (Am2148 only).

- 4. The operating ambient temperature is defined as the "instant-ON" case temperature.

- 5. Chip deselected greater than 55 ns prior to selection.

- 6. Chip deselected less than 55 ns prior to selection.

- 7. Transition is measured ±500 mV from steady state voltage with specified loading in Figure B. These parameters are sampled and not 100% tested. 8. WE is HIGH for read cycle.

- Device is continuously selected, CS = V<sub>IL</sub>.

Address valid prior to or coincident with CS transition LOW.

- 11. For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds

- 12. This parameter is sampled and not 100% tested, but guaranteed by characterization.

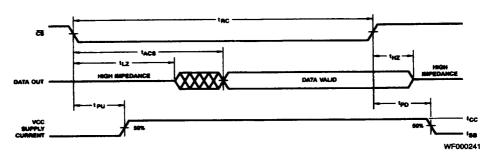

# **SWITCHING CHARACTERISTICS** over operating range unless otherwise specified (Note 1) (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

|     |                                           |                                                                |            | Am2148/9-35 |      | Am2148/9-45<br>Am21L48/9-45 |      | Am2148/9-55<br>Am21L48/9-55 |      | Am2148/9-70<br>Am21L48/9-70 |      |     |

|-----|-------------------------------------------|----------------------------------------------------------------|------------|-------------|------|-----------------------------|------|-----------------------------|------|-----------------------------|------|-----|

| No. | Parameter Parameter b. Symbol Description |                                                                | Min.       | Max.        | Min. | Max.                        | Min. | Max.                        | Min. | Max.                        | Unit |     |

| A   | ead Cycle                                 |                                                                |            |             |      |                             |      |                             |      | _                           |      |     |

| 1   | <sup>t</sup> RC                           | Address Valid to Address Do Not Care<br>Time (Read Cycle Time) |            | 35          |      | 45                          |      | 55                          |      | 70                          |      | ns  |

| 2   | taa .                                     | Address Valid to Data Out Valid De<br>(Address Access Time)    | lay        |             | 35   |                             | 45   |                             | 55   |                             | 70   | ns  |

| 3   | t <sub>ACS1</sub>                         | Chip Select LOW to Data Out                                    | (Note 5)   |             | 35   |                             | 45   |                             | 55   |                             | 70   | ns  |

| 4   | 1ACS2                                     | Valid (Am2148 only)                                            | (Note 6)   |             | 45   |                             | 55   |                             | 65   |                             | 80   | 114 |

| 5   | 1 <sub>ACS</sub>                          | Chip Select LOW to Data Out Valid (Am2149 only)                |            |             | 15   |                             | 20   |                             | 25   |                             | 30   | ns  |

|     |                                           | Chip Select LOW to                                             | Am2148     | 10          |      | 10                          |      | 10                          |      | 10                          |      | ns  |

| 6   | 1LZ                                       | Data Out On (Notes 7 & 12)                                     | Am2149     | 5           |      | 5                           |      | 5                           |      | 5                           |      | 20  |

| 7   | tHZ                                       | Chip Select HIGH to Data Out Off (Notes 7 & 12)                |            | 0           | 20   | 0                           | 20   | 0                           | 20   | 0                           | 20   | ns  |

| 8   | tон                                       | Output hold after address change                               |            | 5           |      | 5                           |      | 5                           |      | 5                           |      | ns  |

| 9   | tPD                                       | Chip Select HIGH to Power Down<br>Delay (Note 12)              | Am2148     |             | 30   |                             | 30   |                             | 30   |                             | 30   | ns  |

| 10  | tpU                                       | Chip Select LOW to Power Up<br>Delay (Note 12)                 | Am2148     | 0           |      | 0                           |      | 0                           |      | 0                           |      | ns  |

| V   | Vrite Cycle                               |                                                                |            |             |      |                             |      |                             |      |                             |      |     |

| 11  | twc                                       | Address Valid to Address Do Not C<br>Cycle Time)               | are (Write | 35          |      | 45                          |      | 55                          |      | 70                          |      | ns  |

| 12  | t <sub>WP</sub>                           | Write Enable LOW to Write Enable HIGH (Note 2)                 |            | 30          |      | 35                          |      | 40                          |      | 50                          |      | ns  |

| 13  | †WR                                       | Write Enable HIGH to Address                                   |            | 5           |      | 5                           |      | 5                           |      | 5                           |      | ns  |

| 14  | twz                                       | Write Enable LOW to Output in Hig<br>(Notes 7 & 12)            | hΖ         | 0           | 10   | 0                           | 15   | 0                           | 20   | 0                           | 25   | ns  |

| 15  | tow                                       | Data In Valid to Write Enable HIGH                             | Ī          | 20          |      | 20                          |      | 20                          |      | 25                          |      | ns  |

| 16  | t <sub>DH</sub>                           | Data Hold Time                                                 |            | 0           |      | 0                           |      | 0                           |      | 0                           |      | ns  |

| 17  | tas                                       | Address Valid to Write Enable LOW                              |            | 0           |      | 0                           |      | 0                           |      | 0                           |      | ns  |

| 18  | tcw                                       | Chip Select LOW to Write Enable H<br>(Note 2)                  | ligh       | 30          |      | 40                          |      | 50                          |      | 65                          |      | ns  |

| 19  | tow                                       | Write Enable HIGH to Output in Low Z (Notes 7 & 12)            |            | 0           |      | 0                           |      | 0                           |      | 0                           |      | ns  |

| 20  | taw                                       | Address Valid to End of Write                                  |            | 30          |      | 40                          |      | 50                          |      | 65                          |      | ns  |

Notes: See notes following DC Characteristics table.

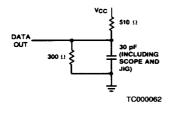

### SWITCHING TEST CIRCUITS

A. Output Load

B. Output Load for tHZ, tLZ, tOW, tWZ

# SWITCHING WAVEFORMS KEY TO SWITCHING WAVEFORMS

DATA OUT PREVIOUS DATA VALID WF000461

Read Cycle No. 1 (Notes 8, 9)

Read Cycle No. 2 (Notes 8, 10)

Notes: See notes following DC Characteristics table.

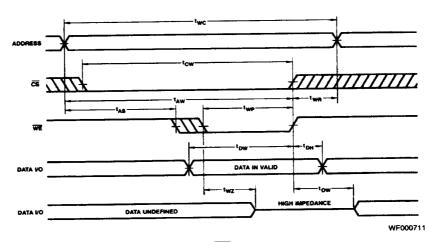

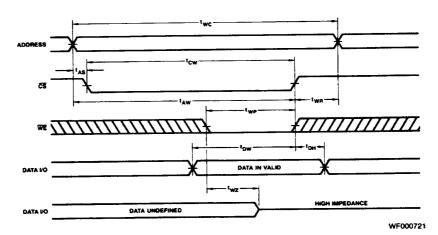

# SWITCHING WAVEFORMS (Cont'd.)

Write Cycle No. 1 (WE Controlled)

Write Cycle No. 2 (CS Controlled)

Note: If CS goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state.

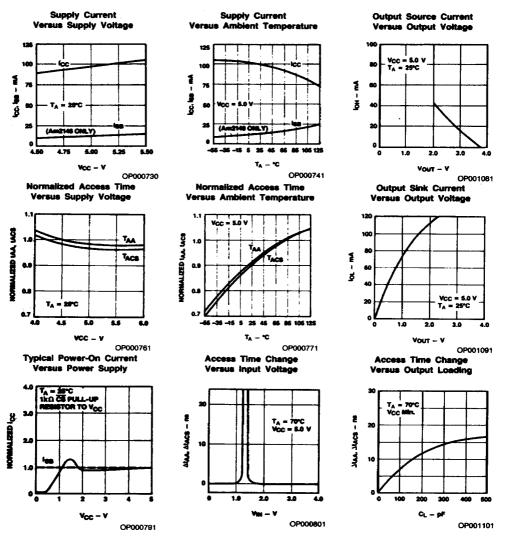

## TYPICAL PERFORMANCE CURVES