**Preliminary**

August 2002 Revision 2.2

# Geode™ CS1301/CS1311 Multimedia Companion: Media Coprocessor

### **General Description**

The National Semiconductor<sup>®</sup> Geode<sup>™</sup> CS1301 and CS1311 multimedia companions act as coprocessors to decode multimedia in National's Geode single chip processor-based systems (i.e., SC1200/SC1201, SC2200, and SC3200, hereafter referred to as SCx200). They provide a multimedia experience for an Information Appliance (IA) user that cannot typically be achieved on a PC.

By implementing a dedicated coprocessor to perform multimedia tasks, a high quality video viewing experience can be achieved. This high quality is achieved by having a coprocessor architecture that is ideally suited for decoding digital media. In addition, since the decoding is not occurring on the SCx200, system events cannot interrupt the coprocessor's task of decoding media and thereby causing stuttering of sound or interruptions in the video.

Lower power consumption can also be achieved using the SCx200/CS1301 or SCx200/CS1311 solution. The CS1301/CS1311 has an architecture specifically designed for decoding media. The architecture is such that while decoding media, power is not consumed by portions of the system that are not used to decode media. Since the SCx200 is not decoding the media locally, it is able to go into a lower power state. When the CS1301/CS1311 is not decoding media, it uses almost no power.

Additionally, since the architecture is designed for decoding media, fewer CS1301/CS1311 cycles are required.

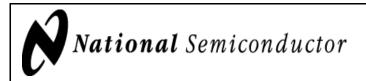

### **Internal Block Diagram**

1

National Semiconductor and Virtual System Architecture are registered trademarks of National Semiconductor Corporation. Geode, MacPHYTER, WebPAD, and VSA are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

### **Features**

#### **General Features**

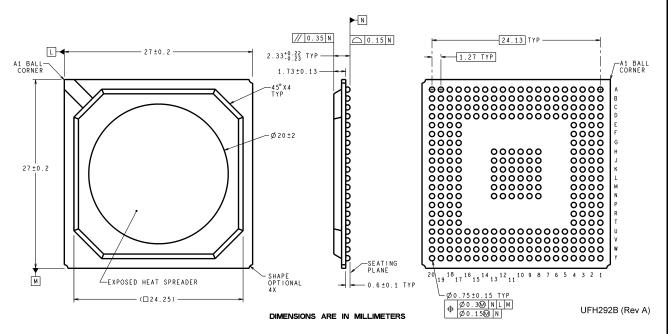

- Physical

- Process 0.25-micron CMOS

- Packaged in a 292-terminal TEPBGA (Thermally Enhanced Plastic Ball Grid Array)

- Power supply:

- CS1301: 2.5V Core; 3.3V I/O (5V tolerant)

- CS1311: 2.2V Core; 3.3V I/O (5V tolerant)

- Consumption 1300 mA; 3.5W

- Power-down 300 mA

- Case Temperature 0° to 85°C

### **Central Processing Unit**

- Clock speed:

- CS1301: 180 MHz— CS1311: 166 MHz

- Instruction length variable (2 to 23 bytes)

- Instruction set arithmetic and logical operations, load/store operations, special multimedia and DSP operations, IEEE compliant floating point operations

- Functional units 27, pipelined

#### **Caches**

■ Data 16 KB, instructions 32 KB

### **Memory System**

- Speed 166 MHz SDRAM

- CPU/Memory programmable; 1:1, 5:4, 4:3, 3:2, and 2:1 speed ratios

- Memory size 512 KB to 64 MB (up to four banks)

- Recommended configurations:

- 16 MB: Two 4M x 16 or two 2M x 32

- 32 MB: Four 2M x 32 or four 4M x 16

- Width 32-bit bus

- Max. bandwidth 664 MB/sec (at 166 MHz)

### **Image Coprocessor**

- Scaling programmable scale factor (0.2X to 10X) using 5-tap filters:

- Horizontal or vertical scaling and filtering of individual Y, U or V

- Horizontal scaling and filtering with color conversion and overlay

- HYUV to RGB, RGB overlay and alpha blending, bit mask blanking

#### **VLD Coprocessor**

Parses MPEG-1 and MPEG-2 elementary bit streams generating run-level pairs and filling macroblock headers

#### **Timers**

■ Four 32-bit wide timers

### **Input/Output Support**

- PCI Interface:

- PCI 2.1 compliant

- Speed 33 MHz

- Bus width 32 bits

- Voltage drive and receive at 3.3V

- Audio In (AI):

- Two I<sup>2</sup>S compliant channels

- Sample size 8 or 16-bit samples per channel

- Audio Out (AO):

- Eight I<sup>2</sup>S compliant channels

- Sample size 16 or 32-bit samples per channel

- Video In (VI):

- Supported signals CCIR-601/656:

- 8-bit video (up to 40 Mpix/sec)

- Image sizes all sizes, subject to sample rate

- Provides programmable on-the-fly 2X horizontal resolution subsampling

- Video Out (VO):

- Image sizes flexible, including CCIR-601; max.

4K x 4K pixels (subject to 80 MB/sec data rate)

- Outputs CCIR-601/656 8-bit video, PAL or NTSC

- Clock rates programmable (4-80 MHz), typical 27 MB/sec (13.5 Mpix/sec for NTSC, PAL; 40 Mpix/sec in YUV 4:2:2 mode)

- Features full 129-level alpha blending, GenLock mode, frame synchronization chroma key, programmable YUV color clipping

- S/PDIF Out:

- Number of channels up to 6

- Sample size 16 or 24 bits per channel

- IEC-958, output up to 40 Mbits/sec

- ACCESS.bus Interface:

- Supported modes single master only

- Addressing 7-bit

- Rates up to 400 Kbps

### 1.0 System Architecture

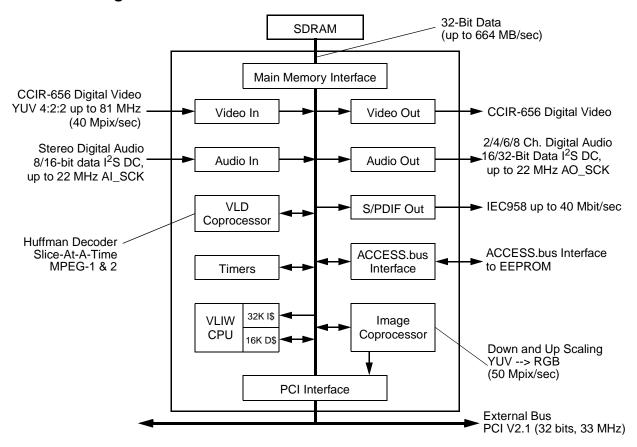

The CS1301/CS1311 multimedia companion acts as a coprocessor to decode multimedia in National's Geode SC1200/SC1201, SC2200, and SC3200 (SCx200 unless otherwise specified). Figure 1-1 provides a typical system block diagram.

Media decoding is one of the most demanding system applications. If media is decoded on the main processor, a much higher performance processor is required to achieve even comparable levels of media decoding quality. Such a system would be significantly over-designed for other tasks, such as browsing the Internet. Using a low-cost processor that is ideally suited for all tasks, and adding the coprocessor for the high performance media decoding requirement, results in a cost-effective solution.

Another advantage of an processor/coprocessor solution is that an OEM (Original Equipment Manufacturer) can provide a scalable solution. A single board can be designed that supports the coprocessor. If it is desired to support a low-end product that does not support the high quality media decoding capabilities, the coprocessor and its supporting components can be excluded from the system, which results in additional savings in an already cost-effective design.

#### 1.1 IMPORTANT DESIGN NOTE

The CS1301/CS1311 was designed to be a general purpose media data processor. As such, the CS1301/CS1311 is capable of far more than the current National CS1301/CS1311 solution. The solution that National is providing is only one possible implementation of the CS1301/CS1311 and only this implementation is fully supported by National Semiconductor. In order to maintain software compatibility with National's provided software, any deviation of the CS1301/CS1311 section of the schematic is strongly discouraged.

For those wishing to deviate from the schematic, or wishing to take advantage of other features of the CS1301/CS1311, documentation is available on the Philips Semiconductors SDE CD-ROM to support design variations. However, additional support to implement these variations must be obtained from one of the TriMedia Alliance Partners who support the CS1301/CS1311, its software, and the peripheral functions.

For a list of TriMedia Alliance Partners, visit: <a href="http://www.trimedia.com/TAPP/">http://www.trimedia.com/TAPP/</a>

Figure 1-1. System Block Diagram

### System Architecture (Continued)

#### 1.2 SOFTWARE

The CS1301/CS1311 software and reference schematic is provided for a system that decodes media quickly with no original software development needed. As part of the CS1301/CS1311 purchase (see Section A.1 "Ordering Information" on page 24 for purchase details), National will license for the use of the operating system drivers and media decoder codecs in object form, which include:

- · Communications manager driver.

- Video filter: Takes the video from the VIP (Video Input Port) of the Geode SCx200 and plays it back through the operating system media player.

- · Various multimedia codecs.

### 1.2.1 Software Support

National provides a reference schematic and the associated software for a processor/coprocessor solution using the Geode SCx200 and the CS1301/CS1311. This implementation is currently supplied as a multimedia decoder for CE player under Microsoft Windows CE.net or Linux. Future support for Microsoft Windows XP is planned. Since this is a software-based DSP (Digital Signal Processor) coprocessor rather than strictly a silicon-based coprocessor, the software can be upgraded to support evolving media standards without a redesign of the hardware.

### 1.2.2 Software Features Support

The CS1301/CS1311 multimedia solution supports the following software components:

#### **General Support**

- Reverse 3:2 pull down

- · Progressive display output

- Capture Video Input

### **MPEG-1 Decoding**

- System stream (ISO 11172-1):

- Up to 1.5 Mbps

- Video stream (ISO 11172-2):

- CIF (up to 360x288) resolution

- 29.97 fps (NTSC)

- 25 fps (PAL)

- Up to 1.12 Mbps

- Audio stream (ISO 11172-3): MPEG-1 layers 1 and 2:

- Up to 384 Kbps, 32 KHz, 44.1 KHz or 48 KHz sample rate

### **MPEG-2 Decoding**

- Program stream (ISO 13818-1): DVD style MPEG-2 program stream

- Video stream (ISO 13818-2) Main level at main profile:

- Full screen NTSC (720x480) at 29.97 fps

- Full screen PAL (720x576) at 25 fps

- · Audio stream MPEG-2 audio:

- Layers 1 and 2 (ISO 13818-3) at 32 KHz, 44.1 KHz or 48 KHz sample rate

- AC3 audio at 32 KHz, 44.1 KHz or 48 KHz sample rate

### MPEG-1, MPEG-2 Layer 3 Audio Decoding (MP3)

- Up to 384 Kbps

- Up to 48 KHz sample rate

- · Fixed bit rate decoding

### **MPEG-4 Decoding**

- Video stream "Simple profile":

- CIF resolution at 30 fps, up to 384 Kbps

- Audio stream "High quality profile":

- MPEG-4 AAC low complexity and MPEG-4 CELP

### WMT (Windows Media Technology) Decoding

- Video stream Windows Media Video v8, also supports v7 decode:

- CIF resolution at 30 fps, up to 1 Mbps

- Audio stream Windows Media Audio v8, also supports v7 decode:

- Up to 128 Kbps and 48 KHz sample rate

### **Windows Media Player Integration**

An implementation has been developed to seamlessly integrate Windows Media Player with WindowsCE.net or Linux. National has taken advantage of the native playback features supported by Microsoft DirectShow and has extended that functionality to the CS1301/CS1311. WindowsCE.net ships with an ActiveX control that wraps the filter graph manager and provides a very high level API (Application Programming Interface). It also supports a browser plug-in. An application writer can use the ActiveX control interface to playback MPEG-1/MPEG-2 media types. The user can also open the MPEG-1/MPEG-2/WMT files in Windows Media Player by double clicking on the file or by launching WMP, then opening the selected media.

New codecs are continually being developed and added (see National's IA Developer's web site for a list of supported codecs).

# System Architecture (Continued) 1.2.3 Software Architecture Overview Note: The shaded boxes indicate components provided by Microsoft Corporation. Figure 1-2 demonstrates the interaction between the various software layers. Windows Media Player **ActiveX Control** Filter Graph Manager File Source DirectShow Filter Video Renderer **TMComm** TMMan32/HostComm/LibLoad/TMCRT Geode™ SCx200 TMMan Driver Geode Part TMMan Driver TM Part Geode™CS1301/CS1311 DAC TMMan32/HostComm/LibLoad/TMCRT To SCx200 CommTM Video Input Port **ExoITMpeg Application** TSSA\* Video VTransCrystal Video Renderer Decoder **TRead** Demux Audio Audio Renderer Decoder \* TriMedia Streaming Software Architecture Figure 1-2. Software Architecture Diagram

### System Architecture (Continued)

### 1.2.4 Software Component Pricing and Licensing

National delivers and supports a complete software solution when paired up with the WindowsCE.net or Linux operating system. The delivered software is a compilation of software created by National Semiconductor, Philips Semiconductors and Microsoft. Customers may need separate pricing and support agreements for Windows Media Technology (Microsoft), BIOS, Operating System, and middleware. National's pricing excludes fundamental patents: MPEG-1, -2, -4 (MPEG-LA) and MP3 (Thomson Multimedia/Fraunhofer ILS). The following tables list the associated software, their respective owners and the licensing requirements for each.

### 1.2.4.1 Codec Software

The codec software includes video and audio decoders and operates on the CS1301/CS1311 (see Table 1-1). This software performs the task of decoding the encoded media content, which are the workhorses of the solution.

#### 1.2.4.2 Host Filter Software

The DirectShow filter is the core piece of software that integrates the CS1301/CS1311 media companion with Microsoft DirectShow (see Table 1-2).

Table 1-1. Codec Software

| Components                              | IP Owner(s)            | Available as<br>Source/Binary | Licensing Requirements                |

|-----------------------------------------|------------------------|-------------------------------|---------------------------------------|

| TM MP3 Decoder                          | Philips Semiconductors | Binary                        | Licensee is responsible for           |

| TM MP3 Basic Application                |                        |                               | licensing of all fundamental patents. |

| TM MPEG-1 Video Decoder                 |                        |                               | paterno.                              |

| TM MPEG-1 Audio Decoder                 |                        |                               |                                       |

| TM MPEG-2 Video Decoder                 |                        |                               |                                       |

| TM MPEG-2 Audio Decoder                 |                        |                               |                                       |

| TM AC-3 Audio Decoder                   |                        |                               |                                       |

| TM MPEG-2 Program Stream Demux          |                        |                               |                                       |

| TM MPEG-2 Basic Application             |                        |                               |                                       |

| TM MPEG-4 Video Decoder                 |                        |                               |                                       |

| TM MPEG-4 AAC Audio Decoder             |                        |                               |                                       |

| TM MPEG-4 CELP Audio Decoder            |                        |                               |                                       |

| TM MPEG-1 File Parser and Demultiplexer |                        |                               |                                       |

| TM MPEG-4 Basic Application             |                        |                               |                                       |

| TM WMT v8 Video Decoder                 | National Semiconductor | Binary                        | Microsoft WMT license                 |

| TM WMT v8 Audio Decoder                 | Microsoft              |                               | required.                             |

### Table 1-2. Host Filter Software

| Components        | IP Owner               | Available as<br>Source/Binary | Licensing Requirements       |

|-------------------|------------------------|-------------------------------|------------------------------|

| DirectShow Filter | National Semiconductor | Binary                        | Not licensed as source code. |

## System Architecture (Continued)

#### 1.2.4.3 Communications Driver Software

The communications driver software includes most of the components that perform the communication and control tasks between the Geode SCx200 and the CS1301/CS1311 (see Table 1-3).

### 1.2.4.4 Software Development Kit

The Software Development Kit (SDK) includes the core software components that run on the TM32A core of the CS1301/CS1311. These are the supporting software com-

ponents that enable the execution of the codec software on the CS1301/CS1311 (see Table 1-4).

### 1.2.4.5 System Software

To expand system functionality beyond media decoding, Geode software components are included. These are standard components to be used in a non-media enabled application to support the required functions of an Information Appliance. In some cases, these drivers have been optimized to work with the CS1301/CS1311 (see Table 1-5).

Table 1-3. Communications Driver Software

| Components        | IP Owner(s)                 | Available as<br>Source/Binary | Licensing Requirements            |

|-------------------|-----------------------------|-------------------------------|-----------------------------------|

| Host TMMan Driver | National Semiconductor      | Open Source                   | Per Philips Semiconductors        |

| TM TMMan Library  | Philips Semiconductors      |                               | public source license provisions. |

| TMComm Library    |                             |                               |                                   |

| HostComm Library  |                             |                               |                                   |

| TMCRT Library     |                             |                               |                                   |

| TMMan 32          |                             |                               |                                   |

| LibLoad           | TriMedia Technologies, Inc. | Binary                        | NA                                |

### Table 1-4. SDK Software

| Components     | IP Owner(s)            | Available as<br>Source/Binary | Licensing Requirements |

|----------------|------------------------|-------------------------------|------------------------|

| COMMTM         | National Semiconductor | Binary                        | NA                     |

| Video Renderer | Philips Semiconductors |                               |                        |

| Audio Renderer |                        |                               |                        |

| TRead          |                        |                               |                        |

| VTrans Crystal |                        |                               |                        |

| PSOS           | VxWorks                | Binary                        | OS run-time licenses.  |

### Table 1-5. System Software

| Components                                                         | IP Owner(s)            | Available as<br>Source/Binary | Licensing Requirements        |

|--------------------------------------------------------------------|------------------------|-------------------------------|-------------------------------|

| Graphics Driver (Linux, WinCE.net)                                 | National Semiconductor | Source                        | National source code license. |

| Audio Driver (Linux, WinCE.net)                                    |                        |                               |                               |

| WinCE.net Power Management OAL                                     |                        |                               |                               |

| Touchscreen Driver (Linux, WinCE.net)                              |                        |                               |                               |

| National's DP83815 MacPHYTER™<br>Network Driver (Linux, WinCE.net) |                        |                               |                               |

### 2.0 Signal Definitions

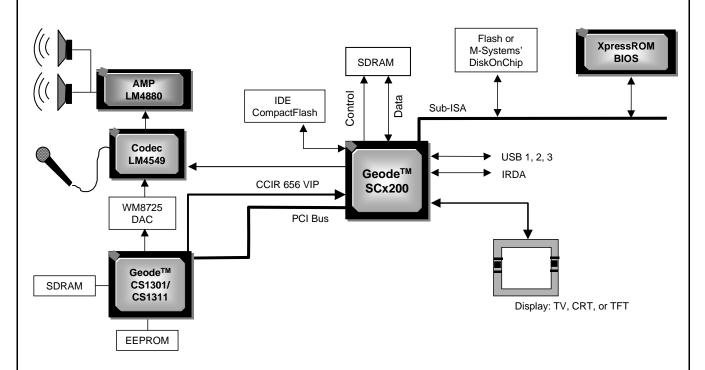

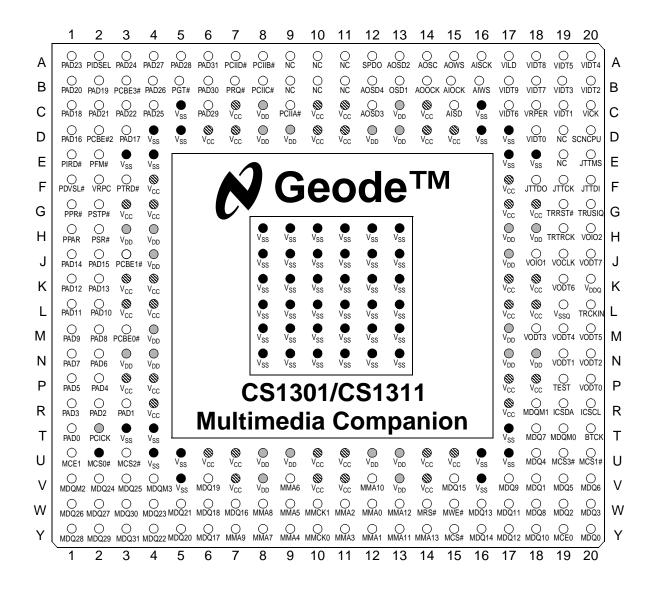

This section defines the signals and describes the external interface of the CS1301/CS1311 media companion. Figure 2-1 shows the signals organized by their functional groups.

The remaining subsections of this chapter describe:

- Section 2.1 "Ball Assignments": Provides a ball assignment diagram and tables listing the signals sorted according to ball number and alphabetically by signal name.

- Section 2.2 "Signal Descriptions": Detailed descriptions of each signal according to functional group.

- Section 2.3 "Reference Voltages": Discussion on ball reference voltages.

#### 2.1 BALL ASSIGNMENTS

The CS1301/CS1311 has a total of 169 functional pins, excluding  $V_{DDQ}$ ,  $V_{SSQ}$ , VREF\_PCI, VREF\_PERIPH, and digital power/ground. For pins with 5.0V input capability, the VREF\_PCI or VREF\_PERIPH determines 3.3V or 5.0V input tolerance. Unused pins can remain floating/unconnected; all pins that drive a clock should drive a series resistor.

Table 2-1 shows the types of I/O circuits used by the CS1301/CS1311 series. Note that the # symbol in a signal name indicates that the active or asserted state occurs when the signal is at a low voltage level. Otherwise, the signal is asserted when at a high voltage level.

Table 2-1. Ball Type Descriptions

| Modes | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| I     | Input only, except during boundary scan.                                                        |

| 0     | Output only, except during boundary scan.                                                       |

| OD    | Open Drain output, active pull low, no active drive high, requires external pull-up.            |

| I/O   | Input or Output.                                                                                |

| I/OD  | Input with Open Drain output, active pull low, no active drive high, requires external pull-up. |

<sup>\*</sup>Video In and Audio In are supported by third party software solutions, not by the National Semiconductor solution.

Figure 2-1. Functional Block Diagram

Note: Signal names have been abbreviated in this figure due to space constraints.

- = GND Connection

- = CS1301 2.5V Core Power Connection; CS1311 2.2V Core Power Connection

- = 3.3V I/O Power Connection

Figure 2-2. 292-TEPBGA Ball Assignment Diagram

Table 2-2. Ball Assignment Sorted by Ball Number

| lable    |                 |        |

|----------|-----------------|--------|

| Ball No. | Signal Name     | Туре   |

| A1       | PCI_AD23        | I/O    |

| A2       | PCI_IDSEL       | I      |

| A3       | PCI_AD24        | I/O    |

| A4       | PCI_AD27        | I/O    |

| A5       | PCI_AD28        | I/O    |

| A6       | PCI_AD31        | I/O    |

| A7       | PCI_INTD#       | I/OD   |

| A8       | PCI_INTB#       | I/O/OD |

| A9       | NC              |        |

| A10      | NC              |        |

| A11      | NC              |        |

| A12      | SPDO            | 0      |

| A13      | AO_SD2          | 0      |

| A14      | AO_SCK          | I/O    |

| A15      | AO_WS           | I/O    |

| A16      | AI_SCK          | I/O    |

| A17      | VI_DVALID       | I      |

| A18      | VI_DATA8        | ı      |

| A19      | VI_DATA5        | ı      |

| A20      | VI_DATA4        | ı      |

| B1       | PCI_AD20        | I/O    |

| B2       | PCI_AD19        | I/O    |

| B3       | PCI_C/BE3#      | I/O    |

| B4       | PCI_AD26        | I/O    |

| B5       | PCI_GNT#        | I      |

| B6       | PCI_AD30        | I/O    |

| B7       | PCI_REQ#        | 0      |

| B8       | PCI_INTC#       | I/OD   |

| B9       | NC              |        |

| B10      | NC              |        |

| B11      | NC              |        |

| B12      | AO_SD4          | 0      |

| B13      | AO_SD1          | 0      |

| B14      | AO_OSCLK        | 0      |

| B15      | AI_OSCLK        | 0      |

| B16      | AI_WS           | I/O    |

| B17      | VI_DATA9        | I      |

| B18      | VI_DATA7        | 1      |

| B19      | VI_DATA3        | I      |

| B20      | VI_DATA2        | I      |

| C1       | PCI_AD18        | I/O    |

| C2       | PCI_AD21        | I/O    |

| C3       | PCI_AD22        | I/O    |

| C4       | PCI_AD25        | I/O    |

| C5       | V <sub>SS</sub> | GND    |

| C6       | PCI_AD29        | I/O    |

| C7       | V <sub>CC</sub> | PWR    |

| C8       | V <sub>DD</sub> | PWR    |

| C9       | PCI_INTA#       | I/OD   |

| C10      | V <sub>CC</sub> | PWR    |

|          |                 | PWR    |

| C11      | V <sub>CC</sub> |        |

| C12      | AO_SD3          | 0      |

| Ball No. | Signal Name     | Туре |

|----------|-----------------|------|

| C13      | V <sub>DD</sub> | PWR  |

| C14      | V <sub>CC</sub> | PWR  |

| C15      | AI_SD           | I    |

| C16      | V <sub>SS</sub> | GND  |

| C17      | VI_DATA6        | I    |

| C18      | VREF_PERIPH     | PWR  |

| C19      | VI_DATA1        | I    |

| C20      | VI_CLK          | I/O  |

| D1       | PCI_AD16        | I/O  |

| D2       | PCI_C/BE#2      | I/O  |

| D3       | PCI_AD17        | I/O  |

| D4       | V <sub>SS</sub> | GND  |

| D5       | V <sub>SS</sub> | GND  |

| D6       | V <sub>CC</sub> | PWR  |

| D7       | V <sub>CC</sub> | PWR  |

| D8       | V <sub>DD</sub> | PWR  |

| D9       | V <sub>DD</sub> | PWR  |

| D10      | V <sub>CC</sub> | PWR  |

| D11      | V <sub>CC</sub> | PWR  |

| D12      | V <sub>DD</sub> | PWR  |

| D12      |                 | PWR  |

|          | V <sub>DD</sub> |      |

| D14      | V <sub>CC</sub> | PWR  |

| D15      | V <sub>CC</sub> | PWR  |

| D16      | V <sub>SS</sub> | GND  |

| D17      | V <sub>SS</sub> | GND  |

| D18      | VI_DATA0        | I    |

| D19      | NC              |      |

| D20      | SCANCPU         | 1    |

| E1       | PCI_IRDY#       | 1/0  |

| E2       | PCI_FRAME#      | 1/0  |

| E3       | V <sub>SS</sub> | GND  |

| E4       | V <sub>SS</sub> | GND  |

| E17      | V <sub>SS</sub> | GND  |

| E18      | V <sub>SS</sub> | GND  |

| E19      | NC              |      |

| E20      | JTAG_TMS        | I    |

| F1       | PCI_DEVSEL#     | I/O  |

| F2       | VREF_PCI        | PWR  |

| F3       | PCI_TRDY#       | I/O  |

| F4       | V <sub>CC</sub> | PWR  |

| F17      | V <sub>CC</sub> | PWR  |

| F18      | JTAG_TDO        | I/O  |

| F19      | JTAG_TCK        | I    |

| F20      | JTAG_TDI        | I    |

| G1       | PCI_PERR#       | I/O  |

| G2       | PCI_STOP#       | I/O  |

| G3       | V <sub>CC</sub> | PWR  |

| G4       | V <sub>CC</sub> | PWR  |

| G17      | V <sub>CC</sub> | PWR  |

| G18      | V <sub>CC</sub> | PWR  |

| Ball No. | Signal Name     | Туре |

|----------|-----------------|------|

| G19      | TRI_RESET#      | I    |

| G20      | TRI_USERIRQ     | 1    |

| H1       | PCI_PAR         | I/O  |

| H2       | PCI_SERR#       | OD   |

| H3       | V <sub>DD</sub> | PWR  |

| H4       | $V_{DD}$        | PWR  |

| H8       | V <sub>SS</sub> | GND  |

| H9       | V <sub>SS</sub> | GND  |

| H10      | V <sub>SS</sub> | GND  |

| H11      | V <sub>SS</sub> | GND  |

| H12      | V <sub>SS</sub> | GND  |

| H13      | V <sub>SS</sub> | GND  |

| H17      | V <sub>DD</sub> | PWR  |

| H18      | V <sub>DD</sub> | PWR  |

| H19      | TRI_TIMER_CLK   | ı    |

| H20      | VO_IO2          | I/O  |

| J1       | PCI_AD14        | I/O  |

| J2       | PCI_AD15        | I/O  |

| J3       | PCI_C/BE1#      | I/O  |

| J4       | V <sub>DD</sub> | PWR  |

| J8       | V <sub>SS</sub> | GND  |

| J9       | V <sub>SS</sub> | GND  |

| J10      | V <sub>SS</sub> | GND  |

| J11      | V <sub>SS</sub> | GND  |

| J12      | V <sub>SS</sub> | GND  |

| J13      | V <sub>SS</sub> | GND  |

| J17      | V <sub>DD</sub> | PWR  |

| J18      | VO_IO1          | I/O  |

| J19      | VO_CLK          | I/O  |

| J20      | VO_DATA7        | 0    |

| K1       | PCI_AD12        | I/O  |

| K2       | PCI_AD13        | I/O  |

| K3       | V <sub>CC</sub> | PWR  |

| K4       | V <sub>CC</sub> | PWR  |

| K8       | V <sub>SS</sub> | GND  |

| K9       | V <sub>SS</sub> | GND  |

| K10      | V <sub>SS</sub> | GND  |

| K11      | V <sub>SS</sub> | GND  |

| K12      | V <sub>SS</sub> | GND  |

| K13      | V <sub>SS</sub> | GND  |

| K17      | V <sub>CC</sub> | PWR  |

| K18      | V <sub>CC</sub> | PWR  |

| K19      | VO_DATA6        | 0    |

| K20      | $V_{DDQ}$       | PWR  |

| L1       | PCI_AD11        | I/O  |

| L2       | PCI_AD10        | I/O  |

| L3       | V <sub>CC</sub> | PWR  |

| L4       | V <sub>CC</sub> | PWR  |

| L8       | V <sub>SS</sub> | GND  |

Table 2-2. Ball Assignment Sorted by Ball Number (Continued)

| lable 2-2. |                  |      |  |

|------------|------------------|------|--|

| Ball No.   | Signal Name      | Туре |  |

| L9         | V <sub>SS</sub>  | GND  |  |

| L10        | V <sub>SS</sub>  | GND  |  |

| L11        | V <sub>SS</sub>  | GND  |  |

| L12        | V <sub>SS</sub>  | GND  |  |

| L13        | V <sub>SS</sub>  | GND  |  |

| L17        | V <sub>CC</sub>  | PWR  |  |

| L18        | V <sub>CC</sub>  | PWR  |  |

| L19        | V <sub>SSQ</sub> | GND  |  |

| L20        | TRI_CLKIN        | I    |  |

| M1         | PCI_AD09         | I/O  |  |

| M2         | PCI_AD08         | I/O  |  |

| M3         | PCI_C/BE0#       | I/O  |  |

| M4         | V <sub>DD</sub>  | PWR  |  |

| M8         | V <sub>SS</sub>  | GND  |  |

| M9         | V <sub>SS</sub>  | GND  |  |

| M10        | V <sub>SS</sub>  | GND  |  |

| M11        | V <sub>SS</sub>  | GND  |  |

| M12        | V <sub>SS</sub>  | GND  |  |

| M13        | V <sub>SS</sub>  | GND  |  |

| M17        | V <sub>DD</sub>  | PWR  |  |

| M18        | VO_DATA3         | 0    |  |

| M19        | VO_DATA4         | 0    |  |

| M20        | VO_DATA5         | 0    |  |

| N1         | PCI_AD07         | I/O  |  |

| N2         | PCI_AD06         | I/O  |  |

| N3         | V <sub>DD</sub>  | PWR  |  |

| N4         | V <sub>DD</sub>  | PWR  |  |

| N8         | V <sub>SS</sub>  | GND  |  |

| N9         | V <sub>SS</sub>  | GND  |  |

| N10        | V <sub>SS</sub>  | GND  |  |

| N11        | V <sub>SS</sub>  | GND  |  |

| N12        | V <sub>SS</sub>  | GND  |  |

| N13        | V <sub>SS</sub>  | GND  |  |

| N17        | V <sub>DD</sub>  | PWR  |  |

| N18        | V <sub>DD</sub>  | PWR  |  |

| N19        | VO_DATA1         | 0    |  |

| N20        | VO_DATA1         | 0    |  |

| P1         | PCI_AD05         | 1/0  |  |

| P2         | PCI AD04         | I/O  |  |

| P3         | V <sub>CC</sub>  | PWR  |  |

| P4         | V <sub>CC</sub>  | PWR  |  |

| P17        | V <sub>CC</sub>  | PWR  |  |

| P18        | V <sub>CC</sub>  | PWR  |  |

| P19        | TESTMODE         | 1    |  |

| P20        | VO_DATA0         | 0    |  |

| R1         | PCI_AD03         | 1/0  |  |

| R2         | PCI_AD02         | 1/0  |  |

| R3         | PCI_AD01         | I/O  |  |

| R4         | V <sub>CC</sub>  | PWR  |  |

|            | 1                | 1    |  |

| ı Assıgnı | ment Sorted by     | Ball Num |

|-----------|--------------------|----------|

| Ball No.  | Signal Name        | Туре     |

| R17       | V <sub>CC</sub>    | PWR      |

| R18       | MM_DQM1            | 0        |

| R19       | IIC_SDA            | I/OD     |

| R20       | IIC_SCL            | I/OD     |

| T1        | PCI_AD00           | I/O      |

| T2        | PCI_CLK            | I        |

| T3        | V <sub>SS</sub>    | GND      |

| T4        | V <sub>SS</sub>    | GND      |

| T17       | V <sub>SS</sub>    | GND      |

| T18       | MM_DQ07            | I/O      |

| T19       | MM_DQM0            | 0        |

| T20       | BOOT_CLK           | I        |

| U1        | MM_CKE1            | 0        |

| U2        | MM_CS0#            | 0        |

| U3        | MM_CS2#            | 0        |

| U4        | V <sub>SS</sub>    | GND      |

| U5        | V <sub>SS</sub>    | GND      |

| U6        | V <sub>CC</sub>    | PWR      |

| U7        | V <sub>CC</sub>    | PWR      |

| U8        | V <sub>DD</sub>    | PWR      |

| U9        | V <sub>DD</sub>    | PWR      |

| U10       | V <sub>CC</sub>    | PWR      |

| U11       | V <sub>CC</sub>    | PWR      |

| U12       | V <sub>DD</sub>    | PWR      |

| U13       | V <sub>DD</sub>    | PWR      |

| U14       | V <sub>CC</sub>    | PWR      |

| U15       | V <sub>CC</sub>    | PWR      |

| U16       |                    | GND      |

|           | V <sub>SS</sub>    |          |

| U17       | V <sub>SS</sub>    | GND      |

| U18       | MM_DQ04            | 1/0      |

| U19       | MM_CS3#<br>MM_CS1# | 0        |

| U20<br>V1 | MM_DQM2            | 0        |

| V2        | MM_DQ24            | 1/0      |

| V3        | MM_DQ25            | 1/0      |

| V4        | MM DQM3            | 0        |

| V5        | V <sub>SS</sub>    | GND      |

| V6        | MM DQ19            | I/O      |

| V7        | V <sub>CC</sub>    | PWR      |

| V8        | V <sub>DD</sub>    | PWR      |

| V9        | MM_A06             | 0        |

| V10       | V <sub>CC</sub>    | PWR      |

| V10       | V <sub>CC</sub>    | PWR      |

| V11       | MM_A10             | 0        |

| V12       | V <sub>DD</sub>    | PWR      |

|           |                    | PWR      |

| V14       | V <sub>CC</sub>    |          |

| V15       | MM_DQ15            | I/O      |

| V16       | V <sub>SS</sub>    | GND      |

| V17       | MM_DQ09            | I/O      |

| Ball No. | Signal Name | Туре |

|----------|-------------|------|

| V18      | MM_DQ01     | I/O  |

| V19      | MM_DQ05     | I/O  |

| V20      | MM_DQ06     | I/O  |

| W1       | MM_DQ26     | I/O  |

| W2       | MM_DQ27     | I/O  |

| W3       | MM_DQ30     | I/O  |

| W4       | MM_DQ23     | I/O  |

| W5       | MM_DQ21     | I/O  |

| W6       | MM_DQ18     | I/O  |

| W7       | MM_DQ16     | I/O  |

| W8       | MM_A08      | 0    |

| W9       | MM_A05      | 0    |

| W10      | MM_CLK1     | 0    |

| W11      | MM_A02      | 0    |

| W12      | MM_A00      | 0    |

| W13      | MM_A12      | 0    |

| W14      | MM_RAS#     | 0    |

| W15      | MM_WE#      | 0    |

| W16      | MM_DQ13     | I/O  |

| W17      | MM_DQ11     | I/O  |

| W18      | MM_DQ08     | I/O  |

| W19      | MM_DQ02     | I/O  |

| W20      | MM_DQ03     | I/O  |

| Y1       | MM_DQ28     | I/O  |

| Y2       | MM_DQ29     | I/O  |

| Y3       | MM_DQ31     | I/O  |

| Y4       | MM_DQ22     | I/O  |

| Y5       | MM_DQ20     | I/O  |

| Y6       | MM_DQ17     | I/O  |

| Y7       | MM_A09      | 0    |

| Y8       | MM_A07      | 0    |

| Y9       | MM_A04      | 0    |

| Y10      | MM_CLK0     | 0    |

| Y11      | MM_A03      | 0    |

| Y12      | MM_A01      | 0    |

| Y13      | MM_A11      | 0    |

| Y14      | MM_A13      | 0    |

| Y15      | MM_CAS#     | 0    |

| Y16      | MM_DQ14     | I/O  |

| Y17      | MM_DQ12     | I/O  |

| Y18      | MM_DQ10     | I/O  |

| Y19      | MM_CKE0     | 0    |

| Y20      | MM_DQ00     | I/O  |

Table 2-3. Ball Assignment Sorted Alphabetically by Signal Name

|             | Table    |

|-------------|----------|

| Signal Name | Ball No. |

| AI_OSCLK    | B15      |

| AI_SCK      | A16      |

| AI SD       | C15      |

| AI WS       | B16      |

| AO OSCLK    | B14      |

| AO SCK      | A14      |

| AO SD1      | B13      |

| AO SD2      | A13      |

| AO SD3      | C12      |

| AO SD4      | B12      |

| AO WS       | A15      |

| BOOT_CLK    | T20      |

| IIC_SCL     | R20      |

| IIC SDA     | R19      |

| _           | F19      |

| JTAG_TCK    | F20      |

| JTAG_TDI    | +        |

| JTAG_TDO    | F18      |

| JTAG_TMS    | E20      |

| MM_A00      | W12      |

| MM_A01      | Y12      |

| MM_A02      | W11      |

| MM_A03      | Y11      |

| MM_A04      | Y9       |

| MM_A05      | W9       |

| MM_A06      | V9       |

| MM_A07      | Y8       |

| MM_A08      | W8       |

| MM_A09      | Y7       |

| MM_A10      | V12      |

| MM_A11      | Y13      |

| MM_A12      | W13      |

| MM_A13      | Y14      |

| MM_CAS#     | Y15      |

| MM_CKE0     | Y19      |

| MM_CKE1     | U1       |

| MM_CLK0     | Y10      |

| MM_CLK1     | W10      |

| MM_CS0#     | U2       |

| MM_CS1#     | U20      |

| MM_CS2#     | U3       |

| MM_CS3#     | U19      |

| MM_DQ00     | Y20      |

| MM_DQ01     | V18      |

| MM_DQ02     | W19      |

| MM_DQ03     | W20      |

| MM_DQ04     | U18      |

| MM DQ05     | V19      |

| MM DQ06     | V20      |

| MM_DQ07     | T18      |

| MM_DQ08     | W18      |

| MM DQ09     | V17      |

| MM DQ10     | Y18      |

| DQ 10       |          |

|                      | gnment Sort                                   |

|----------------------|-----------------------------------------------|

| Signal Name          | Ball No.                                      |

| MM_DQ11              | W17                                           |

| MM_DQ12              | Y17                                           |

| MM_DQ13              | W16                                           |

| MM_DQ14              | Y16                                           |

| MM_DQ15              | V15                                           |

| MM_DQ16              | W7                                            |

| MM_DQ17              | Y6                                            |

| MM_DQ18              | W6                                            |

| MM_DQ19              | V6                                            |

| MM_DQ20              | Y5                                            |

| MM_DQ21              | W5                                            |

| MM_DQ22              | Y4                                            |

| MM_DQ23              | W4                                            |

| MM_DQ24              | V2                                            |

| MM_DQ25              | V3                                            |

| MM_DQ26              | W1                                            |

| MM_DQ27              | W2                                            |

| MM_DQ28              | Y1                                            |

| MM_DQ29              | Y2                                            |

| MM_DQ30              | W3                                            |

| MM_DQ31              | Y3                                            |

| MM_DQM0              | T19                                           |

| MM_DQM1              | R18                                           |

| MM_DQM2              | V1                                            |

| MM_DQM3              | V4                                            |

| MM_RAS#              | W14                                           |

| MM_WE#               | W15                                           |

| NC (Total of 8)      | A9, A10,<br>A11, B9,<br>B10, B11,<br>E19, D19 |

| PCI_AD00             | T1                                            |

| PCI_AD01             | R3                                            |

| PCI_AD02             | R2                                            |

| PCI_AD03             | R1                                            |

| PCI_AD04             | P2                                            |

| PCI_AD05             | P1                                            |

| PCI_AD06             | N2                                            |

| PCI_AD07             | N1                                            |

| PCI_AD08             | M2                                            |

| PCI_AD09             | M1                                            |

| PCI_AD10             | L2                                            |

| PCI_AD11             | L1                                            |

| PCI_AD12             | K1                                            |

| PCI_AD13             | K2                                            |

| PCI_AD14             | J1                                            |

| PCI_AD15             | J2                                            |

| PCI_AD16             | D1                                            |

| PCI_AD17             | D3                                            |

| PCI_AD17             | C1                                            |

| PCI_AD18<br>PCI_AD19 | B2                                            |

| PCI_AD19 PCI AD20    | B1                                            |

| FCI_ADZU             | PI                                            |

PCI\_AD21

C2

| Signal Name                   | Ball No.                     |

|-------------------------------|------------------------------|

| PCI_AD22                      | C3                           |

| PCI_AD23                      | A1                           |

| PCI_AD24                      | A3                           |

| PCI_AD25                      | C4                           |

| PCI_AD26                      | B4                           |

| PCI_AD27                      | A4                           |

| PCI_AD28                      | A5                           |

| PCI_AD29                      | C6                           |

| PCI_AD30                      | B6                           |

| PCI_AD31                      | A6                           |

| PCI_C/BE0#                    | M3                           |

| PCI_C/BE1#                    | J3                           |

| PCI_C/BE2#                    | D2                           |

| PCI_C/BE3#                    | B3                           |

| PCI_CLK                       | T2                           |

| PCI_DEVSEL#                   | F1                           |

| PCI_FRAME#                    | E2                           |

| PCI_GNT#                      | B5                           |

| PCI_IDSEL                     | A2                           |

| PCI_INTA#                     | C9                           |

| PCI_INTB#                     | A8                           |

| PCI_INTC#                     | B8                           |

| PCI_INTD#                     | A7                           |

| PCI_IRDY#                     | E1                           |

| PCI_PAR                       | H1                           |

| PCI_PERR#                     | G1                           |

| PCI_REQ#                      | B7                           |

| PCI_SERR#                     | H2                           |

| PCI_STOP#                     | G2                           |

| PCI_TRDY#                     | F3                           |

| SCANCPU                       | D20                          |

| SPDO                          | A12                          |

| TESTMODE                      | P19                          |

| TRI_CLKIN                     | L20                          |

| TRI_RESET#                    | G19                          |

| TRI_TIMER_CLK                 | H19                          |

| TRI_USERIRQ                   | G20                          |

| V <sub>CC</sub> (3.3V I/O     | C7, C10,<br>C11, C14,        |

| Power Supply,<br>Total of 40) | D6, D7, D10,                 |

| ,                             | D11, D14,                    |

|                               | D15, F4,<br>F17, G3, G4,     |

|                               | G17, G18,<br>K3, K4, K17,    |

|                               | K3, K4, K17,<br>K18, L3, L4, |

|                               | L17, L18, P3,<br>P4, P17,    |

|                               | P4, P17,                     |

|                               | P18, R4,<br>R17, U6, U7,     |

|                               | U10, U11,                    |

|                               | U14, U15,<br>V7, V10,        |

|                               | V11, V14                     |

|                               |                              |

| V <sub>DD</sub> (2.5V Core<br>Power Supply,<br>Total of 24) | C8, C13, D8,<br>D9, D12,<br>D13, H3, H4,<br>H17, H18,<br>J4, J17, M4,<br>M17, N3, N4,<br>N17, N18,<br>U8, U9, U12,<br>U13, V8, V13                                                                                                                           |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DDQ}$                                                   | K20                                                                                                                                                                                                                                                          |

| VI_CLK                                                      | C20                                                                                                                                                                                                                                                          |

| VI_DATA0                                                    | D18                                                                                                                                                                                                                                                          |

| VI_DATA1                                                    | C19                                                                                                                                                                                                                                                          |

| VI DATA2                                                    | B20                                                                                                                                                                                                                                                          |

| VI DATA3                                                    | B19                                                                                                                                                                                                                                                          |

| VI DATA4                                                    | A20                                                                                                                                                                                                                                                          |

| VI_DATA5                                                    | A19                                                                                                                                                                                                                                                          |

| VI_DATA6                                                    | C17                                                                                                                                                                                                                                                          |

| VI DATA7                                                    | B18                                                                                                                                                                                                                                                          |

| VI DATA8                                                    | A18                                                                                                                                                                                                                                                          |

| VI_DATA9                                                    | B17                                                                                                                                                                                                                                                          |

| _                                                           | A17                                                                                                                                                                                                                                                          |

| VI_DVALID<br>VO_CLK                                         |                                                                                                                                                                                                                                                              |

|                                                             | J19                                                                                                                                                                                                                                                          |

| VO_DATA0                                                    | P20                                                                                                                                                                                                                                                          |

| VO_DATA1                                                    | N19                                                                                                                                                                                                                                                          |

| VO_DATA2                                                    | N20                                                                                                                                                                                                                                                          |

| VO_DATA3                                                    | M18                                                                                                                                                                                                                                                          |

| VO_DATA4                                                    | M19                                                                                                                                                                                                                                                          |

| VO_DATA5                                                    | M20                                                                                                                                                                                                                                                          |

| VO_DATA6                                                    | K19                                                                                                                                                                                                                                                          |

| VO_DATA7                                                    | J20                                                                                                                                                                                                                                                          |

| VO_IO1                                                      | J18                                                                                                                                                                                                                                                          |

| VO_IO2                                                      | H20                                                                                                                                                                                                                                                          |

| VREF_PCI                                                    | F2                                                                                                                                                                                                                                                           |

| VREF_PERIPH                                                 | C18                                                                                                                                                                                                                                                          |

| V <sub>SS</sub> (Ground Connection, Total of 55)            | C5, C16, D4, D5, D16, D17, E3, E4, E17, E18, H8, H9, H10, H11, H12, H13, J8, J9, J10, J11, J12, J13, K8, K9, K10, K11, K12, K13, L8, L9, L10, L11, L12, L13, M8, M9, M10, M11, M12, M13, N8, N9, N10, N11, N12, N13, T3, T4, T17, U4, U5, U16, U17, V5, V16, |

| $V_{SSQ}$                                                   | L19                                                                                                                                                                                                                                                          |

Signal Name

Ball No.

## 2.2 SIGNAL DESCRIPTIONS

## 2.2.1 System Interface Signals

| Signal Name   | Ball<br>No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRI_CLKIN     | L20         | I    | Main Input Clock. The SDRAM clock outputs (MM_CLK0 and MM_CLK1) can be set to 2x or 3x this frequency. The on-chip DSPCPU clock (DSPCPU_CLK) can be set to 1x, 5/4, 4/3, 3/2 or 2x the SDRAM clock frequency. The maximum recommended ppm level is ±100 ppm or lower to improve jitter on generated clocks. The duty cycle should not exceed 30/70% asymmetry. |

|               |             |      | The operating limits of the internal PLLs are:                                                                                                                                                                                                                                                                                                                 |

|               |             |      | • 27 MHz < Output of the SDRAM PLL < 200 MHz                                                                                                                                                                                                                                                                                                                   |

|               |             |      | • 33 MHz < Output of the CPU PLL < 266 MHz                                                                                                                                                                                                                                                                                                                     |

|               |             |      | These are not the speed grades of the chips, just the PLL limits.                                                                                                                                                                                                                                                                                              |

| TRI_USERIRQ   | G20         | I    | General Purpose Level/Edge Interrupt Input. Vectored interrupt source number 4.                                                                                                                                                                                                                                                                                |

| TRI_TIMER_CLK | H19         | I    | External General Purpose Clock Source for Timers. Maximum 40 MHz.                                                                                                                                                                                                                                                                                              |

| TRI_RESET#    | G19         | I    | CS1301/CS1311 RESET Input. This pin can be tied to the PCI_RST# signal in the PCI bus systems. Upon releasing RESET, CS1301/CS1311 initiates its boot protocol.                                                                                                                                                                                                |

| VREF_PCI      | F2          | PWR  | <b>PCI Voltage Reference.</b> Determines the mode of operation of the PCI pins. VREF_PCI must be connected to V <sub>SS</sub> (0V) for use in 3.3V PCI signaling environment, as is the case for a Geode SCx200 system.                                                                                                                                        |

|               |             |      | The supply to this pin should be AC bypassed and provide 40 mA of DC sink or source capability.                                                                                                                                                                                                                                                                |

| VREF_PERIPH   | C18         | PWR  | <b>Peripheral Voltage Reference.</b> Determines the mode of operation of the I/O pins listed in Section 2.3 "Reference Voltages" on page 22.                                                                                                                                                                                                                   |

|               |             |      | VREF_PERIPH must be connected to 5.0V if the designated I/O pins listed in Section 2.3 should be 5.0V input voltage capable.                                                                                                                                                                                                                                   |

|               |             |      | VREF_PERIPH must be connected to V <sub>SS</sub> (0V) if the designated I/O pins listed in Section 2.3 are 3.3V only inputs.                                                                                                                                                                                                                                   |

|               |             |      | The supply to this pin should be AC bypassed and provide 40 mA of DC sink or source capability.                                                                                                                                                                                                                                                                |

## 2.2.2 Memory Interface Signals

| Signal Name  | Ball<br>No.                    | Туре | Description                                                                                                                                                                                                                   |

|--------------|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MM_CLK0      | Y10                            | 0    | SDRAM Output Clock (at 2x or 3x TRI_CLKIN frequency). Two identi-                                                                                                                                                             |

| MM_CLK1      | W10                            |      | cal outputs are provided to reliably drive several small memory configurations without external glue. A series terminating resistor close to CS1301/CS1311 is required to reduce ringing.                                     |

|              |                                |      | For driving a $50\Omega$ trace, a resistor of 27 to $33\Omega$ is recommended. The use of higher impedance traces in the SDRAM signals is not recommended.                                                                    |

| MM_A[13:00]  | See Table                      | 0    | Address Bus. Used for row and column addresses.                                                                                                                                                                               |

|              | 2-3 on<br>page 12              |      | WARNING: Do not connect MM_A[13:11] directly to SDRAM A[13:11] pins. Refer to Chapter 12 SDRAM Memory System of the Philips Semi-conductor <i>PNX1300 Series Media Processors Data Book</i> for accurate connection diagrams. |

| MM_DQ[31:00] | See Table<br>2-3 on<br>page 12 | I/O  | <b>32-Bit Data I/O Bus.</b> The Main Memory Interface module also supports a 16-bit I/O interface.                                                                                                                            |

| MM_CKE0      | Y19                            | 0    | Clock Enable Output to SDRAMs. Two identical outputs are provided in order to reliably drive several small memory configurations without external glue.                                                                       |

| MM_CKE1      | U1                             |      |                                                                                                                                                                                                                               |

| MM_CS0#      | U2                             | 0    | Chip Select for DRAM rank n; active low. The chip select pins may be                                                                                                                                                          |

| MM_CS1#      | U20                            |      | used as address pins to support the 256-Mbit SDRAM device organized in x16.                                                                                                                                                   |

| MM_CS2#      | U3                             |      |                                                                                                                                                                                                                               |

| MM_CS3#      | U19                            |      |                                                                                                                                                                                                                               |

| MM_RAS#      | W14                            | 0    | Row Address Strobe; active low.                                                                                                                                                                                               |

| MM_CAS#      | Y15                            | 0    | Column Address Strobe; active low.                                                                                                                                                                                            |

| MM_WE#       | W15                            | 0    | Write Enable; active low.                                                                                                                                                                                                     |

| MM_DQM0      | T19                            | 0    | Data Mask Enable. These are byte-enable signals for the 32-bit                                                                                                                                                                |

| MM_DQM1      | R18                            |      | MM_DQ bus.                                                                                                                                                                                                                    |

| MM_DQM2      | V1                             |      |                                                                                                                                                                                                                               |

| MM_DQM3      | V4                             |      |                                                                                                                                                                                                                               |

## 2.2.3 PCI Interface Signals

| Signal Name   | Ball<br>No.                    | Туре                                                                                                                            | Description                                                                                                                                                                                                                |

|---------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_CLK       | T2                             | I                                                                                                                               | PCI Clock. All PCI input signals are sampled with respect to the rising edge of this clock. All PCI outputs are generated based on this clock. This clock is required for normal operation of the PCI module.              |

| PCI_AD[31:00] | See Table<br>2-3 on<br>page 12 | I/O                                                                                                                             | Multiplexed Address and Data.                                                                                                                                                                                              |

| PCI_C/BE0#    | М3                             | I/O                                                                                                                             | Multiplexed Bus Commands and Byte-Enables. High for command,                                                                                                                                                               |

| PCI_C/BE1#    | J3                             |                                                                                                                                 | low for byte-enable.                                                                                                                                                                                                       |

| PCI_C/BE2#    | D2                             |                                                                                                                                 |                                                                                                                                                                                                                            |

| PCI_C/BE3#    | В3                             |                                                                                                                                 |                                                                                                                                                                                                                            |

| PCI_PAR       | H1                             | I/O                                                                                                                             | Parity. Even parity across AD and C/BE# lines.                                                                                                                                                                             |

| PCI_FRAME#    | E2                             | I/O                                                                                                                             | <b>Frame Sustained TRI-STATE.</b> Frame is driven by a master to indicate the beginning and duration of an access.                                                                                                         |

| PCI_IRDY#     | E1                             | I/O                                                                                                                             | <b>Initiator Ready Sustained TRI-STATE.</b> Initiator Ready indicates that the bus master is ready to complete the current data phase.                                                                                     |

| PCI_TRDY#     | F3                             | I/O                                                                                                                             | <b>Target Ready Sustained TRI-STATE.</b> Target Ready indicates that the bus target is ready to complete the current data phase.                                                                                           |

| PCI_STOP#     | G2                             | I/O                                                                                                                             | <b>Stop Sustained TRI-STATE.</b> Indicates that the target is requesting that the master stop the current transaction.                                                                                                     |

| PCI_IDSEL     | A2                             | I                                                                                                                               | ID Select. Used as chip select during configuration read/write cycles.                                                                                                                                                     |

| PCI_DEVSEL#   | F1                             | I/O                                                                                                                             | <b>Device Select Sustained TRI-STATE.</b> Indicates whether any device of the bus has been selected.                                                                                                                       |

| PCI_REQ#      | В7                             | 0                                                                                                                               | Request. Driven by the CS1301/CS1311 as a PCI bus master to requesuse of the PCI bus.                                                                                                                                      |

| PCI_GNT#      | B5                             | I                                                                                                                               | <b>Grant.</b> Indicates to the CS1301/CS1311 that access to the PCI bus ha been granted.                                                                                                                                   |

| PCI_PERR#     | G1                             | I/O                                                                                                                             | Parity Error Sustained TRI-STATE. Parity error generated/received by CS1301/CS1311.                                                                                                                                        |

| PCI_SERR#     | H2                             | OD                                                                                                                              | <b>System Error.</b> This signal is asserted when operating as a target and detecting an address parity error.                                                                                                             |

| PCI_INTA#     | C9                             | I/OD                                                                                                                            | PCI Interrupts A, B, C, and D. Can operate as an input (power-up                                                                                                                                                           |

| PCI_INTB#     | A8                             | I/O/OD                                                                                                                          | default) or output, as determined by direction control bits in PCI MMIO register INT_CTL.                                                                                                                                  |

| PCI_INTC#     | B8                             | I/OD                                                                                                                            | As an input, PCI_INT# can be used to receive PCI interrupt requests                                                                                                                                                        |

| PCI_INTD#     | A7                             | I/OD                                                                                                                            | (normal PCI use is active low, level-sensitive mode, but the VIC can be set to treat these as a positive edge triggered mode). As an input, PCI_INT# can also be used as a general interrupt request if not neede for PCI. |

|               |                                | As an output, the value of a PCI_INT# can be programmed through PC MMIO registers to generate interrupts for other PCI masters. |                                                                                                                                                                                                                            |

### 2.2.4 Video In Interface Signals