## EL4450

OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

contact our Technical Support Center at

1-888-INTERSIL or www.intersil.com/tsc

# DATASHEET

FN7168 Rev 0.00 January 1996

### Wideband Four-Quadrant Multiplier

The EL4450 is a complete four-quadrant multiplier circuit. It offers wide bandwidth and good linearity while including a powerful output voltage amplifier, drawing modest supply current.

The EL4450 operates on  $\pm 5V$  supplies and has an analog input range of  $\pm 2V$ , making it ideal for video signal processing. AC characteristics do not vary over the  $\pm 5V$  to  $\pm 15V$  supply range.

The multiplier has an operational temperature range of  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  and are packaged in plastic 14-pin PDIP and SO.

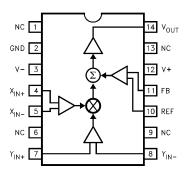

### **Pinout**

EL4450 (14-PIN PDIP, SO) TOP VIEW

#### **Features**

- Complete four-quadrant multiplier with output amp requires no extra components

- Good linearity of 0.3%

- 90MHz bandwidth for both X and Y inputs

- Operates on ±5V to ±15V supplies

- · All inputs are differential

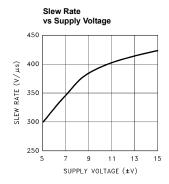

- 400V/µs slew rate

## **Applications**

- · Modulation/Demodulation

- RMS computation

- Real-time power computation

- · Nonlinearity correction/generation

## **Ordering Information**

| PART<br>NUMBER | TEMP. RANGE    | PACKAGE     | PKG. NO. |

|----------------|----------------|-------------|----------|

| EL4450CN       | -40°C to +85°C | 14-Pin PDIP | MDP0031  |

| EL4450CM       | -40°C to +85°C | 14-Pin SO   | MDP0027  |

## **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| V+       | Positive Supply Voltage                           | lout  | Output Current                           |

|----------|---------------------------------------------------|-------|------------------------------------------|

| $V_S$    | V+ to V- Supply Voltage                           | PD    | Maximum Power Dissipation See Curves     |

| $V_{IN}$ | Voltage at any Input or Feedback V+ to V-         | $T_A$ | Operating Temperature Range40°C to +85°C |

| VIN      | Difference between Pairs of Inputs or Feedback 6V | TS    | Storage Temperature Range60°C to +150°C  |

| liki     | Current into any Input or Feedback Pin            | •     |                                          |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

### **Open-Loop DC Electrical Specifications**

Power Supplies at  $\pm 5V$ ,  $T_A = 25$ °C,  $V_{FB} = V_{OUT}$ .

| PARAMETER         | DESCRIPTION                                                                                                               | N                                                                              | MIN   | TYP   | MAX  | UNITS            |

|-------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|-------|------|------------------|

| V <sub>DIFF</sub> | Differential Input Voltage—Clipping                                                                                       |                                                                                | 1.8   | 2.0   |      | ٧                |

|                   | 0.2% nonlinearity                                                                                                         |                                                                                |       | 1.0   |      | V                |

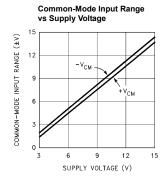

| V <sub>CM</sub>   | Common-Mode Range of V <sub>DIFF</sub> = 0, V <sub>S</sub> = ±5V                                                          |                                                                                |       | ±2.8  |      | V                |

|                   | V <sub>S</sub> = ±15V                                                                                                     |                                                                                |       | ±12.8 |      | V                |

| Vos               | Input Offset Voltage                                                                                                      |                                                                                |       | 8     | 35   | mV               |

| I <sub>B</sub>    | Input Bias Current                                                                                                        |                                                                                |       | 9     | 20   | μA               |

| los               | Input Offset Current between X <sub>IN</sub> + and X <sub>IN</sub> -, Y <sub>IN</sub> + and Y <sub>IN</sub> -, REF and FB |                                                                                |       | 0.5   | 4    | μA               |

| Gain              | Gain Factor of $V_{OUT} = Gain \times X_{IN} + \times Y_{IN}$                                                             |                                                                                | 0.45  | 0.5   | 0.55 | V/V <sup>2</sup> |

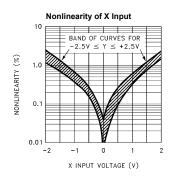

| NLx               | Nonlinearity of X Input; X <sub>IN</sub> between -1V and +1V                                                              |                                                                                |       | 0.3   | 0.7  | %                |

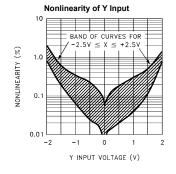

| NLy               | Nonlinearity of Y Input; Y <sub>IN</sub> between -1V and +1V                                                              |                                                                                |       | 0.2   | 0.35 | %                |

| R <sub>IN</sub>   | Input resistance                                                                                                          | X <sub>IN</sub> + to X <sub>IN</sub> -, Y <sub>IN</sub> + to Y <sub>IN</sub> - |       | 230   |      | kΩ               |

|                   |                                                                                                                           | REF to FB                                                                      |       | 90    |      |                  |

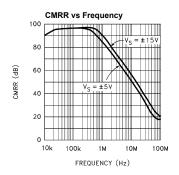

| CMRR              | Common-Mode Rejection Ratio, X <sub>IN</sub> and Y <sub>IN</sub>                                                          |                                                                                | 70    | 90    |      | dB               |

| PSRR              | Power-Supply Rejection Ratio, FB                                                                                          |                                                                                | 60    | 72    |      | dB               |

| VO                | Output Voltage Swing (V <sub>IN</sub> = 0, V <sub>REF</sub> Varied)                                                       | $V_S = \pm 5V$                                                                 | ±2.5  | ±2.8  |      | V                |

|                   |                                                                                                                           | V <sub>S</sub> = ±15V                                                          | ±12.5 | ±12.8 |      |                  |

| I <sub>SC</sub>   | Output Short-Circuit Current                                                                                              |                                                                                | 40    | 85    |      | mA               |

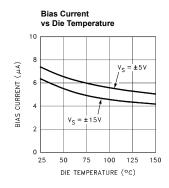

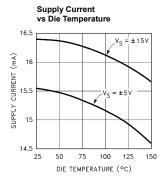

| IS                | Supply Current, $V_S = \pm 15V$                                                                                           |                                                                                |       | 15.4  | 18   | mA               |

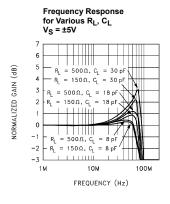

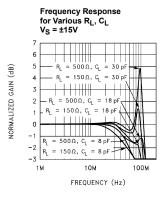

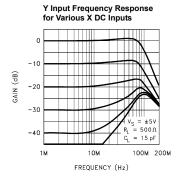

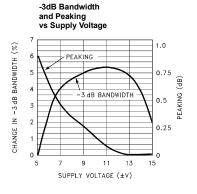

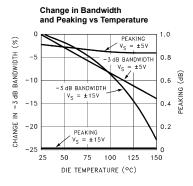

## $\textbf{Closed-Loop AC Electrical Specifications} \qquad \text{Power Supplies at $\pm 12$V, $T_A = 25^{\circ}$C, $R_L = 500\Omega$, $C_L = 15$pF.}$

| PARAMETER      | DESCRIPTION                                     | MIN | TYP | MAX | UNITS |

|----------------|-------------------------------------------------|-----|-----|-----|-------|

| BW, -3dB       | -3dB Small-Signal Bandwidth, X or Y             |     | 90  |     | MHz   |

| BW, ±0.1dB     | 0.1dB Flatness Bandwidth                        |     | 10  |     | MHz   |

| Peaking        | Frequency Response Peaking                      |     | 1.0 |     | dB    |

| SR             | Slew Rate, V <sub>OUT</sub> between -2V and +2V | 300 | 400 |     | V/µs  |

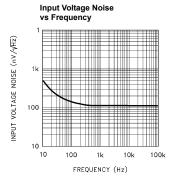

| V <sub>N</sub> | Input-Referred Noise Voltage Density            |     | 100 |     | nV/Hz |

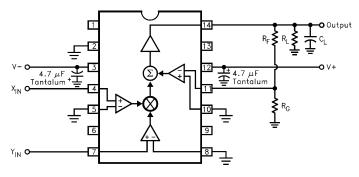

## **Test Circuit**

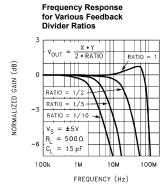

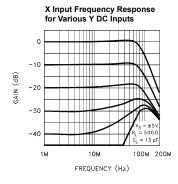

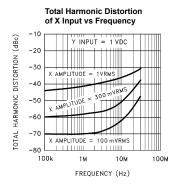

Note: For typical performance curves,  $R_F$  = 0,  $R_G$  =  $\infty$ ,  $V_S$  =  $\pm 5V$ ,  $R_L$  =  $500\Omega$ , and  $C_L$  = 15pF unless otherwise noted.

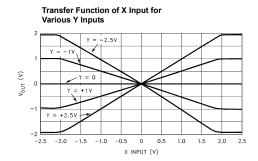

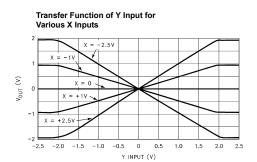

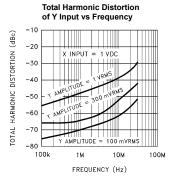

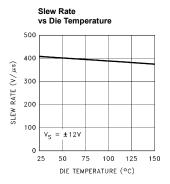

# **Typical Performance Curves**

## Typical Performance Curves (Continued)

## Typical Performance Curves (Continued)

## Applications Information

The EL4450 is a complete four-quadrant multiplier with 90MHz bandwidth. It has three sets of inputs; a differential multiplying X-input, a differential multiplying Y-input, and another differential input which is used to complete a feedback loop with the output. Here is a typical connection:

The gain of the feedback divider is H, and  $H = R_G/(R_G + R_F)$ . The transfer function of the part is:

$$V_{OUT} = A_O \times (1/2 \times ((V_{INX} + -V_{INX} -) \times (V_{INY} + -V_{INY} -)) + (V_{BEF} - V_{EB})).$$

$V_{FB}$  is connected to  $V_{OUT}$  through a feedback network, so  $V_{FB} = H^*V_{OUT}$ .  $A_O$  is the open-loop gain of the amplifier, and is about 600. The large value of  $A_O$  drives:

$$(1/2 \times ((V_{INX} + -V_{INX} -) \times (V_{INY} + -V_{INY} -)) + (V_{REF} - V_{FB})) {\to} 0.$$

Rearranging and substituting for V<sub>REF</sub>:

$$\begin{split} V_{OUT} &= (1/2 \times ((V_{INX} +\!\!-\! V_{INX} \!\!-\!) \times (V_{INY} +\!\!-\! V_{INY} \!\!-\!)) +\!\! V_{REF}) /\! H, \\ \text{or } V_{OUT} &= (XY/2 + V_{REF}) /\! H \end{split}$$

Thus the output is equal to one-half the product of X and Y inputs and offset by  $V_{REF}$ , all gained up by the feedback divider ratio. The EL4450 is stable for a direct connection between  $V_{OUT}$  and FB, and the feedback divider may be used for higher output gain, although with the traditional loss of bandwidth.

It is important to keep the feedback divider's impedance at the FB terminal low so that stray capacitance does not diminish the loop's phase margin. The pole caused by the parallel impedance of the feedback resistors and stray capacitance should be at least 150MHz; typical strays of 3pF thus require a feedback impedance of  $360\Omega$  or less. Alternatively, a small capacitor across  $R_{\text{F}}$  can be used to create more of a frequency-compensated divider. The value of the capacitor should scale with the parasitic capacitance at the FB input. It is also practical to place small capacitors across both the feedback resistors (whose values maintain the desired gain) to swamp out parasitics. For instance, two 10pF capacitors across equal divider resistors for a maximum gain of 1 will dominate parasitic effects and allow a higher divider resistance.

The REF pin can be used as the output's ground reference, or for DC offsetting of the output, or it can be used to sum in another signal.

#### **Input Connections**

The input transistors can be driven from resistive and capacitive sources, but are capable of oscillation when presented with an inductive input. It takes about 80nH of series inductance to make the inputs actually oscillate, equivalent to four inches of unshielded wiring or about 6 of unterminated input transmission line. The oscillation has a characteristic frequency of 500MHz. Placing one's finger (via a metal probe) or an oscilloscope probe on the input will kill the oscillation.

Normal high-frequency construction obviates any such problems, where the input source is reasonably close to the input. If this is not possible, one can insert series resistors of around to  $51\Omega$  to de-Q the inputs.

### Signal Amplitudes

Signal input common-mode voltage must be between (V-)  $\pm 2.5$ V and (V+)  $\pm 2.5$ V to ensure linearity. Additionally, the differential voltage on any input stage must be limited to  $\pm 6$ V to prevent damage. The differential signal range is  $\pm 2$ V in the EL4450. The input range is substantially constant with temperature.

#### The Ground Pin

The ground pin draws only  $6\mu A$  maximum DC current, and may be biased anywhere between (V-) +2.5V and (V+) -3.5V. The ground pin is connected to the IC's substrate and frequency compensation components. It serves as a shield within the IC and enhances input stage CMRR over frequency, and if connected to a potential other than ground, it must be bypassed.

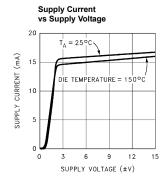

### **Power Supplies**

The EL4450 works well on supplies from  $\pm 3V$  to  $\pm 15V$ . The supplies may be of different voltages as long as the requirements of the GND pin are observed (see the Ground Pin section for a discussion). The supplies should be bypassed close to the device with short leads.  $4.7\mu F$  tantalum capacitors are very good, and no smaller bypasses need be placed in parallel. Capacitors as low as  $0.01\mu F$  can be used if small load currents flow.

Single-polarity supplies, such as +12V with +5V can be used, where the ground pin is connected to +5V and V- to ground. The inputs and outputs will have to have their levels shifted above ground to accommodate the lack of negative supply.

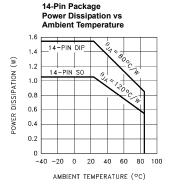

The power dissipation of the EL4450 increases with power supply voltage, and this must be compatible with the package chosen. This is a close estimate for the dissipation of a circuit:

$$P_D = 2*I_S, max*V_S + (V_S - V_O)*V_O/R_{PAR}$$

where

IS, max is the maximum supply current

V<sub>S</sub> is the ± supply voltage (assumed equal)

V<sub>O</sub> is the output voltage

RPAR is the parallel of all resistors loading the output

For instance, the EL4450 draws a maximum of 18mA. With light loading,  $R_{PAR}\!\!\to\!\!\infty$  and the dissipation with ±5V supplies is 180mW. The maximum supply voltage that the device can run on for a given  $P_D$  and the other parameters is:

$$V_S,max = (P_D + V_O^2/R_{PAR})/(2I_S + V_O/R_{PAR})$$

The maximum dissipation a package can offer is:

$P_D$ , max =  $(T_J$ , max $-T_A$ , max $)/\theta_{JA}$

#### Where

T<sub>J</sub>,max is the maximum junction temperature, 150°C for reliability, less to retain optimum electrical performance

$T_A$ ,max is the ambient temperature, 70°C for commercial and 85°C for industrial range

$\theta_{\mbox{\scriptsize JA}}$  is the thermal resistance of the mounted package, obtained from data sheet dissipation curves

The more difficult case is the SO-14 package. With a maximum junction temperature of 150°C and a maximum ambient temperature of 85°C, the 65°C temperature rise and package thermal resistance of 120°/W gives a dissipation of 542mW at 85°C. This allows the full maximum operating supply voltage unloaded, but reduced if loaded significantly.

### **Output Loading**

The output stage is very powerful. It typically can source 85mA and sink 120mA. Of course, this is too much current to sustain and the part will eventually be destroyed by excessive dissipation or by metal traces on the die opening. The metal traces are completely reliable while delivering the 30mA continuous output given in the Absolute Maximum Ratings table in this data sheet, or higher purely transient currents.

Gain accuracy degrades only 0.2% from no load to 100 $\Omega$  load. Heavy resistive loading will degrade frequency response and video distortion for loads < 100 $\Omega$ .

Capacitive loads will cause peaking in the frequency response. If a capacitive load must be driven, a small-valued series resistor can be used to isolate it.  $12\Omega$  to  $51\Omega$  should suffice. A  $22\Omega$  series resistor will limit peaking to 2.5dB with even a 220pF load.

### Mixer Applications

Because of its lower distortion levels, the Y input is the better choice for a mixer's signal port. The X input would receive oscillator amplitudes of about 1V RMS maximum. Carrier suppression is initially limited by the offset voltage of the Y input, 20mV maximum, and is about 37dB worst-case. Better suppression can be obtained by nulling the offset of the X input. Similarly, nulling the offset of the Y input will improve signal-port suppression. Driving an input differentially will also maximize feedthrough suppression at frequencies beyond 10MHz.

### **AC Level Detectors**

Square-law converters are commonly used to convert AC signals to DC voltages corresponding to the original amplitude in subsystems like automatic gain controls (AGCs) and amplitude-stabilized oscillators. Due to the controlled AC amplitudes, the inputs of the multiplier will see a relatively constant signal level. Best performance will be obtained for

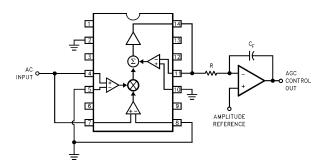

inputs between 200mVRMS and 1VRMS. The traditional use of the EL4450 as an AGC detector and control loop would be:

FIGURE 1. TRADITIONAL AGC DETECTOR/DC FEEDBACK CIRCUIT

The EL4450 simply provides an output equal to the square of the input signal and an integrator filters out the AC component, while comparing the DC component to an amplitude reference. The integrator output is the DC control voltage to the variable-gain sections of the AGC (not shown). If a negative polarity of reference is required, one of the multiplier input terminal pairs is reversed, inverting the multiplier output. Input bias current will cause input voltage offsets due to source impedances; putting a compensating resistor in series with the grounded inputs of the EL4450 will reduce this offset greatly.

This control system will attempt to force:

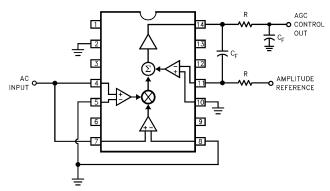

FIGURE 2. SIMPLIFIED AGC DETECTOR/DC FEEDBACK CIRCUIT

The extra op-amp can be eliminated by using this circuit (Figure 2).

Here the internal op-amp of the EL4450 replaces the external amplifier. The feedback capacitor  $C_F$  does not provide a perfect integration action; a zero occurs at a frequency of  $1/2\pi RC_F$ . This is canceled by including another  $RC_F$  pair at the AGC control output. If the reference voltage must be negative, the resistor at pin 11 is connected to ground rather than the reference and pin 10 connected to the reference.

The amplitude reference will have to support some AC currents flowing through R. If this is a problem, several changes can be made to eliminate it. The reference is connected to pin 10 and the resistor R connected to pin 11 reconnected to ground, and one of the multiplier input connections are reversed.

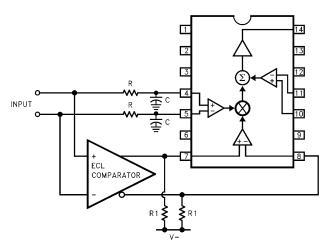

Square-law detectors have a restricted input range, about 10:1, because the output rapidly disappears into the DC errors as signal amplitudes reduce. This circuit gives a multiplier output that is the absolute value of the input, thus increasing range to 100:1(Figure 3).

An ECL comparator produces an output corresponding to the sign of the input, which when multiplied by the input produces an effective absolute-value function. The RC product

connected to the X inputs simply emulates the time delay of the comparator to maintain circuit accuracy at higher frequencies.

### **Nonlinear Function Generation**

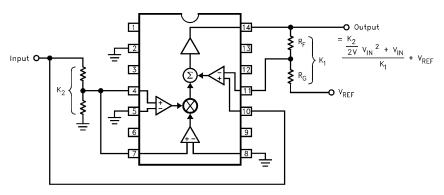

The REF pin of the EL4450 can be used to sum in various quantities of polynomial function generators. For instance, this

FIGURE 3. ABSOLUTE-VALUE INPUT CIRCUITRY

FIGURE 4. POLYNOMIAL FUNCTION GENERATOR

sum of REF allows a linear signal path which can have various amounts of squared signal added (Figure 4).

The polarity of the squared signal can be reversed by swapping one of the X or Y input pairs.

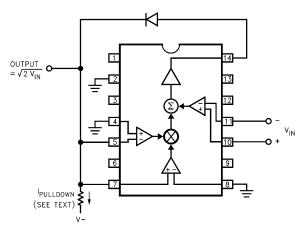

The REF and FB pins also simplify feedback schemes that allow square-rooting.

The diode and I<sub>PULLDOWN</sub> assure that the output will always produce the positive square-root of the input signal.

I<sub>PULLDOWN</sub> should be large enough to assure that the diode be forward-biased for any load current. In this configuration,

the bandwidth of the circuit will reduce for smaller input signals (Figure 5).

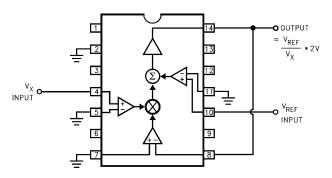

The REF and FB terminals can also be used to implement division.

The output frequency response reduces for smaller values of  $V_X$ , but is not affected by  $V_{REF}$  (Figure 6).

FIGURE 5. SQUARE-ROOTER

FIGURE 6. DIVIDER CONNECTION

© Copyright Intersil Americas LLC 2003. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>