# LM2578A/LM3578A Switching Regulator

## **General Description**

The LM2578A is a switching regulator which can easily be set up for such DC-to-DC voltage conversion circuits as the buck, boost, and inverting configurations. The LM2578A features a unique comparator input stage which not only has separate pins for both the inverting and non-inverting inputs, but also provides an internal 1.0V reference to each input, thereby simplifying circuit design and p.c. board layout. The output can switch up to 750 mA and has output pins for its collector and emitter to promote design flexibility. An external current limit terminal may be referenced to either the ground or the  $V_{\rm in}$  terminal, depending upon the application. In addition, the LM2578A has an on board oscillator, which sets the switching frequency with a single external capacitor from <1 Hz to 100 kHz (typical).

The LM2578A is an improved version of the LM2578, offering higher maximum ratings for the total supply voltage and output transistor emitter and collector voltages.

### **Features**

- Inverting and non-inverting feedback inputs

- 1.0V reference at inputs

- Operates from supply voltages of 2V to 40V

- Output current up to 750 mA, saturation less than 0.9V

- Current limit and thermal shut down

- Duty cycle up to 90%

## **Applications**

- Switching regulators in buck, boost, inverting, and single-ended transformer configurations

- Motor speed control

- Lamp flasher

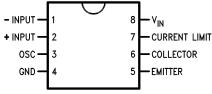

## **Connection Diagram and Ordering Information**

## **Dual-In-Line Package**

00871129

Order Number LM3578AM, LM2578AN or LM3578AN See NS Package Number M08A or N08E

## **Functional Diagram**

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Total Supply Voltage 50V

Collector Output to Ground -0.3V to +50V

Emitter Output to Ground (Note 2) -1V to +50V

Power Dissipation (Note 3) Internally limited

Output Current 750 mA

Storage Temperature -65°C to +150°C

Lead Temperature

(soldering, 10 seconds) 260°C Maximum Junction Temperature 150°C

ESD Tolerance (Note 4)

## **Operating Ratings**

Ambient Temperature Range

LM2578A  $-40^{\circ}\text{C} \leq \text{T}_{\text{A}}$   $\leq +85^{\circ}\text{C}$

LM3578A  $0^{\circ}\text{C} \le \text{T}_{\text{A}} \le +70^{\circ}\text{C}$

Junction Temperature Range

LM2578A  $-40^{\circ}\text{C} \leq \text{T}_{\text{J}}$

≤+125°C

2 kV

LM3578A  $0^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq +125^{\circ}\text{C}$

## **Electrical Characteristics**

These specifications apply for  $2V \le V_{IN} \le 40V$  ( $2.2V \le V_{IN} \le 40V$  for  $T_J \le -25^{\circ}C$ ), timing capacitor  $C_T = 3900$  pF, and  $25\% \le duty$  cycle  $\le 75\%$ , unless otherwise specified. Values in standard typeface are for  $T_J = 25^{\circ}C$ ; values in **boldface type** apply for operation over the specified operating junction temperature range.

|                              |                                             |                                                            |          | LM2578A/            |                   |

|------------------------------|---------------------------------------------|------------------------------------------------------------|----------|---------------------|-------------------|

| Symbol                       | Parameter                                   | Conditions                                                 | Typical  | LM3578A             | Units             |

|                              |                                             |                                                            | (Note 5) | Limit (Note 6)      |                   |

| OSCILLATO                    | DR                                          |                                                            |          |                     |                   |

| f <sub>osc</sub>             | Frequency                                   |                                                            | 20       |                     | kHz               |

|                              |                                             |                                                            |          | 24                  | kHz (max)         |

|                              |                                             |                                                            |          | 16                  | kHz (min)         |

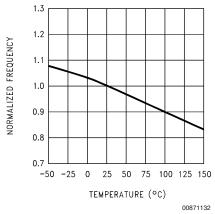

| $\Delta f_{OSC}/\Delta T$    | Frequency Drift with Temperature            |                                                            | -0.13    |                     | %/°C              |

|                              | Amplitude                                   |                                                            | 550      |                     | mV <sub>p-p</sub> |

| REFERENCI                    | E/COMPARATOR (Note 7)                       |                                                            |          | •                   |                   |

| V <sub>R</sub>               | Input Reference                             | $I_1 = I_2 = 0$ mA and                                     | 1.0      |                     | V                 |

|                              | Voltage                                     | I <sub>1</sub> = I <sub>2</sub> = 1 mA ±1% (Note 8)        |          | 1.050/ <b>1.070</b> | V (max)           |

|                              |                                             |                                                            |          | 0.950/ <b>0.930</b> | V (min)           |

| $\Delta V_{R}/\Delta V_{IN}$ | Input Reference Voltage Line<br>Regulation  | $I_1 = I_2 = 0 \text{ mA and}$                             | 0.003    |                     | %/V               |

|                              |                                             | I <sub>1</sub> = I <sub>2</sub> = 1 mA ±1% (Note 8)        |          | 0.01/ <b>0.02</b>   | %/V (max)         |

| INV                          | Inverting Input Current                     | I <sub>1</sub> = I <sub>2</sub> = 0 mA, duty cycle = 25%   | 0.5      |                     | μA                |

|                              | Level Shift Accuracy                        | Level Shift Current = 1 mA                                 | 1.0      |                     | %                 |

|                              |                                             |                                                            |          | 10/13               | % (max)           |

| ΔV <sub>R</sub> /Δt          | Input Reference Voltage Long Term Stability |                                                            | 100      |                     | ppm/1000h         |

| OUTPUT                       |                                             |                                                            |          | •                   |                   |

| V <sub>C</sub> (sat)         | Collector Saturation Voltage                | I <sub>C</sub> = 750 mA pulsed, Emitter                    | 0.7      |                     | V                 |

|                              |                                             | grounded                                                   |          | 0.90/1.2            | V (max)           |

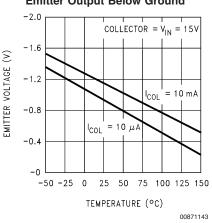

| V <sub>E</sub> (sat)         | Emitter Saturation Voltage                  | I <sub>O</sub> = 80 mA pulsed,                             | 1.4      |                     | V                 |

|                              |                                             | $V_{IN} = V_{C} = 40V$                                     |          | 1.7/2.0             | V (max)           |

| I <sub>CES</sub>             | Collector Leakage Current                   | V <sub>IN</sub> = V <sub>CE</sub> = 40V, Emitter grounded, | 0.1      |                     | μA                |

|                              |                                             | Output OFF                                                 |          | 200/ <b>250</b>     | μA (max)          |

| BV <sub>CEO(SUS)</sub>       | Collector-Emitter Sustaining Voltage        | I <sub>SUST</sub> = 0.2A (pulsed), V <sub>IN</sub> = 0     | 60       |                     | V                 |

| - (,                         |                                             |                                                            |          | 50                  | V (min)           |

| CURRENT L                    | İMIT                                        |                                                            |          |                     |                   |

| V <sub>CL</sub>              | Sense Voltage Shutdown Level                | Referred to V <sub>IN</sub> or Ground                      | 110      |                     | mV                |

|                              |                                             | (Note 9)                                                   |          | 80                  | mV (min)          |

|                              |                                             |                                                            |          | 160                 | mV (max)          |

## **Electrical Characteristics** (Continued)

These specifications apply for  $2V \le V_{IN} \le 40V$  ( $2.2V \le V_{IN} \le 40V$  for  $T_J \le -25^{\circ}C$ ), timing capacitor  $C_T = 3900$  pF, and  $25\% \le 0$  duty cycle  $\le 75\%$ , unless otherwise specified. Values in standard typeface are for  $T_J = 25^{\circ}C$ ; values in **boldface type** apply for operation over the specified operating junction temperature range.

| Symbol                   | Parameter                       | Conditions                                 | Typical (Note 5) | LM2578A/<br>LM3578A<br>Limit (Note 6) | Units    |

|--------------------------|---------------------------------|--------------------------------------------|------------------|---------------------------------------|----------|

| CURRENT L                | IMIT                            |                                            |                  |                                       |          |

| $\Delta V_{CL}/\Delta T$ | Sense Voltage Temperature Drift |                                            | 0.3              |                                       | %/°C     |

| 1                        | <br>  Sense Bias Current        | Referred to V <sub>IN</sub>                | 4.0              |                                       | μA       |

| I <sub>CL</sub>          | Sense bias ounent               | Referred to ground                         | 0.4              |                                       | μΑ       |

| DEVICE PO                | WER CONSUMPTION                 |                                            |                  | l                                     | <u> </u> |

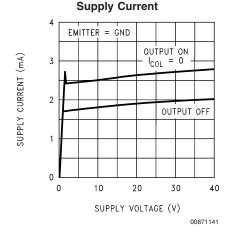

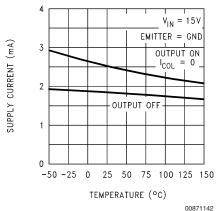

| I <sub>s</sub>           | Supply Current                  | Output OFF, V <sub>E</sub> = 0V            | 2.0              |                                       | mA       |

|                          |                                 |                                            |                  | 3.5/ <b>4.0</b>                       | mA (max) |

|                          |                                 | Output ON, I <sub>C</sub> = 750 mA pulsed, | 14               |                                       | mA       |

|                          |                                 | $V_E = 0V$                                 |                  |                                       |          |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.

Note 2: For  $T_J \ge 100^{\circ}C$ , the Emitter pin voltage should not be driven more than 0.6V below ground (see Application Information).

**Note 3:** At elevated temperatures, devices must be derated based on package thermal resistance. The device in the 8-pin DIP must be derated at 95°C/W, junction to ambient. The device in the surface-mount package must be derated at 150°C/W, junction-to-ambient.

Note 4: Human body model, 1.5 k $\Omega$  in series with 100 pF.

Note 5: Typical values are for  $T_J = 25^{\circ}C$  and represent the most likely parametric norm.

**Note 6:** All limits guaranteed at room temperature (standard type face) and at temperature extremes (bold type face). Room temperature limits are 100% production tested. Limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate AOQL.

Note 7: Input terminals are protected from accidental shorts to ground but if external voltages higher than the reference voltage are applied, excessive current will flow and should be limited to less than 5 mA.

Note 8: I<sub>1</sub> and I<sub>2</sub> are the external sink currents at the inputs (refer to Test Circuit).

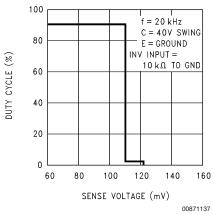

Note 9: Connection of a  $10 \text{ k}\Omega$  resistor from pin 1 to pin 4 will drive the duty cycle to its maximum, typically 90%. Applying the minimum Current Limit Sense Voltage to pin 7 will not reduce the duty cycle to less than 50%. Applying the maximum Current Limit Sense Voltage to pin 7 is certain to reduce the duty cycle below 50%. Increasing this voltage by 15 mV may be required to reduce the duty cycle to 0%, when the Collector output swing is 40V or greater (see Ground-Referred Current Limit Sense Voltage typical curve).

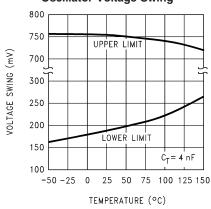

## **Typical Performance Characteristics**

# Oscillator Frequency Change with Temperature

#### **Oscillator Voltage Swing**

00871133

## **Typical Performance Characteristics** (Continued)

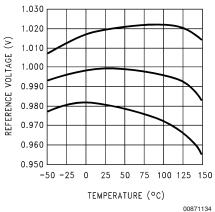

### Input Reference Voltage Drift with Temperature

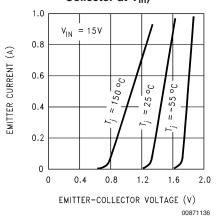

# Emitter Saturation Voltage (Sourcing Current, Collector at V<sub>in</sub>)

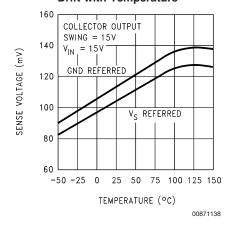

## Current Limit Sense Voltage Drift with Temperature

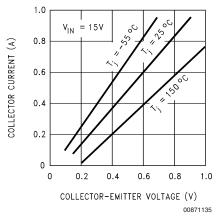

### Collector Saturation Voltage (Sinking Current, Emitter Grounded)

## Ground Referred Current Limit Sense Voltage

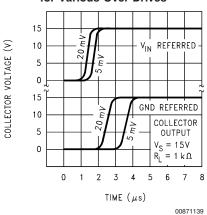

## **Current Limit Response Time** for Various Over Drives

## Typical Performance Characteristics (Continued)

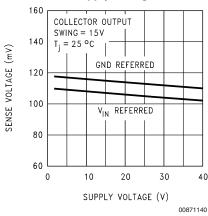

# Current Limit Sense Voltage vs Supply Voltage

### **Supply Current**

#### Collector Current with Emitter Output Below Ground

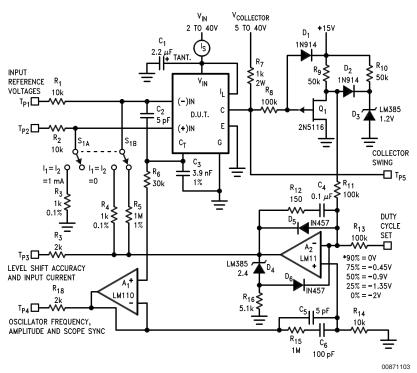

## **Test Circuit\***

Parameter tests can be made using the test circuit shown. Select the desired  $V_{\rm in},$  collector voltage and duty cycle with adjustable power supplies. A digital volt meter with an input resistance greater than 100  $M\Omega$  should be used to measure the following:

Input Reference Voltage to Ground; S1 in either position.

Level Shift Accuracy (%) =  $(T_{P3}(V)/1V) \times 100\%$ ; S1 at  $I_1 = I_2 = 1 \text{ mA}$

Input Current (mA) = (1V -  $T_{p3}$  (V))/1  $M\Omega$ : S1 at  $I_1$  =  $I_2$  = 0 mA.

Oscillator parameters can be measured at  $T_{\rm p4}$  using a frequency counter or an oscilloscope.

The Current Limit Sense Voltage is measured by connecting an adjustable 0-to-1V floating power supply in series with the current limit terminal and referring it to either the ground or the  $V_{\rm in}$  terminal. Set the duty cycle to 90% and monitor test point  $T_{\rm P5}$  while adjusting the floating power supply voltage until the LM2578A's duty cycle just reaches 0%. This voltage is the Current Limit Sense Voltage.

The Supply Current should be measured with the duty cycle at 0% and S1 in the  $\rm I_1=I_2=0$  mA position.

\*LM2578A specifications are measured using automated test equipment. This circuit is provided for the customer's convenience when checking parameters. Due to possible variations in testing conditions, the measured values from these testing procedures may not match those of the factory.

## Test Circuit\* (Continued)

Op amp supplies are  $\pm 15V$  DVM input resistance >100 M $\Omega$  \*LM2578 max duty cycle is 90%

## **Definition of Terms**

**Input Reference Voltage:** The voltage (referred to ground) that must be applied to either the inverting or non-inverting input to cause the regulator switch to change state (ON or OFF).

**Input Reference Current:** The current that must be drawn from either the inverting or non-inverting input to cause the regulator switch to change state (ON or OFF).

**Input Level Shift Accuracy:** This specification determines the output voltage tolerance of a regulator whose output control depends on drawing equal currents from the inverting and non-inverting inputs (see the Inverting Regulator of *Figure 21*, and the RS-232 Line Driver Power Supply of *Figure 23*).

Level Shift Accuracy is tested by using two equal-value resistors to draw current from the inverting and non-inverting input terminals, then measuring the percentage difference in the voltages across the resistors that produces a controlled duty cycle at the switch output.

Collector Saturation Voltage: With the inverting input terminal grounded thru a 10 k $\Omega$  resistor and the output transistor's emitter connected to ground, the Collector Saturation-Voltage is the collector-to-emitter voltage for a given collector current.

**Emitter Saturation Voltage:** With the inverting input terminal grounded thru a 10 k $\Omega$  resistor and the output transistor's collector connected to  $V_{in}$ , the Emitter Saturation Voltage is the collector-to-emitter voltage for a given emitter current.

**Collector Emitter Sustaining Voltage:** The collectoremitter breakdown voltage of the output transistor, measured at a specified current. **Current Limit Sense Voltage:** The voltage at the Current Limit pin, referred to either the supply or the ground terminal, which (via logic circuitry) will cause the output transistor to turn OFF and resets cycle-by-cycle at the oscillator frequency.

**Current Limit Sense Current:** The bias current for the Current Limit terminal with the applied voltage equal to the Current Limit Sense Voltage.

**Supply Current:** The IC power supply current, excluding the current drawn through the output transistor, with the oscillator operating.

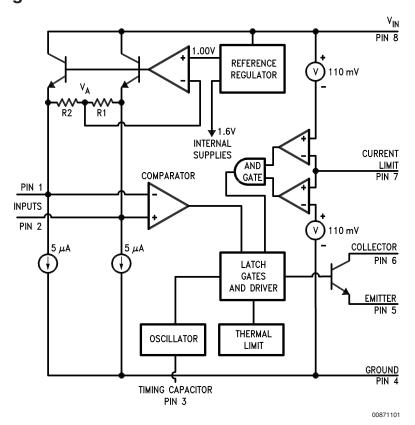

## **Functional Description**

The LM2578A is a pulse-width modulator designed for use as a switching regulator controller. It may also be used in other applications which require controlled pulse-width voltage drive.

A control signal, usually representing output voltage, fed into the LM2578A's comparator is compared with an internally-generated reference. The resulting error signal and the oscillator's output are fed to a logic network which determines when the output transistor will be turned ON or OFF. The following is a brief description of the subsections of the LM2578A.

#### **COMPARATOR INPUT STAGE**

The LM2578A's comparator input stage is unique in that both the inverting and non-inverting inputs are available to the user, and both contain a 1.0V reference. This is accomplished as follows: A 1.0V reference is fed into a modified voltage follower circuit (see FUNCTIONAL DIAGRAM). When both input pins are open, no current flows through R1

## Functional Description (Continued)

and R2. Thus, both inputs to the comparator will have the potential of the 1.0V reference,  $V_A$ . When one input, for example the non-inverting input, is pulled  $\Delta V$  away from  $V_A$ , a current of  $\Delta V/R1$  will flow through R1. This same current flows through R2, and the comparator sees a total voltage of  $2\Delta V$  between its inputs. The high gain of the system, through feedback, will correct for this imbalance and return both inputs to the 1.0V level.

This unusual comparator input stage increases circuit flexibility, while minimizing the total number of external components required for a voltage regulator system. The inverting switching regulator configuration, for example, can be set up without having to use an external op amp for feedback polarity reversal (see TYPICAL APPLICATIONS).

#### **OSCILLATOR**

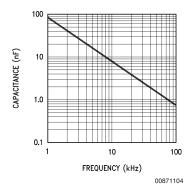

The LM2578A provides an on-board oscillator which can be adjusted up to 100 kHz. Its frequency is set by a single external capacitor, C<sub>1</sub>, as shown in *Figure 1*, and follows the equation

$f_{OSC} = 8x10^{-5}/C_1$

The oscillator provides a blanking pulse to limit maximum duty cycle to 90%, and a reset pulse to the internal circuitry.

FIGURE 1. Value of Timing Capacitor vs Oscillator Frequency

#### **OUTPUT TRANSISTOR**

The output transistor is capable of delivering up to 750 mA with a saturation voltage of less than 0.9V. (see *Collector Saturation Voltage* and *Emitter Saturation Voltage* curves).

The emitter must not be pulled more than 1V below ground (this limit is 0.6V for  $T_{\rm J} \geq 100^{\circ} C)$ . Because of this limit, an external transistor must be used to develop negative output voltages (see the Inverting Regulator Typical Application). Other configurations may need protection against violation of this limit (see the Emitter Output section of the Applications Information).

#### CURRENT LIMIT

The LM2578A's current limit may be referenced to either the ground or the  $V_{\rm in}$  pins, and operates on a cycle-by-cycle basis

The current limit section consists of two comparators: one with its non-inverting input referenced to a voltage 110 mV below  $V_{\rm in}$ , the other with its inverting input referenced

110 mV above ground (see FUNCTIONAL DIAGRAM). The current limit is activated whenever the current limit terminal is pulled 110 mV away from either  $V_{\rm in}$  or ground.

## **Applications Information**

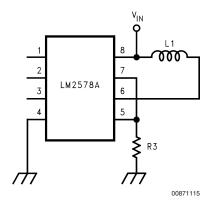

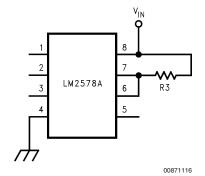

#### **CURRENT LIMIT**

As mentioned in the functional description, the current limit terminal may be referenced to either the  $V_{\rm in}$  or the ground terminal. Resistor R3 converts the current to be sensed into a voltage for current limit detection.

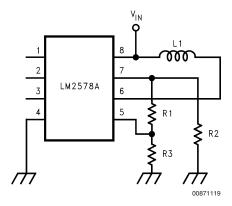

FIGURE 2. Current Limit, Ground Referred

FIGURE 3. Current Limit, Vin Referred

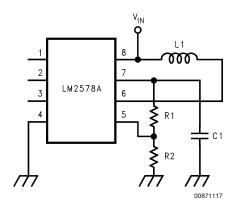

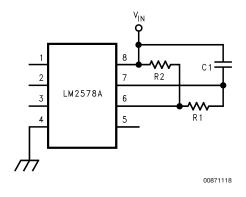

#### **CURRENT LIMIT TRANSIENT SUPPRESSION**

When noise spikes and switching transients interfere with proper current limit operation, R1 and C1 act together as a low pass filter to control the current limit circuitry's response time.

Because the sense current of the current limit terminal varies according to where it is referenced, R1 should be less than 2 k $\Omega$  when referenced to ground, and less than 100 $\Omega$  when referenced to  $V_{\rm in}$ .

## **Applications Information** (Continued)

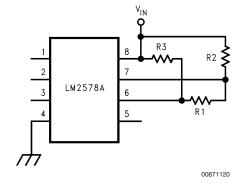

FIGURE 4. Current Limit Transient Suppressor, Ground Referred

FIGURE 5. Current Limit Transient Suppressor,  $V_{\rm in}$  Referred

## **C.L. SENSE VOLTAGE MULTIPLICATION**

When a larger sense resistor value is desired, the voltage divider network, consisting of R1 and R2, may be used. This effectively multiplies the sense voltage by (1 + R1/R2). Also, R1 can be replaced by a diode to increase current limit sense voltage to about 800 mV (diode  $V_f + 110$  mV).

FIGURE 6. Current Limit Sense Voltage Multiplication, Ground Referred

FIGURE 7. Current Limit Sense Voltage Multiplication, V<sub>in</sub> Referred

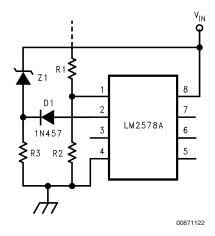

#### **UNDER-VOLTAGE LOCKOUT**

Under-voltage lockout is accomplished with few external components. When  $V_{\rm in}$  becomes lower than the zener breakdown voltage, the output transistor is turned off. This occurs because diode D1 will then become forward biased, allowing resistor R3 to sink a greater current from the non-inverting input than is sunk by the parallel combination of R1 and R2 at the inverting terminal. R3 should be one-fifth of the value of R1 and R2 in parallel.

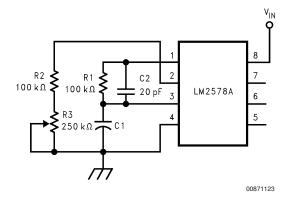

FIGURE 8. Under-Voltage Lockout

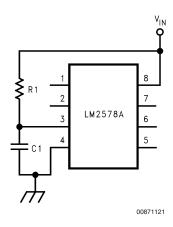

#### MAXIMUM DUTY CYCLE LIMITING

The maximum duty cycle can be externally limited by adjusting the charge to discharge ratio of the oscillator capacitor with a single external resistor. Typical values are 50  $\mu$ A for the charge current, 450  $\mu$ A for the discharge current, and a voltage swing from 200 mV to 750 mV. Therefore, R1 is selected for the desired charging and discharging slopes and C1 is readjusted to set the oscillator frequency.

## **Applications Information** (Continued)

FIGURE 9. Maximum Duty Cycle Limiting

#### **DUTY CYCLE ADJUSTMENT**

When manual or mechanical selection of the output transistor's duty cycle is needed, the cirucit shown below may be used. The output will turn on with the beginning of each oscillator cycle and turn off when the current sunk by R2 and R3 from the non-inverting terminal becomes greater than the current sunk from the inverting terminal.

With the resistor values as shown, R3 can be used to adjust the duty cycle from 0% to 90%.

When the sum of R2 and R3 is twice the value of R1, the duty cycle will be about 50%. C1 may be a large electrolytic capacitor to lower the oscillator frequency below 1 Hz.

FIGURE 10. Duty Cycle Adjustment

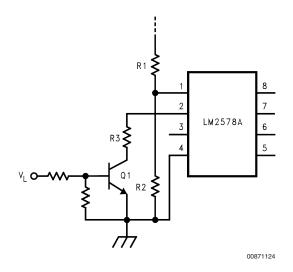

#### **REMOTE SHUTDOWN**

The LM2578A may be remotely shutdown by sinking a greater current from the non-inverting input than from the inverting input. This may be accomplished by selecting resistor R3 to be approximately one-half the value of R1 and R2 in parallel.

FIGURE 11. Shutdown Occurs when V<sub>L</sub> is High

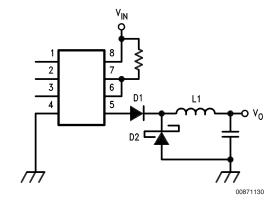

#### **EMITTER OUTPUT**

When the LM2578A output transistor is in the OFF state, if the Emitter output swings below the ground pin voltage, the output transistor will turn ON because its base is clamped near ground. The *Collector Current with Emitter Output Below Ground* curve shows the amount of Collector current drawn in this mode, vs temperature and Emitter voltage. When the Collector-Emitter voltage is high, this current will cause high power dissipation in the output transistor and should be avoided.

This situation can occur in the high-current high-voltage buck application if the Emitter output is used and the catch diode's forward voltage drop is greater than 0.6V. A fast-recovery diode can be added in series with the Emitter output to counter the forward voltage drop of the catch diode (see *Figure 2*). For better efficiency of a high output current buck regulator, an external PNP transistor should be used as shown in *Figure 16*.

FIGURE 12. D1 Prevents Output Transistor from Improperly Turning ON due to D2's Forward Voltage

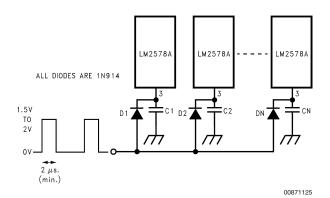

#### SYNCHRONIZING DEVICES

When several devices are to be operated at once, their oscillators may be synchronized by the application of an external signal. This drive signal should be a pulse waveform with a minimum pulse width of 2  $\mu$ s. and an amplitude from

## **Applications Information** (Continued)

1.5V to 2.0V. The signal source must be capable of 1.) driving capacitive loads and 2.) delivering up to 500  $\mu A$  for each LM2578A.

Capacitors C1 thru CN are to be selected for a 20% slower frequency than the synchronization frequency.

FIGURE 13. Synchronizing Devices

## **Typical Applications**

The LM2578A may be operated in either the continuous or the discontinuous conduction mode. The following applications (except for the Buck-Boost Regulator) are designed for continuous conduction operation. That is, the inductor current is not allowed to fall to zero. This mode of operation has higher efficiency and lower EMI characteristics than the discontinuous mode.

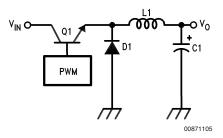

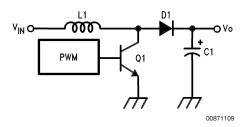

#### **BUCK REGULATOR**

The buck configuration is used to step an input voltage down to a lower level. Transistor Q1 in *Figure 14* chops the input DC voltage into a squarewave. This squarewave is then converted back into a DC voltage of lower magnitude by the low pass filter consisting of L1 and C1. The duty cycle, D, of the squarewave relates the output voltage to the input voltage by the following equation:

$$V_{out} = D \times V_{in} = V_{in} \times (t_{on})/(t_{on} + t_{off})$$

FIGURE 14. Basic Buck Regulator

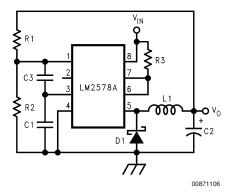

Figure 15 is a 15V to 5V buck regulator with an output current,  $I_o$ , of 350 mA. The circuit becomes discontinuous at 20% of  $I_{o(max)}$ , has 10 mV of output voltage ripple, an efficiency of 75%, a load regulation of 30 mV (70 mA to 350 mA) and a line regulation of 10 mV (12  $\leq$   $V_{in}$   $\leq$  18V).

Component values are selected as follows:

$$R1 = (V_0 - 1) \times R2 \text{ where } R2 = 10 \text{ k}\Omega$$

$R3 = V/I_{sw(max)}$

$R3 = 0.15\Omega$

where:

V is the current limit sense voltage, 0.11V

$\mathbf{I}_{\mathrm{sw(max)}}$  is the maximum allowable current thru the output transistor.

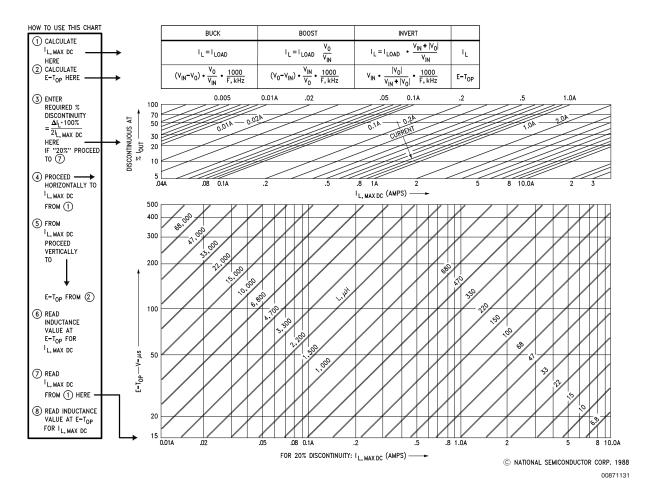

L1 is the inductor and may be found from the inductance calculation chart (*Figure 16*) as follows:

Given V<sub>in</sub> = 15V

$V_0 = 5V$

$I_{o(max)} = 350 \text{ mA}$

$f_{OSC} = 50 \text{ kHz}$

Discontinuous at 20% of I<sub>o(max)</sub>.

Note that since the circuit will become discontinuous at 20% of  $\rm I_{o(max)},$  the load current must not be allowed to fall below 70 mA.

FIGURE 15. Buck or Step-Down Regulator

FIGURE 16. DC/DC Inductance Calculator

**Step 1:** Calculate the maximum DC current through the inductor,  $I_{L(max)}$ . The necessary equations are indicated at the top of the chart and show that  $I_{L(max)} = I_{o(max)}$  for the buck configuration. Thus,  $I_{L(max)} = 350$  mA.

**Step 2:** Calculate the inductor Volts-sec product, E- $T_{\rm op}$ , according to the equations given from the chart. For the Buck:

E-T<sub>op</sub> =

$$(V_{in} - V_{o}) (V_{o}/V_{in}) (1000/f_{osc})$$

= $(15 - 5) (5/15) (1000/50)$

=  $66V$ -µs.

with the oscillator frequency,  $f_{\rm osc}$ , expressed in kHz.

**Step 3:** Using the graph with axis labeled "Discontinuous At %  $I_{OUT}$ " and " $I_{L(max, DC)}$ " find the point where the desired maximum inductor current,  $I_{L(max, DC)}$  intercepts the desired discontinuity percentage.

In this example, the point of interest is where the 0.35A line intersects with the 20% line. This is nearly the midpoint of the horizontal axis.

Step 4: This last step is merely the translation of the point found in Step 3 to the graph directly below it. This is accomplished by moving straight down the page to the point which intercepts the desired E-T $_{\rm op}$ . For this example, E-T $_{\rm op}$  is 66V-µs and the desired inductor value is 470 µH. Since this example was for 20% discontinuity, the bottom chart could have been used directly, as noted in step 3 of the chart instructions.

For a full line of standard inductor values, contact Pulse Engineering (San Diego, Calif.) regarding their PE526XX series, or A. I. E. Magnetics (Nashville, Tenn.).

A more precise inductance value may be calculated for the Buck, Boost and Inverting Regulators as follows:

#### BUCK

$$L = V_o (V_{in} - V_o)/(\Delta I_L V_{in} f_{osc})$$

#### BOOST

$$L = V_{in} (V_o - V_{in})/(\Delta I_L f_{osc} V_o)$$

#### **INVERT**

$$L = V_{in} \ |V_o|/[\Delta I_L(V_{in} + |V_o|)f_{osc}]$$

where  $\Delta I_L$  is the current ripple through the inductor.  $\Delta I_L$  is usually chosen based on the minimum load current expected of the circuit. For the buck regulator, since the inductor current  $I_L$  equals the load current  $I_O$ ,

$$\Delta I_L = 2 \bullet I_{O(min)}$$

$\Delta I_L = 140$  mA for this circuit.  $\Delta I_L$  can also be interpreted as  $\Delta I_L = 2 \bullet \text{ (Discontinuity Factor)} \bullet I_L$

where the Discontinuity Factor is the ratio of the minimum load current to the maximum load current. For this example, the Discontinuity Factor is 0.2.

The remainder of the components of *Figure 15* are chosen as follows:

C1 is the timing capacitor found in Figure 1.

$$C2 \ge V_o (V_{in} - V_o)/(8f_{osc}^2 V_{in} V_{ripple} L1)$$

where  $V_{\text{ripple}}$  is the peak-to-peak output voltage ripple.

C3 is necessary for continuous operation and is generally in the 10 pF to 30 pF range.

D1 should be a Schottky type diode, such as the 1N5818 or 1N5819.

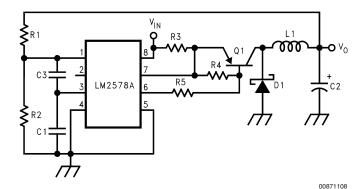

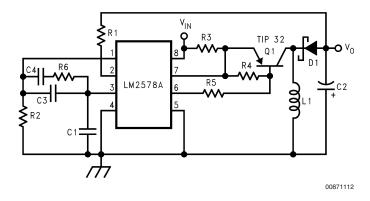

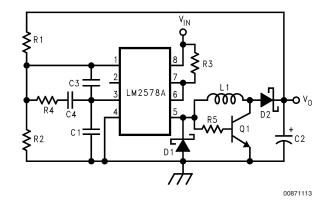

#### **BUCK WITH BOOSTED OUTPUT CURRENT**

For applications requiring a large output current, an external transistor may be used as shown in *Figure 17*. This circuit steps a 15V supply down to 5V with 1.5A of output current. The output ripple is 50 mV, with an efficiency of 80%, a load regulation of 40 mV (150 mA to 1.5A), and a line regulation of 20 mV (12V  $\leq$  V $_{in}$   $\leq$  18V).

Component values are selected as outlined for the buck regulator with a discontinuity factor of 10%, with the addition of R4 and R5:

$$R4 = 10V_{BE1}B_f/I_p$$

$$R5 = (V_{in} - V - V_{BE1} - V_{sat}) B_f/(I_{L(max, DC)} + I_{R4})$$

where

$V_{BE1}$  is the  $V_{BE}$  of transistor Q1.

$V_{\text{sat}}$  is the saturation voltage of the LM2578A output transistor.

V is the current limit sense voltage.

$B_{\rm f}$  is the forced current gain of transistor Q1 (B  $_{\rm f}$  = 30 for Figure 17 ).

$$I_{R4} = V_{BE1}/R4$$

$$I_p = I_{L(max. DC)} + 0.5\Delta I_L$$

$V_{in} = 15V$  $R4 = 200\Omega$  $f_{osc} = 50 \text{ kHz}$ C3 = 20 pF $V_0 = 5V$  $R5 = 330\Omega$  $R1 = 40 \text{ k}\Omega$  $L1 = 220 \mu H$  $V_{ripple} = 50 \text{ mV}$ C1 = 1820 pF $R2 = 10 \text{ k}\Omega$ D1 = 1N5819 $I_0 = 1.5A$  $C2 = 330 \mu F$  $R3 = 0.05\Omega$ Q1 = D45

FIGURE 17. Buck Converter with Boosted Output Current

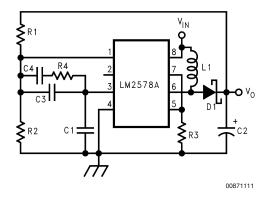

#### **BOOST REGULATOR**

The boost regulator converts a low input voltage into a higher output voltage. The basic configuration is shown in *Figure 18*. Energy is stored in the inductor while the transistor is on and then transferred with the input voltage to the output capacitor for filtering when the transistor is off. Thus,

$$V_o = V_{in} + V_{in}(t_{on}/t_{off}).$$

FIGURE 18. Basic Boost Regulator

The circuit of *Figure 19* converts a 5V supply into a 15V supply with 150 mA of output current, a load regulation of 14 mV (30 mA to 140 mA), and a line regulation of 35 mV  $(4.5V \le V_{\rm in} \le 8.5V)$ .

| $V_{in} = 5V$                | $R4 = 200 \text{ k}\Omega$ |

|------------------------------|----------------------------|

| $V_o = 15V$                  | C1 = 1820 pF               |

| $V_{ripple} = 10 \text{ mV}$ | $C2 = 470 \mu F$           |

| $I_o = 140 \text{ mA}$       | C3 = 20 pF                 |

| $f_{osc} = 50 \text{ kHz}$   | $C4 = 0.0022 \mu F$        |

| $R1 = 140 \text{ k}\Omega$   | $L1 = 330 \mu H$           |

| $R2 = 10 \text{ k}\Omega$    | D1 = 1N5818                |

| $R3 = 0.15\Omega$            |                            |

FIGURE 19. Boost or Step-Up Regulator

$$\begin{split} &\text{R1} = (\text{V}_{\text{o}} - 1) \text{ R2 where R2} = 10 \text{ k}\Omega. \\ &\text{R3} = \text{V/(I}_{\text{L(max, DC)}} + 0.5 \text{ }\Delta\text{I}_{\text{L}}) \\ &\text{where:} \\ &\Delta\text{I}_{\text{L}} = 2(\text{I}_{\text{LOAD(min)}})(\text{V}_{\text{o}}/\text{V}_{\text{in}}) \\ &\Delta\text{I}_{\text{L}} \text{ is 200 mA in this example.} \end{split}$$

R4, C3 and C4 are necessary for continuous operation and are typically 220 k $\Omega$ , 20 pF, and 0.0022  $\mu$ F respectively.

C1 is the timing capacitor found in Figure 1.

$$C2 \ge I_o (V_o - V_{in})/(f_{osc} V_o V_{ripple}).$$

D1 is a Schottky type diode such as a 1N5818 or 1N5819.

L1 is found as described in the buck converter section, using the inductance chart for *Figure 16* for the boost configuration and 20% discontinuity.

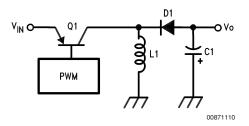

#### **INVERTING REGULATOR**

Figure 20 shows the basic configuration for an inverting regulator. The input voltage is of a positive polarity, but the output is negative. The output may be less than, equal to, or greater in magnitude than the input. The relationship between the magnitude of the input voltage and the output voltage is  $V_o = V_{in} \times (t_{on}/t_{off})$ .

FIGURE 20. Basic Inverting Regulator

Figure 21 shows an LM2578A configured as a 5V to -15V polarity inverter with an output current of 300 mA, a load regulation of 44 mV (60 mA to 300 mA) and a line regulation of 50 mV (4.5V  $\leq$  V $_{in}$   $\leq$  8.5V).

$$\begin{split} \text{R1} &= (\text{IV}_{\text{o}}\text{I} + 1) \text{ R2 where R2} = 10 \text{ k}\Omega. \\ \text{R3} &= \text{V/(I}_{\text{L(max, DC)}} + 0.5 \text{ }\Delta\text{I}_{\text{L}}). \\ \text{R4} &= 10\text{V}_{\text{BE1}}\text{B}_{\text{I}}/(\text{I}_{\text{L (max, DC)}} + 0.5 \text{ }\Delta\text{I}_{\text{L}}) \end{split}$$

where:

$V,\,V_{BE1},\,V_{sat},\,$  and  $B_f$  are defined in the "Buck Converter with Boosted Output Current" section.

$$\Delta I_L = 2(I_{LOAD(min)})(V_{in} + |V_o|)/V_{IN}$$

R5 is defined in the "Buck with Boosted Output Current" section.

R6 serves the same purpose as R4 in the Boost Regulator circuit and is typically 220  $k\Omega.$

C1, C3 and C4 are defined in the "Boost Regulator" section.

$$C2 \ge I_o |V_o|/[f_{osc}(|V_o| + V_{in}) |V_{ripple}]$$

L1 is found as outlined in the section on buck converters, using the inductance chart of *Figure 16* for the invert configuration and 20% discontinuity.

$V_{in} = 5V$  $R4 = 190\Omega$  $f_{\rm osc} = 50 \text{ kHz}$ C3 = 20 pF $V_0 = -15V$  $R1 = 160 \text{ k}\Omega$  $R5 = 82\Omega$  $C4 = 0.0022 \mu F$  $V_{ripple} = 5 \text{ mV}$  $R6 = 220 \text{ k}\Omega$  $R2 = 10 \text{ k}\Omega$  $L1 = 150 \mu H$  $I_0 = 300 \text{ mA}$ C1 = 1820 pF $R3 = 0.01\Omega$ D1 = 1N5818 $C2 = 1000 \mu F$  $I_{min} = 60 \text{ mA}$

FIGURE 21. Inverting Regulator

## **BUCK-BOOST REGULATOR**

The Buck-Boost Regulator, shown in *Figure 22*, may step a voltage up or down, depending upon whether or not the desired output voltage is greater or less than the input voltage. In this case, the output voltage is 12V with an input voltage from 9V to 15V. The circuit exhibits an efficiency of 75%, with a load regulation of 60 mV (10 mA to 100 mA) and a line regulation of 52 mV.

$$R1 = (V_o - 1) R2$$

where  $R2 = 10 k\Omega$

R3 = V/0.75A

R4, C1, C3 and C4 are defined in the "Boost Regulator" section.

D1 and D2 are Schottky type diodes such as the 1N5818 or

$$C2 \geq \frac{\left(I_{o}/V_{ripple}\right)\left(V_{o} + 2V_{d}\right)}{\left[f_{osc}\left(V_{in} + V_{o} + 2V_{d} - V_{sat} - V_{sat1}\right)\right]}$$

where:

V<sub>d</sub> is the forward voltage drop of the diodes.

$\ensuremath{\text{V}_{\text{sat}}}$  is the saturation voltage of the LM2578A output transistor.

V<sub>sat1</sub> is the saturation voltage of transistor Q1.

$$L1 \ge (V_{in} - V_{sat} - V_{sat1}) (t_{on}/I_p)$$

where:

$$\begin{split} t_{on} &= \frac{(1/f_{osc}) \left(V_{o} + 2V_{d}\right)}{\left(V_{o} + V_{in} + 2V_{d} - V_{sat} - V_{sat1}\right)} \\ I_{p} &= \frac{2I_{o} \left(V_{in} + V_{o} + 2V_{d} - V_{sat} - V_{sat1}\right)}{\left(V_{in} - V_{sat} - V_{sat1}\right)} \end{split}$$

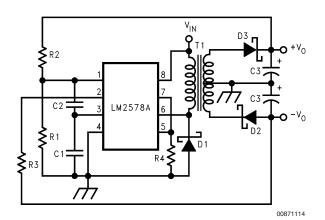

#### **RS-232 LINE DRIVER POWER SUPPLY**

The power supply, shown in *Figure 23*, operates from an input voltage as low as 4.2V (5V nominal), and delivers an output of  $\pm 12$ V at  $\pm 40$  mA with better than 70% efficiency. The circuit provides a load regulation of  $\pm 150$  mV (from 10% to 100% of full load) and a line regulation of  $\pm 10$  mV. Other notable features include a cycle-by-cycle current limit and an output voltage ripple of less than 40 mVp-p.

A unique feature of this circuit is its use of feedback from both outputs. This dual feedback configuration results in a sharing of the output voltage regulation by each output so that neither side becomes unbalanced as in single feedback systems. In addition, since both sides are regulated, it is not necessary to use a linear regulator for output regulation.

The feedback resistors, R2 and R3, may be selected as follows by assuming a value of 10 k $\Omega$  for R1;

R2 =

$$(V_o - 1V)/45.8$$

μA = 240 kΩ

R3 =  $(|V_o| + 1V)/54.2$  μA = 240 kΩ

Actually, the currents used to program the values for the feedback resistors may vary from 40  $\mu\text{A}$  to 60  $\mu\text{A}$ , as long as their sum is equal to the 100  $\mu\text{A}$  necessary to establish the 1V threshold across R1. Ideally, these currents should be equal (50  $\mu\text{A}$  each) for optimal control. However, as was done here, they may be mismatched in order to use standard resistor values. This results in a slight mismatch of regulation between the two outputs.

The current limit resistor, R4, is selected by dividing the current limit threshold voltage by the maximum peak current level in the output switch. For our purposes R4 = 110 mV/  $750 \text{ mA} = 0.15\Omega$ . A value of  $0.1\Omega$  was used.

$9V \leq V_{in} \leq 15V$ R5 = 270 $V_0 = 12V$ C1 = 1820 pF $I_0 = 100 \text{ mA}$  $C2 = 220 \mu F$  $V_{ripple} = 50 \text{ mV}$ C3 = 20 pF $f_{osc} = 50 \text{ kHz}$  $C4 = 0.0022 \mu F$ R1 = 110k $L1 = 220 \mu$ H R2 = 10kD1, D2 = 1N5819 R3 = 0.15Q1 = D44R4 = 220k

FIGURE 22. Buck-Boost Regulator

$\begin{array}{lll} V_{in} = 5V & R4 = 0.15\Omega \\ V_{o} \pm 12V & C1 = 820 \ pF \\ I_{o} = \pm 40 \ mA & C2 = 10 \ pF \\ f_{osc} = 80 \ kHz & C3 = 220 \ \mu F \\ R1 = 10 \ k\Omega & D1, \ D2, \ D3 = 1N5819 \\ R2 = 240 \ k\Omega & T1 = PE-64287 \\ R3 = 240 \ k\Omega & \end{array}$

FIGURE 23. RS-232 Line Driver Power Supply

Capacitor C1 sets the oscillator frequency and is selected from Figure 1.

Capacitor C2 serves as a compensation capacitor for synchronous operation and a value of 10 to 50 pF should be sufficient for most applications.

A minimum value for an ideal output capacitor C3, could be calculated as C =  $I_o$  x  $t/\Delta V$  where  $I_o$  is the load current, t is the transistor on time (typically 0.4/f $_{\rm osc}$ ), and  $\Delta V$  is the peak-to-peak output voltage ripple. A larger output capacitor than this theoretical value should be used since electrolytics have poor high frequency performance. Experience has shown that a value from 5 to 10 times the calculated value should be used

For good efficiency, the diodes must have a low forward voltage drop and be fast switching. 1N5819 Schottky diodes work well.

Transformer selection should be picked for an output transistor "on" time of  $0.4/f_{\rm osc}$ , and a primary inductance high enough to prevent the output transistor switch from ramping higher than the transistor's rating of 750 mA. Pulse Engineering (San Diego, Calif.) and Renco Electronics, Inc. (Deer Park, N.Y.) can provide further assistance in selecting the proper transformer for a specific application need. The transformer used in *Figure 23* was a Pulse Engineering PE-64287.

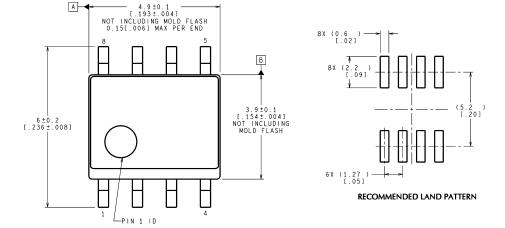

# **Physical Dimensions** inches (millimeters) unless otherwise noted

CONTROLLING DIMENSION IS MILLIMETER

VALUES IN [ ] ARE INCHES

DIMENSIONS IN ( ) FOR REFERENCE ONLY

M08A (Rev K)

Plastic Surface-Mount Package (M) Order Number LM3578AM **NS Package Number M08A**

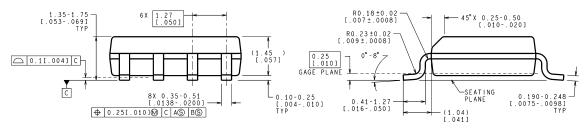

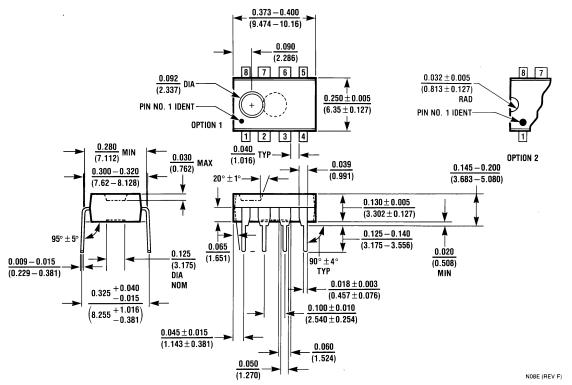

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

Molded Dual-In-Line Package (N)

Order Number LM2578AN or LM3578AN

NS Package Number N08E

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560