# **Integrated Synthesizer and VCO**

Data Sheet ADF4360-8

#### **FEATURES**

Output frequency range: 65 MHz to 400 MHz

3.0 V to 3.6 V power supply

1.8 V logic compatibility

Integer-N synthesizer

Programmable output power level

3-wire serial interface

Digital lock detect

Hardware and software power-down mode

## **APPLICATIONS**

System clock generation Test equipment Wireless LANs CATV equipment

#### **GENERAL DESCRIPTION**

The ADF4360-8 is an integrated integer-N synthesizer and voltage-controlled oscillator (VCO). The ADF4360-8 center frequency is set by external inductors. This allows a frequency range of between 65 MHz to 400 MHz.

Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use.

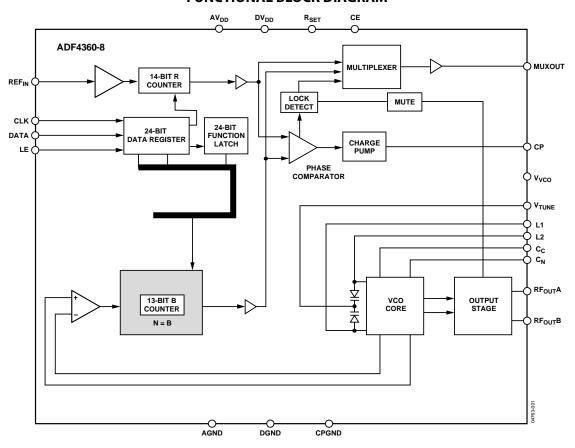

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# ADF4360-8\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS $\Box$

View a parametric search of comparable parts.

# **EVALUATION KITS**

· ADF4360-8 Evaluation Board

# **DOCUMENTATION**

# **Application Notes**

- AN-30: Ask the Applications Engineer PLL Synthesizers

- AN-873: Lock Detect on the ADF4xxx Family of PLL Synthesizers

#### **Data Sheet**

• ADF4360-8: Integrated Synthesizer and VCO Data Sheet

#### **User Guides**

- UG-105: Evaluation Board for the ADF4360-8 Integrated PLL and VCO Frequency Synthesizer

- UG-476: PLL Software Installation Guide

# SOFTWARE AND SYSTEMS REQUIREMENTS 🖵

• ADF4360 - Microcontroller No-OS Driver

# **TOOLS AND SIMULATIONS**

- ADIsimPLL™

- ADIsimRF

# REFERENCE MATERIALS 🖵

#### **Product Selection Guide**

RF Source Booklet

#### **Technical Articles**

- Phase Locked Loops for High-Frequency Receivers and Transmitters – Part 1

- Phase Locked Loops for High-Frequency Receivers and Transmitters – Part 3

- Phase-Locked Loops for High-Frequency Receivers and Transmitters - Part 2

# DESIGN RESOURCES 🖵

- · ADF4360-8 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

# **DISCUSSIONS**

View all ADF4360-8 EngineerZone Discussions.

# SAMPLE AND BUY

Visit the product page to see pricing options.

# TECHNICAL SUPPORT 🖵

Submit a technical question or find your regional support number.

# DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                                                                 |

|------------------------------------------------------------------------------------------|

| Applications1                                                                            |

| General Description1                                                                     |

| Functional Block Diagram 1                                                               |

| Revision History                                                                         |

| Specifications                                                                           |

| Timing Characteristics                                                                   |

| Absolute Maximum Ratings                                                                 |

| Transistor Count                                                                         |

| ESD Caution                                                                              |

| Pin Configuration and Function Descriptions7                                             |

| Typical Performance Characteristics                                                      |

| Circuit Description                                                                      |

| Reference Input Section                                                                  |

| N Counter                                                                                |

| R Counter                                                                                |

| PFD and Charge Pump10                                                                    |

| REVISION HISTORY                                                                         |

| 5/2016—Rev. C to Rev. D  Changed ADF4360 Family to ADF4360-8 and  ADSP-21xx to ADSP-2181 |

| 11/2012—Rev. B to Rev. C         Changes to Table 1                                      |

| <b>2/2012—Rev. A to Rev. B</b> Changes to Figure 3 and Table 4                           |

| Changes to Output Matching Section 23                                                    |

| MUXOUT and Lock Detect                       | 1( |

|----------------------------------------------|----|

| Input Shift Register                         | 11 |

| VCO                                          | 11 |

| Output Stage                                 | 12 |

| Latch Structure                              |    |

| Power-Up                                     | 17 |

| Control Latch                                |    |

| N Counter Latch                              |    |

| R Counter Latch                              |    |

| Applications Information                     |    |

| ••                                           |    |

| Choosing the Correct Inductance Value        | 21 |

| Fixed Frequency LO                           | 21 |

| Interfacing                                  | 22 |

| PCB Design Guidelines for Chip Scale Package | 22 |

| Output Matching                              | 23 |

| Outline Dimensions                           | 24 |

| Ordering Guide                               | 24 |

| Updated Outline Dimensions                   | 24 |

| Changes to Ordering Guide                    |    |

| 01/2005—Rev. 0 to Rev. A                     |    |

| Changes to Table 1                           |    |

| Changes to Table 2                           |    |

| Changes to Figure 20                         |    |

| Added Power-Up Section                       |    |

| Deleted Power-Up Section                     |    |

| Updated Outline Dimensions                   |    |

| Changes to Ordering Guide                    | 24 |

# SPECIFICATIONS1

$AV_{DD} = DV_{DD} = V_{VCO} = 3.3~V \pm 10\%; AGND = DGND = 0~V; T_{A} = T_{MIN}~to~T_{MAX}, unless otherwise~noted.$

Table 1.

| Parameter                                          | <b>B Version</b>      | Unit          | Test Conditions/Comments                                                                             |

|----------------------------------------------------|-----------------------|---------------|------------------------------------------------------------------------------------------------------|

| REF <sub>IN</sub> CHARACTERISTICS                  |                       |               |                                                                                                      |

| REF <sub>IN</sub> Input Frequency                  | 10/250                | MHz min/max   | For f $<$ 10 MHz, use a dc-coupled CMOS-compatible square wave, slew rate $>$ 21 V/ $\mu$ s.         |

| REF <sub>IN</sub> Input Sensitivity                | 0.7/AV <sub>DD</sub>  | V p-p min/max | AC-coupled.                                                                                          |

|                                                    | 0 to AV <sub>DD</sub> | V max         | CMOS-compatible.                                                                                     |

| REF <sub>IN</sub> Input Capacitance                | 5.0                   | pF max        |                                                                                                      |

| REF <sub>IN</sub> Input Current                    | ±60                   | μA max        |                                                                                                      |

| PHASE DETECTOR                                     |                       |               |                                                                                                      |

| Phase Detector Frequency <sup>2</sup>              | 8                     | MHz max       |                                                                                                      |

| CHARGE PUMP                                        |                       |               |                                                                                                      |

| I <sub>CP</sub> Sink/Source <sup>3</sup>           |                       |               | With $R_{SET} = 4.7 \text{ k}\Omega$ .                                                               |

| High Value                                         | 2.5                   | mA typ        |                                                                                                      |

| Low Value                                          | 0.312                 | mA typ        |                                                                                                      |

| RSET Range                                         | 2.7/10                | kΩ            |                                                                                                      |

| Icp Three-State Leakage                            | 0.2                   | nA typ        |                                                                                                      |

| Current                                            |                       |               |                                                                                                      |

| Sink and Source Current<br>Matching                | 2                     | % typ         | $1.25 \text{ V} \le \text{V}_{CP} \le 2.5 \text{ V}.$                                                |

| I <sub>CP</sub> <b>vs. V</b> <sub>CP</sub>         | 1.5                   | % typ         | $1.25 \text{ V} \le \text{V}_{CP} \le 2.5 \text{ V}.$                                                |

| I <sub>CP</sub> vs. Temperature                    | 2                     | % typ         | $V_{CP} = 2.0 \text{ V}.$                                                                            |

| LOGIC INPUTS                                       |                       |               |                                                                                                      |

| V <sub>INH</sub> , Input High Voltage              | 1.5                   | V min         |                                                                                                      |

| V <sub>INL</sub> , Input Low Voltage               | 0.6                   | V max         |                                                                                                      |

| I <sub>INH</sub> /I <sub>INL</sub> , Input Current | ±1                    | μA max        |                                                                                                      |

| C <sub>IN</sub> , Input Capacitance                | 3.0                   | pF max        |                                                                                                      |

| LOGIC OUTPUTS                                      |                       |               |                                                                                                      |

| V <sub>он</sub> , Output High Voltage              | $DV_{DD} - 0.4$       | V min         | CMOS output chosen.                                                                                  |

| Iон, Output High Current                           | 500                   | μA max        |                                                                                                      |

| Vol., Output Low Voltage                           | 0.4                   | V max         | $I_{OL} = 500  \mu A.$                                                                               |

| POWER SUPPLIES                                     |                       |               |                                                                                                      |

| $AV_DD$                                            | 3.0/3.6               | V min/V max   |                                                                                                      |

| $DV_DD$                                            | $AV_{DD}$             |               |                                                                                                      |

| $VV_{CO}$                                          | $AV_{DD}$             |               |                                                                                                      |

| $AI_DD^4$                                          | 5                     | mA typ        |                                                                                                      |

| $DI_DD^4$                                          | 2.5                   | mA typ        |                                                                                                      |

| IV <sub>CO</sub> <sup>4, 5</sup>                   | 12.0                  | mA typ        | I <sub>CORE</sub> = 5 mA.                                                                            |

| I <sub>RFOUT</sub> <sup>4</sup>                    | 3.5 to 11.0           | mA typ        | RF output stage is programmable.                                                                     |

| Low Power Sleep Mode⁴                              | 7                     | μA typ        |                                                                                                      |

| RF OUTPUT CHARACTERISTICS <sup>5</sup>             |                       |               |                                                                                                      |

| Maximum VCO Output Frequency                       | 400                   | MHz           | I <sub>CORE</sub> = 5 mA. Depending on L. See the Choosing the Correct Inductance Value section.     |

| Minimum VCO Output Frequency                       | 65                    | MHz           |                                                                                                      |

| VCO Output Frequency                               | 88/108                | MHz min/max   | L1, L2 = 270 nH. See the Choosing the Correct Inductance Value section for other frequency values.   |

| VCO Frequency Range                                | 1.2                   | Ratio         | F <sub>MAX</sub> /F <sub>MIN</sub>                                                                   |

| VCO Sensitivity                                    | 2                     | MHz/V typ     | L1, L2 = 270 nH. See the Choosing the Correct Inductance Value section for other sensitivity values. |

| Lock Time <sup>6</sup>                             | 400                   | μs typ        | To within 10 Hz of final frequency.                                                                  |

| Frequency Pushing (Open Loop)                      | 0.24                  | MHz/V typ     |                                                                                                      |

| Parameter                                                  | <b>B Version</b> | Unit        | Test Conditions/Comments                                                            |

|------------------------------------------------------------|------------------|-------------|-------------------------------------------------------------------------------------|

| Frequency Pulling (Open Loop)                              | 10               | Hz typ      | Into 2.00 VSWR load.                                                                |

| Harmonic Content (Second)                                  | -16              | dBc typ     |                                                                                     |

| Harmonic Content (Third)                                   | -21              | dBc typ     |                                                                                     |

| Output Power <sup>5, 7</sup>                               | -9/0             | dBm typ     | Using tuned load, programmable in 3 dB steps; see Table 7.                          |

| Output Power <sup>5, 8</sup>                               | -14/-9           | dBm typ     | Using 50 $\Omega$ resistors to $V_{VCO}$ , programmable in 3 dB steps; see Table 7. |

| Output Power Variation                                     | ±3               | dB typ      |                                                                                     |

| VCO Tuning Range                                           | 1.25/2.5         | V min/max   |                                                                                     |

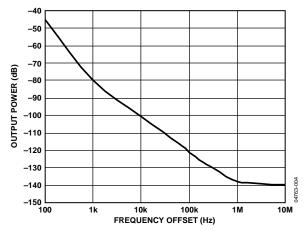

| NOISE CHARACTERISTICS <sup>5</sup>                         |                  |             |                                                                                     |

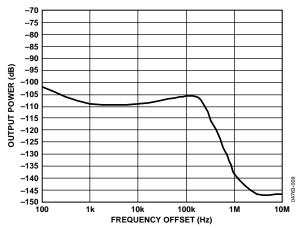

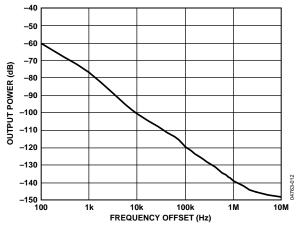

| VCO Phase Noise Performance9                               | -120             | dBc/Hz typ  | At 100 kHz offset from carrier.                                                     |

|                                                            | -139             | dBc/Hz typ  | At 800 kHz offset from carrier.                                                     |

|                                                            | -140             | dBc/Hz typ  | At 3 MHz offset from carrier.                                                       |

|                                                            | -142             | dBc/Hz typ  | At 10 MHz offset from carrier.                                                      |

| Synthesizer Phase Noise Floor 10                           | -160             | dBc/Hz typ  | At 200 kHz PFD frequency.                                                           |

|                                                            | -150             | dBc/Hz typ  | At 1 MHz PFD frequency.                                                             |

|                                                            | -142             | dBc/Hz typ  | At 8 MHz PFD frequency.                                                             |

| Phase Noise Figure of Merit <sup>10</sup>                  | -215             | dBc/Hz typ  |                                                                                     |

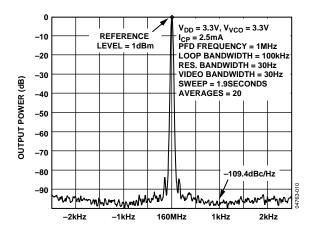

| In-Band Phase Noise <sup>11, 12</sup>                      | -102             | dBc/Hz typ  | At 1 kHz offset from carrier.                                                       |

| RMS Integrated Phase Error <sup>13</sup>                   | 0.09             | Degrees typ | 100 Hz to 100 kHz.                                                                  |

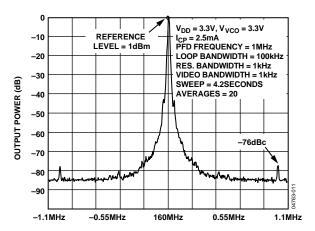

| Spurious Signals due to PFD<br>Frequency <sup>12, 14</sup> | <b>-75</b>       | dBc typ     |                                                                                     |

| Level of Unlocked Signal with<br>MTLD Enabled              | -70              | dBm typ     |                                                                                     |

<sup>&</sup>lt;sup>1</sup> Operating temperature range is –40°C to +85°C.

<sup>&</sup>lt;sup>2</sup> Guaranteed by design. Sample tested to ensure compliance.

<sup>3</sup> I<sub>CP</sub> is internally modified to maintain constant loop gain over the frequency range.

$<sup>^4\,</sup>T_A=25^{\circ}C;\,AV_{DD}^{\cdot}=DV_{DD}=V_{VCO}=3.3\;V.$

<sup>&</sup>lt;sup>5</sup> Unless otherwise stated, these characteristics are guaranteed for VCO core power = 5 mA. L1, L2 = 270 nH, 470  $\Omega$  resistors to GND in parallel with L1, L2.

<sup>&</sup>lt;sup>6</sup> Jumping from 88 MHz to 108 MHz. PFD frequency = 200 kHz; loop bandwidth = 10 kHz. <sup>7</sup> For more detail on using tuned loads, see the Output Matching section.

$<sup>^8</sup>$  Using 50  $\Omega$  resistors to  $V_{VCO}$ , into a 50  $\Omega$  load.

<sup>&</sup>lt;sup>9</sup> The noise of the VCO is measured in open-loop conditions.

<sup>10</sup> The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log N (where N is the N divider value). The

phase noise figure of merit subtracts 10 log (PFD frequency).

The phase noise is measured with the EV-ADF4360-8EB1Z evaluation board and the HP 8562E spectrum analyzer. The spectrum analyzer provides the REF<sub>IN</sub> for the synthesizer; offset frequency = 1 kHz.

$<sup>^{12}</sup>$  f<sub>REFIN</sub> = 10 MHz; f<sub>PFD</sub> = 200 kHz; N = 1000; loop bandwidth = 10 kHz.

$<sup>^{13}</sup>$  f<sub>REFIN</sub> = 10 MHz; f<sub>PFD</sub> = 1 MHz; N = 120; loop bandwidth = 100 kHz.

<sup>14</sup> The spurious signals are measured with the EV-ADF4360-8EB1Z evaluation board and the HP 8562E spectrum analyzer. The spectrum analyzer provides the REF<sub>IN</sub> for the synthesizer;  $f_{REFOUT} = 10 \text{ MHz}$  at 0 dBm.

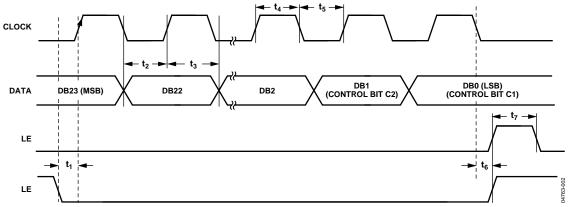

# TIMING CHARACTERISTICS<sup>1</sup>

$AV_{DD} = DV_{DD} = V_{VCO} = 3.3 \ V \pm 10\%; AGND = DGND = 0 \ V; 1.8 \ V \ and \ 3 \ V \ logic levels used; T_A = T_{MIN} \ to \ T_{MAX}, unless \ otherwise \ noted.$

Table 2.

| Parameter      | Limit at T <sub>MIN</sub> to T <sub>MAX</sub> (B Version) | Unit   | Test Conditions/Comments |

|----------------|-----------------------------------------------------------|--------|--------------------------|

| t <sub>1</sub> | 20                                                        | ns min | LE setup time            |

| $t_2$          | 10                                                        | ns min | DATA to CLOCK setup time |

| t <sub>3</sub> | 10                                                        | ns min | DATA to CLOCK hold time  |

| t <sub>4</sub> | 25                                                        | ns min | CLOCK high duration      |

| t <sub>5</sub> | 25                                                        | ns min | CLOCK low duration       |

| t <sub>6</sub> | 10                                                        | ns min | CLOCK to LE setup time   |

| $t_7$          | 20                                                        | ns min | LE pulse width           |

$<sup>^{\</sup>rm 1}$  Refer to the Power-Up section for the recommended power-up procedure for this device.

Figure 2. Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                            | Rating                                     |

|--------------------------------------|--------------------------------------------|

| AV <sub>DD</sub> to GND <sup>1</sup> | -0.3 V to +3.9 V                           |

| $AV_{DD}$ to $DV_{DD}$               | -0.3 V to +0.3 V                           |

| V <sub>vco</sub> to GND              | -0.3 V to +3.9 V                           |

| $V_{VCO}$ to $AV_{DD}$               | -0.3 V to +0.3 V                           |

| Digital I/O Voltage to GND           | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Analog I/O Voltage to GND            | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| REF <sub>IN</sub> to GND             | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Operating Temperature Range          | -40°C to + 85°C                            |

| Storage Temperature Range            | −65°C to +150°C                            |

| Maximum Junction Temperature         | 150°C                                      |

| CSP $\theta_{JA}$ Thermal Impedance  |                                            |

| Paddle Soldered                      | 50°C/W                                     |

| Paddle Not Soldered                  | 88°C/W                                     |

| Lead Temperature, Soldering Reflow   | 260°C                                      |

$<sup>^{1}</sup>$  GND = AGND = DGND = 0 V.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

This device is a high performance RF integrated circuit with an ESD rating of <1 kV, and it is ESD sensitive. Proper precautions should be taken for handling and assembly.

# TRANSISTOR COUNT

12543 (CMOS) and 700 (Bipolar)

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

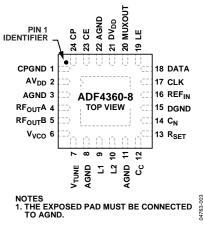

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.      | Mnemonic            | Description                                                                                                                                                                                                                                   |

|--------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | CPGND               | Charge Pump Ground. This is the ground return path for the charge pump.                                                                                                                                                                       |

| 2            | $AV_DD$             | Analog Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. $AV_{DD}$ must have the same value as $DV_{DD}$ .                                   |

| 3, 8, 11, 22 | AGND                | Analog Ground. This is the ground return path of the prescaler and VCO.                                                                                                                                                                       |

| 4            | RF <sub>OUT</sub> A | VCO Output. The output level is programmable from 0 dBm to -9 dBm. See the Output Matching section for a description of the various output stages.                                                                                            |

| 5            | RF <sub>OUT</sub> B | VCO Complementary Output. The output level is programmable from 0 dBm to –9 dBm. See the Output Matching section for a description of the various output stages.                                                                              |

| 6            | V <sub>vco</sub>    | Power Supply for the VCO. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. V <sub>VCO</sub> must have the same value as AV <sub>DD</sub> .                |

| 7            | V <sub>TUNE</sub>   | Control Input to the VCO. This voltage determines the output frequency and is derived from filtering the CP output voltage.                                                                                                                   |

| 9            | L1                  | An external inductor to AGND should be connected to this pin to set the ADF4360-8 output frequency. L1 and L2 need to be the same value. A 470 $\Omega$ resistor should be added in parallel to AGND.                                         |

| 10           | L2                  | An external inductor to AGND should be connected to this pin to set the ADF4360-8 output frequency. L1 and L2 need to be the same value. A 470 $\Omega$ resistor should be added in parallel to AGND.                                         |

| 12           | Cc                  | Internal Compensation Node. This pin must be decoupled to ground with a 10 nF capacitor.                                                                                                                                                      |

| 13           | R <sub>SET</sub>    | Connecting a resistor between this pin and $CP_{GND}$ sets the maximum charge pump output current for the synthesizer. The nominal voltage potential at the $R_{SET}$ pin is 0.6 V. The relationship between $I_{CP}$ and $R_{SET}$ is        |

|              |                     | $I_{CPmax} = \frac{11.75}{R_{SET}}$                                                                                                                                                                                                           |

|              |                     | where $R_{SET} = 4.7 \text{ k}\Omega$ , $I_{CPmax} = 2.5 \text{ mA}$ .                                                                                                                                                                        |

| 14           | C <sub>N</sub>      | Internal Compensation Node. This pin must be decoupled to $V_{VCO}$ with a 10 $\mu F$ capacitor.                                                                                                                                              |

| 15           | DGND                | Digital Ground.                                                                                                                                                                                                                               |

| 16           | REF <sub>IN</sub>   | Reference Input. This is a CMOS input with a nominal threshold of $V_{DD}/2$ and a dc equivalent input resistance of 100 k $\Omega$ (see Figure 16). This input can be driven from a TTL or CMOS crystal oscillator, or it can be ac-coupled. |

| 17           | CLK                 | Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                             |

| 18           | DATA                | Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control bits. This input is a high impedance CMOS input.                                                                                                   |

| 19           | LE                  | Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, and the relevant latch is selected using the control bits.                                                         |

| 20           | MUXOUT              | This multiplexer output lets either the lock detect, the scaled RF, or the scaled reference frequency be accessed externally.                                                                                                                 |

| 21           | $DV_{DD}$           | Digital Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the digital ground plane should be placed as close as possible to this pin. $DV_{DD}$ must have the same value as $AV_{DD}$ .                                 |

| 23           | CE                  | Chip Enable. A logic low on this pin powers down the device and puts the charge pump into three-state mode. Taking the pin high powers up the device depending on the status of the power-down bits.                                          |

| 24           | СР                  | Charge Pump Output. When enabled, this provides $\pm I_{\mathbb{CP}}$ to the external loop filter, which in turn drives the internal VCO.                                                                                                     |

|              | EP                  | Exposed Pad. The exposed pad must be connected to AGND.                                                                                                                                                                                       |

# TYPICAL PERFORMANCE CHARACTERISTICS

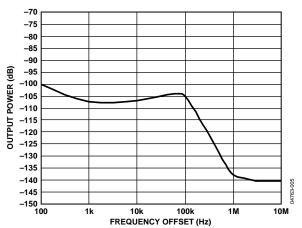

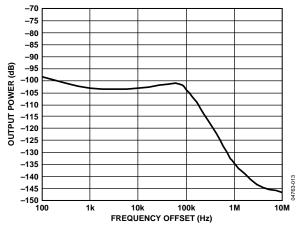

Figure 4. Open-Loop VCO Phase Noise, L1, L2 = 560 nH

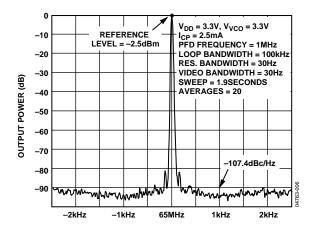

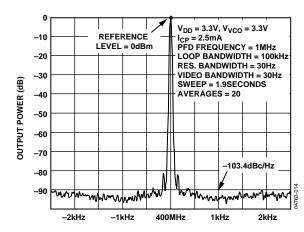

Figure 5. VCO Phase Noise, 65 MHz, 1 MHz PFD, 100 kHz Loop Bandwidth

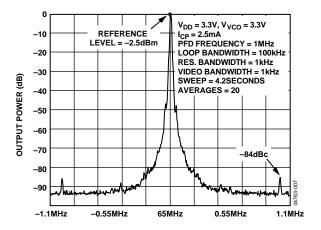

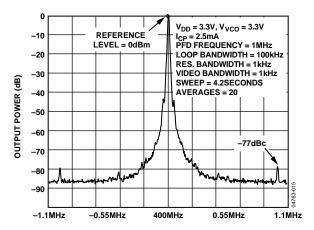

Figure 6. Close-In Phase Noise at 65 MHz (1 MHz Channel Spacing)

Figure 7. Reference Spurs at 65 MHz (1 MHz Channel Spacing, 100 kHz Loop Bandwidth)

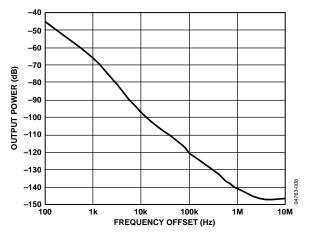

Figure 8. Open-Loop VCO Phase Noise, L1, L2 = 110 nH

Figure 9. VCO Phase Noise, 160 MHz, 1 MHz PFD, 100 kHz Loop Bandwidth

Figure 10. Close-In Phase Noise at 160 MHz (1 MHz Channel Spacing)

Figure 11. Reference Spurs at 160 MHz (1 MHz Channel Spacing, 100 kHz Loop Bandwidth)

Figure 12. Open-Loop VCO Phase Noise, L1, L2 = 18 nH

Figure 13. VCO Phase Noise, 400 MHz, 1 MHz PFD, 100 kHz Loop Bandwidth

Figure 14. Close-In Phase Noise at 400 MHz (1 MHz Channel Spacing)

Figure 15. Reference Spurs at 400 MHz (1 MHz Channel Spacing, 100 kHz Loop Bandwidth)

# **CIRCUIT DESCRIPTION**

## REFERENCE INPUT SECTION

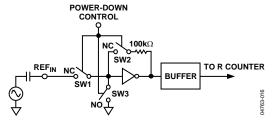

The reference input stage is shown in Figure 16. SW1 and SW2 are normally closed switches. SW3 is normally open. When power-down is initiated, SW3 is closed, and SW1 and SW2 are opened. This ensures that there is no loading of the REF $_{\rm IN}$  pin on power-down.

Figure 16. Reference Input Stage

#### **N COUNTER**

The CMOS N counter allows a wide division ratio in the PLL feedback counter. The counters are specified to work when the VCO output is 400 MHz or less. To avoid confusion, this is referred to as the B counter. It makes it possible to generate output frequencies that are spaced only by the reference frequency divided by *R*. The VCO frequency equation is

$$f_{VCO} = B \times f_{REFIN} / R$$

where:

$f_{VCO}$  is the output frequency of the VCO.

*B* is the preset divide ratio of the binary 13-bit counter (3 to 8191). *f*<sub>REFIN</sub> is the external reference frequency oscillator.

## **R COUNTER**

The 14-bit R counter allows the input reference frequency to be divided down to produce the reference clock to the phase frequency detector (PFD). Division ratios from 1 to 16,383 are allowed.

## **PFD AND CHARGE PUMP**

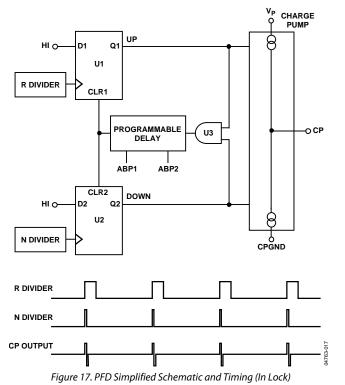

The PFD takes inputs from the R counter and N counter (N = BP + A) and produces an output proportional to the phase and frequency difference between them. Figure 17 is a simplified schematic. The PFD includes a programmable delay element that controls the width of the antibacklash pulse. This pulse ensures that there is no dead zone in the PFD transfer function, and minimizes phase noise and reference spurs. Two bits in the R counter latch, ABP2 and ABP1, control the width of the pulse (see Table 9).

MUXOUT AND LOCK DETECT

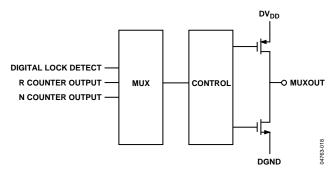

The output multiplexer on the ADF4360-8 allows the user to access various internal points on the chip. The state of MUX-OUT is controlled by M3, M2, and M1 in the function latch. The full truth table is shown in Table 7. Figure 18 shows the MUXOUT section in block diagram form.

Figure 18. MUXOUT Circuit

#### **Lock Detect**

MUXOUT can be programmed for one type of lock detect. Digital lock detect is active high. When LDP in the R counter latch is set to 0, digital lock detect is set high when the phase error on three consecutive phase detector cycles is less than 15 ns.

With LDP set to 1, five consecutive cycles of less than 15 ns phase error are required to set the lock detect. It stays set high until a phase error of greater than 25 ns is detected on any subsequent PD cycle.

# **INPUT SHIFT REGISTER**

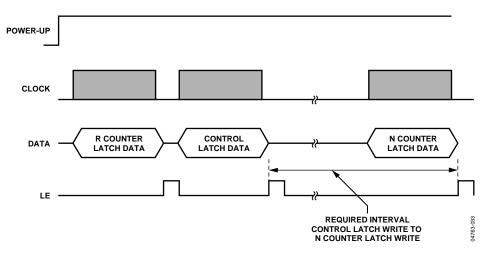

The digital section of the ADF4360-8 includes a 24-bit input shift register, a 14-bit R counter, and an 18-bit N counter comprised of a 5-bit A counter and a 13-bit B counter. Data is clocked into the 24-bit shift register on each rising edge of CLK. The data is clocked in MSB first. Data is transferred from the shift register to one of four latches on the rising edge of LE. The destination latch is determined by the state of the two control bits (C2, C1) in the shift register. The two LSBs, DB1 and DB0, are shown in Figure 2.

The truth table for these bits is shown in Table 5. Table 6 shows a summary of how the latches are programmed. Note that the test modes latch is used for factory testing and should not be programmed by the user.

Table 5. C2 and C1 Truth Table

|    | Control Bits |                  |

|----|--------------|------------------|

| C2 | C1           | Data Latch       |

| 0  | 0            | Control Latch    |

| 0  | 1            | R Counter        |

| 1  | 0            | N Counter (B)    |

| 1  | 1            | Test Modes Latch |

### VCO

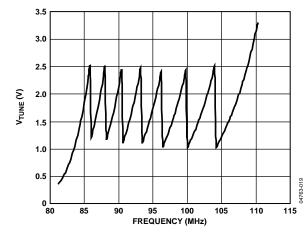

The VCO core in the ADF4360-8 uses eight overlapping bands, as shown in Figure 19, to allow a wide frequency range to be covered without a large VCO sensitivity ( $K_V$ ) and resultant poor phase noise and spurious performance.

The correct band is chosen automatically by the band select logic at power-up or whenever the N counter latch is updated. It is important that the correct write sequence be followed at power-up. This sequence is

- 1. R counter latch

- 2. Control latch

- 3. N counter latch

During band select, which takes five PFD cycles, the VCO  $V_{\text{TUNE}}$  is disconnected from the output of the loop filter and connected to an internal reference voltage.

Figure 19. Frequency vs.  $V_{TUNE}$ , ADF4360-8, L1 and L2 = 270 nH

The R counter output is used as the clock for the band select logic and should not exceed 1 MHz. A programmable divider is provided at the R counter input to allow division by 1, 2, 4, or 8, and is controlled by the BSC1 bit and the BSC2 bit in the R counter latch. Where the required PFD frequency exceeds 1 MHz, the divide ratio should be set to allow enough time for correct band selection.

After band selection, normal PLL action resumes. The value of  $K_V$  is determined by the value of inductors used (see the Choosing the Correct Inductance Value section). The ADF4360-8 contains linearization circuitry to minimize any variation of the product of  $I_{CP}$  and  $K_V$ .

The operating current in the VCO core is programmable in four steps: 2.5 mA, 5 mA, 7.5 mA, and 10 mA. This is controlled by the PC1 bit and the PC2 bit in the control latch.

#### **OUTPUT STAGE**

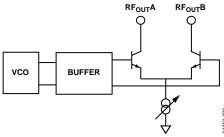

The RFoutA and RFoutB pins of the ADF4360-8 are connected to the collectors of an NPN differential pair driven by buffered outputs of the VCO, as shown in Figure 20. To allow the user to optimize the power dissipation vs. the output power requirements, the tail current of the differential pair is programmable via Bits PL1 and PL2 in the control latch. Four current levels may be set: 3.5 mA, 5 mA, 7.5 mA, and 11 mA. These levels give output power levels of –9 dBm, –6 dBm, –3 dBm, and 0 dBm, respectively, using the correct shunt inductor to  $V_{\rm DD}$  and ac coupling into a 50  $\Omega$  load. Alternatively, both outputs can be combined in a 1 + 1:1 transformer or a 180° microstrip coupler (see the Output Matching section).

If the outputs are used individually, the optimum output stage consists of a shunt inductor to  $V_{\text{\tiny DD}}\text{-}$

Another feature of the ADF4360-8 is that the supply current to the RF output stage is shut down until the device achieves lock, as measured by the digital lock detect circuitry. This is enabled by the Mute-Till-Lock Detect (MTLD) bit in the control latch.

Figure 20. Output Stage ADF4360-8

# **LATCH STRUCTURE**

Table 6 shows the three on-chip latches for the ADF4360-8. The two LSBs decide which latch is programmed.

# **Table 6. Latch Structure**

# **CONTROL LATCH**

| RESERVED | RESERVED | POWER-<br>DOWN 2 | POWER-<br>DOWN 1 |      | JRREN'<br>ETTING |      |      | URREN<br>ETTING |      | POV  | PUT<br>VER<br>/EL | MUTE-TIL-<br>LD | CP GAIN | CP<br>THREE-<br>STATE | PHASE<br>DETECTOR<br>POLARITY |     | MUXOU |     | COUNTER<br>RESET | CO<br>POV<br>LEV | VER |        | TROL<br>TS |

|----------|----------|------------------|------------------|------|------------------|------|------|-----------------|------|------|-------------------|-----------------|---------|-----------------------|-------------------------------|-----|-------|-----|------------------|------------------|-----|--------|------------|

| DB23     | DB22     | DB21             | DB20             | DB19 | DB18             | DB17 | DB16 | DB15            | DB14 | DB13 | DB12              | DB11            | DB10    | DB9                   | DB8                           | DB7 | DB6   | DB5 | DB4              | DB3              | DB2 | DB1    | DB0        |

| RSV      | RSV      | PD2              | PD1              | CPI6 | CPI5             | CPI4 | CPI3 | CPI2            | CPI1 | PL2  | PL1               | MTLD            | CPG     | СР                    | PDP                           | М3  | M2    | M1  | CR               | PC2              | PC1 | C2 (0) | C1 (0)     |

# N COUNTER LATCH

| RESERVED | RESERVED | CP GAIN |      | 13-BIT B COUNTER                                              |  |  |  |  |  |  |  |     |     | RESE | RVED |     |     |        | TROL<br>TS |

|----------|----------|---------|------|---------------------------------------------------------------|--|--|--|--|--|--|--|-----|-----|------|------|-----|-----|--------|------------|

| DB23     | DB22     | DB21    | DB20 | B20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 |  |  |  |  |  |  |  | DB7 | DB6 | DB5  | DB4  | DB3 | DB2 | DB1    | DB0        |

| RSV      | RSV      | CPG     | B13  | B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1                    |  |  |  |  |  |  |  | RSV | RSV | RSV  | RSV  | RSV | RSV | C2 (1) | C1 (0)     |

# R COUNTER LATCH

| RESERVED | RESERVED | SEL  | EC!  | TEST<br>MODE<br>BIT | LOCK<br>DETECT<br>PRECISION | BACK<br>PUI | ITI-<br>(LASH<br>LSE<br>OTH |      | 14-BIT REFERENCE COUNTER |      |      |      |      |     |     |     |     |     | TROL<br>TS |     |     |        |        |

|----------|----------|------|------|---------------------|-----------------------------|-------------|-----------------------------|------|--------------------------|------|------|------|------|-----|-----|-----|-----|-----|------------|-----|-----|--------|--------|

| DB23     | DB22     | DB21 | DB20 | DB19                | DB18                        | DB17        | DB16                        | DB15 | DB14                     | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4        | DB3 | DB2 | DB1    | DB0    |

| RSV      | RSV      | BSC2 | BSC1 | ТМВ                 | LDP                         | ABP2        | ABP1                        | R14  | R13                      | R12  | R11  | R10  | R9   | R8  | R7  | R6  | R5  | R4  | R3         | R2  | R1  | C2 (0) | C1 (1) |

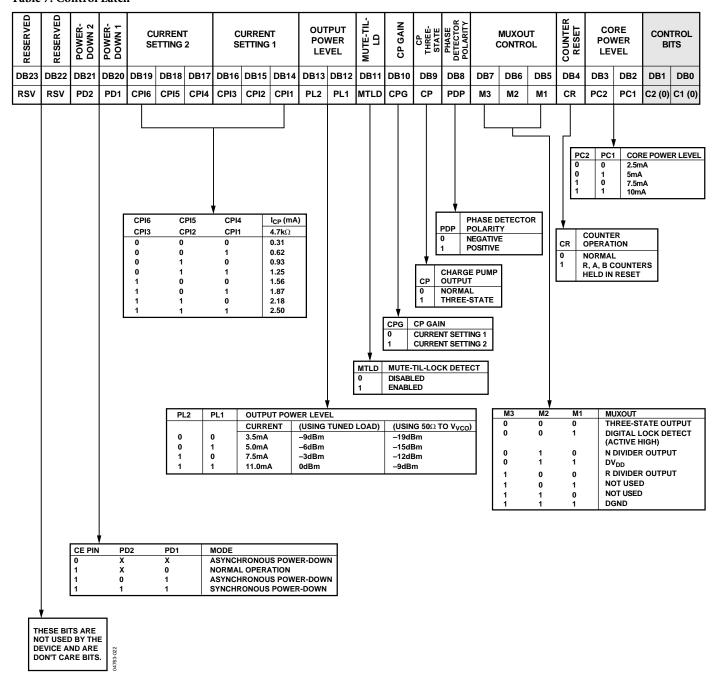

Table 7. Control Latch

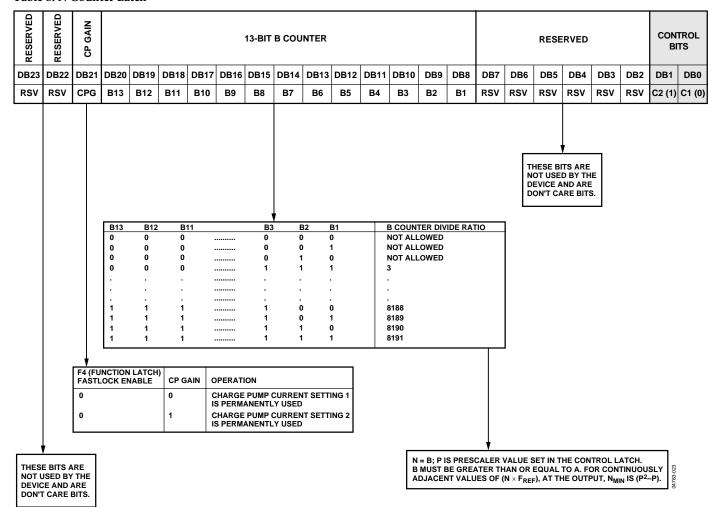

**Table 8. N Counter Latch**

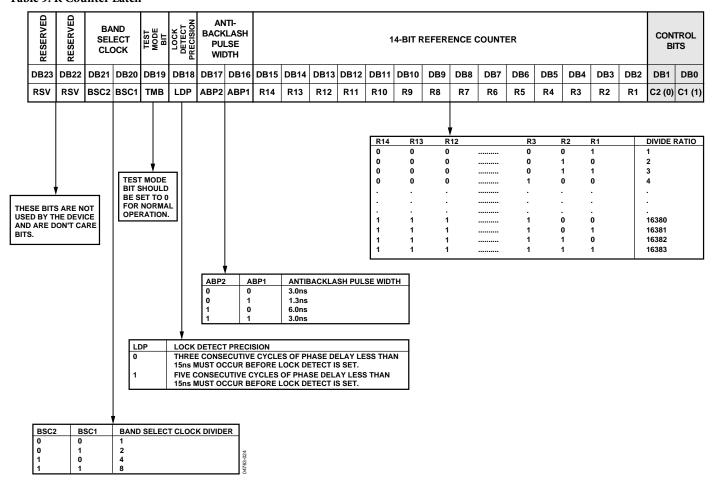

**Table 9. R Counter Latch**

#### **POWER-UP**

#### Power-Up Sequence

The correct programming sequence for the ADF4360-8 after power-up is

- 1. R counter latch

- 2. Control latch

- N counter latch

# **Initial Power-Up**

Initial power-up refers to programming the device after the application of voltage to the  $AV_{\rm DD}$ ,  $DV_{\rm DD}$ ,  $V_{\rm VCO}$ , and CE pins. On initial power-up, an interval is required between programming the control latch and programming the N counter latch. This interval is necessary to allow the transient behavior of the ADF4360-8 during initial power-up to settle.

During initial power-up, a write to the control latch powers up the device, and the bias currents of the VCO begin to settle. If these currents have not settled to within 10% of their steady-state value, and if the N counter latch is then programmed, the VCO may not oscillate at the desired frequency, which does not allow the band select logic to choose the correct frequency band, and the ADF4360-8 may not achieve lock. If the recommended interval is inserted, and the N counter latch is programmed, the band select logic can choose the correct frequency band, and the device locks to the correct frequency.

The duration of this interval is affected by the value of the capacitor on the  $C_N$  pin (Pin 14). This capacitor is used to reduce the close-in noise of the ADF4360-8 VCO. The recommended value of this capacitor is 10  $\mu$ F. Using this value requires an interval of  $\geq$ 15 ms between the latching in of the control latch bits and latching in of the N counter latch bits. If a shorter delay is required, the capacitor can be reduced. A slight phase noise penalty is incurred by this change, which is further explained in Table 10.

Table 10. C<sub>N</sub> Capacitance vs. Interval and Phase Noise

| C <sub>N</sub> | Recommended Interval Between      | Ope                 | Open-Loop Phase Noise at 10 kHz Offset |                      |  |  |  |  |  |  |  |

|----------------|-----------------------------------|---------------------|----------------------------------------|----------------------|--|--|--|--|--|--|--|

| Value          | Control Latch and N Counter Latch | L1 and L2 = 18.0 nH | L1 and L2 = 110.0 nH                   | L1 and L2 = 560.0 nH |  |  |  |  |  |  |  |

| 10 μF          | ≥15 ms                            | -100 dBc/Hz         | −97 dBc/Hz                             | −99 dBc/Hz           |  |  |  |  |  |  |  |

| 440 nF         | ≥ 600 µs                          | −99 dBc/Hz          | −96 dBc/Hz                             | –98 dBc/Hz           |  |  |  |  |  |  |  |

Figure 21. ADF4360-8 Power-Up Timing

### Hardware Power-Up/Power-Down

If the device is powered down via the hardware (using the CE pin) and powered up again without any change to the N counter register during power-down, the device locks at the correct frequency, because the device is already in the correct frequency band. The lock time depends on the value of capacitance on the  $C_{\rm N}$  pin, which is <15 ms for 10  $\mu$ F capacitance. The smaller capacitance of 440 nF on this pin enables lock times of <600  $\mu$ s.

The N counter value cannot be changed while the device is in power-down, since the device may not lock to the correct frequency on power-up. If it is updated, the correct programming sequence for the device after power-up is the R counter latch, followed by the control latch, and finally the N counter latch, with the required interval between the control latch and N counter latch, as described in the Initial Power-Up section.

### Software Power-Up/Power-Down

If the device is powered down via the software (using the control latch) and powered up again without any change to the N counter latch during power-down, the device locks at the correct frequency, because the device is already in the correct frequency band. The lock time depends on the value of capacitance on the  $C_{\rm N}$  pin, which is <15 ms for 10  $\mu F$  capacitance. The smaller capacitance of 440 nF on this pin enables lock times of <600  $\mu s$ .

The N counter value cannot be changed while the device is in power-down, because the device may not lock to the correct frequency on power-up. If it is updated, the correct programming sequence for the device after power-up is to the R counter latch, followed by the control latch, and finally the N counter latch, with the required interval between the control latch and N counter latch, as described in the Initial Power-Up section.

#### **CONTROL LATCH**

With (C2, C1) = (0, 0), the control latch is programmed. Table 7 shows the input data format for programming the control latch.

#### Power-Down

DB21 (PD2) and DB20 (PD1) provide programmable powerdown modes.

In the programmed asynchronous power-down, the device powers down immediately after latching a 1 into Bit PD1, with the condition that PD2 has been loaded with a 0. In the programmed synchronous power-down, the device power-down is gated by the charge pump to prevent unwanted frequency jumps. Once the power-down is enabled by writing a 1 into Bit PD1 (on the condition that a 1 has also been loaded to PD2), the device goes into power-down on the second rising edge of the R counter output, after LE goes high. When the CE pin is low, the device is immediately disabled, regardless of the state of PD1 or PD2.

When a power-down is activated (either synchronous or asynchronous mode), the following events occur:

- All active dc current paths are removed.

- The R, N, and timeout counters are forced to their load state conditions.

- The charge pump is forced into three-state mode.

- The digital lock detect circuitry is reset.

- The RF outputs are de-biased to a high impedance state.

- The reference input buffer circuitry is disabled.

- The input register remains active and capable of loading and latching data.

### **Charge Pump Currents**

CPI3, CPI2, and CPI1 in the ADF4360-8 determine Current Setting 1.

CPI6, CPI5, and CPI4 determine Current Setting 2. See the truth table in Table 7.

## **Output Power Level**

Bits PL1 and PL2 set the output power level of the VCO. See the truth table in Table 7.

#### Mute-Till-Lock Detect

DB11 of the control latch in the ADF4360-8 is the Mute-Till-Lock Detect bit. This function, when enabled, ensures that the RF outputs are not switched on until the PLL is locked.

#### **CP** Gain

DB10 of the control latch in the ADF4360-8 is the Charge Pump Gain bit. When it is programmed to 1, Current Setting 2 is used. When programmed to 0, Current Setting 1 is used.

## **Charge Pump Three-State**

This bit puts the charge pump into three-state mode when programmed to a 1. It should be set to 0 for normal operation.

## **Phase Detector Polarity**

The PDP bit in the ADF4360-8 sets the phase detector polarity. The positive setting enabled by programming a 1 is used when using the on-chip VCO with a passive loop filter or with an active non-inverting filter. It can also be set to 0, which is required if an active inverting loop filter is used.

# **MUXOUT Control**

The on-chip multiplexer is controlled by M3, M2, and M1. See the truth table in Table 7.

## **Counter Reset**

DB4 is the counter reset bit for the ADF4360-8. When this is 1, the R counter and the A, B counters are reset. For normal operation, this bit should be 0.

## **Core Power Level**

PC1 and PC2 set the power level in the VCO core. The recommended setting is  $5\,\mathrm{mA}$ . See the truth table in Table 7.

#### N COUNTER LATCH

Table 8 shows the input data format for programming the N counter latch.

### **Reserved Bits**

DB2 to DB7 are spare bits and have been designated as reserved. They should be programmed to 0.

#### **B** Counter Latch

B13 to B1 program the B counter. The divide range is 3 (00...0011) to 8191 (11...111).

## **Overall Divide Range**

The overall VCO feedback divide range is defined by B.

#### **CP** Gain

DB21 of the N counter latch in the ADF4360-8 is the charge pump gain bit. When it is programmed to 1, Current Setting 2 is used. When programmed to 0, Current Setting 1 is used. This bit can also be programmed through DB10 of the control latch. The bit always reflects the latest value written to it, whether this is through the control latch or the N counter latch.

#### R COUNTER LATCH

With (C2, C1) = (0, 1), the R counter latch is programmed. Table 9 shows the input data format for programming the R counter latch.

#### R Counter

R1 to R14 set the counter divide ratio. The divide range is 1 (00...001) to 16383 (111...111).

#### **Antibacklash Pulse Width**

DB16 and DB17 set the antibacklash pulse width.

## **Lock Detect Precision**

DB18 is the lock detect precision bit. This bit sets the number of reference cycles with less than 15 ns phase error for entering the locked state. With LDP at 1, five cycles are taken; with LDP at 0, three cycles are taken.

#### **Test Mode Bit**

DB19 is the test mode bit (TMB) and should be set to 0. With TMB = 0, the contents of the test mode latch are ignored and normal operation occurs, as determined by the contents of the control latch, R counter latch, and N counter latch. Note that test modes are for factory testing only and should not be programmed by the user.

## **Band Select Clock**

These bits set a divider for the band select logic clock input. The output of the R counter is, by default, the value used to clock the band select logic; if this value is too high (>1 MHz), a divider can be switched on to divide the R counter output to a smaller value (see Table 9).

## **Reserved Bits**

DB23 to DB22 are spare bits that have been designated as reserved. They should be programmed to 0.

# APPLICATIONS INFORMATION

## **CHOOSING THE CORRECT INDUCTANCE VALUE**

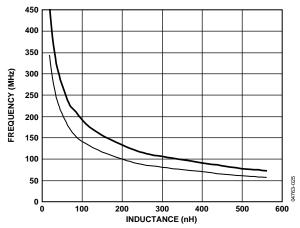

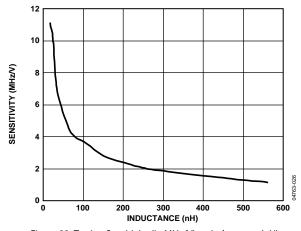

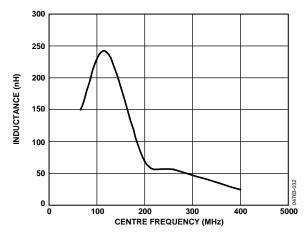

The ADF4360-8 can be used at many different frequencies simply by choosing the external inductors to give the correct output frequency. Figure 22 shows a graph of both minimum and maximum frequency vs. the external inductor value. The correct inductor should cover the maximum and minimum frequencies desired. The inductors used are 0603 CS or 0805 CS type from Coilcraft. To reduce mutual coupling, the inductors should be placed at right angles to one another.

The lowest center frequency of oscillation possible is approximately 65 MHz, which is achieved using 560 nH inductors. This relationship can be expressed by

$$F_O = \frac{1}{2\pi\sqrt{9.3 \text{ pF}(0.9 \text{ nH} + L_{EXT})}}$$

where  $F_O$  is the center frequency and  $L_{EXT}$  is the external inductance.

Figure 22. Output Center Frequency vs. External Inductor Value

The approximate value of capacitance at the midpoint of the center band of the VCO is 9.3 pF, and the approximate value of internal inductance due to the bond wires is 0.9 nH. The VCO sensitivity is a measure of the frequency change vs. the tuning voltage. It is a very important parameter for the low-pass filter. Figure 23 shows a graph of the tuning sensitivity (in MHz/V) vs. the inductance (nH). It can be seen that as the inductance increases, the sensitivity decreases. This relationship can be derived from the equation above; that is, since the inductance has increased, the change in capacitance from the varactor has less of an effect on the frequency.

Figure 23. Tuning Sensitivity (in MHz/V) vs. Inductance (nH)

### **FIXED FREQUENCY LO**

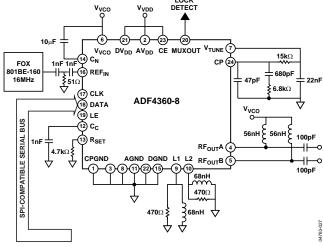

Figure 24 shows the ADF4360-8 used as a fixed frequency LO at 200 MHz. The low-pass filter was designed using ADIsimPLL for a channel spacing of 2 MHz and an open-loop bandwidth of 100 kHz. The maximum PFD frequency of the ADF4360-8 is 8 MHz. Since using a larger PFD frequency allows the use of a smaller N, the in-band phase noise is reduced to as low as possible, –109 dBc/Hz. The typical rms phase noise (100 Hz to 100 kHz) of the LO in this configuration is 0.09°. The reference frequency is from a 16 MHz TCXO from Fox; thus, an R value of 2 is programmed. Taking into account the high PFD frequency and its effect on the band select logic, the band select clock divider is enabled. In this case, a value of 8 is chosen. A very simple shunt inductor and dc-blocking capacitor complete the RF output stage.

Figure 24. Fixed Frequency LO

#### **INTERFACING**

The ADF4360-8 has a simple SPI-compatible serial interface for writing to the device. CLK, DATA, and LE control the data transfer. When LE goes high, the 24 bits that have been clocked into the appropriate register on each rising edge of CLK are transferred to the appropriate latch. See Figure 2 for the timing diagram and Table 5 for the latch truth table.

The maximum allowable serial clock rate is 20 MHz. This means that the maximum update rate possible is 833 kHz, or one update every 1.2  $\mu$ s. This is more than adequate for systems that have typical lock times in hundreds of microseconds.

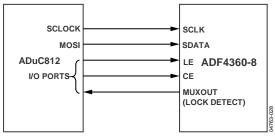

#### **ADuC812** Interface

Figure 25 shows the interface between the ADF4360-8 and the ADuC812 MicroConverter\*. Since the ADuC812 is based on an 8051 core, this interface can be used with any 8051-based microcontrollers. The MicroConverter is set up for SPI master mode with CPHA = 0. To initiate the operation, the I/O port driving LE is brought low. Each latch of the ADF4360-8 needs a 24-bit word, which is accomplished by writing three 8-bit bytes from the MicroConverter to the device. After the third byte has been written, the LE input should be brought high to complete the transfer.

Figure 25. ADuC812 to ADF4360-8 Interface

I/O port lines on the ADuC812 are also used to control power-down (CE input) and detect lock (MUXOUT configured as lock detect and polled by the port input). When operating in the described mode, the maximum SCLOCK rate of the ADuC812 is 4 MHz. This means that the maximum rate at which the output frequency can be changed is 166 kHz.

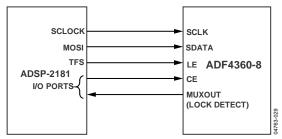

#### ADSP-2181 Interface

Figure 26 shows the interface between the ADF4360-8 and the ADSP-2181 digital signal processor. The ADF4360-8 needs a 24-bit serial word for each latch write. The easiest way to accomplish this using the ADSP-2181 is to use the autobuffered transmit mode of operation with alternate framing. This provides a means for transmitting an entire block of serial data before an interrupt is generated.

Figure 26. ADSP-2181 to ADF4360-8 Interface

Set up the word length for 8 bits and use three memory locations for each 24-bit word. To program each 24-bit latch, store the 8-bit bytes, enable the autobuffered mode, and write to the transmit register of the DSP. This last operation initiates the autobuffer transfer.

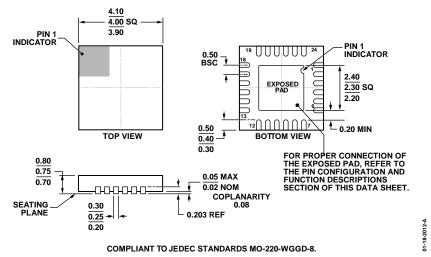

#### PCB DESIGN GUIDELINES FOR CHIP SCALE PACKAGE

The leads on the chip scale package (CP-24) are rectangular. The printed circuit board pad for these should be 0.1 mm longer than the package lead length and 0.05 mm wider than the package lead width. The lead should be centered on the pad to ensure that the solder joint size is maximized.

The bottom of the chip scale package has a central thermal pad. The thermal pad on the printed circuit board should be at least as large as this exposed pad. On the printed circuit board, there should be a clearance of at least 0.25 mm between the thermal pad and the inner edges of the pad pattern to ensure that shorting is avoided.

Thermal vias may be used on the printed circuit board thermal pad to improve thermal performance of the package. If vias are used, they should be incorporated into the thermal pad at 1.2 mm pitch grid. The via diameter should be between 0.3 mm and 0.33 mm, and the via barrel should be plated with 1 ounce of copper to plug the via.

The user should connect the printed circuit thermal pad to AGND. This is internally connected to AGND.

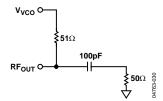

## **OUTPUT MATCHING**

There are a number of ways to match the output of the ADF4360-8 for optimum operation; the most basic is to use a 50  $\Omega$  resistor to  $V_{\rm VCO}$ . A dc bypass capacitor of 100 pF is connected in series, as shown in Figure 27. Because the resistor is not frequency dependent, this provides a good broadband match. The output power in the circuit below typically gives -9 dBm output power into a 50  $\Omega$  load.

Figure 27. Simple ADF4360-8 Output Stage

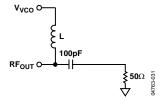

A better solution is to use a shunt inductor (acting as an RF choke) to  $V_{\rm VCO}$ . This gives a better match and, therefore, more output power.

Experiments have shown that the circuit shown in Figure 28 provides an excellent match to 50  $\Omega$  over the operating range of the ADF4360-8. This gives approximately 0 dBm output power across the specific frequency range of the ADF4360-8 using the recommended shunt inductor, followed by a 100 pF dc blocking capacitor.

Figure 28. Optimum ADF4360-8 Output Stage

The recommended value of this inductor changes with the VCO center frequency. A graph of the optimum inductor value vs. frequency is shown in Figure 29.

Figure 29. Optimum ADF4360-8 Shunt Inductor

Both complementary architectures can be examined using the EV-ADF4360-8EB1Z evaluation board. If the user does not need the differential outputs available on the ADF4360-8, the user should either terminate the unused output or combine both outputs using a balun. Alternatively, instead of the LC balun, both outputs may be combined using a 180° rat-race coupler.

# **OUTLINE DIMENSIONS**

Figure 30. 24-Lead Lead Frame Chip Scale Package [LFCSP] 4 mm x 4 mm Body and 0.75 mm Package Height (CP-24-14) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Frequency Range   | Package Description                           | Package Option |

|--------------------|-------------------|-------------------|-----------------------------------------------|----------------|

| ADF4360-8BCPZ      | −40°C to +85°C    | 65 MHz to 400 MHz | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-14       |

| ADF4360-8BCPZRL    | -40°C to +85°C    | 65 MHz to 400 MHz | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-14       |

| ADF4360-8BCPZRL7   | -40°C to +85°C    | 65 MHz to 400 MHz | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-14       |

| EV-ADF4360-8EB1Z   |                   |                   | Evaluation Board                              |                |

<sup>&</sup>lt;sup>1</sup>Z = RoHS Compliant Part.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

EV-ADF4360-8EB1Z ADF4360-8BCPZRL ADF4360-8BCPZRL7 ADF4360-8BCPZ