# OBSOLETE PRODUCT NO RECOMMENDED REPLACEMENT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

# DATASHEET

**EL4393**

Triple 80MHz Video Amplifier w/Disable

FN7165 Rev 0.00 January 1996

The EL4393 is three wideband current-feedback amplifiers optimized for video performance. Each amplifier can drive a load of  $150\Omega$  at video levels. Each amplifier has a disable capability, which is controlled by a TTL/CMOS compatible logic signal. The EL4393 operates on supplies as low as  $\pm 4V$  up to  $\pm 15V$ .

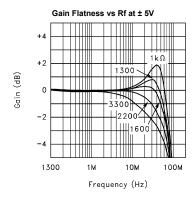

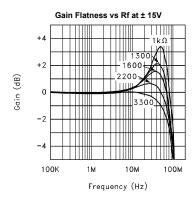

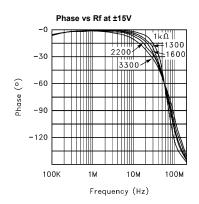

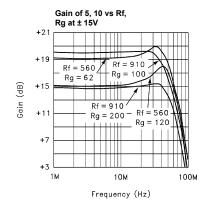

Being a current-feedback design, the bandwidth stays relatively constant at approximately 80MHz over the  $\pm 1$  to  $\pm 10$  gain range. The EL4393 has been optimized for use with  $1300\Omega$  feedback resistors at a gain of 2.

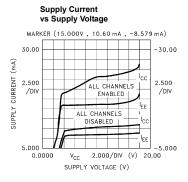

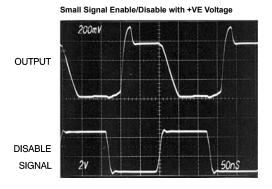

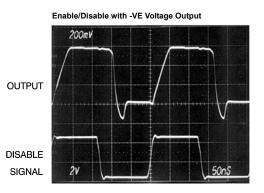

When the outputs are disabled, the supply current consumption drops, by about 4mA per channel that is disabled. This feature can be used to reduce power dissipation.

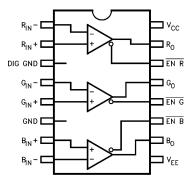

#### **Pinout**

#### EL4393 (16-PIN PDIP, SO) TOP VIEW

#### **Features**

- · 80MHz -3dB bandwidth for gains of 1 to 10

- 900V/µs slew rate

- 10MHz bandwidth flat to 0.1dB

- · Excellent differential gain and phase

- TTL/CMOS compatible

- · Available in SOL-16

#### **Applications**

- · RGB drivers

- · RGB multiplexers

- · RGB gain blocks

- · Video gain blocks

- · Coax cable driver

- · ADC drivers/input multiplexer

#### Ordering Information

| PART<br>NUMBER | TEMP. RANGE    | PACKAGE     | PKG. NO. |

|----------------|----------------|-------------|----------|

| EL4393CN       | -40°C to +85°C | 16-Pin PDIP | MDP0031  |

| EL4393CM       | -40°C to +85°C | 16-Pin SOL  | MDP0027  |

#### **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

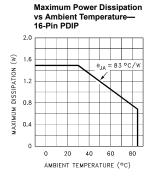

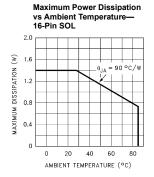

| Voltage between V <sub>S</sub> + and V <sub>S</sub> +33V  | Internal Power Dissipation See Curves            |

|-----------------------------------------------------------|--------------------------------------------------|

| Voltage at V <sub>S</sub> ++18V                           | Operating Ambient Temperature Range40°C to +85°C |

| Voltage at V <sub>S</sub>                                 | Operating Junction Temperature                   |

| Voltage between V <sub>IN</sub> + and V <sub>IN</sub> ±6V | Storage Temperature Range65°C to +150°C          |

| Current into V <sub>IN</sub> + or V <sub>IN</sub>         |                                                  |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

#### Open-Loop DC Electrical Specifications Supplies at $\pm 15$ V, Load = 1k $\Omega$

| PARAMETER             | DESCRIPTION                                          | TEMP  | MIN | TYP   | MAX | UNITS         |

|-----------------------|------------------------------------------------------|-------|-----|-------|-----|---------------|

| V <sub>OS</sub>       | Input Offset Voltage                                 | +25°C |     | 2     | ±15 | mV            |

| TCV <sub>OS</sub>     | Temperature Coefficient of V <sub>OS</sub>           | Full  |     | 50    |     | μV/°C         |

| I <sub>B</sub> +      | I <sub>IN</sub> + Input Bias Current                 | +25°C |     | 0.2   | 5   | μA            |

| I <sub>B</sub> -      | I <sub>IN</sub> - Input Bias Current                 | +25°C |     | 10    | 65  | μA            |

| TCI <sub>B</sub> -    | Temperature Coefficient of I <sub>B</sub> -          | Full  |     | 25    |     | nA/°C         |

| CMRR                  | Common-Mode Rejection Ratio (Note 1)                 | +25°C | 50  | 58    |     | dB            |

| -ICMR                 | I <sub>IN</sub> - Input Common-Mode Current (Note 1) | +25°C |     | 3     | 8   | μ <b>A</b> /V |

| PSRR                  | Power Supply Rejection Ratio (Note 2)                | +25°C | 50  | 58    |     | dB            |

| -IPSR                 | I <sub>IN</sub> - Current Supply Rejection (Note 2)  | +25°C |     | 2     | 5   | μA/V          |

| R <sub>OL</sub>       | Transimpedance                                       | +25°C | 100 | 217   |     | kΩ            |

| R <sub>IN</sub>       | IN+ Input Impedance                                  | +25°C |     | 2     |     | MΩ            |

| V <sub>IN</sub>       | IN+ Input Range                                      | +25°C | ±13 | ±13.5 |     | V             |

| Vo                    | Output Voltage Swing; $R_L = 1k\Omega$               | +25°C | ±12 | ±13   |     | V             |

| I <sub>SC</sub>       | Short-Circuit Current (Note 3)                       | +25°C | 40  | 70    |     | mA            |

| I <sub>O, DIS</sub>   | Output Current when Disabled                         | +25°C |     | 5     | 150 | μA            |

| DIS V <sub>IL</sub>   | Disable Voltage for Logic Low                        | +25°C |     |       | 0.8 | V             |

| DIS V <sub>IH</sub>   | Disable Voltage for Logic High                       | +25°C | 2.2 |       |     | V             |

| DIS I <sub>IL</sub>   | Disable Logic Low Input Current                      | +25°C |     | 3     | 25  | μA            |

| DIS I <sub>IH</sub>   | Disable Logic High Input Current                     | +25°C |     | 0     | 5   | μA            |

| I <sub>CC (en)</sub>  | Positive Supply Current all Channels Enabled         | +25°C | 15  | 20    | ±29 | mA            |

| I <sub>CC (dis)</sub> | Positive Supply Current all Channels Disabled        | +25°C | 6   | 11    | 16  | mA            |

| I <sub>EE (en)</sub>  | Negative Supply Current all Channels Enabled         | +25°C | 13  | 18    | ±28 | mA            |

| I <sub>EE</sub> (dis) | Negative Supply Current all Channels Disabled        | +25°C | 4   | 9     | 14  | mA            |

#### NOTES:

- 1.  $V_{CM} = \pm 10V$  for  $V_S = \pm 15V$ .

- 2.  $V_{OS}$  is measured at  $V_S = \pm 4.5 V$  and  $V_S = \pm 16 V$ , both supplies are changed simultaneously.

- 3. Only one output short-circuited. Pulse test or use heatsink.

# **AC Electrical Specifications** Supplies at $\pm 15V$ , Load = $150\Omega$ and 15pF, except where noted. Rf1 and Rf2 = $1500\Omega$ ; A<sub>V</sub> = 2, $T_A = 25^{\circ}C$ .(Note 1)

| PARAMETER      | DESCRIPTION                                              | MIN | TYP            | MAX | UNITS      |

|----------------|----------------------------------------------------------|-----|----------------|-----|------------|

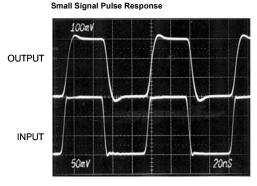

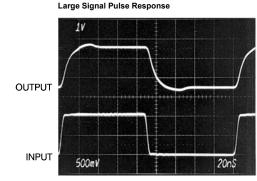

| SR             | Slew Rate (Note 2)                                       |     | 960            |     | V/µs       |

| SR             | Slew Rate w/±5V Supplies (Note 3)                        |     | 470            |     | V/µs       |

| t <sub>S</sub> | Settling Time to 1% 5V <sub>P-P</sub> 5V Step (Note 4)   |     | 32             |     | ns         |

| BW             | Bandwidth, -3dB<br>±5V Supplies, -3dB                    |     | 80<br>60       |     | MHz<br>MHz |

| BW             | Bandwidth, -0.1dB<br>±5V Supplies, -0.1dB                |     | 16<br>21       |     | MHz<br>MHz |

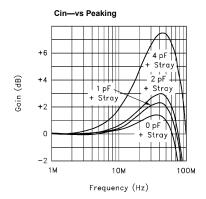

| Peaking        | -3dB BW Tests                                            |     | 0.6            |     | dB         |

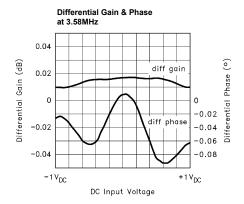

| dG             | Differential Gain at 3.58MHz<br>at ±5V Supplies (Note 5) |     | 0.03<br>0.30   |     | %<br>%     |

| dθ             | Differential Phase at 3.58MHz at ±5V Supplies (Note 5)   |     | 0.088<br>0.096 |     | (°)<br>(°) |

#### NOTES:

- 1. Test fixture was designed to minimize capacitance at the I<sub>N</sub>+ input. A "good" fixture should have less than 2pF of stray capacitance to ground at this very sensitive pin. See application notes for further details.

- 2.  $R_L = 300\Omega$ , -5V to +5V swing, SR measured at 20% to 80%

- 3. -2V to +2V swing, SR measured at 20% to 80%.

- 4.  $R_L = 300\Omega$ .

- 5. DC offset from -0.7V through +0.7V AC amplitude is 286mV<sub>P-P</sub>, equivalent to 40 ire.

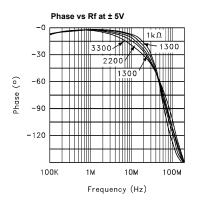

## **Typical Performance Curves**

## Typical Performance Curves (Continued)

## Typical Performance Curves (Continued)

# Typical Application for EL4393, and General Rules for PCB Layout

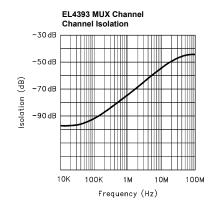

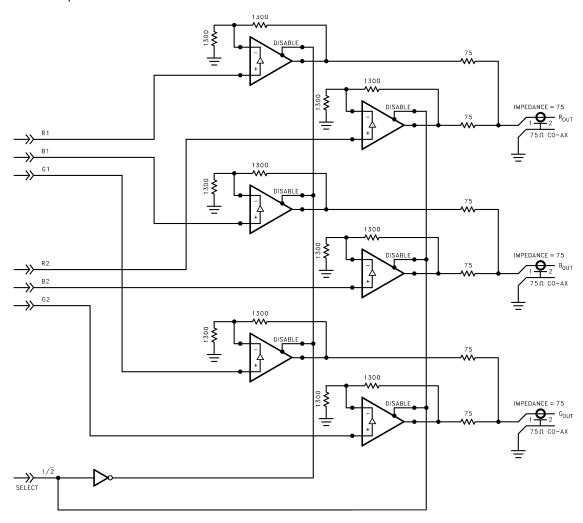

The figure shows two EL4393s configured as a 2:1 RGB multiplexer, and cable driver, driving  $75\Omega$ , back terminated cables. Each channel of the EL4393 is configured to give a gain of two, to make up for the losses of the back terminating resistor.

In this example, the Disable pins of each RGB section are driven by a complementary TTL "select" signal. Larger multiplexers can be assembled, with a 1-of-n TTL decoder selecting each RGB triplet.

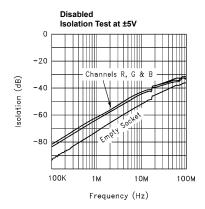

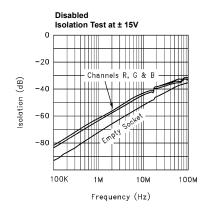

The circuit gives channel isolations of typically better than -50dB at 10MHz, and with a 20dB/decade slope, extending down to better than -90dB at frequencies below 100kHz.

The schematic does not show things like power supply decoupling, or pcb layout, grounding and signal returns, but these will all affect the overall performance of the circuit, and care should be taken with these aspects.

It is recommended that the  $V_{CC}$  and  $V_{EE}$  pins each be decoupled by a  $0.1\mu F$  NPO or X7R dielectric ceramic capacitors to ground within 0.1 inch of the part, and in parallel with the  $0.1\mu F$ , a  $47\mu F$  tantalum capacitor, also to ground. The  $47\mu F$  capacitors should be within 0.25 inch of their power pins. The ground plane should be underneath the package, but cut away from the In- inputs. Care should be taken with the center channel feedback—it must be kept away from any of the In+ or In- pins, if it has to go under the package. Route the G-out line between the pin 3 ground and the pin 4 In- if going under the package is essential. Otherwise, loop the G-out trace around all the other circuitry, to its Rf resistor. The Rf and if used, Rg resistors should be on the input side of the package, to minimize trace length on the In- pins.

The digital input disables are on the output side of the package, so that a good ground plane down the center of the board underneath the package will isolate any fast edges from the sensitive inputs.

TYPICAL APPLICATION CIRCUIT

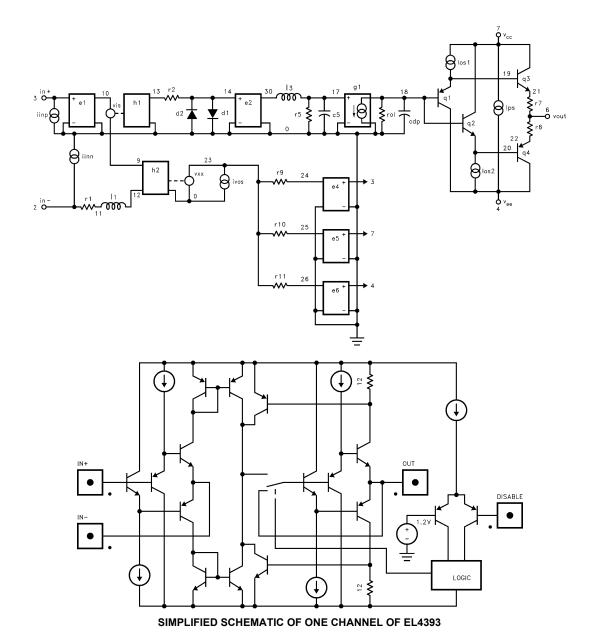

#### EL4393 Macromodel

```

* Revision A, July 1993

* Enhancements include PSRR, CMRR, and Slew Rate Limiting

* Connections:

+input

-Input

+Vsupply

-Vsupply

Putput

* subckt EL4393/EL 3

2

6

4

* Input Stage

e1 10 0 3 0 1.0

vis 10 9 0V

h2 9 12 vxx 1.0

r1 2 11 50

I 1 11 12 29 nH

iinp 3 0 0.2 µA

iinm 2 0 10 \mu A

* Slew Rate Limiting

h1 13 0 vis 600

r2 13 14 1K

d1 14 0 dclamp

d2 0 14 dclamp

* High Frequency Pole

e2 30 0 14 0 0.00166666666

I5 30 17 1.2 μH

c5 17 0 1 pF

r5 17 0 500

* Transimpedance Stage

g1 0 18 17 0 1.0

rol 18 0 250k

cdp 18 0 2.2 pF

* Output Stage

q1 4 18 19 qp

q2 7 18 20 qn

q3 7 19 21 qn

q4 4 20 22 qp

r7 21 6 4

r8 22 6 4

ios1 7 19 2.5 mA

ios2 20 4 2.5 mA

* Error Terms

ivos 0 23 2 mA

vxx 23 0 0V

e4 24 0 3 0 1.0

e5 25 0 7 0 1.0

e6 26 0 4 0 1.0

r9 24 23 1K

```

r10 25 23 1K r11 26 33 1K

\* Models

\*

.model qn npn (is=5e-15 bf=100 tf=0.2nS) .model qp pnp (is=5e-15 bf=100 tf=0.2nS) .model dclamp d (is=1e-30 ibv=0.266 bv=1.5 n=4)

.ends

© Copyright Intersil Americas LLC 2003. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>