## **High Speed Low Power CAN Transceiver**

The NCV7341 CAN transceiver is the interface between a controller area network (CAN) protocol controller and the physical bus and may be used in both 12 V and 24 V systems. The transceiver provides differential transmit capability to the bus and differential receive capability to the CAN controller.

Due to the wide common-mode voltage range of the receiver inputs, the NCV7341 is able to reach outstanding levels of electromagnetic susceptibility (EMS). Similarly, extremely low electromagnetic emission (EME) is achieved by the excellent matching of the output signals.

The NCV7341 is a new addition to the ON Semiconductor CAN high-speed transceiver family and offers the following additional features:

#### **Features**

- Ideal Passive Behavior when Supply Voltage is Removed

- Separate V<sub>IO</sub> Supply for Digital Interface Allowing Communication to CAN Controllers and Microcontrollers with Different Supply Levels

- Fully Compatible with the ISO 11898 Standard

- High Speed (up to 1 Mb)

- Very Low Electromagnetic Emission (EME)

- V<sub>SPLIT</sub> Voltage Source for Stabilizing the Recessive Bus Level if Split Termination is Used (Further Improvement of EME)

- Differential Receiver with High Common-Mode Range for Electromagnetic Immunity (EMI)

- Up to 110 Nodes can be Connected in Function of the Bus Topology

- Transmit Data (TxD) Dominant Time-out Function

- Bus Error Detection with Version NCV7341D20

- Bus Pins Protected Against Transients in Automotive Environments

- Bus Pins and Pin V<sub>SPLIT</sub> Short–Circuit Proof to Battery and Ground

- Thermally Protected

- NCV Prefix for Automotive and Other Applications Requiring Site and Change Controls

- These are Pb-Free Devices\*

#### **Typical Applications**

- Automotive

- Industrial Networks

#### ON Semiconductor®

http://onsemi.com

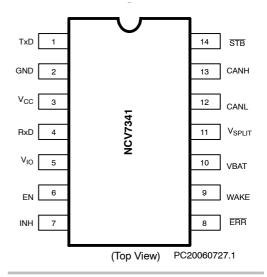

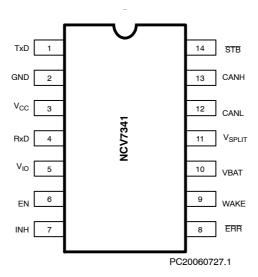

#### **PIN ASSIGNMENT**

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 17 of this data sheet.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

**Table 1. TECHNICAL CHARACTERISTICS**

| Symbol                       | Parameter                                            | Condition                                                                  | Max      | Max                   | Unit |

|------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|----------|-----------------------|------|

| V <sub>CC</sub>              | Supply Voltage for the Core Circuitry                |                                                                            | 4.75     | 5.25                  | V    |

| V <sub>IO</sub>              | Supply Voltage for the Digital Interface             |                                                                            | 2.8      | 5.25                  | V    |

| V <sub>EN</sub>              | DC Voltage at Pin EN                                 |                                                                            | -0.3     | V <sub>IO</sub> + 0.3 | V    |

| V <sub>STB</sub>             | DC Voltage at Pin STB                                |                                                                            | -0.3     | V <sub>IO</sub> + 0.3 | V    |

| $V_{TxD}$                    | DC Voltage at Pin TxD                                |                                                                            | -0.3     | V <sub>IO</sub> + 0.3 | V    |

| V <sub>RxD</sub>             | DC Voltage at Pin RxD                                |                                                                            | -0.3     | V <sub>IO</sub> + 0.3 | V    |

| V <sub>ERR</sub>             | DC Voltage at Pin ERR                                |                                                                            | -0.3     | V <sub>IO</sub> + 0.3 | V    |

| V <sub>CANH</sub>            | DC Voltage at Pin CANH                               | 0 < V <sub>CC</sub> < 5.25 V; No Time Limit                                | -58      | +58                   | V    |

| V <sub>CANL</sub>            | DC Voltage at Pin CANL                               | 0 < V <sub>CC</sub> < 5.25 V; No Time Limit                                | -58      | +58                   | V    |

| V <sub>SPLIT</sub>           | DC Voltage at Pin V <sub>SPLIT</sub>                 | 0 < V <sub>CC</sub> < 5.25 V; No time Limit                                | -58      | +58                   | V    |

| V <sub>O(dif)(bus_dom)</sub> | Differential Bus Output Voltage in Dominant<br>State | $42.5 \Omega$ < $R_{LT}$ < $60 \Omega$                                     | 1.5      | 3                     | V    |

| CM <sub>range</sub>          | Input Common-Mode Range for Comparator               | Guaranteed Differential Receiver<br>Threshold and Leakage Current          | -35      | +35                   | V    |

| C <sub>load</sub>            | Load Capacitance on IC Outputs                       |                                                                            |          | 15                    | pF   |

| t <sub>pd(rec-dom)</sub>     | Propagation Delay TxD to RxD                         | See Figure 6                                                               | 90       | 230                   | ns   |

| t <sub>pd(dom-rec)</sub>     | Propagation Delay TxD to RxD                         | See Figure 6                                                               | 90       | 245                   | ns   |

| T <sub>J</sub>               | Junction Temperature                                 |                                                                            | -40      | 150                   | °C   |

| ESD <sub>HBM</sub>           | ESD Level, Human Body Model                          | Pins CANH, CANL, V <sub>SPLIT</sub> ,<br>WAKE, V <sub>BAT</sub> other Pins | -4<br>-3 | 4<br>3                | kV   |

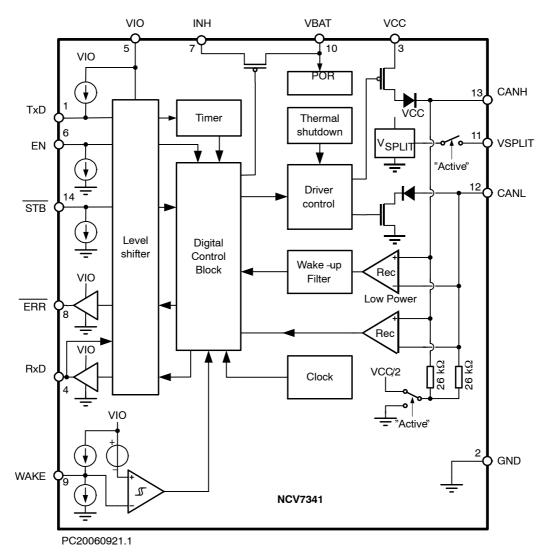

## **BLOCK DIAGRAM**

Figure 1. Block Diagram

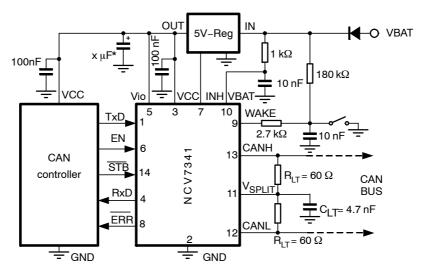

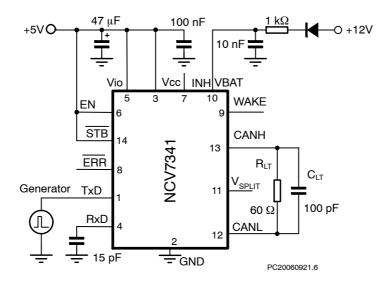

#### TYPICAL APPLICATION SCHEMATICS

Note (\*): Value depending on regulator

PC20060921.4

Figure 2. Application Diagram with a 5V CAN Controller

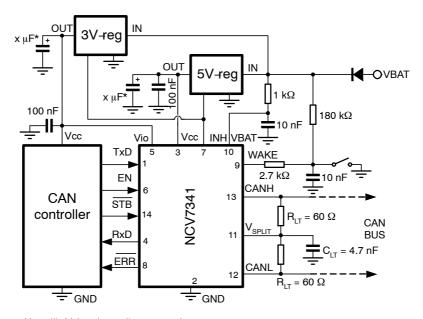

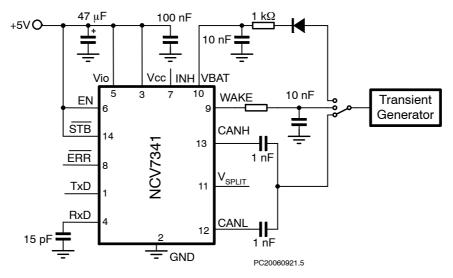

Note (\*): Value depending on regulator

PC20060921.4

Figure 3. Application Diagram with a 3V CAN Controller

## **PIN DESCRIPTION**

Figure 4. NCV7340 Pin Assignment

## **Table 2. PIN DESCRIPTION**

| Pin | Name               | Description                                                                    |

|-----|--------------------|--------------------------------------------------------------------------------|

| 1   | TxD                | Transmit data input; low level = dominant on the bus; internal pull-up current |

| 2   | GND                | Ground                                                                         |

| 3   | V <sub>CC</sub>    | Supply voltage for the core circuitry and the transceiver                      |

| 4   | RxD                | Receive data output; dominant bus => low output                                |

| 5   | V <sub>IO</sub>    | Supply voltage for the CAN controller interface                                |

| 6   | EN                 | Enable input; internal pull-down current                                       |

| 7   | INH                | High voltage output for controlling external voltage regulators                |

| 8   | ERR                | Digital output indicating errors and power-up; active low                      |

| 9   | WAKE               | Local wake-up input                                                            |

| 10  | $V_{BAT}$          | Battery supply connection                                                      |

| 11  | V <sub>SPLIT</sub> | Common-mode stabilization output                                               |

| 12  | CANL               | Low-level CAN bus line (low in dominant)                                       |

| 13  | CANH               | High-level CAN bus line (high in dominant)                                     |

| 14  | STB                | Stand-by mode control input; internal pull-down current                        |

#### **FUNCTIONAL DESCRIPTION**

## **OPERATING MODES**

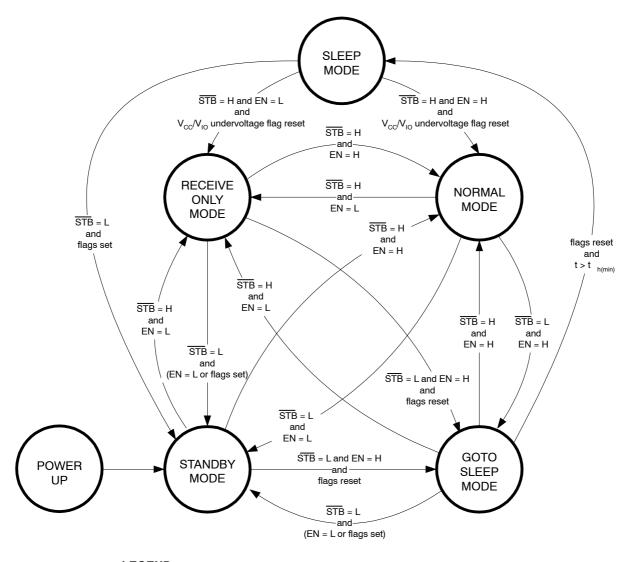

Operation modes of NCV7341 are shown in Figures 5 and in Table 3.

**LEGEND** PC20060921.2

"Flags set": wake-up or power-up not (wake-up or power-up)

Figure 5. Operation Modes

**Table 3. OPERATION MODES**

|         | Conditions |                                                          |                              |                            | Transceiver Behav           | rior     |

|---------|------------|----------------------------------------------------------|------------------------------|----------------------------|-----------------------------|----------|

| Pin STB | Pin EN     | V <sub>CC</sub> /V <sub>IO</sub><br>Undervoltage<br>Flag | VBAT<br>Undervoltage<br>Flag | Power-up or<br>Wakeup Flag | Operating Mode              | Pin INH  |

| Х       | Х          | Set                                                      | X                            | X                          | Sleep                       | Floating |

|         |            | Reset                                                    | Set                          | Set                        | Standby                     | High     |

|         |            |                                                          |                              | Reset                      | If in sleep, then no change | Floating |

|         |            |                                                          |                              |                            | otherwise stand-by          | High     |

| Low     | Low        | Reset                                                    | Reset                        | Set                        | Stand-by                    | High     |

|         |            |                                                          |                              | Reset                      | If in sleep, then no change | Floating |

|         |            |                                                          |                              |                            | otherwise stand-by          | High     |

| Low     | High       | Reset                                                    | Reset                        | Set                        | Stand-by                    | High     |

|         |            |                                                          |                              | Reset                      | If in sleep, then no change | Floating |

|         |            |                                                          |                              |                            | otherwise go-to-sleep       | High     |

| High    | Low        | Reset                                                    | Reset                        | X                          | Receive-only                | High     |

| High    | High       | Reset                                                    | Reset                        | Х                          | Normal                      | High     |

#### **Normal Mode**

In Normal mode, the transceiver is able to communicate via the bus lines. The CAN controller can transmit data to the bus via TxD pin and receive data from the bus via Pin RxD. The bus lines (CANH and CANL) are internally biased to  $V_{\rm CC}/2$  via the common–mode input resistance. Pin  $V_{\rm SPLIT}$  is also providing voltage  $V_{\rm CC}/2$  which can be further used to externally stabilize the common mode voltage of the bus – see Figure 2 and Figure 3. Pin INH is active (pulled high) so that the external regulators controlled by INH Pin are switched on.

#### Receive-Only Mode

In Receive–only mode, the CAN transmitter is disabled. The CAN controller can still receive data from the bus via RxD Pin as the receiver part remains active. Equally to normal mode, the bus lines (CANH and CANL) are internally biased to  $V_{\rm CC}/2$  and Pin  $V_{\rm SPLIT}$  is providing voltage  $V_{\rm CC}/2$ . Pin INH is also active (pulled high).

#### Standby Mode

Standby mode is a low–power mode. Both the transmitter and the receiver are disabled and a very low–power differential receiver monitors the CAN bus activity. Bus lines are biased internally to ground via the common mode input resistance and Pin  $V_{SPLIT}$  is high–impedant (floating). A wake–up event can be detected either on the CAN bus or on the WAKE Pin. A valid wake–up is signaled on pins  $\overline{ERR}$  and RxD. Pin INH remains active (pulled high) so that the external regulators controlled by INH Pin are switched on.

#### Go-To-Sleep Mode

Go-To-Sleep mode is an intermediate state used to put the transceiver into sleep mode in a controlled way. Go-To-Sleep mode is entered when the CAN controller

puts pin EN to High and  $\overline{STB}$  Pin to Low. If the logical state of Pins EN and  $\overline{STB}$  is kept unchanged for minimum period of  $t_{h(min)}$  and neither a wake-up nor a power-up event occur during this time, the transceiver enters sleep mode. While in go-to-sleep mode, the transceiver behaves identically to stand-by mode.

#### Sleep Mode

Sleep mode is a low-power mode in which the consumption is further reduced compared to stand-by mode. Sleep mode can be entered via go-to-sleep mode or in case an undervoltage on either  $V_{CC}$  or  $V_{IO}$  occurs for longer than the under-voltage detection time. The transceiver behaves identically to standby mode, but the INH Pin is deactivated (left floating) and the external regulators controlled by INH Pin are switched off. In this way, the  $V_{BAT}$  consumption is reduced to a minimum. The device will leave sleep mode either by a wake-up event (in case of a CAN bus wake-up or via Pin WAKE) or by putting Pin  $\overline{STB}$  high (as long as an under-voltage on  $V_{CC}$  or  $V_{IO}$  is not detected).

#### Internal Flags

The transceiver keeps several internal flags reflecting conditions and events encountered during its operation. Some flags influence the operation mode of the transceiver (see Figure 5 and Table 3). Beside the undervoltage and the TxD dominant timeout flags, all others can be read by the CAN controller on Pin  $\overline{ERR}$ . Pin  $\overline{ERR}$  signals internal flags depending on the operation mode of the transceiver. An overview of the flags and their visibility on Pin  $\overline{ERR}$  is given in Table 4. Because the  $\overline{ERR}$  Pin uses negative logic, it will be pulled low if the signaled flag is set and will be pulled high if the signaled flag is reset.

**Table 4. INTERNAL FLAGS AND THEIR VISIBILITY**

| Internal Flag                                 | Set Condition                                                                                                                                                   | Reset Condition                                                                                              | Visibility on Pin ERR                                                                          |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> /V <sub>IO</sub> Undervoltage | $\begin{aligned} &V_{CC} < V_{CC(SLEEP)} \text{ longer than } t_{UV(VCC)} \\ &\text{or } V_{IO} < V_{IO(SLEEP)} \text{ longer than } t_{UV(VIO)} \end{aligned}$ | At wake-up or power-up                                                                                       | No                                                                                             |

| V <sub>BAT</sub> Undervoltage                 | V <sub>BAT</sub> < V <sub>BAT(STB)</sub>                                                                                                                        | When V <sub>BAT</sub> recovers                                                                               | No                                                                                             |

| Powerup                                       | V <sub>BAT</sub> rises above VBAT <sub>(PWUP)</sub><br>(V <sub>BAT</sub> connection to the transceiver)                                                         | When normal mode is entered                                                                                  | In receive-only mode. Not going from normal mode                                               |

| Wake-up                                       | When remote or local wake-up is detected                                                                                                                        | At power-up or when normal mode is entered or when V <sub>CC</sub> /V <sub>IO</sub> undervoltage flag is set | Both on ERR and RxD (both pulled to low). In go-to-sleep, standby and sleep mode.              |

| Local Wake-up                                 | When local wake-up is detected (i.e.via pin WAKE)                                                                                                               | At power-up or when leaving normal mode                                                                      | In normal mode before 4 consecutive dominant symbols are sent. Then ERR pin becomes High again |

| Failure                                       | Pin TxD clamped low or overtemperature                                                                                                                          | When entering normal mode<br>or when RxD is Low while<br>TxD is high (provided all<br>failures disappeared)  | Overtemperature condition observable in receive-only mode entered from normal mode             |

| Bus Failure<br>(NCV7341D20)                   | One of the bus lines shorted to ground or supply during four consecutive transmitted dominants                                                                  | No bus line short (to ground<br>or supply) detected during<br>four consecutive dominant bit<br>transmissions | In normal mode                                                                                 |

#### V<sub>CC</sub>/V<sub>IO</sub> Undervoltage Flag

The  $V_{CC}/V_{IO}$  undervoltage flag is set if  $V_{CC}$  supply drops below  $V_{CC(sleep)}$  level for longer than  $t_{UV(VCC)}$  or  $V_{IO}$  supply drops below  $V_{IO(sleep)}$  level for longer than  $t_{UV(VIO)}$ . If the flag is set, the transceiver enters sleep mode. After a waiting time identical to the undervoltage detection times  $t_{UV(VCC)}$  and  $t_{UV(VIO)}$ , respectively, the flag can be reset either by a valid wake-up request or when the powerup flag is set. During this waiting time, the wakeup detection is blocked.

#### VBAT Under-voltage Flag

The flag is set when  $V_{BAT}$  supply drops below  $V_{BAT(STB)}$  level. The transceiver will enter the standby mode. The flag is reset when  $V_{BAT}$  supply recovers. The transceiver then enters the mode defined by inputs  $\overline{STB}$  and EN.

#### Power-up Flag

This flag is set when  $V_{BAT}$  supply recovers after being below  $V_{BAT(PWUP)}$  level, which corresponds to a connection of the transceiver to the battery. The  $V_{CC}/V_{IO}$  undervoltage flag is cleared so that the transceiver cannot enter the Go-to-sleep Mode, ensuring that INH Pin is high and the external voltage regulators are activated at the battery connection. In Receive-only mode, the powerup flag can be observed on the  $\overline{ERR}$  Pin. The flag is reset when Normal mode is entered.

#### Wake-up Flag

This flag is set when the transceiver detects a valid wake-up request via the bus or via the WAKE Pin. Setting the wake-up flag is blocked during the waiting time of the  $V_{CC}/V_{IO}$  undervoltage flag. The wake-up flag is immediately propagated to Pins  $\overline{ERR}$  and RxD – provided that supplies  $V_{CC}$  and  $V_{IO}$  are available. The wake-up flag

is reset at power-up or when  $V_{\rm CC}/V_{\rm IO}$  undervoltage occurs or when Normal mode is entered.

#### Local wake-up Flag

This flag is set when a valid wake-up request through WAKE Pin occurs. It can be observed on the  $\overline{ERR}$  Pin in normal mode. It can only be set when the powerup flag is reset. The local wake-up flag is reset at powerup or at leaving Normal mode.

#### Failure Flag

The failure flag is set in one of the following situations:

- TxD Pin is Low (i.e. dominant is requested by the CAN controller) for longer than t<sub>dom(TxD)</sub> Under this condition, the transmitter is disabled so that a bus lockup is avoided in case of an application failure which would drive permanent dominant on the bus. The transmitter remains disabled until the failure flag is

- Overtemperature If the junction temperature reaches T<sub>J(SD)</sub>, the transmitter is disabled in order to protect it from overheating and the failure flag is set. The transmitter remains disabled until the failure flag is reset.

The failure flag is reset when Normal mode is entered or when TxD pin is High while RxD pin is Low. In case of overtemperature, the failure flag is observable on pin  $\overline{ERR}$ .

#### **Bus Failure Flag (NCV7341D20)**

The transmitter of the NCV7341D20 device version allows bus failure detection. During dominant bit transmission, a short of the CANH or CANL line to ground or supply ( $V_{CC}$ , VBAT or other) is internally detected. If the short circuit condition lasts for four consecutive dominant

transmissions, an internal bus failure flag is set and made immediately visible through a Low level on the  $\overline{ERR}$  pin. The transmission and reception circuitry continues to function.

When four consecutive dominant transmissions succeed without a bus line short being detected, the internal bus failure flag is reset and  $\overline{ERR}$  pin is released to High level.

#### **Split Circuit**

The  $V_{SPLIT}$  Pin is operational only in normal and receive–only modes. It is floating in standby and sleep modes. The  $V_{SPLIT}$  can be connected as shown in Figure 2 and Figure 3 and its purpose is to provide a stabilized DC voltage of  $V_{CC}/2$  to the bus avoiding possible steps in the common–mode signal, therefore reducing EME. These unwanted steps could be caused by an unpowered node on the network with excessive leakage current from the bus that shifts the recessive voltage from its nominal  $V_{CC}/2$  level.

#### Wake-up

The transceiver can detect wake-up events in stand-by, go-to-sleep and sleep modes. Two types of wake-up events are handled – remote wake-up via the CAN bus or a local wake-up via the WAKE pin. A valid remote wake-up is recognized after two dominant states of the CAN bus of at least  $t_{\text{dom}}$ , each of them followed by a recessive state of at least  $t_{\text{rec}}$ .

A local wake-up is detected after a change of state (High to Low, or Low to High) on WAKE Pin which is stable for at least t<sub>WAKE</sub>. To increase the EMS level of the WAKE Pin, an internal current source is connected to it. If the state of the WAKE Pin is stable at least for t<sub>WAKE</sub>, the direction of the current source follows (pulldown current for Low state, pullup current for High state). It is recommended to connect Pin WAKE either to GND or VBAT if it's not used in the application.

#### **Fail Safe Features**

Fail safe behavior is ensured by the detection functions associated with the internal flags.

Furthermore, a current-limiting circuit protects the transmitter output stage from damage caused by accidental short circuit to either positive or negative supply voltage, although power dissipation increases during this fault condition.

The Pins CANH and CANL are protected from automotive electrical transients (according to ISO 7637; see Figure 9). Pins TxD is pulled high and Pins  $\overline{\text{STB}}$  and EN are pulled low internally should the input become disconnected. Pins TxD,  $\overline{\text{STB}}$ , EN and RxD will be floating, preventing reverse supply should the  $V_{IO}$  supply be removed.

#### **ELECTRICAL CHARACTERISTICS**

#### **Definitions**

All voltages are referenced to GND (Pin 2). Positive currents flow into the IC. Sinking current means the current is flowing into the pin; sourcing current means the current is flowing out of the pin.

#### **Absolute Maximum Ratings**

Stresses above those listed in the following table may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

**Table 5. ABSOLUTE MAXIMUM RATINGS**

| Symbol                                              | Parameter                                                                                                                        | Conditions                                     | Min.       | Max.                  | Unit    |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------|-----------------------|---------|

| V <sub>BAT</sub>                                    | Supply voltage                                                                                                                   |                                                | -0.3       | 58                    | V       |

| V <sub>CC</sub>                                     | Supply voltage                                                                                                                   |                                                | -0.3       | +7                    | V       |

| V <sub>IO</sub>                                     | Supply voltage                                                                                                                   |                                                | -0.3       | +7                    | V       |

| V <sub>CANH</sub>                                   | DC voltage at pin CANH                                                                                                           | 0 < V <sub>CC</sub> < 5.25 V;<br>no time limit | -58        | +58                   | V       |

| V <sub>CANL</sub>                                   | DC voltage at pin CANL                                                                                                           | 0 < V <sub>CC</sub> < 5.25 V;<br>no time limit | -58        | +58                   | V       |

| V <sub>CANL</sub> -V <sub>CANH</sub>                | DC voltage between bus pins CANH and CANL                                                                                        | 0 < V <sub>CC</sub> < 5.25 V;<br>no time limit | -58        | +58                   | V       |

| V <sub>SPLIT</sub>                                  | DC voltage at pin VSPLIT                                                                                                         | 0 < V <sub>CC</sub> < 5.25 V;<br>no time limit | -58        | +58                   | V       |

| V <sub>INH</sub>                                    | DC voltage at pin INH                                                                                                            |                                                | -0.3       | VBAT+0.3              | V       |

| $V_{WAKE}$                                          | DC voltage at pin WAKE                                                                                                           |                                                | -0.3       | 58                    | V       |

| $V_{TxD}$                                           | DC voltage at pin TxD                                                                                                            |                                                | -0.3       | 7                     | V       |

| V <sub>RxD</sub>                                    | DC voltage at pin RxD                                                                                                            |                                                | -0.3       | V <sub>IO</sub> + 0.3 | V       |

| V <sub>STB</sub>                                    | DC voltage at pin STB                                                                                                            |                                                | -0.3       | 7                     | V       |

| V <sub>EN</sub>                                     | DC voltage at pin EN                                                                                                             |                                                | -0.3       | 7                     | V       |

| V <sub>ERR</sub>                                    | DC voltage at pin ERR                                                                                                            |                                                | -0.3       | V <sub>IO</sub> + 0.3 | V       |

| V <sub>tran(CANH)</sub>                             | Transient voltage at pin CANH                                                                                                    | (Note 1)                                       | -300       | +300                  | V       |

| V <sub>tran(CANL)</sub>                             | Transient voltage at pin CANL                                                                                                    | (Note 1)                                       | -300       | +300                  | V       |

| V <sub>tran(VSPLIT)</sub>                           | Transient voltage at pin VSPLIT                                                                                                  | (Note 1)                                       | -300       | +300                  | V       |

| V <sub>esd</sub> (CANL/CANH/<br>VSPLIT, VBAT, WAKE) | Electrostatic discharge voltage at pins intended to be wired outside of the module (CANH, CANL, V <sub>SPLIT</sub> , VBAT, WAKE) | (Note 2)<br>(Note 4)                           | -4<br>-500 | 4<br>500              | kV<br>V |

| V <sub>esd</sub>                                    | Electrostatic discharge voltage at all other pins                                                                                | (Note 2)<br>(Note 4)                           | -3<br>-500 | 3<br>500              | kV<br>V |

| Latch-up                                            | Static latch-up at all pins                                                                                                      | (Note 3)                                       |            | 120                   | mA      |

| T <sub>stg</sub>                                    | Storage temperature                                                                                                              |                                                | -50        | +150                  | °C      |

| T <sub>amb</sub>                                    | Ambient temperature                                                                                                              |                                                | -50        | +125                  | °C      |

| T <sub>junc</sub>                                   | Maximum junction temperature                                                                                                     |                                                | -50        | +180                  | °C      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. Applied transient waveforms in accordance with ISO 7637 part 3, test pulses 1, 2, 3a, and 3b (see Figure 9).

- 2. Standardized human body model electrostatic discharge (ESD) pulses in accordance to MIL883 method 3015.7.

- 3. Static latch-up immunity: Static latch-up protection level when tested according to EIA/JESD78.

- 4. Standardized charged device model ESD pulses when tested according to EOS/ESD DS5.3-1993.

#### **Operating Conditions**

Operating conditions define the limits for functional operation, parametric characteristics and reliability specification of the device. Functionality of the device is not guaranteed outside the operating conditions.

**Table 6. OPERATING RANGES**

| Symbol                               | Parameter                                             | Conditions                                       | Min  | Max                    | Unit |

|--------------------------------------|-------------------------------------------------------|--------------------------------------------------|------|------------------------|------|

| V <sub>BAT</sub>                     | Supply Voltage                                        |                                                  | 5.0  | 50                     | V    |

| V <sub>BAT_SLEEP</sub>               | Supply Voltage in the Sleep Mode                      | (Note 1)                                         | 6.0  | 50                     | V    |

| V <sub>CC</sub>                      | Supply Voltage                                        |                                                  | 4.75 | 5.25                   | V    |

| V <sub>IO</sub>                      | Supply Voltage                                        |                                                  | 2.8  | 5.25                   | V    |

| V <sub>CANH</sub>                    | DC Voltage at Pin CANH                                | Receiver Function Guaranteed                     | -35  | +35                    | V    |

| V <sub>CANL</sub>                    | DC Voltage at Pin CANL                                | Receiver Function Guaranteed                     | -35  | +35                    | V    |

| V <sub>CANL</sub> -V <sub>CANH</sub> | DC Voltage Between Bus Pins CANH and CANL             | Receiver Function Guaranteed                     | -35  | +35                    | V    |

| V <sub>SPLIT</sub>                   | DC Voltage at Pin V <sub>SPLIT</sub>                  | Leakage and Current Limitation are<br>Guaranteed | -35  | +35                    | V    |

| V <sub>INH</sub>                     | DC Voltage at Pin INH                                 |                                                  | -0.3 | V <sub>BAT</sub> + 0.3 | V    |

| V <sub>WAKE</sub>                    | DC Voltage at Pin WAKE                                |                                                  | -0.3 | V <sub>BAT</sub> + 0.3 | V    |

| $V_{TxD}$                            | DC Voltage at Pin TxD                                 |                                                  | -0.3 | V <sub>IO</sub> + 0.3  | V    |

| V <sub>RxD</sub>                     | DC Voltage at Pin RxD                                 |                                                  | -0.3 | V <sub>IO</sub> + 0.3  | V    |

| V <sub>STB</sub>                     | DC Voltage at Pin STB                                 |                                                  | -0.3 | V <sub>IO</sub> + 0.3  | V    |

| V <sub>EN</sub>                      | DC Voltage at Pin EN                                  |                                                  | -0.3 | V <sub>IO</sub> + 0.3  | V    |

| VERR                                 | DC Voltage at Pin ERR                                 |                                                  | -0.3 | V <sub>IO</sub> + 0.3  | V    |

| C <sub>LOAD</sub>                    | Capacitive Load on Digital Outputs (Pins RxD and ERR) |                                                  |      | 15                     | pF   |

| T <sub>A</sub>                       | Ambient Temperature                                   |                                                  | -40  | +125                   | °C   |

| T <sub>J</sub>                       | Maximum Junction Temperature                          |                                                  | -40  | +150                   | °C   |

In the sleep mode, all relevant parameters are guaranteed only for V<sub>BAT</sub> > 6 V. For V<sub>BAT</sub> between 5 V and 6 V, no power-on-reset will occur and the functionality is also guaranteed, but some parameters might get slightly out of the specification – e.g. the wakeup detection thresholds.

#### **Table 7. THERMAL CHARACTERISTICS**

| Symbol Parameter      |                                                                | Conditions | Value | Unit |

|-----------------------|----------------------------------------------------------------|------------|-------|------|

| R <sub>th(vj-a)</sub> | Thermal Resistance from Junction-to-Ambient in SOIC-14 Package | 1S0P PCB   | 128   | K/W  |

| R <sub>th(vj-a)</sub> | Thermal Resistance from Junction-to-Ambient in SOIC-14 Package | 2S2P PCB   | 70    | K/W  |

## Characteristics

The characteristics of the device are valid for operating conditions defined in Table 7 and the bus lines are considered to be loaded with  $R_{LT}$  = 60  $\Omega$ , unless specified otherwise.

**Table 8. DC CHARACTERISTICS**

| Symbol                        | Parameter                                                                                                    | Conditions                                                                                                                               | Min                 | Тур | Max                   | Unit |

|-------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----------------------|------|

| SUPPLY (PIN VBA               | AT)                                                                                                          |                                                                                                                                          | -                   | -   | -                     | -    |

| VBAT <sub>(STB)</sub>         | Level for Setting V <sub>BAT</sub><br>Undervoltage Flag                                                      | V <sub>CC</sub> = 5 V                                                                                                                    | 2.75                | 3.3 | 4.5                   | V    |

| VBAT <sub>(PWUP)</sub>        | Level for Setting Powerup<br>Flag                                                                            | V <sub>CC</sub> = 0 V                                                                                                                    | 2.75                | 3.3 | 4.5                   | V    |

| I <sub>VBAT</sub>             | V <sub>BAT</sub> Current Consumption in<br>Normal and Receive-Only<br>Modes                                  | INH and WAKE Not Loaded                                                                                                                  | 1.0                 | 10  | 40                    | μА   |

|                               | V <sub>BAT</sub> Current Consumption in<br>Standby and Go-to-Sleep<br>Modes. The total supply                | $V_{VCC} > 4.75 \text{ V}, V_{VIO} > 2.8 \text{ V}$<br>$V_{INH} = V_{WAKE} = V_{VBAT} = 12 \text{ V}$<br>$T_{amb} < 100^{\circ}\text{C}$ |                     |     | 18                    | μΑ   |

|                               | current is drawn partially from $V_{BAT}$ and partially from $V_{CC}$ .                                      | V <sub>VCC</sub> > 4.75 V, V <sub>VIO</sub> > 2.8 V<br>V <sub>INH</sub> = V <sub>WAKE</sub> = V <sub>VBAT</sub> = 12 V                   | 8.0                 | 12  | 22.5                  | μΑ   |

|                               | V <sub>BAT</sub> Current Consumption in<br>Sleep Mode. The supply<br>current is drawn from V <sub>BAT</sub>  | $V_{VCC} = V_{INH} = V_{VIO} = 0 V$<br>$V_{WAKE} = V_{VBAT} = 12 V$<br>$T_{amb} < 100^{\circ}C$                                          |                     |     | 35                    | μΑ   |

|                               | only·                                                                                                        | V <sub>VCC</sub> = V <sub>INH</sub> = V <sub>VIO</sub> = 0 V<br>V <sub>WAKE</sub> = V <sub>VBAT</sub> = 12 V                             | 10                  | 20  | 50                    | μΑ   |

| SUPPLY (PIN V <sub>CC</sub>   | )                                                                                                            |                                                                                                                                          |                     |     |                       |      |

| V <sub>CC(SLEEP)</sub>        | V <sub>CC</sub> Level for Setting V <sub>CC</sub> /V <sub>IO</sub><br>Undervoltage Flag                      | V <sub>BAT</sub> = 12 V                                                                                                                  | 2.75                | 3.3 | 4.5                   | V    |

| I <sub>VCC</sub>              | V <sub>CC</sub> Current Consumption in<br>Normal or Receive-Only<br>Mode                                     | Normal Mode:<br>V <sub>TxD</sub> = 0 V, i.e. Dominant                                                                                    | 25                  | 55  | 80                    | mA   |

|                               |                                                                                                              | Normal Mode: V <sub>TxD</sub> = V <sub>IO</sub> , i.e.<br>Recessive (or Receive–Only<br>Mode)                                            | 2.0                 | 6.0 | 10                    | mA   |

|                               | V <sub>CC</sub> Current Consumption in Standby and Go-to-Sleep                                               | T <sub>amb</sub> < 100°C                                                                                                                 |                     |     | 17.5                  | μΑ   |

|                               | Mode. The total supply current is drawn partially from V <sub>BAT</sub> and partially from V <sub>CC</sub> . |                                                                                                                                          | 6.5                 | 12  | 19.5                  | μΑ   |

|                               | V <sub>CC</sub> Current Consumption in                                                                       | T <sub>amb</sub> < 100°C                                                                                                                 |                     |     | 1.0                   | μΑ   |

|                               | Sleep Mode                                                                                                   |                                                                                                                                          | 0.2                 | 0.5 | 2.0                   | μА   |

| SUPPLY (PIN V <sub>IO</sub> ) |                                                                                                              |                                                                                                                                          | •                   | •   |                       |      |

| V <sub>IO(SLEEP)</sub>        | V <sub>IO</sub> Level for Setting V <sub>CC</sub> /V <sub>IO</sub><br>Undervoltage Flag                      |                                                                                                                                          | 0.9                 | 1.6 | 2.0                   | V    |

| I <sub>VIO</sub>              | V <sub>IO</sub> Current Consumption in<br>Normal or Receive-Only                                             | Normal Mode:<br>V <sub>TxD</sub> = 0V, i.e. Dominant                                                                                     | 100                 | 350 | 1000                  | μΑ   |

|                               | Mode                                                                                                         | Normal Mode: V <sub>TxD</sub> = V <sub>IO</sub> , i.e.<br>Recessive (or Receive–Only<br>mode)                                            | 0                   | 0.2 | 1.0                   | μΑ   |

|                               | V <sub>IO</sub> Current Consumption in                                                                       | T <sub>amb</sub> < 100°C                                                                                                                 |                     |     | 1.0                   | μΑ   |

|                               | Standby or Sleep Mode                                                                                        |                                                                                                                                          | 0                   | 0   | 5.0                   | μΑ   |

| TRANSMITTER DA                | ATA INPUT (PIN TxD)                                                                                          |                                                                                                                                          |                     |     |                       |      |

| V <sub>IH</sub>               | High-Level Input Voltage                                                                                     | Output Recessive                                                                                                                         | 0.7V <sub>VIO</sub> | _   | V <sub>IO</sub> + 0.3 | V    |

| V <sub>IL</sub>               | Low-Level Input Voltage                                                                                      | Output Dominant                                                                                                                          | -0.3                | -   | 0.3V <sub>VIO</sub>   | ٧    |

| I <sub>IH</sub>               | High-Level Input Current                                                                                     | $V_{TxD} = V_{VIO}$                                                                                                                      | -5.0                | 0   | +5.0                  | μΑ   |

|                               |                                                                                                              |                                                                                                                                          |                     |     |                       | _    |

#### Table 8. DC CHARACTERISTICS

| Symbol                        | Parameter                                                                   | Conditions                                                                  | Min                        | Тур                       | Max                     | Unit |

|-------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|---------------------------|-------------------------|------|

| TRANSMITTER DA                | ATA INPUT (PIN TxD)                                                         |                                                                             |                            | 1                         | ı                       |      |

| I <sub>IL</sub>               | Low-Level Input Current                                                     | V <sub>TxD</sub> = 0.3 V <sub>VIO</sub>                                     | -70                        | -250                      | -500                    | μΑ   |

| C <sub>i</sub>                | Input Capacitance                                                           | Not Tested                                                                  | 1.0                        | 5.0                       | 10                      | pF   |

| STANDBY AND EN                | NABLE INPUTS (PINS STB AND EI                                               | N)                                                                          | 1                          |                           |                         | I    |

| V <sub>IH</sub>               | High-Level Input Voltage                                                    |                                                                             | 0.7V <sub>VIO</sub>        | _                         | V <sub>IO</sub> + 0.3   | V    |

| V <sub>IL</sub>               | Low-Level Input Voltage                                                     |                                                                             | -0.3                       | -                         | 0.3V <sub>VIO</sub>     | V    |

| I <sub>IH</sub>               | High-Level Input Current                                                    | $V_{STB} = V_{EN} = 0.7V_{VIO}$                                             | 1.0                        | 5.0                       | 10                      | μΑ   |

| I <sub>IL</sub>               | Low-Level Input Current                                                     | V <sub>STB</sub> = V <sub>EN</sub> = 0 V                                    | -0.5                       | 0                         | 5.0                     | μΑ   |

| C <sub>i</sub>                | Input Capacitance                                                           |                                                                             | 1.0                        | 5.0                       | 10                      | pF   |

| RECEIVER DATA                 | OUTPUT (PIN RxD)                                                            |                                                                             |                            |                           |                         |      |

| I <sub>OH</sub>               | High-Level Output Current                                                   | $V_{RxD} = V_{VIO} - 0.4 V$<br>$V_{VIO} = V_{VCC}$                          | -1.0                       | -3.0                      | -6.0                    | mA   |

| I <sub>OL</sub>               | Low-Level Output Current                                                    | $V_{RxD} = 0.4 \text{ V}$<br>$V_{TxD} = 0 \text{ V Bus is Dominant}$        | 2.0                        | 5.0                       | 12                      | mA   |

| FLAG INDICATION               | I OUTPUT (PIN ERR)                                                          |                                                                             |                            |                           |                         |      |

| I <sub>OH</sub>               | High-Level Output Current                                                   | $V_{\overline{ERR}} = V_{VIO} - 0.4 V$ $V_{VIO} = V_{VCC}$                  | -4.0                       | -20                       | -50                     | μΑ   |

| I <sub>OL</sub>               | Low-Level Output Current                                                    | V <sub>ERR</sub> = 0.4 V                                                    | 100                        | 200                       | 350                     | μΑ   |

| LOCAL WAKE-UP                 | PINPUT (PIN WAKE)                                                           |                                                                             |                            |                           |                         |      |

| I <sub>IH</sub>               | High-Level Input Current                                                    | V <sub>WAKE</sub> = V <sub>VBAT</sub> - 1.9 V                               | -1.0                       | -5.0                      | -10                     | μΑ   |

| I <sub>IL</sub>               | Low-Level Input Current                                                     | V <sub>WAKE</sub> = V <sub>VBAT</sub> – 3.1 V                               | 1.0                        | 5.0                       | 10                      | μΑ   |

| V <sub>threshold</sub>        | Threshold of the Local<br>Wake-up Comparator                                | Sleep or Standby Mode                                                       | V <sub>VBAT</sub> –<br>3 V | V <sub>VBAT</sub> – 2.5 V | V <sub>VBAT</sub> – 2 V | V    |

| INHIBIT OUTPUT (              | (PIN INH)                                                                   |                                                                             |                            |                           |                         |      |

| VH <sub>DROP</sub>            | High Level Voltage Drop                                                     | I <sub>INH</sub> = -180 μA                                                  | 50                         | 200                       | 800                     | mV   |

| I <sub>LEAK</sub>             | Leakage Current in Sleep<br>Mode                                            |                                                                             | 0                          | -                         | 5.0                     | μΑ   |

|                               | Mode                                                                        | T <sub>amb</sub> < 100°C                                                    | 0                          | -                         | 1.0                     | μΑ   |

| BUS LINES (PINS               | CANH AND CANL)                                                              |                                                                             |                            |                           |                         |      |

| V <sub>o(reces)</sub> (norm)  | Recessive Bus Voltage                                                       | V <sub>TxD</sub> = V <sub>VCC</sub> ; No Load, Normal Mode                  | 2.0                        | 2.5                       | 3.0                     | V    |

| V <sub>o(reces)</sub> (stby)  | Recessive Bus Voltage                                                       | V <sub>TxD</sub> = V <sub>VCC</sub> ; No Load, Standby<br>Mode              | -100                       | 0                         | 100                     | mV   |

| I <sub>o(reces)</sub> (CANH)  | Recessive Output Current at Pin CANH                                        | -35 V < V <sub>CANH</sub> < +35 V;<br>0 V < V <sub>CC</sub> < 5.25 V        | -2.5                       | -                         | +2.5                    | mA   |

| I <sub>o(reces)</sub> (CANL)  | Recessive Output Current at Pin CANL                                        | -35 V < V <sub>CANL</sub> < +35 V;<br>0 V < V <sub>VCC</sub> < 5.25 V       | -2.5                       | -                         | +2.5                    | mA   |

| V <sub>o(dom)</sub> (CANH)    | Dominant output Voltage at Pin CANH                                         | V <sub>TxD</sub> = 0 V                                                      | 3.0                        | 3.6                       | 4.25                    | V    |

| V <sub>o(dom)</sub> (CANL)    | Dominant Output Voltage at Pin CANL                                         | V <sub>TxD</sub> = 0 V                                                      | 0. 5                       | 1.4                       | 1.75                    | V    |

| Vo(dif) (bus_dom)             | Differential Bus Output<br>Voltage (V <sub>CANH</sub> - V <sub>CANL</sub> ) | $V_{TxD}$ = 0 V; Dominant;<br>42.5 $\Omega$ < R <sub>LT</sub> < 60 $\Omega$ | 1.5                        | 2.25                      | 3.0                     | V    |

| V <sub>o(dif)</sub> (bus_rec) | Differential Bus Output<br>Voltage (V <sub>CANH</sub> - V <sub>CANL</sub> ) | V <sub>TxD</sub> = V <sub>CC</sub> ; Recessive; No Load                     | -120                       | 0                         | +50                     | mV   |

| I <sub>o(sc)</sub> (CANH)     | Short-Circuit Output Current at Pin CANH                                    | V <sub>CANH</sub> = 0 V; V <sub>TxD</sub> = 0 V                             | -45                        | -70                       | -120                    | mA   |

**Table 8. DC CHARACTERISTICS**

| Symbol                      | Parameter                                                                                         | Conditions                                                                    | Min                      | Тур                      | Max                      | Unit |

|-----------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| BUS LINES (PINS             | CANH AND CANL)                                                                                    |                                                                               | •                        | •                        |                          |      |

| I <sub>o(sc)</sub> (CANL)   | Short-Circuit Output Current at Pin CANL                                                          | V <sub>CANL</sub> = 42 V; V <sub>TxD</sub> = 0 V                              | 45                       | 70                       | 120                      | mA   |

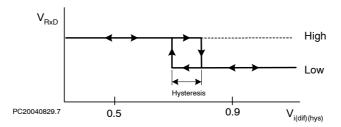

| V <sub>i(dif) (th)</sub>    | Differential Receiver Threshold<br>Voltage (see Figure 7)                                         | -12 V < V <sub>CANL</sub> < +12 V<br>-12 V < V <sub>CANH</sub> < +12 V        | 0.5                      | 0.7                      | 0.9                      | V    |

| V <sub>ihem(dif)</sub> (th) | Differential Receiver Threshold<br>Voltage for High<br>Common-Mode (see Figure 7)                 | -35 V < V <sub>CANL</sub> < +35 V<br>-35 V < V <sub>CANH</sub> < +35 V        | 0.35                     | 0.7                      | 1.00                     | V    |

| V <sub>i(dif)</sub> (hys)   | Differential Receiver Input<br>Voltage Hysteresis<br>(see Figure 7)                               | -35 V < V <sub>CANL</sub> < +35 V<br>-35V <v<sub>CANH &lt; +35 V</v<sub>      | 50                       | 70                       | 100                      | mV   |

| V <sub>I(dif)_</sub> WAKE   | Differential Receiver Input<br>Voltage for Bus Wake-up<br>Detection (in Sleep or<br>Standby Mode) | -12 V < V <sub>CANH</sub> < +12 V<br>-12 V < V <sub>CANH</sub> < +12 V        | 0.4                      | 0.8                      | 1.15                     | V    |

| R <sub>i(cm) (CANH)</sub>   | Common-Mode Input<br>Resistance at Pin CANH                                                       |                                                                               | 15                       | 26                       | 39                       | kΩ   |

| R <sub>i(cm)</sub> (CANL)   | Common-Mode Input<br>Resistance at Pin CANL                                                       |                                                                               | 15                       | 26                       | 39                       | kΩ   |

| $R_{i(cm)(m)}$              | Matching between Pin CANH<br>and Pin CANL Common<br>Mode Input Resistance                         | V <sub>CANH</sub> = V <sub>CANL</sub>                                         | -3.0                     | 0                        | +3.0                     | %    |

| R <sub>i(dif)</sub>         | Differential Input Resistance                                                                     |                                                                               | 25                       | 50                       | 75                       | kΩ   |

| C <sub>i(CANH)</sub>        | Input Capacitance at Pin<br>CANH                                                                  | $V_{TxD} = V_{CC}$                                                            |                          | 7.5                      | 20                       | pF   |

| C <sub>i(CANL)</sub>        | Input Capacitance at Pin<br>CANL                                                                  | V <sub>TxD</sub> = V <sub>CC</sub>                                            |                          | 7.5                      | 20                       | pF   |

| C <sub>i(dif)</sub>         | Differential Input Capacitance                                                                    | $V_{TxD} = V_{CC}$                                                            |                          | 3.75                     | 10                       | pF   |

| COMMON-MODE                 | STABILIZATION (PIN V <sub>SPLIT</sub> )                                                           |                                                                               |                          |                          |                          |      |

| V <sub>SPLIT</sub>          | Reference Output Voltage at Pin V <sub>SPLIT</sub>                                                | Normal mode;<br>-500 μA < I <sub>SPLIT</sub> < 500 μA                         | 0.3 x<br>V <sub>CC</sub> | 0.5 x<br>V <sub>CC</sub> | 0.7 x<br>V <sub>CC</sub> |      |

| I <sub>SPLIT(i)</sub>       | V <sub>SPLIT</sub> Leakage Current                                                                | Standby Mode<br>-27 V < V <sub>SPLIT</sub> < 40 V                             | -50                      |                          | +50                      | μΑ   |

|                             |                                                                                                   | Standby Mode<br>-27 V < V <sub>SPLIT</sub> < 40 V<br>T <sub>amb</sub> < 100°C | -5.0                     |                          | +5.0                     |      |

| I <sub>SPLIT(lim)</sub>     | V <sub>SPLIT</sub> Limitation Current<br>(Absolute Value)                                         | Normal Mode                                                                   | 1.3                      | 3.0                      | 5.0                      | mA   |

| THERMAL SHUTE               | DOWN                                                                                              |                                                                               | -                        |                          |                          |      |

| T <sub>J(SD)</sub>          | Shutdown Junction<br>Temperature                                                                  |                                                                               | 150                      | 160                      | 180                      | °C   |

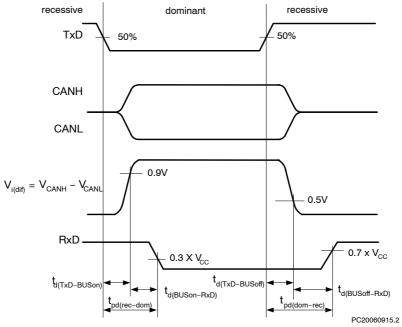

**Table 9. AC CHARACTERISTICS**

| Symbol                     | Parameter                                                     | Conditions                  | Min  | Тур | Max  | Unit |

|----------------------------|---------------------------------------------------------------|-----------------------------|------|-----|------|------|

| TIMING CHARACT             | TERISTICS (Figure 6)                                          |                             | •    |     | •    |      |

| t <sub>d</sub> (TxD-BUSon) | Delay TxD to Bus Active                                       | Setup According to Figure 8 | 40   | 85  | 105  | ns   |

| t <sub>d(TxD-BUSoff)</sub> | Delay TxD to Bus Inactive                                     | Setup According to Figure 8 | 30   | 60  | 105  | ns   |

| t <sub>d(BUSon-RxD)</sub>  | Delay Bus Active to RxD                                       | Setup According to Figure 8 | 25   | 55  | 105  | ns   |

| t <sub>d(BUSoff-RxD)</sub> | Delay Bus Inactive to RxD                                     | Setup According to Figure 8 | 40   | 65  | 105  | ns   |

| <sup>t</sup> pd(rec-dom)   | Propagation Delay TxD to<br>RxD from Recessive to<br>Dominant | Setup According to Figure 8 | 90   | 130 | 230  | ns   |

| t <sub>d(dom-rec)</sub>    | Propagation Delay TxD to<br>RxD from Dominant to<br>Recessive | Setup According to Figure 8 | 90   | 140 | 245  | ns   |

| t <sub>UV(VCC)</sub>       | Undervoltage Detection Time on V <sub>CC</sub>                |                             | 5.0  | 10  | 12.5 | ms   |

| t <sub>UV(VIO)</sub>       | Undervoltage Detection Time on V <sub>IO</sub>                |                             | 5.0  | 10  | 12.5 | ms   |

| t <sub>dom(TxD)</sub>      | TxD Dominant Timeout                                          |                             | 300  | 600 | 1000 | μs   |

| t <sub>h(min)</sub>        | Minimum Hold-Time for the Go-to-Sleep Mode                    |                             | 15   | 35  | 50   | μS   |

| t <sub>dom</sub>           | Dominant Time for Wake-up                                     | Vdif(CAN) > 1.4 V           | 0.75 | 2.5 | 5.0  | μs   |

|                            | via the Bus                                                   | Vdif(CAN) > 1.2 V           | 0.75 | 3.0 | 5.8  | μs   |

| t <sub>rec</sub>           | Recessive Time for Wake-up via the Bus                        | V <sub>BAT</sub> = 12 V     | 0.75 | 2.5 | 5.0  | μs   |

| t <sub>WAKE</sub>          | Debounce Time for the<br>Wake-up via WAKE Pin                 | V <sub>BAT</sub> = 12 V     | 5.0  | 25  | 50   | μS   |

| t <sub>errdet</sub>        | Minimum dominant bit time for bus error detection             | NCV7341D20 version          | 1    | 2   | 4    | μs   |

## **MEASUREMENT DEFINITIONS AND SETUPS**

Figure 6. Timing Diagram for AC Characteristics

Figure 7. Hysteresis of the Receiver

Figure 8. Test Circuit for Timing Characteristics

**Figure 9. Test Circuit for Automotive Transients**

#### **DEVICE ORDERING INFORMATION**

| Part Number   | Description                                 | Temperature Range | Package Type         | Shipping <sup>†</sup> |

|---------------|---------------------------------------------|-------------------|----------------------|-----------------------|

| NCV7341D20G   | HS CAN Transceiver with bus error detection | −40°C − 125°C     | SOIC-14<br>(Pb-Free) | 55 Tube / Tray        |

| NCV7341D20R2G |                                             | −40°C − 125°C     | SOIC-14<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCV7341D21G   | HS CAN Transceiver                          | −40°C − 125°C     | SOIC-14<br>(Pb-Free) | 55 Tube / Tray        |

| NCV7341D21R2G |                                             | −40°C − 125°C     | SOIC-14<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

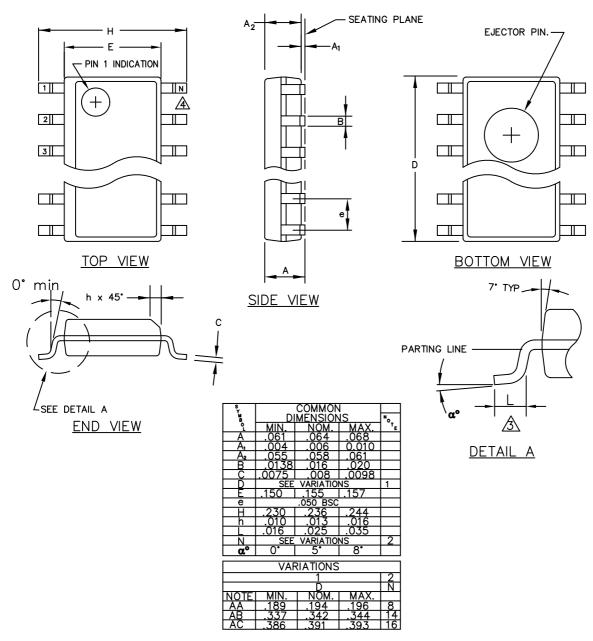

SOIC 14 CASE 751AP-01 ISSUE A

#### 1. ALL DIMENSIONS ARE IN MILLIMETERS.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

NCV7341D21G NCV7341D20G NCV7341D20R2G