## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

### **General Description**

The MAX16930/MAX16931 offer two high-voltage, synchronous step-down controllers and a step-up preboost controller. They operate with an input voltage supply from 2V to 42V with preboost active and can "operate in drop-out condition by running at 95% duty cycle. The devices are intended for applications with mid- to high-power requirements that operate at a wide input voltage range such as during automotive cold-crank or engine stop-start conditions.

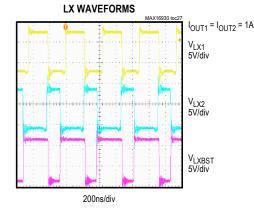

The MAX16930/MAX16931 step-down controllers operate 180° out-of-phase at frequencies up to 2.2MHz to allow small external components, reduced output ripple, and to guarantee no AM band interference. The switching frequency is resistor adjustable. The FSYNC input programmability enables three frequency modes for optimized performance: forced fixed-frequency operation, skip mode with ultra-low quiescent current (20µA), and synchronization to an external clock. The devices also provide a spread-spectrum option to minimize EMI interference.

The MAX16930/MAX16931 are offered with an asynchronous step-up controller. This preboost circuitry turns on during low input voltage conditions. It is designed to provide power to step-down controller channels with input voltages as low as 2V.

The devices also feature a power-OK monitor and overvoltage and undervoltage lockout. Protection features include cycle-by-cycle current limit and thermal shutdown.

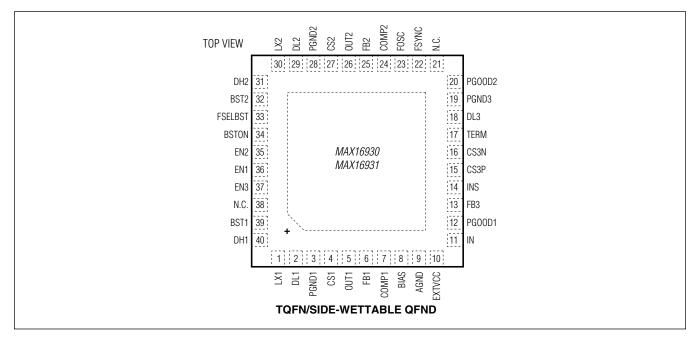

The devices are available in 40-pin TQFN-EP and side-wettable QFND-EP packages and are specified for operation over the -40°C to +125°C automotive temperature range.

<u>Selector Guide</u> and <u>Ordering Information</u> appear at end of data sheet.

### **Benefits and Features**

- Meets Stringent OEM Module Power Consumption and Performance Specifications

- 20µA Quiescent Current in Skip Mode

- ±1% Output-Voltage Accuracy: 5.0V/3.3V Fixed or Adjustable Between 1V and 10V

- Enables Crank-Ready Designs

- Integrated Preboost for Operation Down to 2V in Bootstrap Mode

- Wide Input Supply Range from 3.5V to 36V (without Preboost)

- EMI Reduction Features Reduce Interference with Sensitive Radio Bands without Sacrificing Wide Input Voltage Range

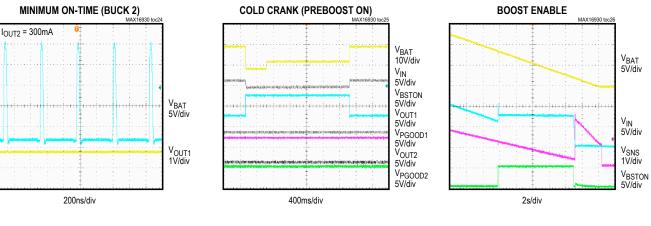

- 50ns (typ) Minimum On-Time Guarantees Skip-Free Operation for 3.3V Output from Car Battery at 2.2MHz

- Frequency-Synchronization Input

- Resistor-Programmable Frequency Between 200kHz and 2.2MHz

- Integration and Thermally Enhanced Packages Save Board Space and Cost

- Dual, 2MHz Step-Down Controllers

- 180° Out-of-Phase Operation

- Current-Mode Controllers with Forced-Continuous and Skip Modes

- Thermally Enhanced 40-Pin TQFN-EP and Side-Wettable QFND-EP Packages

- Protection Features Improve System Reliability

- Supply Overvoltage and Undervoltage Lockout

- Overtemperature and Short-Circuit Protection

### **Applications**

POL Applications for Automotive Power Distributed DC Power Systems Navigation and Radio Head Units

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

### **Absolute Maximum Ratings**

| IN, INS, CS3P, CS3N, FB3, EN1, EN2, |                 |

|-------------------------------------|-----------------|

| EN3, TERM to PGND                   | 0.3V to +42V    |

| CS1, CS2, OUT1, OUT2 to AGND        | 0.3V to +11V    |

| CS1 to OUT1                         | 0.2V to +0.2V   |

| CS2 to OUT2                         | 0.2V to +0.2V   |

| CS3P to CS3N                        | 0.2V to +0.2V   |

| BIAS, FSYNC, FOSC to AGND           | -0.3V to +6.0V  |

| COMP1, COMP2, BSTON to AGND         | -0.3V to +6.0V  |

| FB1, FB2, FSELBST, EXTVCC to AGND   | -0.3V to +6.0V  |

| DL_ to PGND_ (Note 1)               | -0.3V to +6.0V  |

| BST_ to LX_ (Note 1)                | 0.3V to + 6.0V  |

| DH_ to LX_ (Note 1)                 | -0.3V to + 6.0V |

| LX_ to PGND_ (Note 1)                                 | 0.3V to +42V   |

|-------------------------------------------------------|----------------|

| PGND_ to AGND                                         | 0.3V to +0.3V  |

| PGOOD1, PGOOD2 to AGND                                | 0.3V to +6.0V  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| TQFN (derate 37mW/°C above +70°C)                     | 2963mW         |

| QFND (derate 29.4mW/°C above +70°C)                   | 2350mW         |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature Range                            | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     |                |

| Soldering Temperature (reflow)                        | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Package Thermal Characteristics (Note 2)

QFND Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>)......34°C/W Junction-to-Case Thermal Resistance (θ<sub>JC</sub>)......3.9°C/W

Note 1: Self-protected against transient voltages exceeding these limits for ≤ 50ns under normal operation and loads up to the maximum rated output current.

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **Electrical Characteristics**

$(V_{IN} = 14V, V_{BIAS} = 5V, C_{BIAS} = 6.8\mu$ F,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.) (Note 3)

| PARAMETER                              | SYMBOL            | CONDITIONS                                                                                       | MIN   | ТҮР | MAX   | UNIT |  |

|----------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|-------|-----|-------|------|--|

| SYNCHRONOUS STEP-DOWN DC-DC CONVERTERS |                   |                                                                                                  |       |     |       |      |  |

|                                        |                   | Normal operation                                                                                 | 3.5   |     | 36    |      |  |

| Supply Voltage Range                   | VIN               | t < 1s                                                                                           |       |     | 42    | V    |  |

| Supply voltage hange                   | VIN               | With preboost after initial startup condition is satisfied                                       | 2.0   |     | 36    | V    |  |

|                                        |                   | $V_{EN1} = V_{EN2} = V_{EN3} = 0V$                                                               |       | 8   | 20    |      |  |

| Supply Current                         |                   | $V_{EN1} = 5V, V_{OUT1} = 5V, V_{EN2} = V_{EN3} = 0V, V_{EXTVCC} = 5V$ , no switching            |       | 30  | 40    |      |  |

|                                        | I <sub>IN</sub>   | $V_{EN2}$ = 5V, $V_{OUT2}$ = 3.3V, $V_{EN1}$ = $V_{EN3}$ = 0V, $V_{EXTVCC}$ = 3.3V, no switching |       | 20  | 30    | μA   |  |

|                                        |                   |                                                                                                  |       | 25  | 40    |      |  |

| Puek 1 Fixed Output Valtage            |                   | V <sub>FB1</sub> = V <sub>BIAS</sub> , PWM mode                                                  | 4.95  | 5   | 5.05  | V    |  |

| Buck 1 Fixed Output Voltage            | V <sub>OUT1</sub> | V <sub>FB1</sub> = V <sub>BIAS</sub> , skip mode                                                 | 4.95  | 5   | 5.075 | V    |  |

| Duck 0 Fixed Output Valtage            |                   | V <sub>FB2</sub> = V <sub>BIAS</sub> , PWM mode                                                  | 3.234 | 3.3 | 3.366 | V    |  |

| Buck 2 Fixed Output Voltage            | V <sub>OUT2</sub> | V <sub>FB2</sub> = V <sub>BIAS</sub> , skip mode                                                 | 3.234 | 3.3 | 3.4   | v    |  |

| Output Voltage Adjustable<br>Range     |                   | Buck 1, buck 2                                                                                   | 1     |     | 10    | V    |  |

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

## **Electrical Characteristics (continued)**

(V<sub>IN</sub> = 14V, V<sub>BIAS</sub> = 5V, C<sub>BIAS</sub> =  $6.8\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER                               | SYMBOL                | CONDITIONS                                                            | MIN  | ТҮР                | MAX  | UNIT |

|-----------------------------------------|-----------------------|-----------------------------------------------------------------------|------|--------------------|------|------|

| Regulated Feedback Voltage              | V <sub>FB1,2</sub>    |                                                                       | 0.99 | 1.0                | 1.01 | V    |

|                                         |                       | FB rising                                                             | +10  | +15                | +20  | 0/   |

| Output Overvoltage Threshold            |                       | FB falling (Note 4)                                                   | +5   | +10                | +15  | %    |

| Feedback Leakage Current                | I <sub>FB1,2</sub>    | $T_A = +25^{\circ}C$                                                  |      | 0.01               | 1    | μA   |

| Feedback Line Regulation Error          | ,                     | $V_{IN} = 3.5V$ to 36V, $V_{FB} = 1V$                                 |      | 0.00               |      | %/V  |

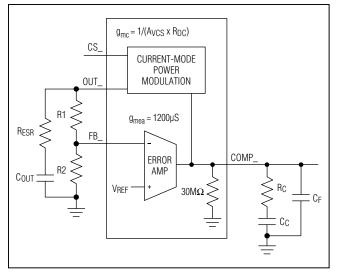

| Transconductance<br>(from FB_ to COMP_) | 9m                    | V <sub>FB</sub> = 1V, V <sub>BIAS</sub> = 5V (Note 5)                 |      | 1200               | 2400 | μS   |

|                                         |                       | MAX16930, DL_ low to DH_ high                                         |      | 35                 |      |      |

| - · -·                                  |                       | MAX16930, DH_ low to DL_ high                                         |      | 60                 |      |      |

| Dead Time                               |                       | MAX16931, DL_ low to DH_ high                                         |      | 60                 |      | ns   |

|                                         |                       | MAX16931, DH_ low to DL_ high                                         |      | 100                |      |      |

| Maximum Duty-Cycle                      |                       | Buck 1, buck 2                                                        |      |                    | 95   | %    |

| Minimum On-Time                         | t <sub>ON(MIN)</sub>  | Buck 1, buck 2                                                        |      | 50                 |      | ns   |

| PWM Switching Frequency                 |                       | Programmable, high frequency,<br>MAX16930                             | 1    |                    | 2.2  |      |

| Range                                   |                       | Programmable, low frequency,<br>MAX16931                              | 0.2  |                    | 1    | MHz  |

| Buck 2 Switching Frequency              |                       | MAX16930ATLT/V+,<br>MAX16930BATLU/V+ only                             |      | 1/2f <sub>SW</sub> |      | MHz  |

|                                         | f                     | MAX16930, R <sub>FOSC</sub> = 13.7k $\Omega$ , V <sub>BIAS</sub> = 5V | 1.98 | 2.2                | 2.42 | MHz  |

| Switching Frequency Accuracy            | f <sub>SW</sub>       | MAX16931, $R_{FOSC} = 80.6 k\Omega$ , $V_{BIAS} = 5V$                 | 360  | 400                | 440  | kHz  |

| Spread-Spectrum Range                   |                       | Spread spectrum enabled                                               |      | ±6                 |      | %    |

| FSYNC INPUT                             |                       |                                                                       |      |                    |      |      |

| FSYNC Frequency Range                   |                       | Minimum sync pulse of 100ns, MAX16930                                 | 1.2  |                    | 2.4  | MHz  |

|                                         |                       | Minimum sync pulse of 100ns, MAX16931                                 | 240  |                    | 1200 | kHz  |

| FSYNC Switching Thresholds              |                       | High threshold                                                        | 1.5  |                    |      | V    |

|                                         |                       | Low threshold                                                         |      |                    | 0.6  |      |

| CS Current-Limit Voltage<br>Threshold   | V <sub>LIMIT1,2</sub> | $V_{CS}$ - $V_{OUT}$ , $V_{BIAS}$ = 5V, $V_{OUT} \ge 2.5V$            | 64   | 80                 | 96   | mV   |

| Skip Mode Threshold                     |                       | Current sense = 80mV                                                  |      | 15                 |      | mV   |

| Soft-Start Ramp Time                    |                       | Buck 1 and buck 2, fixed soft-start time regardless of frequency      | 2    | 6                  | 10   | ms   |

| Phase Shift Between Buck1 and Buck 2    |                       |                                                                       |      | 180                |      | o    |

| LX1, LX2 Leakage Current                |                       | $V_{IN} = 6V, V_{LX_{-}} = V_{IN}, T_A = +25^{\circ}C$                |      | 0.01               | 1    | μA   |

| DH1, DH2 Pullup Resistance              |                       | $V_{BIAS} = 5V, I_{DH} = -100$ mA                                     |      | 10                 | 20   | Ω    |

| DH1, DH2 Pulldown Resistance            |                       | $V_{BIAS} = 5V, I_{DH_} = +100mA$                                     |      | 2                  | 4    | Ω    |

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

### **Electrical Characteristics (continued)**

$(V_{IN} = 14V, V_{BIAS} = 5V, C_{BIAS} = 6.8\mu$ F,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.) (Note 3)

| PARAMETER                                                                                                     | SYMBOL                 | CONDITIONS                                                                                                                                                      | MIN  | ТҮР  | МАХ  | UNIT   |  |

|---------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|--|

| DL1, DL2 Pullup Resistance                                                                                    |                        | $V_{BIAS} = 5V, I_{DL_} = -100mA$                                                                                                                               |      | 4    | 8    | Ω      |  |

| DL1, DL2 Pulldown Resistance                                                                                  |                        | $V_{BIAS} = 5V, I_{DL_} = +100mA$                                                                                                                               |      | 1.5  | 3    | Ω      |  |

|                                                                                                               | P <sub>GOOD_H</sub>    | % of V <sub>OUT</sub> , rising                                                                                                                                  | 85   | 90   | 95   |        |  |

| PGOOD1, PGOOD2 Threshold                                                                                      | P <sub>GOOD_F</sub>    | % of V <sub>OUT</sub> , falling                                                                                                                                 | 80   | 85   | 90   | - %    |  |

| PGOOD1, PGOOD2 Leakage<br>Current                                                                             |                        | $V_{PGOOD1,2} = 5V, T_A = +25^{\circ}C$                                                                                                                         |      | 0.01 | 1    | μA     |  |

| PGOOD1, PGOOD2 Startup<br>Delay Time                                                                          |                        | Buck 1 and buck 2 after soft-start is complete                                                                                                                  |      | 64   |      | Cycles |  |

| PGOOD1, PGOOD2 Debounce<br>Time                                                                               |                        | Fault detection                                                                                                                                                 | 8    | 20   | 40   | μs     |  |

| INTERNAL LDO: BIAS                                                                                            | -                      |                                                                                                                                                                 |      |      |      |        |  |

| Internal BIAS Voltage                                                                                         |                        | V <sub>IN</sub> > 6V                                                                                                                                            | 4.75 | 5    | 5.25 | V      |  |

| BIAS UVLO Threshold                                                                                           |                        | V <sub>BIAS</sub> rising                                                                                                                                        |      | 3.1  | 3.4  | V      |  |

| BIAS OVED THreshold                                                                                           |                        | V <sub>BIAS</sub> falling                                                                                                                                       | 2.7  | 2.9  |      |        |  |

| Hysteresis                                                                                                    |                        |                                                                                                                                                                 |      | 0.2  |      | V      |  |

| External $V_{CC}$ Threshold                                                                                   | V <sub>TH,EXTVCC</sub> | EXTVCC rising, HYST = 110mV                                                                                                                                     |      | 3    | 3.2  | V      |  |

| THERMAL OVERLOAD                                                                                              |                        |                                                                                                                                                                 |      |      |      |        |  |

| Thermal Shutdown Temperature                                                                                  |                        | (Note 5)                                                                                                                                                        |      | 170  |      | °C     |  |

| Thermal Shutdown Hysteresis                                                                                   |                        | (Note 5)                                                                                                                                                        |      | 20   |      | °C     |  |

| EN LOGIC INPUT                                                                                                |                        |                                                                                                                                                                 |      |      |      |        |  |

| High Threshold                                                                                                |                        |                                                                                                                                                                 | 1.8  |      |      | V      |  |

| Low Threshold                                                                                                 |                        |                                                                                                                                                                 |      |      | 0.8  | V      |  |

| Input Current                                                                                                 |                        | EN1, EN2 logic inputs only, $T_A = +25^{\circ}C$                                                                                                                |      | 0.01 | 1    | μA     |  |

| PREBOOST                                                                                                      |                        |                                                                                                                                                                 |      |      |      |        |  |

| Minimum On Time                                                                                               | TON <sub>BST</sub>     |                                                                                                                                                                 |      | 60   |      | ns     |  |

| Minimum Off Time                                                                                              | TOFF <sub>BST</sub>    |                                                                                                                                                                 |      | 60   |      | ns     |  |

| Switching Frequency                                                                                           | fra                    | $V_{\text{FSELBST}} = 0V, R_{\text{FOSC}} = 13.7 \text{k}\Omega$                                                                                                | 1.98 | 2.2  | 2.42 | MHz    |  |

| Switching Frequency                                                                                           | f <sub>BOOST</sub>     | $V_{\text{FSELBST}} = V_{\text{BIAS}}, R_{\text{FOSC}} = 13.7 \text{k}\Omega$                                                                                   | 0.4  | 0.44 | 0.48 |        |  |

| Current Limit                                                                                                 | ILIMBST                | CS3P - CS3N                                                                                                                                                     | 108  | 120  | 132  | mV     |  |

| INS Unlock Threshold VINS,UV One-time latch during s<br>tis disabled until the VINS,UV this threshold (MAX169 |                        | One-time latch during startup; preboost<br>is disabled until the V <sub>INS</sub> rises above<br>this threshold (MAX16930ATLV/V+,<br>MAX16930BATLW/V+ (Note 6)) | 1    | 1.05 | 1.1  | V      |  |

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

### **Electrical Characteristics (continued)**

$(V_{IN} = 14V, V_{BIAS} = 5V, C_{BIAS} = 6.8\mu$ F,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.) (Note 3)

| PARAMETER                                                                 | SYMBOL                  | CONDITIONS                                                                                                                                                  | MIN    | ТҮР  | MAX    | UNIT |

|---------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|------|

| INS Off Threshold                                                         | V <sub>INS,OFF</sub>    | Battery rising and EN3 high, preboost<br>turns off if V <sub>INS</sub> is above this threshold<br>(MAX16930ATLV/V+, MAX16930BATLW/<br>V+ (Note 6))          | 1.2    | 1.25 | 1.3    | V    |

| INS On Threshold                                                          | V <sub>INS,ON</sub> ,SW | Battery falling and EN3 high, preboost<br>turns back on when V <sub>INS</sub> falls below<br>this threshold (MAX16930ATLV/V+,<br>MAX16930BATLW/V+ (Note 6)) | 1.1    | 1.15 | 1.2    | v    |

| INS Threshold<br>Undervoltage Lockout                                     |                         | Battery rising and EN3 high<br>(MAX16930ATLV/V+, MAX16930BATLW/<br>V+ (Note 6))                                                                             | 0.325  | 0.35 | 0.375  |      |

|                                                                           | V <sub>INS,UV</sub>     | Battery falling and EN3 high, preboost<br>turns off when V <sub>INS</sub> falls below this<br>threshold (MAX16930ATLV/V+,<br>MAX16930BATLW/V+ (Note 6))     | 0.275  | 0.3  | 0.325  | V    |

| BSTON Leakage Current                                                     |                         | $V_{BSTON} = 5V, T_A = +25^{\circ}C$                                                                                                                        |        | 0.01 | 1      | μA   |

| BSTON Debounce Time                                                       |                         | Fault detection                                                                                                                                             |        | 10   |        | μs   |

| DL3 Pullup Resistance                                                     |                         | $V_{BIAS} = 5V, I_{DL3} = -100mA$                                                                                                                           |        | 4    | 8      | Ω    |

| DL3 Pulldown resistance                                                   |                         | $V_{BIAS} = 5V, I_{DL3} = +100mA$                                                                                                                           |        | 1    | 2      | Ω    |

| Feedback Voltage                                                          | V <sub>FB3</sub>        | No load on boost output                                                                                                                                     | 1.1875 | 1.25 | 1.3125 | V    |

| Boost Load Begulation Error 0mV < V <sub>CS3P</sub> - V <sub>CS3N</sub> < |                         | 0mV < V <sub>CS3P</sub> - V <sub>CS3N</sub> < 120mV,<br>error proportional to input current                                                                 |        | 0.7  |        | %/A  |

| EN3 Threshold                                                             |                         | High threshold                                                                                                                                              | 3.5    |      |        | V    |

|                                                                           |                         | Low threshold                                                                                                                                               |        |      | 2      | v    |

| EN3 Input Current                                                         |                         | V <sub>EN3</sub> = 5.5V                                                                                                                                     |        | 7    | 14     | μA   |

| TERM Resistance                                                           |                         | I <sub>TERM</sub> = 10mA                                                                                                                                    |        | 70   | 150    | Ω    |

| TERM Leakage Current                                                      |                         | $V_{\text{TERM}} = 14V, V_{\text{EN3}} = 0V, T_{\text{A}} = +25^{\circ}\text{C}$                                                                            |        | 0.01 | 1      | μA   |

| INS and FB3 Leakage Current                                               |                         | $T_A = +25^{\circ}C$                                                                                                                                        |        | 0.01 | 1      | μA   |

**Note 3:** Limits are 100% production tested at  $T_A = +25^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}$ C.

Note 4: Overvoltage protection is detected at the FB1/FB2 pins. If the feedback voltage reaches overvoltage threshold of FB1/FB2 + 15% (typ), the corresponding controllers stop switching. The controllers resume switching once the output drops below FB1/FB2 + 10% (typ).

Note 5: Guaranteed by design; not production tested.

Note 6: INS pin functionality is disabled for the MAX16930ATLV/V+, MAX16930BATLW/V+. EN3 directly controls the turn-on and turn-off of the boost controller.

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

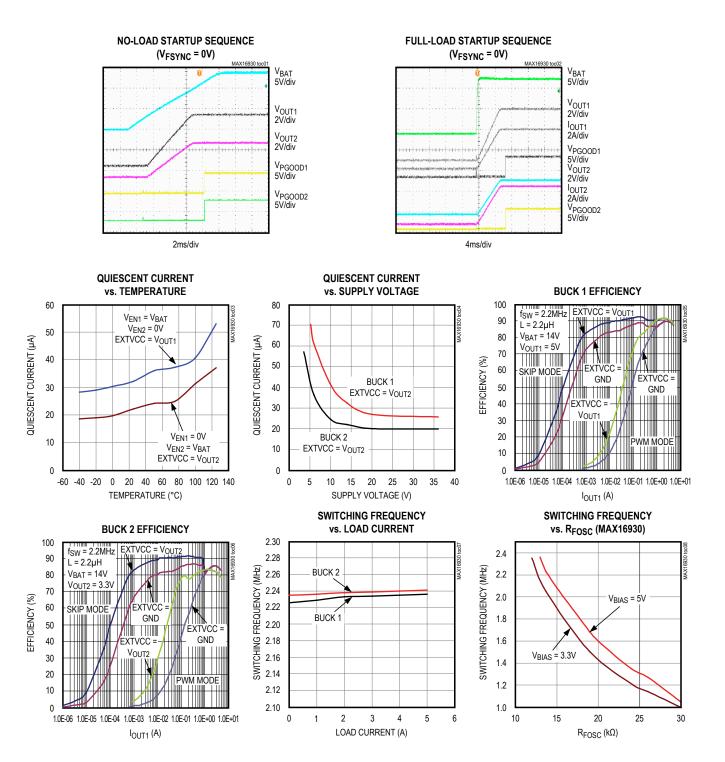

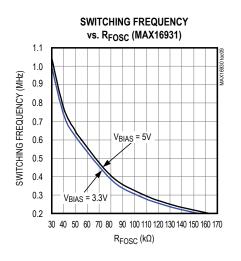

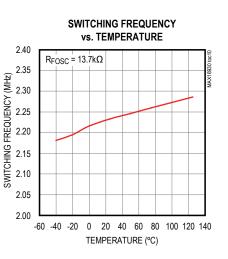

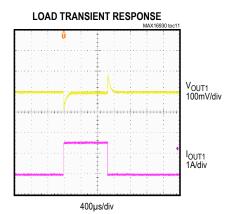

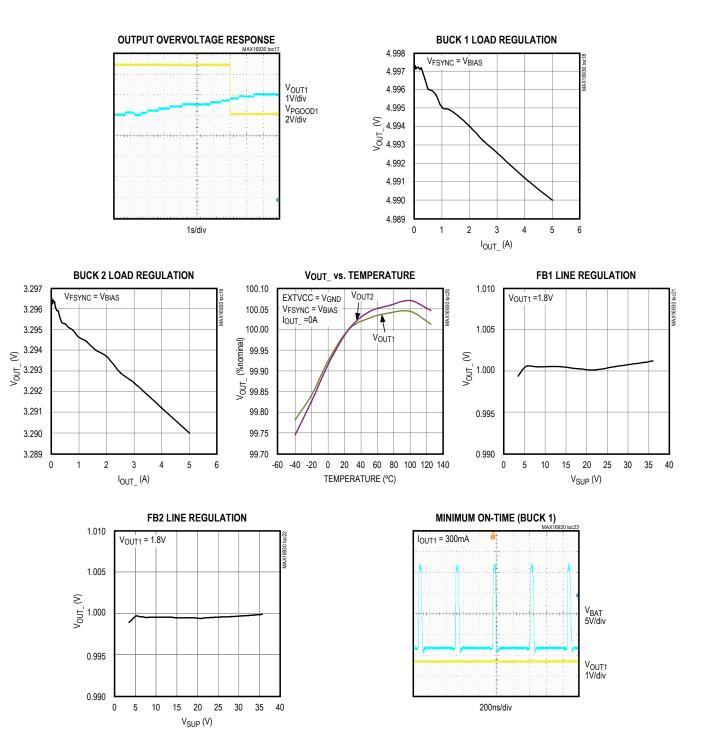

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

S

Vour

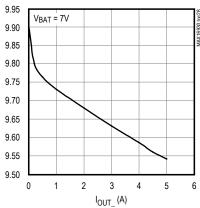

PREBOOST LOAD REGULATION

# 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

## **Pin Configuration**

### **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LX1    | Inductor Connection for Buck 1. Connect LX1 to the switched side of the inductor. LX1 serves as the lower supply rail for the DH1 high-side gate drive.                                                                                                                                                                                                 |

| 2   | DL1    | Low-Side Gate Drive Output for Buck 1. DL1 output voltage swings from VPGND1 to VBIAS.                                                                                                                                                                                                                                                                  |

| 3   | PGND1  | Power Ground for Buck 1                                                                                                                                                                                                                                                                                                                                 |

| 4   | CS1    | Positive Current-Sense Input for Buck 1. Connect CS1 to the positive terminal of the current-sense resistor. See the <i>Current Limiting and Current-Sense Inputs</i> and <i>Current-Sense Measurement</i> sections.                                                                                                                                    |

| 5   | OUT1   | Output Sense and Negative Current-Sense Input for Buck 1. When using the internal preset 5V feedback divider (FB1 = BIAS), the buck uses OUT1 to sense the output voltage. Connect OUT1 to the negative terminal of the current-sense resistor. See the <i>Current Limiting and Current-Sense Inputs</i> and <i>Current-Sense Measurement</i> sections. |

| 6   | FB1    | Feedback Input for Buck 1. Connect FB1 to BIAS for the 5V fixed output or to a resistive divider between OUT1 and GND to adjust the output voltage between 1V and 10V. In adjustable mode, FB1 regulates to 1V (typ). See the <i>Setting the Output Voltage in Buck Converters</i> section.                                                             |

| 7   | COMP1  | Buck 1 Error-Amplifier Output. Connect an RC network to COMP1 to compensate buck 1.                                                                                                                                                                                                                                                                     |

| 8   | BIAS   | 5V Internal Linear Regulator Output. Bypass BIAS to GND with a low-ESR ceramic capacitor of 6.8µF minimum value. BIAS provides the power to the internal circuitry and external loads. See the <i>Fixed 5V Linear Regulator (BIAS)</i> section.                                                                                                         |

| 9   | AGND   | Signal Ground for IC                                                                                                                                                                                                                                                                                                                                    |

| 10  | EXTVCC | 3.1V to 5.2V Input to the Switchover Comparator                                                                                                                                                                                                                                                                                                         |

# 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

## **Pin Description (continued)**

| PIN    | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11     | IN     | Supply Input. Connect IN to the output of the preboost. Bypass IN with sufficient capacitance to supply the two out-of-phase buck converters.                                                                                                                                                                                                                                                                                                                                                            |

| 12     | PGOOD1 | Open-Drain Power-Good Output for Buck 1. PGOOD1 is low if OUT1 is more than 15% (typ) below the normal regulation point. PGOOD1 asserts low during soft-start and in shutdown. PGOOD1 becomes high impedance when OUT1 is in regulation. To obtain a logic signal, pullup PGOOD1 with an external resistor connected to a positive voltage lower than 5.5V. Place a minimum of $100\Omega$ (R <sub>PGOOD1</sub> ) in series with PGOOD1. See the <i>Voltage Monitoring (PGOOD_)</i> section for details. |

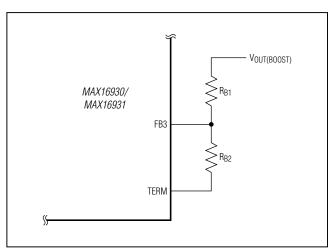

| 13     | FB3    | Preboost Feedback Input. Connect FB3 to the center tap of a resistive-divider between the boost regulator output and TERM to adjust the output voltage. FB3 regulates to 1.25V (typ). Ensure that the parallel combination of the resistor-divider network is > $500\Omega$ . See the <i>Setting the Output Voltage in Boost Converter</i> section.                                                                                                                                                      |

| 14     | INS    | Input Voltage Sense for Preboost. The voltage at INS is compared to internal comparator reference. Program the preboost threshold by using resistor-divider from BAT to INS to TERM pin. Ensure that the parallel combination of the resistor-divider network is > $500\Omega$ . For the MAX16930ATLV/V+ and MAX16930BATLW/V+, the INS functionality is disabled; however, the INS pin should still be connected using the resistor-divider between V <sub>BAT</sub> and the TERM pin.                   |

| 15     | CS3P   | Positive Current-Sense Input for Preboost. Connect CS3P to the positive terminal of the current-<br>sense resistor. See the <i>Current Limit in Boost Controller</i> and <i>Shunt Resistor Selection in Boost</i><br><i>Converter</i> sections.                                                                                                                                                                                                                                                          |

| 16     | CS3N   | Negative Current-Sense Input for Preboost. Connect CS3N to the negative terminal of the current-<br>sense resistor. See the <i>Current Limit in Boost Controller</i> and <i>Shunt Resistor Selection in Boost</i><br><i>Converter</i> sections.                                                                                                                                                                                                                                                          |

| 17     | TERM   | Ground Switch. TERM opens when the voltage at EN3 is logic-low. Use TERM to terminate the preboost feedback and INS resistive divider.                                                                                                                                                                                                                                                                                                                                                                   |

| 18     | DL3    | Preboost n-Channel MOSFET Gate-Drive Output                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19     | PGND3  | Power Ground for Preboost. All the high-current paths for the preboost should terminate to this ground.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20     | PGOOD2 | Open-Drain Power-Good Output for Buck 2. PGOOD2 is low if OUT2 is more than 90% (typ) below the normal regulation point. PGOOD2 asserts low during soft-start and in shutdown. PGOOD2 becomes high impedance when OUT2 is in regulation. To obtain a logic signal, pullup PGOOD2 with an external resistor connected to a positive voltage lower than 5.5V.                                                                                                                                              |

| 21, 38 | N.C.   | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 22     | FSYNC  | External Clock Synchronization Input. Synchronization to the controller operating frequency ratio is 1. Keep f <sub>SYNC</sub> a minimum of 10% greater than the maximum internal switching frequency for stable operation. See the <i>Switching Frequency/External Synchronization</i> section.                                                                                                                                                                                                         |

| 23     | FOSC   | Frequency Setting Input. Connect a resistor from FOSC to AGND to set the switching frequency of the DC-DC converters.                                                                                                                                                                                                                                                                                                                                                                                    |

| 24     | COMP2  | Buck 2 Error Amplifier Output. Connect an RC network to COMP2 to compensate buck 2.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25     | FB2    | Feedback Input for Buck 2. Connect FB2 to BIAS for the 3.3V fixed output or to a resistive divider between OUT2 and GND to adjust the output voltage between 1V and 10V. In adjustable mode, FB2 regulates to 1V (typ). See the <i>Setting the Output Voltage in Buck Converters</i> section.                                                                                                                                                                                                            |

# 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

## **Pin Description (continued)**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26  | OUT2    | Output Sense and Negative Current-Sense Input for Buck 2. When using the internal preset 3.3V feedback-divider (FB2 = BIAS), the buck uses OUT2 to sense the output voltage. Connect OUT2 to the negative terminal of the current-sense resistor. See the <i>Current Limiting and Current-Sense Inputs</i> and <i>Current-Sense Measurement</i> sections. |

| 27  | CS2     | Positive Current-Sense Input for Buck 2. Connect CS2 to the positive terminal of the current-sense resistor. See the <i>Current Limiting and Current-Sense Inputs</i> and <i>Current-Sense Measurement</i> sections.                                                                                                                                      |

| 28  | PGND2   | Power Ground for Buck 2                                                                                                                                                                                                                                                                                                                                   |

| 29  | DL2     | Low-Side Gate Drive Output for Buck 2. DL2 output voltage swings from $V_{PGND2}$ to $V_{BIAS}$ .                                                                                                                                                                                                                                                         |

| 30  | LX2     | Inductor Connection for Buck 2. Connect LX2 to the switched side of the inductor. LX2 serves as the lower supply rail for the DH2 high-side gate drive.                                                                                                                                                                                                   |

| 31  | DH2     | High-Side Gate Drive Output for Buck 2. DH2 output voltage swings from $V_{LX2}$ to $V_{BST2}$ .                                                                                                                                                                                                                                                          |

| 32  | BST2    | Boost Capacitor Connection for High-Side Gate Voltage of Buck 2. Connect a high-voltage diode between BIAS and BST2. Connect a ceramic capacitor between BST2 and LX2. See the <i>High-Side Gate-Driver Supply (BST_)</i> section.                                                                                                                        |

| 33  | FSELBST | Frequency Select Pin for the Preboost. When pulled low, the preboost will have the same switching frequency as buck 1. When pulled high, the preboost will have a switching frequency that is 1/5th that of buck 1. FSELBST is only active for the MAX16930. FSELBST should be connected to ground for the MAX16931.                                      |

| 34  | BSTON   | Preboost On-Indicator Output. To obtain a logic signal, pull up BSTON with an external resistor connected to a positive voltage lower than 5.5V. BSTON goes high to indicate that the preboost is on.                                                                                                                                                     |

| 35  | EN2     | High-Voltage Tolerant, Active-High Digital Enable Input for Buck 2. Driving EN2 high enables buck 2.                                                                                                                                                                                                                                                      |

| 36  | EN1     | High-Voltage Tolerant, Active-High Digital Enable Input for Buck 1. Driving EN1 high enables buck 1.                                                                                                                                                                                                                                                      |

| 37  | EN3     | High-Voltage Tolerant, Active-High Digital Enable Input for Preboost. When EN3 is high, the external preboost is enabled and begins switching if V <sub>INS</sub> drops below V <sub>INS,OLV</sub> and required conditions are met (see the <i>Preboost</i> section).                                                                                     |

| 39  | BST1    | Boost Capacitor Connection for High-Side Gate Voltage of Buck 1. Connect a high-voltage diode between BIAS and BST1. Connect a ceramic capacitor between BST1 and LX1. See the <i>High-Side Gate-Driver Supply (BST_)</i> section.                                                                                                                        |

| 40  | DH1     | High-Side Gate-Drive Output for Buck 1. DH1 output voltage swings from $V_{LX1}$ to $V_{BST1}$ .                                                                                                                                                                                                                                                          |

|     | EP      | Exposed Pad. Connect the exposed pad to ground. Connecting the exposed pad to ground does not remove the requirement for proper ground connections to PGND1, PGND2, PGND3, and AGND. The exposed pad is attached with epoxy to the substrate of the die, making it an excellent path to remove heat from the IC.                                          |

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

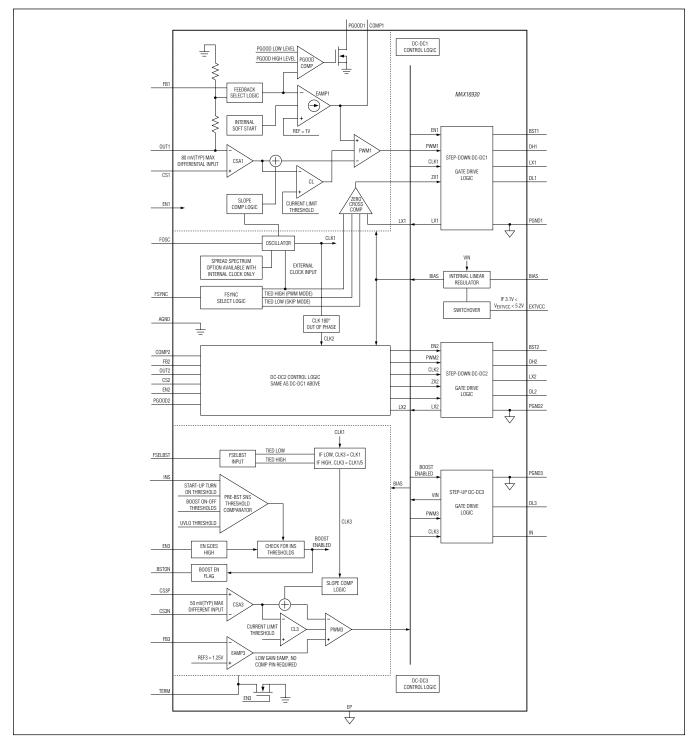

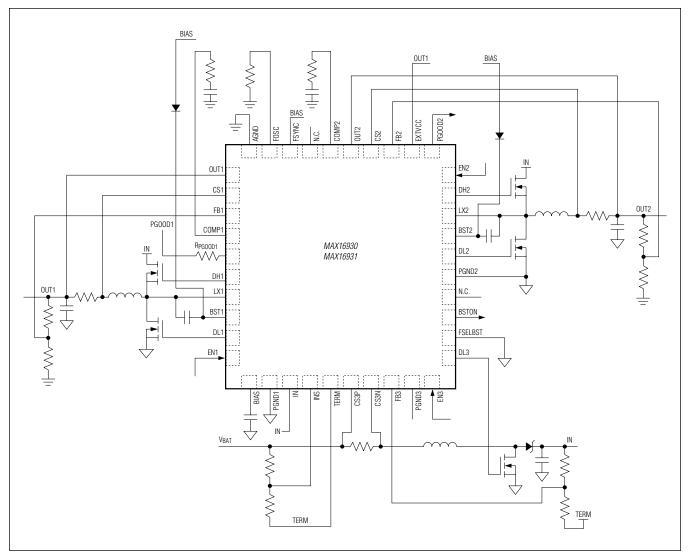

### **Detailed Description**

The MAX16930/MAX16931 are automotive-rated tripleoutput switching power supplies. These devices integrate two synchronous step-down controllers and an asynchronous step-up controller and can provide up to three independently controlled power rails as follows:

- A preboost with adjustable output voltage.

- A buck controller with a fixed 5V output voltage or an adjustable 1V to 10V output voltage.

- A buck controller with a fixed 3.3V output voltage or an adjustable 1V to 10V output voltage.

The buck controllers and the preboost can each provide up to 10A output current and are independently controllable.

Buck 1, buck 2, and the preboost are enabled and disabled by the EN1, EN2, and EN3 control inputs, respectively. These are active-high inputs and can be connected directly to car battery.

- EN1 and EN2 enable the respective buck controllers. Connect EN1 and EN2 directly to V<sub>BAT</sub> or to powersupply sequencing logic.

- EN3 controls the boost controller

In standby mode (only buck 2 is active), the total supply current is reduced to  $30\mu A$  (typ). When all three controllers are disabled, the total current drawn is further reduced to  $6.8\mu A$ .

### Fixed 5V Linear Regulator (BIAS)

The internal circuitry of the MAX16930/MAX16931 requires a 5V bias supply. An internal 5V linear regulator (BIAS) generates this bias supply. Bypass BIAS with a  $6.8\mu$ F or greater ceramic capacitor to guarantee stability under the full-load condition.

The internal linear regulator can source up to 100mA (150mA under EXTVCC switchover, see the <u>EXTVCC</u> <u>Switchover</u> section). Use the following equation to estimate the internal current requirements for the MAX16930/ MAX16931:

$$\begin{split} I_{BIAS} &= I_{CC} + f_{SW}(Q_{G\_DL3} + Q_{G\_DH1} + Q_{G\_DL1} + Q_{G\_DH2} + Q_{G\_DL2}) = 10 \text{mA to 50mA (typ)} \end{split}$$

where  $I_{CC}$  is the internal supply current, 5mA (typ),  $f_{SW}$  is the switching frequency, and  $Q_{G_{-}}$  is the MOSFET's total gate charge (specification limits at  $V_{GS} = 5V$ ). To minimize the internal power dissipation, bypass BIAS to an external 5V rail.

### **EXTVCC Switchover**

The internal linear regulator can be bypassed by connecting an external supply (3V to 5.2V) or the output of one of the buck converters to EXTVCC. BIAS internally switches to EXTVCC and the internal linear regulator turns off. This configuration has several advantages:

- It reduces the internal power dissipation of the MAX16930/MAX16931.

- The low-load efficiency improves as the internal supply current gets scaled down proportionally to the duty cycle.

If  $V_{EXTVCC}$  drops below  $V_{TH,EXTVCC} = 3.0V$  (min), the internal regulator enables and switches back to BIAS.

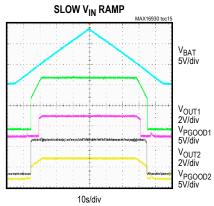

### Undervoltage Lockout (UVLO)

The BIAS input undervoltage-lockout (UVLO) circuitry inhibits switching if the 5V bias supply (BIAS) is below its 2.9V (typ) UVLO falling threshold. Once the 5V bias supply (BIAS) rises above its UVLO rising threshold and EN1 and EN2 enable the buck controllers, the controllers start switching and the output voltages begin to ramp up using soft-start.

### **Buck Controllers**

The MAX16930/MAX16931 provide two buck controllers with synchronous rectification. The step-down controllers use a PWM, current-mode control scheme. External logic-level MOSFETs allow for optimized load-current design. Fixed-frequency operation with optimal interleaving minimizes input ripple current from the minimum to the maximum input voltages. Output-current sensing provides an accurate current limit with a sense resistor or power dissipation can be reduced using loss-less current sensing across the inductor.

### Soft-Start

Once a buck converter is enabled by driving the corresponding EN\_ high, the soft-start circuitry gradually ramps up the reference voltage during soft-start time ( $t_{SSTART} = 6ms (typ)$ ) to reduce the input surge currents during startup. Before the device can begin the soft-start, the following conditions must be met:

- 1)  $V_{\mbox{BIAS}}$  exceeds the 3.4V (max) undervoltage lockout threshold.

- 2)  $V_{EN_{-}}$  is logic-high.

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

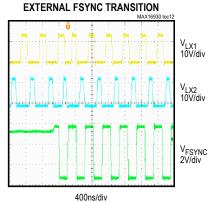

#### Switching Frequency/External Synchronization

The MAX16930 provides an internal oscillator adjustable from 1MHz to 2.2MHz. The MAX16931 provides an internal oscillator adjustable from 200kHz to 1MHz. High-frequency operation optimizes the application for the smallest component size, trading off efficiency to higher switching losses. Low-frequency operation offers the best overall efficiency at the expense of component size and board space. To set the switching frequency, connect a resistor R<sub>FOSC</sub> from FOSC to AGND. See TOCs 8 and 9 in the *Typical Operating Characteristics* section to determine the relationship between switching frequency and R<sub>FOSC</sub>.

Buck 1 and the boost converter are synchronized with the internal clock-signal rising edge, while buck 2 is synchronized with the clock-signal falling edge. The preboost enables the low-side switch (DL3) with the rising edge of the cycle while buck 1 turns on its highside n-channel MOSFET (DH1).

The devices can be synchronized to an external clock by connecting the external clock signal to FSYNC. A rising edge on FSYNC resets the internal clock. Keep the FSYNC frequency between 110% and 125% of the internal frequency. The FSYNC signal should have a 50% duty cycle.

### Light-Load Efficiency Skip Mode (V<sub>FSYNC</sub> = 0V)

Drive FSYNC low to enable skip mode. In skip mode, the devices stop switching until the FB voltage drops below the reference voltage. Once the FB voltage has dropped below the reference voltage, the devices begin switching until the inductor current reaches 30% (skip threshold) of the maximum current defined by the inductor DCR or output shunt resistor.

### Forced-PWM Mode (V<sub>FSYNC</sub>)

Driving FSYNC high prevents the devices from entering skip mode by disabling the zero-crossing detection of the inductor current. This forces the low-side gatedriver waveform to constantly be the complement of the high-side gate-drive waveform, so the inductor current reverses at light loads and discharges the output capacitor. The benefit of forced PWM mode is to keep the switching frequency constant under all load conditions. However, forced-frequency operation diverts a considerable amount of the output current to PGND, reducing the efficiency under light-load conditions.

Forced-PWM mode is useful for improving load-transient response and eliminating unknown frequency harmonics that can interfere with AM radio bands.

#### Maximum Duty-Cycle Operation

The devices have a maximum duty cycle of 95%. The internal logic of the IC looks for approximately 8 to 10 consecutive high-side FET ON pulses and decides to turn ON the low-side FET for 150ns (typ) every 12µs. The input voltage at which the devices enter dropout changes depending on the input voltage, output voltage, switching frequency, load current, and the efficiency of the design. The input voltage at which the devices enter dropout can be approximated as:

#### $V_{OUT} = [V_{OUT} + (I_{OUT} \times R_{ON} H)]/0.95$

**Note:** The above equation does not take into account the efficiency and switching frequency, but is a good first-order approximation. Use the  $R_{ON\_H}$  max number from the data sheet of the high-side MOSFET used.

#### **Spread Spectrum**

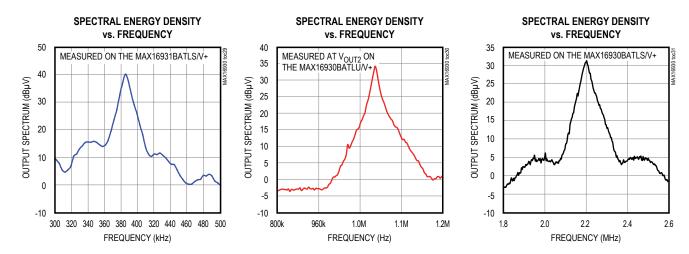

The MAX16930AGLS/MAX16930BAGLU/MAX16931BAGLS feature enhanced EMI performance. They perform  $\pm 6\%$  dithering of the switching frequency to reduce peak emission noise at the clock frequency and its harmonics, making it easier to meet stringent emission limits. When using an external clock source (i.e., driving the FSYNC input with an external clock), spread spectrum is disabled.

#### **Buck 2 Switching Frequency**

For the MAX16930ATLT and MAX16930BATLU, the switching frequency of buck 2 is set to 1/2 of  $f_{SW}$  (buck 1 switching frequency). When using these devices, the external components of buck 2 should be sized to account for the reduced switching frequencies (see the *Design Procedure* section).

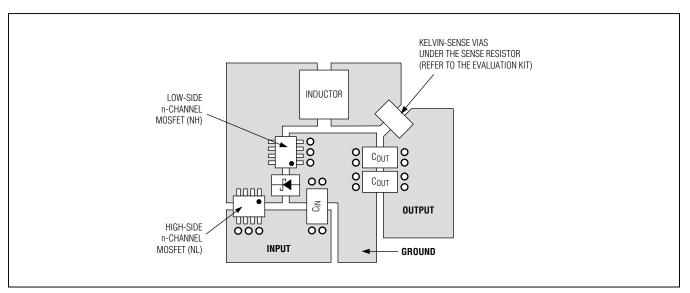

### MOSFET Gate Drivers (DH\_ and DL\_)

The DH\_ high-side n-channel MOSFET drivers are powered from capacitors at BST\_ while the low-side drivers (DL\_) are powered by the 5V linear regulator (BIAS). On each channel, a shoot-through protection circuit monitors the gate-to-source voltage of the external MOSFETs to prevent a MOSFET from turning on until the complementary switch is fully off. There must be a low-resistance, low-inductance path from the DL\_ and DH\_ drivers to the MOSFET gates for the protection circuits to work properly. Follow the instructions listed to provide the necessary lowresistance and low-inductance path:

• Use very short, wide traces (50 mils to 100 mils wide if the MOSFET is 1 in from the driver).

It may be necessary to decrease the slew rate for the gate drivers to reduce switching noise or to compensate for low-gate charge capacitors. For the low-side drivers,

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

use gate capacitors in the range of 1nF to 5nF from DL\_ to GND. For the high-side drivers, connect a small 5 $\Omega$  to 10 $\Omega$  resistor between BST\_ and the bootstrap capacitor.

**Note:** Gate drivers must be protected during shutdown, at the absence of the supply voltage ( $V_{BIAS} = 0V$ ) when the gate is pulled high either capacitively or by the leakage path on the PCB. Therefore, external gate pulldown resistors are needed, especially at DL3 to prevent making a direct path from  $V_{BAT}$  to GND.

### High-Side Gate-Driver Supply (BST\_)

The high-side MOSFET is turned on by closing an internal switch between BST\_ and DH\_ and transferring the bootstrap capacitor's (at BST\_) charge to the gate of the high-side MOSFET. This charge refreshes when the high-side MOSFET turns off and the LX\_ voltage drops down to ground potential, taking the negative terminal of the capacitor to the same potential. At this time the bootstrap diode recharges the positive terminal of the bootstrap capacitor.

The selected n-channel high-side MOSFET determines the appropriate boost capacitance values (C<sub>BST</sub> in the *Typical Operating Circuit*) according to the following equation:

$$C_{BST_{-}} = \frac{Q_{G}}{\Delta V_{BST_{-}}}$$

where  $Q_G$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST}$  is the voltage variation allowed on the high-side MOSFET driver after turn-on. Choose  $\Delta V_{BST}$  such that the available gate-drive voltage is not significantly degraded (e.g.,  $\Delta V_{BST}$  = 100mV to 300mV) when determining C<sub>BST</sub>. The boost capacitor should be a low-ESR ceramic capacitor. A minimum value of 100nF works in most cases.

## Current Limiting and Current-Sense Inputs (OUT\_ and CS\_)

The current-limit circuit uses differential current-sense inputs (OUT\_ and CS\_) to limit the peak inductor current. If the magnitude of the current-sense signal exceeds the current-limit threshold (V<sub>LIMIT1,2</sub> = 80mV (typ)), the PWM controller turns off the high-side MOSFET. The actual maximum load current is less than the peak current-limit threshold by an amount equal to half of the inductor ripple current. Therefore, the maximum load capability is a function of the current-sense resistance, inductor value, switching frequency, and duty cycle (V<sub>OUT\_</sub>/V<sub>IN</sub>).

For the most accurate current sensing, use a current-sense shunt resistor ( $R_{SH}$ ) between the inductor and the output

capacitor. Connect CS\_ to the inductor side of R<sub>SH</sub> and OUT\_ to the capacitor side. Dimension R<sub>SH</sub> such that the maximum inductor current (I<sub>L,MAX</sub> = I<sub>LOAD,MAX</sub>+1/2 I<sub>RIPPLE,PP</sub>) induces a voltage of V<sub>LIMIT1,2</sub> across R<sub>SH</sub> including all tolerances. For higher efficiency, the current can also be measured directly across the inductor. This method could cause up to 30% error over the entire temperature range and requires a filter network in the current-sense circuit. See the <u>Current-Sense Measurement</u> section.

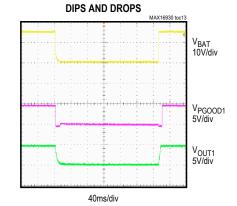

### Voltage Monitoring (PGOOD\_)

The MAX16930/MAX16931 include several power monitoring signals to facilitate power-supply sequencing and supervision. PGOOD\_ can be used to enable circuits that are supplied by the corresponding voltage rail, or to turn on subsequent supplies.

Each PGOOD\_ goes high (high impedance) when the corresponding regulator output voltage is in regulation. Each PGOOD\_ goes low when the corresponding regulator output voltage drops below 15% (typ) or rises above 15% (typ) of its nominal regulated voltage. Connect a 10k $\Omega$  (typ) pullup resistor from PGOOD\_ to the relevant logic rail to level-shift the signal. PGOOD\_ asserts low during soft-start, soft-discharge, and when either buck converter is disabled (either EN1 or EN2 is low). To ensure latchup immunity on the PGOOD1 pin in compliance with the AEC-Q100 guidelines, a minimum resistance of 100 $\Omega$  should be placed between the PGOOD1 pin and any other external components.

#### Supply Monitoring (INS)

The supply voltage in automotive systems can vary significantly and indicate potentially dangerous situations for the application. Undervoltage transients can indicate impending loss of power (for example during engine-start with a weak battery), while overvoltage conditions can quickly exceed the thermal budget of the application.

The devices include a dedicated battery voltage sensor at INS to quickly detect overvoltage and undervoltage for the boost converter.

| SIGNAL             | VBAT(MIN)<br>(V) | VBAT(TYP)<br>(V) | VBAT(MAX)<br>(V) |

|--------------------|------------------|------------------|------------------|

| VINS,OFF           | 10.38            | 10.81            | 11.25            |

| VINS,ON,SW         | 9.515            | 9.95             | 10.38            |

| VINS,UV<br>Rising  | 2.81             | 3.0275           | 3.24             |

| VINS,UV<br>Falling | 2.38             | 2.6              | 2.81             |

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

Connect INS to the center tap of a resistive divider from the input voltage (battery) to TERM to set the threshold voltage for V<sub>INS,OFF</sub>, V<sub>INS,ON,SW</sub>, and V<sub>INS,UV</sub>. For example, with a 153k $\Omega$  ±1% resistor between INS and V<sub>BAT</sub> and a 20k $\Omega$  ±1% resistor between INS and TERM, the following typical automotive V<sub>BAT</sub> levels can be sensed, allowing for proper turn-on/turn-off of the preboost. If this setting is not sufficient, optimize the divider for the most critical level. For the MAX16930ATLV/V+ and MAX16930BATLW/V+, the INS pin functionality is disabled; however, the INS pin should still be connected using the resistor-divider between V<sub>BAT</sub> and the TERM pin, as explained above.

### Preboost

The MAX16930/MAX16931 include an asynchronous current-mode preboost with adjustable output. This preboost can be used independently, but is ideally suited for applications that need to stay fully functional during input voltage dropouts typical for automotive cold-crank or start-stop.

The preboost is turned on by bringing EN3 high.

EN3 can be used for power-supply sequencing and implementing a boost timeout to prevent overheating the components used for the boost converter.

While the boost circuit is essential to maintain functionality during undervoltage events, it reduces system efficiency. During normal operation, the boost diode dissipates power and the resistive dividers at INS and FB3 sink significant amounts of quiescent current. To ensure latchup immunity on the INS and FB3 pins in compliance with the AEC-Q100 guidelines, ensure that the parallel combination of this resistor-divider network used on these pins is >  $500\Omega$ .

## Increasing the Efficiency of the Boost Circuit (TERM)

The MAX16930/MAX16931 provide a feature to improve the efficiency of the boost circuit when it is not active:

TERM provides a switch to GND for the INS and FB3 voltage-dividers. This switch opens during standby mode and shutdown mode to reduce the quiescent current by 240µA, assuming that resistors used in the voltage-divider network are in the range of 100kΩ.

### Preboost n-Channel MOSFET Driver (DL3)

DL3 drives the gate of an external n-channel MOSFET. The driver is powered by the 5V (typ) internal regulator (BIAS) or the external bypass supply (EVTVCC). DL3 asserts low during standby mode.

### **Switching Frequency in Boost Controller**

The preboost switching frequency ( $f_{BOOST}$ ) is derived from the buck controllers switching frequency ( $f_{SW}$ ) by setting FOSC. See the <u>Electrical Characteristics</u> table. On the MAX16930,  $f_{BOOST}$  can be set equal to  $f_{SW}$  by connecting FBSTSEL to ground or to 1/5 $f_{SW}$  by connecting FBSTSEL to BIAS. The gate driver of the preboost turns on simultaneously with the high-side driver of buck 1. FSELBST should be connected to ground on the MAX16931.

#### **Current Limit in Boost Controller**

A current-sense resistor (R<sub>CS</sub>), connected CS3P and CS3N, sets the current limit of the boost converter. The CS input has a voltage trip level (V<sub>CS</sub>) of 120mV (typ). The low 120mV current-limit threshold reduces the power dissipation in the current-sense resistor. Use a current-sense filter to reduce capacitive coupling during turn on. See the <u>Shunt Resistor Selection in Boost Converter</u> section.

#### Thermal-Overload, Overcurrent, and Overvoltage and Undervoltage Behavior

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the devices. When the junction temperature exceeds +170°C, an internal thermal sensor shuts down the devices, allowing them to cool. The thermal sensor turns on the devices again after the junction temperature cools by 20°C.

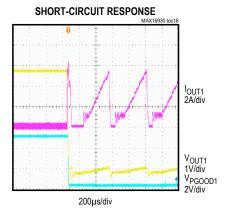

#### **Overcurrent Protection**

If the inductor current on the MAX16930 and MAX16931 exceed the maximum current limit programmed at CS\_ and OUT\_, the respective driver turns off. In an overcurrent mode, this results in shorter and shorter high-side pulses.

A hard short results in a minimum on-time pulse every clock cycle.

Choose the components so they can withstand the shortcircuit current if required.

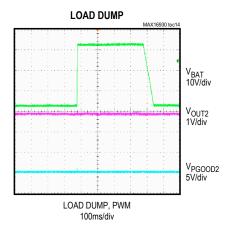

#### **Overvoltage Protection**

The devices limit the output voltage of the buck converters by turning off the high-side gate driver at approximately 115% of the regulated output voltage. The output voltage needs to come back in regulation before the high-side gate driver starts switching again.

# 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

### **Design Procedure**

### **Buck Converter Design Procedure**

### Effective Input Voltage Range in Buck Converters

Although the MAX16930/MAX16931 can operate from input supplies up to 36V (42V transients) and regulate down to 1V, the minimum voltage conversion ratio ( $V_{OUT}$ /  $V_{IN}$ ) might be limited by the minimum controllable on-time. For proper fixed-frequency PWM operation and optimal efficiency, buck 1 and buck 2 should operate in continuous conduction during normal operating conditions. For continuous conduction, set the voltage conversion ratio as follows:

$$\frac{V_{OUT}}{V_{IN}} > t_{ON(MIN)} \times f_{SW}$$

where  $t_{ON(MIN)}$  is 50ns (typ) and  $f_{SW}$  is the switching frequency in Hz. If the desired voltage conversion does not meet the above condition, pulse skipping occurs to decrease the effective duty cycle. Decrease the switching frequency if constant switching frequency is required. The same is true for the maximum voltage conversion ratio.

The maximum voltage conversion ratio is limited by the maximum duty cycle (95%).

$$\frac{V_{OUT}}{V_{IN} - V_{DROP}} < 0.95$$

where  $V_{DROP} = I_{OUT} (R_{ON,HS} + R_{DCR})$  is the sum of the parasitic voltage drops in the high-side path and  $f_{SW}$  is the programmed switching frequency. During low drop operation, the devices reduce  $f_{SW}$  to 25% (max) of the programmed frequency. In practice, the above condition should be met with adequate margin for good load-transient response.

### Setting the Output Voltage in Buck Converters

Connect FB1 and FB2 to BIAS to enable the fixed buck controller output voltages (5V and 3.3V) set by a preset internal resistive voltage-divider connected between the feedback (FB\_) and AGND. To externally adjust the output voltage between 1V and 10V, connect a resistive divider from the output (OUT\_) to FB\_ to AGND (see the <u>Typical Operating Circuit</u>. Calculate  $R_{FB_1}$  and  $R_{FB_2}$  with the following equation:

$$R_{FB_1} = R_{FB_2} \left[ \left( \frac{V_{OUT_1}}{V_{FB_1}} \right) - 1 \right]$$

where  $V_{FB} = 1V$  (typ) (see the <u>Electrical Characteristics</u> table).

DC output accuracy specifications in the <u>Electrical</u> <u>Characteristics</u> table refer to the error comparator's threshold,  $V_{FB}$  = 1V (typ). When the inductor conducts continuously, the devices regulate the peak of the output ripple, so the actual DC output voltage is lower than the slope-compensated trip level by 50% of the output ripple voltage.

In discontinuous conduction mode (skip or STDBY active and  $I_{OUT} < I_{LOAD(SKIP)}$ ), the devices regulate the valley of the output ripple, so the output voltage has a DC regulation level higher than the error-comparator threshold.

### **Inductor Selection in Buck Converters**

Three key inductor parameters must be specified for operation with the MAX16930/MAX16931: inductance value (L), inductor saturation current ( $I_{SAT}$ ), and DC resistance ( $R_{DCR}$ ). To determine the optimum inductance, knowing the typical duty cycle (D) is important.

$$D = \frac{V_{OUT}}{V_{IN}} OR D = \frac{V_{OUT}}{V_{IN} - I_{OUT} (R_{DS(ON)} + R_{DCR})}$$

if the R<sub>DCR</sub> of the inductor and R<sub>DS(ON)</sub> of the MOSFET are available with V<sub>IN</sub> = (V<sub>BAT</sub> - V<sub>DIODE</sub>). All values should be typical to optimize the design for normal operation.

### Inductance

The exact inductor value is not critical and can be adjusted in order to make trade-offs among size, cost, efficiency, and transient response requirements.

- Lower inductor values increase LIR, which minimizes size and cost and improves transient response at the cost of reduced efficiency due to higher peak currents.

- Higher inductance values decrease LIR, which increases efficiency by reducing the RMS current at the cost of requiring larger output capacitors to meet load-transient specifications.

The ratio of the inductor peak-to-peak AC current to DC average current (LIR) must be selected first. A good initial value is a 30% peak-to-peak ripple current to average current ratio (LIR = 0.3). The switching frequency, input voltage, output voltage, and selected LIR then determine the inductor value as follows:

$$L[\mu H] = \frac{(V_{IN} - V_{OUT}) \times D}{f_{SW} [MHz] \times I_{OUT} \times LIR}$$

where  $V_{IN}$ ,  $V_{OUT}$ , and  $I_{OUT}$  are typical values (so that efficiency is optimum for typical conditions).

## 2MHz, 36V, Dual Buck with Preboost and 20µA Quiescent Current

#### **Peak Inductor Current**

Inductors are rated for maximum saturation current. The maximum inductor current equals the maximum load current in addition to half of the peak-to-peak ripple current:

$$I_{\text{PEAK}} = I_{\text{LOAD}(\text{MAX})} + \frac{\Delta I_{\text{INDUCTOR}}}{2}$$

For the selected inductance value, the actual peak-to-peak inductor ripple current ( $\Delta I_{INDUCTOR}$ ) is calculated as:

$\Delta I_{INDUCTOR} = \frac{V_{OUT} \left(V_{IN} - V_{OUT}\right)}{V_{IN} \times f_{SW} \times L}$

where  $\Delta I_{INDUCTOR}$  is in mA, L is in  $\mu H,$  and  $f_{SW}$  is in kHz.

Once the peak current and the inductance are known, the inductor can be selected. The saturation current should be larger than  $I_{PEAK}$  or at least in a range where the inductance does not degrade significantly. The MOSFETs are required to handle the same range of current without dissipating too much power.

#### **MOSFET Selection in Buck Converters**

Each step-down controller drives two external logic-level n-channel MOSFETs as the circuit switch elements. The key selection parameters to choose these MOSFETs include the items in the following sections.

#### **Threshold Voltage**

All four n-channel MOSFETs must be a logic-level type with guaranteed on-resistance specifications at  $V_{GS}$  = 4.5V. If the internal regulator is bypassed (for example:  $V_{EXTVCC}$  = 3.3V), then the n-channel MOSFETs should be chosen to have guaranteed on-resistance at that gate-to-source voltage.

#### Maximum Drain-to-Source Voltage (VDS(MAX))

All MOSFETs must be chosen with an appropriate  $V_{\text{DS}}$  rating to handle all  $V_{\text{IN}}$  voltage conditions.

#### **Current Capability**

The n-channel MOSFETs must deliver the average current to the load and the peak current during switching. Choose MOSFETs with the appropriate average current at  $V_{GS}$  = 4.5V or  $V_{GS}$  =  $V_{EXTVCC}$  when the internal linear regulator is bypassed. For load currents below approximately 3A, dual MOSFETs in a single package can be an economical solution. To reduce switching noise for smaller MOSFETs, use a series resistor in the BST\_ path and additional gate capacitance. Contact the factory for guidance using gate resistors.

#### **Current-Sense Measurement**

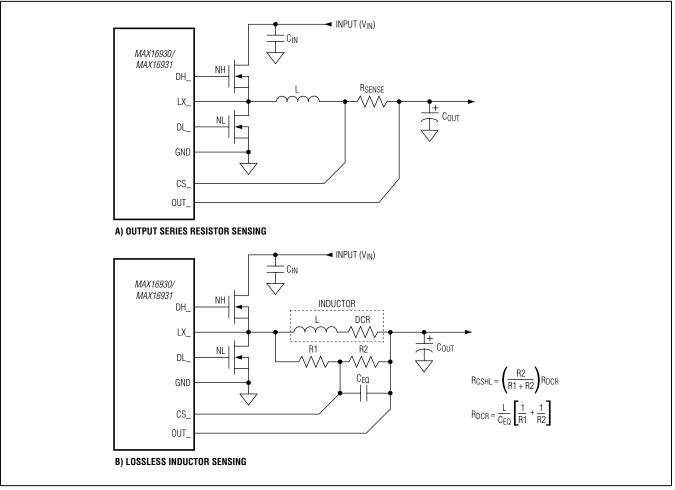

For the best current-sense accuracy and overcurrent protection, use a  $\pm 1\%$  tolerance current-sense resistor between the inductor and output as shown in Figure 1A. This configuration constantly monitors the inductor current, allowing accurate current-limit protection. Use low-inductance current-sense resistors for accurate measurement.

Alternatively, high-power applications that do not require highly accurate current-limit protection can reduce the overall power dissipation by connecting a series RC circuit across the inductor (Figure 1B) with an equivalent time constant:

$$R_{CSHL} = \left(\frac{R2}{R1+R2}\right)R_{DCR}$$

and:

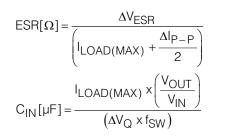

$$\mathsf{R}_{\mathsf{DCR}} = \frac{\mathsf{L}}{\mathsf{C}_{\mathsf{EQ}}} \left( \frac{1}{\mathsf{R1}} + \frac{1}{\mathsf{R2}} \right)$$